#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

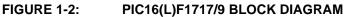

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1719t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3-7: PIC16(L)F1717 MEMORY MAP, BANK 24-31

= Unimplemented data memory locations, read as '0'.

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh |                               | C8Bh |                               | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| C0Ch | —                             | C8Ch | —                             | D0Ch | —                             | D8Ch | _                             | E0Ch |                               | E8Ch |                               | F0Ch |                               | F8Ch |                               |

| C0Dh | _                             | C8Dh | -                             | D0Dh | -                             | D8Dh | —                             | E0Dh |                               | E8Dh |                               | F0Dh |                               | F8Dh |                               |

| C0Eh | —                             | C8Eh | _                             | D0Eh | _                             | D8Eh | _                             | E0Eh |                               | E8Eh |                               | F0Eh |                               | F8Eh |                               |

| C0Fh | —                             | C8Fh | —                             | D0Fh | —                             | D8Fh |                               | E0Fh |                               | E8Fh |                               | F0Fh |                               | F8Fh |                               |

| C10h | —                             | C90h | _                             | D10h | _                             | D90h | _                             | E10h |                               | E90h |                               | F10h |                               | F90h |                               |

| C11h | —                             | C91h | —                             | D11h | _                             | D91h |                               | E11h |                               | E91h |                               | F11h |                               | F91h |                               |

| C12h | —                             | C92h | —                             | D12h | —                             | D92h | _                             | E12h |                               | E92h |                               | F12h |                               | F92h |                               |

| C13h | _                             | C93h | _                             | D13h | _                             | D93h |                               | E13h |                               | E93h |                               | F13h |                               | F93h |                               |

| C14h | —                             | C94h | —                             | D14h | —                             | D94h | _                             | E14h |                               | E94h |                               | F14h |                               | F94h |                               |

| C15h | —                             | C95h | —                             | D15h | —                             | D95h |                               | E15h |                               | E95h |                               | F15h |                               | F95h |                               |

| C16h | —                             | C96h | —                             | D16h | _                             | D96h |                               | E16h |                               | E96h |                               | F16h |                               | F96h |                               |

| C17h | _                             | C97h | _                             | D17h | _                             | D97h | _                             | E17h | See Table 3-9 for             | E97h | See Table 3-9 for             | F17h | See Table 3-9 for             | F97h | See Table 3-10 for            |

| C18h | _                             | C98h | _                             | D18h | _                             | D98h | _                             | E18h | register mapping              | E98h | register mapping              | F18h | register mapping              | F98h | register mapping              |

| C19h | —                             | C99h | —                             | D19h | —                             | D99h | —                             | E19h | details                       | E99h | details                       | F19h | details                       | F99h | details                       |

| C1Ah | —                             | C9Ah | —                             | D1Ah | —                             | D9Ah | —                             | E1Ah |                               | E9Ah |                               | F1Ah |                               | F9Ah |                               |

| C1Bh | —                             | C9Bh | —                             | D1Bh | —                             | D9Bh | _                             | E1Bh |                               | E9Bh |                               | F1Bh |                               | F9Bh |                               |

| C1Ch | _                             | C9Ch | _                             | D1Ch | _                             | D9Ch | _                             | E1Ch |                               | E9Ch |                               | F1Ch |                               | F9Ch |                               |

| C1Dh | _                             | C9Dh | _                             | D1Dh | _                             | D9Dh | _                             | E1Dh |                               | E9Dh |                               | F1Dh |                               | F9Dh |                               |

| C1Eh | _                             | C9Eh | _                             | D1Eh | _                             | D9Eh | _                             | E1Eh |                               | E9Eh |                               | F1Eh |                               | F9Eh |                               |

| C1Fh | _                             | C9Fh | _                             | D1Fh | _                             | D9Fh | —                             | E1Fh |                               | E9Fh |                               | F1Fh |                               | F9Fh |                               |

| C20h |                               | CA0h |                               | D20h |                               | DA0h |                               | E20h |                               | EA0h |                               | F20h |                               | FA0h |                               |

|      | Unimplemented<br>Read as '0'  |      |                               |      |                               |      |                               |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

|      | Accesses<br>70h – 7Fh         |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                               | E7Fh |                               | EFFh |                               | F7Fh |                               | FFFh |                               |

Legend:

| R/W-0/0          | R/W-0/0                                                                        | R/W-0/0                                 | R/W-0/0        | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |  |  |

|------------------|--------------------------------------------------------------------------------|-----------------------------------------|----------------|-----------------|-----------------|----------------|--------------|--|--|--|

| CxINTP           | CxINTN                                                                         |                                         | CxPCH<2:0>     | > CxNCH<2:0>    |                 |                |              |  |  |  |

| bit 7            |                                                                                |                                         |                |                 |                 |                | bit          |  |  |  |

| Lagandi          |                                                                                |                                         |                |                 |                 |                |              |  |  |  |

| Legend:          |                                                                                |                                         |                |                 |                 |                |              |  |  |  |

| R = Readable     |                                                                                | W = Writable                            |                | •               | mented bit, rea |                |              |  |  |  |

| u = Bit is unc   | •                                                                              | x = Bit is unkr                         |                | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set |                                                                                | '0' = Bit is clea                       | ared           |                 |                 |                |              |  |  |  |

| bit 7            | CxINTP: Co                                                                     | mparator Interru                        | pt on Positive | e Going Edge E  | nable bits      |                |              |  |  |  |

|                  |                                                                                | F interrupt flag v<br>rupt flag will be |                |                 |                 |                |              |  |  |  |

| bit 6            | CxINTN: Co                                                                     | mparator Interru                        | ipt on Negativ | e Going Edge I  | Enable bits     |                |              |  |  |  |

|                  |                                                                                | F interrupt flag                        |                |                 |                 |                |              |  |  |  |

|                  | 0 = No inter                                                                   | rupt flag will be                       | set on a nega  | tive going edge | e of the CxOUT  | bit            |              |  |  |  |

| bit 5-3          | CxPCH<2:0                                                                      | Comparator I                            | Positive Input | Channel Select  | t bits          |                |              |  |  |  |

|                  | -                                                                              | 111 = CxVP connects to AGND             |                |                 |                 |                |              |  |  |  |

|                  | 110 = CxVP connects to FVR Buffer 2                                            |                                         |                |                 |                 |                |              |  |  |  |

|                  | 101 = CxVP connects to DAC1_output<br>100 = CxVP connects to DAC2 output       |                                         |                |                 |                 |                |              |  |  |  |

|                  | $100 = CxVP$ connects to DAC2_output<br>011 = CxVP unconnected, input floating |                                         |                |                 |                 |                |              |  |  |  |

|                  | 010 = CxVP unconnected, input floating                                         |                                         |                |                 |                 |                |              |  |  |  |

|                  |                                                                                | 001 = CxVP connects to CxIN1+ pin       |                |                 |                 |                |              |  |  |  |

|                  | 000 = CxVP connects to CxIN0+ pin                                              |                                         |                |                 |                 |                |              |  |  |  |

| bit 2-0          | CxNCH<2:0                                                                      | >: Comparator I                         | Vegative Input | t Channel Seleo | ct bits         |                |              |  |  |  |

|                  | 111 = CxVN                                                                     | 111 = CxVN connects to AGND             |                |                 |                 |                |              |  |  |  |

|                  | 110 = CxVN connects to FVR Buffer 2                                            |                                         |                |                 |                 |                |              |  |  |  |

|                  | 101 = CxVN unconnected, input floating                                         |                                         |                |                 |                 |                |              |  |  |  |

|                  |                                                                                | unconnected, i                          |                |                 |                 |                |              |  |  |  |

|                  |                                                                                | connects to Cx                          |                |                 |                 |                |              |  |  |  |

|                  |                                                                                | connects to Cx<br>connects to Cx        | •              |                 |                 |                |              |  |  |  |

|                  |                                                                                |                                         |                |                 |                 |                |              |  |  |  |

#### REGISTER 16-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

| Name                 | Bit 7            | Bit 6            | Bit 5  | Bit 4  | Bit 3   | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |

|----------------------|------------------|------------------|--------|--------|---------|------------|--------|--------|---------------------|--|

| INTCON               | GIE              | PEIE             | TMR0IE | INTE   | IOCIE   | TMR0IF     | INTF   | IOCIF  | 90                  |  |

| NCO1ACCU             |                  | — NCO1ACC<19:16> |        |        |         |            |        |        |                     |  |

| NCO1ACCH             |                  |                  |        | NCO1AC | C<15:8> |            |        |        | 239                 |  |

| NCO1ACCL             |                  | NCO1ACC<7:0>     |        |        |         |            |        |        |                     |  |

| NCO1CLK              | N                | 1PWS<2:0         | >      | _      | _       | _          | N1CK   | S<1:0> | 238                 |  |

| NCO1CON              | N1EN — I         |                  | N1OUT  | N1POL  | —       | _          | —      | N1PFM  | 237                 |  |

| NCO1INCU             | — NCO1INC<19:16> |                  |        |        |         |            |        |        | 240                 |  |

| NCO1INCH             |                  |                  |        | NCO1IN | C<15:8> |            |        |        | 240                 |  |

| NCO1INCL             |                  |                  |        | NCO1IN | NC<7:0> |            |        |        | 239                 |  |

| PIE3                 | _                | NCOIE            | COGIE  | ZCDIE  | CLC4IE  | CLC3IE     | CLC2IE | CLC1IE | 93                  |  |

| PIR3                 | _                | NCOIF            | COGIF  | ZCDIF  | CLC4IF  | CLC3IF     | CLC2IF | CLC1IF | 96                  |  |

| TRISA                | TRISA7           | TRISA6           | TRISA5 | TRISA4 | TRISA3  | TRISA2     | TRISA1 | TRISA0 | 124                 |  |

| TRISC                | TRISC7           | TRISC6           | TRISC5 | TRISC4 | TRISC3  | TRISC2     | TRISC1 | TRISC0 | 135                 |  |

| TRISD <sup>(1)</sup> | TRISD7           | TRISD6           | TRISD5 | TRISD4 | TRISD3  | TRISD2     | TRISD1 | TRISD0 | 140                 |  |

| RxyPPS               |                  |                  | _      |        | F       | RxyPPS<4:0 | >      |        | 153                 |  |

TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOX

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCOx module.

Note 1: PIC16(L)F1717/9 only.

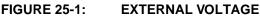

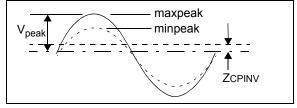

#### 25.0 ZERO-CROSS DETECTION (ZCD) MODULE

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, ZCPINV, which is typically 0.75 V above ground.

The connection to the signal to be detected is through a series current limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 25-2.

The ZCD module is useful when monitoring an AC waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- · Low EMI cycle switching

#### 25.1 External Resistor Selection

The ZCD module requires a current limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 25-1 and Figure 25-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it doesn't interfere with the current source and sink.

$$R_{series} = \frac{V_{peak}}{3 \times 10^{-4}}$$

### FIGURE 25-2: SIMPLIFIED ZCD BLOCK DIAGRAM

### 28.5 Register Definitions: Timer2 Control

### REGISTER 28-1: T2CON: TIMER2 CONTROL REGISTER

| U-0                          | R/W-0/0                                            | R/W-0/0                                          | R/W-0/0       | R/W-0/0       | R/W-0/0          | R/W-0/0     | R/W-0/0      |  |  |  |  |

|------------------------------|----------------------------------------------------|--------------------------------------------------|---------------|---------------|------------------|-------------|--------------|--|--|--|--|

| _                            |                                                    | T2OUT                                            | PS<3:0>       |               | TMR2ON           | T2CKPS<1:0> |              |  |  |  |  |

| bit 7                        | ·                                                  |                                                  |               |               |                  |             | bit          |  |  |  |  |

|                              |                                                    |                                                  |               |               |                  |             |              |  |  |  |  |

| <b>Legend:</b><br>R = Readab | le hit                                             | W = Writable                                     | hit           | II = Unimplei | mented bit, read | as '0'      |              |  |  |  |  |

| u = Bit is unchanged         |                                                    | x = Bit is unkr                                  |               |               | at POR and BO    |             | other Resets |  |  |  |  |

| 1' = Bit is set              |                                                    | '0' = Bit is clea                                |               |               |                  |             |              |  |  |  |  |

| 1 - Dit 13 3                 |                                                    |                                                  |               |               |                  |             |              |  |  |  |  |

| bit 7                        | Unimpleme                                          | nted: Read as '                                  | 0'            |               |                  |             |              |  |  |  |  |

| bit 6-3                      | T2OUTPS<3:0>: Timer2 Output Postscaler Select bits |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1111 = 1:16 Postscaler                             |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1110 <b>= 1:15</b>                                 |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1101 <b>= 1:14</b>                                 |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1100 = 1:13                                        |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1011 = 1:12                                        |                                                  |               |               |                  |             |              |  |  |  |  |

|                              |                                                    | 1010 = 1:11 Postscaler<br>1001 = 1:10 Postscaler |               |               |                  |             |              |  |  |  |  |

|                              |                                                    | 000 = 1:9 Postscaler                             |               |               |                  |             |              |  |  |  |  |

|                              | 0111 = <b>1</b> :8 F                               |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 0110 = 1.7 F                                       |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 0101 = 1:6 F                                       | Postscaler                                       |               |               |                  |             |              |  |  |  |  |

|                              | 0100 = 1:5 F                                       | 0100 = 1:5 Postscaler                            |               |               |                  |             |              |  |  |  |  |

|                              | 0011 = <b>1</b> :4 F                               |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 0010 = 1:3 F                                       |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 0001 = 1:2 F                                       |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 0000 = 1:1 F                                       |                                                  |               |               |                  |             |              |  |  |  |  |

| bit 2                        | TMR2ON: T                                          |                                                  |               |               |                  |             |              |  |  |  |  |

|                              | 1 = Timer2 i<br>0 = Timer2 i                       |                                                  |               |               |                  |             |              |  |  |  |  |

| bit 1-0                      | T2CKPS<1:                                          | 0>: Timer2 Cloc                                  | k Prescale Se | elect bits    |                  |             |              |  |  |  |  |

|                              | 11 = Presca                                        | ler is 64                                        |               |               |                  |             |              |  |  |  |  |

|                              | 10 = Presca                                        | ler is 16                                        |               |               |                  |             |              |  |  |  |  |

|                              | 01 = Presca                                        | ler is 4                                         |               |               |                  |             |              |  |  |  |  |

|                              | 00 = Presca                                        |                                                  |               |               |                  |             |              |  |  |  |  |

#### 29.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1 and CCP2).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

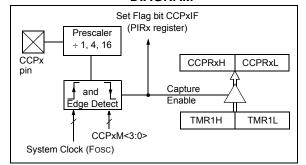

#### 29.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 29-1 shows a simplified diagram of the capture operation.

#### 29.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 29-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 29.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

| Name    | Bit 7      | Bit 6        | Bit 5      | Bit 4                      | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |  |

|---------|------------|--------------|------------|----------------------------|--------------|---------|---------|---------|---------------------|--|

| CCP1CON | _          | _            | DC1B       | <1:0>                      |              | CCP1N   | ∕l<3:0> |         | 294                 |  |

| CCPR1L  | Capture/Co | mpare/PWM    | Register 1 | (LSB)                      |              |         |         |         | 291*                |  |

| CCPTMRS | P4TSE      | L<1:0>       | P3TSE      | L<1:0>                     | C2TSE        | EL<1:0> | C1TSE   | :L<1:0> | 286                 |  |

| INTCON  | GIE        | PEIE         | TMR0IE     | TMR0IE INTE IOCIE TMR0IF I |              | INTF    | IOCIF   | 90      |                     |  |

| PIE1    | TMR1GIE    | ADIE         | RCIE       | TXIE                       | SSP1IE       | CCP1IE  | TMR2IE  | TMR1IE  | 91                  |  |

| PIE2    | OSFIE      | C2IE         | C1IE       | _                          | BCL1IE       | TMR6IE  | TMR4IE  | CCP2IE  | 92                  |  |

| PIR1    | TMR1GIF    | ADIF         | RCIF       | TXIF                       | SSP1IF       | CCP1IF  | TMR2IF  | TMR1IF  | 94                  |  |

| PIR2    | OSFIF      | C2IF         | C1IF       | _                          | BCL1IF       | TMR6IF  | TMR4IF  | CCP2IF  | 95                  |  |

| PR2     | Timer2 Per | iod Registe  | ٢          |                            |              |         |         |         | 282*                |  |

| ANSELB  | —          | _            | ANSB5      | ANSB4                      | ANSB3        | ANSB2   | ANSB1   | ANSB0   | 131                 |  |

| ANSELC  | ANSC7      | ANSC6        | ANSC5      | ANSC4                      | ANSC3        | ANSC2   |         | _       | 136                 |  |

| TRISB   | TRISB7     | TRISB6       | TRISB5     | TRISB4                     | TRISB3       | TRISB2  | TRISB1  | TRISB0  | 130                 |  |

| TRISC   | TRISC7     | TRISC6       | TRISC5     | TRISC4                     | TRISC3       | TRISC2  | TRISC1  | TRISC0  | 135                 |  |

| RxyPPS  | _          |              |            |                            | 153          |         |         |         |                     |  |

| CCP1PPS | _          |              | _          |                            | 152          |         |         |         |                     |  |

| CCP2PPS | —          | —            | —          |                            | CCP2PPS<4:0> |         |         |         |                     |  |

| T2CON   |            |              | T2OUT      | PS<3:0>                    |              | TMR2ON  | T2CKP   | S<1:0>  | 284                 |  |

| TMR2    | Timer2 Mo  | dule Registe | er         |                            |              |         |         |         | 282                 |  |

#### TABLE 29-3: SUMMARY OF REGISTERS ASSOCIATED WITH CCP

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP.

\* Page provides register information.

| FIGURE 30-9:                        | SPI N                                 | IODE W     | /AVEFO                | RM (SL                                     | AVE MC                                                                                      | DE WIT           | HCKE                                   | = 0)             |                              |                                                                                   |                 |

|-------------------------------------|---------------------------------------|------------|-----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|------------------|----------------------------------------|------------------|------------------------------|-----------------------------------------------------------------------------------|-----------------|

|                                     | ·<br>·                                |            |                       |                                            |                                                                                             |                  |                                        |                  |                              |                                                                                   | <br>            |

|                                     | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-  |            | -<br>                 | ·<br>· · · · · · · · · · · · · · · · · · · |                                                                                             |                  | -<br>                                  |                  |                              | •                                                                                 | :<br>:<br>:<br> |

| 80%<br>(CKF = 1<br>(CKF = 0)        | ·<br>·<br>·<br>·                      |            |                       |                                            | ,<br>,<br>,                                                                                 |                  |                                        |                  | ·<br>·<br>·                  |                                                                                   | 3<br>           |

| WERE 10<br>SEP (BUF<br>VER11<br>SEC |                                       |            |                       |                                            | ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; |                  |                                        |                  |                              | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: | ·<br>·<br>·     |

|                                     |                                       |            | <br>;<br>;<br>;       | ,                                          | ,                                                                                           | ,                | /~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | , / ~,           |                              | , , , , , , , , , , , , , , , , , , ,                                             |                 |

| lapat<br>Secupio                    |                                       | 1941 7<br> | *<br>*<br>*<br>*<br>* | :<br>:<br>:<br>:<br>:<br>:                 | :<br>:<br>: 40:<br>: 40:                                                                    |                  | ;<br>;<br>;<br>;<br>;                  |                  |                              | 20<br>2<br>2                                                                      |                 |

|                                     |                                       |            | s<br>s<br>s<br>s      | <                                          | 2<br>2<br>2<br>2<br>2                                                                       | ;<br>;<br>,<br>, | s<br>c<br>s<br>s                       | 2<br>2<br>2<br>2 | 2<br>2<br>2<br>2<br>2<br>    | :<br>:<br>:<br>:                                                                  |                 |

| 9.891982 85<br>86919609             | · · · · · · · · · · · · · · · · · · · |            | -<br>2<br>2<br>2      | ,<br>5<br>7<br>7                           | •<br>\$<br>\$<br>•                                                                          |                  | -<br>2<br>2<br>2                       | ,<br>5<br>7<br>7 | •<br>• :<br>• :<br>• · · · · | ,<br>/p.<br>,                                                                     |                 |

| Virite Catistan<br>detection active |                                       |            |                       |                                            | ********                                                                                    |                  |                                        |                  |                              |                                                                                   |                 |

#### FIGURE 30-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SS           SCK           (CKP = 0           CKE = 1)           SCK           (CKP = 1           CKE = 1)           Write to           SSP1BUF           XxXXX |                                 |             |                     |        |                       |                            |               |                            |                       |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------|---------------------|--------|-----------------------|----------------------------|---------------|----------------------------|-----------------------|----------|

| SDO ——                                                                                                                                                          |                                 | bit 7       | bit 6               | bit 5  | bit 4                 | bit 3                      | bit 2         | bit 1                      | bit 0                 |          |

| SDI ——                                                                                                                                                          | 1<br><u>1</u><br>1              | bit 7       | $\sim$              |        | $\sim$                |                            | $\rightarrow$ |                            | bit 0                 |          |

| Input<br>Sample                                                                                                                                                 |                                 | <u>†</u>    | 1                   | 1      | 1                     | 1                          | 1             | <u> </u>                   | <u> </u>              |          |

| SSP1IF<br>Interrupt<br>Flag                                                                                                                                     | -<br>-<br>-<br>-<br>-<br>-<br>- |             | <br> <br> <br> <br> | 1<br>1 | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1 |               | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1 |          |

| SSP1SR to<br>SSP1BUF                                                                                                                                            |                                 | 1<br>1<br>1 | 1<br>1<br>1         | I      | 1<br>1<br>1           | I<br>I<br>I                | 1<br>1<br>1   | 1<br>1<br>1<br>T           | 1<br>1<br>1<br>1      | <u>.</u> |

| Vote Collegion<br>Anterior polive                                                                                                                               |                                 |             |                     |        |                       |                            |               |                            |                       | ·        |

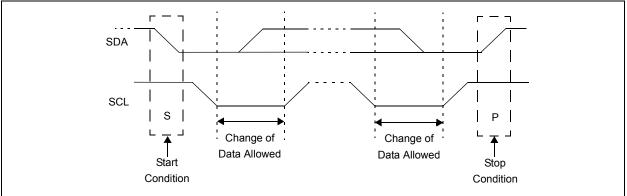

#### 30.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 30-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 30.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

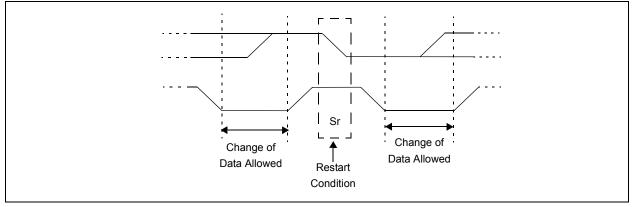

#### 30.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 30-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

## 30.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSP1CON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

#### FIGURE 30-12: I<sup>2</sup>C START AND STOP CONDITIONS

#### FIGURE 30-13: I<sup>2</sup>C RESTART CONDITION

#### 30.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 30-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSP1STAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSP1BUF clearing the BF flag.

- 7. Slave loads low address into SSP1ADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSP1ADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSP1IF is set.

- **Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSP1ADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSP1BUF clearing BF.

- 12. Slave loads high address into SSP1ADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSP1CON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSP1BUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

#### 30.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSP1ADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 30-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 30-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                               |

| Example:         | RETFIE                                                                                                                                                                                                          |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |  |  |  |

| Operands:        | None                                                                                                                                                  |  |  |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                            |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                          |                  | d ∈ [0,1]                                                                                                                                                                                                         |  |  |  |  |

|                  | $TOS \rightarrow PC$                                                                                                                                                          | Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                          | Status Affected: | C                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                             |                  | C Register f                                                                                                                                                                                                      |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                             |                  |                                                                                                                                                                                                                   |  |  |  |  |

| Example:         | CALL TABLE;W contains table                                                                                                                                                   | Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |

|                  | ;offset value                                                                                                                                                                 | Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |  |

|                  | <ul> <li>;W now has table value</li> </ul>                                                                                                                                    | Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |  |

| TABLE            | •                                                                                                                                                                             |                  | Before Instruction                                                                                                                                                                                                |  |  |  |  |

|                  | ADDWF PC $;W = offset$                                                                                                                                                        |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |

|                  | RETLW k1 ;Begin table                                                                                                                                                         |                  | C = 0<br>After Instruction                                                                                                                                                                                        |  |  |  |  |

|                  | RETLW k2 ;                                                                                                                                                                    |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |

|                  | •                                                                                                                                                                             |                  | $W = 1100 \ 1100$                                                                                                                                                                                                 |  |  |  |  |

|                  | •                                                                                                                                                                             |                  | C = 1                                                                                                                                                                                                             |  |  |  |  |

|                  | RETLW kn ; End of table                                                                                                                                                       |                  |                                                                                                                                                                                                                   |  |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                                                   |  |  |  |  |

|  | TABLE 34-9: | PLL CLOCK TIMING SPECIFICATIONS |

|--|-------------|---------------------------------|

|--|-------------|---------------------------------|

| Standard Operating Conditions (unless otherwise stated) |                     |                               |        |       |        |       |            |  |

|---------------------------------------------------------|---------------------|-------------------------------|--------|-------|--------|-------|------------|--|

| Param.<br>No.                                           | Sym.                | Characteristic                | Min.   | Typ.† | Max.   | Units | Conditions |  |

| F10                                                     | Fosc                | Oscillator Frequency Range    | 4      | _     | 8      | MHz   |            |  |

| F11                                                     | Fsys                | On-Chip VCO System Frequency  | 16     | _     | 32     | MHz   |            |  |

| F12                                                     | TRC                 | PLL Start-up Time (Lock Time) | —      | —     | 2      | ms    |            |  |

| F13*                                                    | $\Delta \text{CLK}$ | CLKOUT Stability (Jitter)     | -0.25% | _     | +0.25% | %     |            |  |

These parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

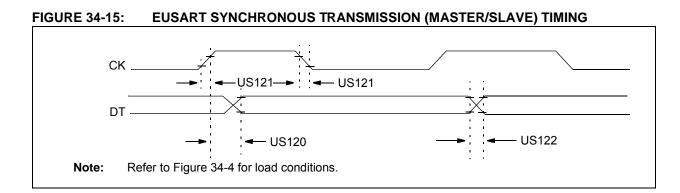

#### TABLE 34-22: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                   |      |      |                           |                                  |

|---------------------------------------------------------|----------|-----------------------------------|------|------|---------------------------|----------------------------------|

| Param.<br>No.                                           | Symbol   | Characteristic                    | Min. | Max. | Units                     | Conditions                       |

| US120                                                   | TCKH2DTV | SYNC XMIT (Master and Slave)      |      | 80   | ns                        | $3.0V \le VDD \le 5.5V$          |

|                                                         |          | Clock high to data-out valid      |      | 100  | ns                        | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US121                                                   | TCKRF    | Clock out rise time and fall time | _    | 45   | ns                        | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |          | (Master mode)                     | _    | 50   | ns                        | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US122                                                   | TDTRF    | Data-out rise time and fall time  | _    | 45   | ns                        | $3.0V \le V\text{DD} \le 5.5V$   |

|                                                         |          |                                   | _    | 50   | ions $1.8V \le VDD \le 3$ | $1.8V \le V\text{DD} \le 5.5V$   |

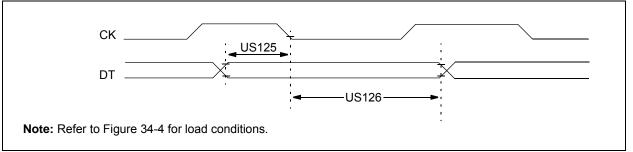

#### FIGURE 34-16: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 34-23: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                  |      |      |       |            |  |

|---------------------------------------------------------|----------|--------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                                           | Symbol   | Characteristic                                   | Min. | Max. | Units | Conditions |  |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave)                      |      |      |       |            |  |

|                                                         |          | Data-setup before CK $\downarrow$ (DT hold time) | 10   | —    | ns    |            |  |

| US126                                                   | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)   | 15   | _    | ns    |            |  |

#### TABLE 34-24: SPI MODE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                       |                                                                       |              |       |      |       |                                  |

|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|--------------|-------|------|-------|----------------------------------|

| Param.<br>No.                                           | Symbol                | Characteristic                                                        | Min.         | Тур.† | Max. | Units | Conditions                       |

| SP70*                                                   | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | 2.25 TCY     | _     |      | ns    |                                  |

| SP71*                                                   | TscH                  | SCK input high time (Slave mode)                                      | Tcy + 20     |       |      | ns    |                                  |

| SP72*                                                   | TscL                  | SCK input low time (Slave mode)                                       | Tcy + 20     | —     | —    | ns    |                                  |

| SP73*                                                   | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge                              | 100          | —     | —    | ns    |                                  |

| SP74*                                                   | TscH2DIL,<br>TscL2DIL | Hold time of SDI data input to SCK edge                               | 100          | —     | —    | ns    |                                  |

| SP75*                                                   | TDOR                  | SDO data output rise time                                             | _            | 10    | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |                       |                                                                       |              | 25    | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP76*                                                   | TDOF                  | SDO data output fall time                                             | —            | 10    | 25   | ns    |                                  |

| SP77*                                                   | TssH2doZ              | SS <sup>↑</sup> to SDO output high-impedance                          | 10           | —     | 50   | ns    |                                  |

| SP78*                                                   | TscR                  | SCK output rise time<br>(Master mode)                                 | —            | 10    | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |                       |                                                                       | —            | 25    | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP79*                                                   | TscF                  | SCK output fall time (Master mode)                                    | —            | 10    | 25   | ns    |                                  |

| SP80*                                                   | TscH2doV,<br>TscL2doV |                                                                       | —            | —     | 50   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |                       |                                                                       | —            | —     | 145  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP81*                                                   | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge                                     | 1 Tcy        | —     | —    | ns    |                                  |

| SP82*                                                   | TssL2DoV              | SDO data output valid after $\overline{SS}\downarrow$ edge            | —            | —     | 50   | ns    |                                  |

| SP83*                                                   | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   | 1.5 Tcy + 40 | —     | —    | ns    |                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

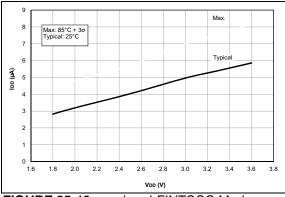

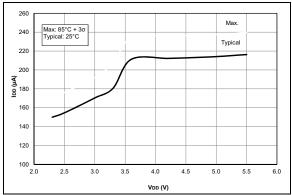

FIGURE 35-19: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16LF1717/8/9 Only.

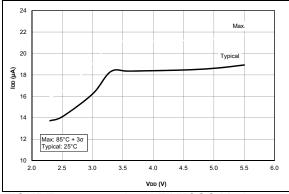

FIGURE 35-20: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1717/8/9 Only.

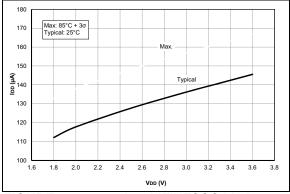

FIGURE 35-21: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16LF1717/8/9 Only.

FIGURE 35-22: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16F1717/8/9 Only.

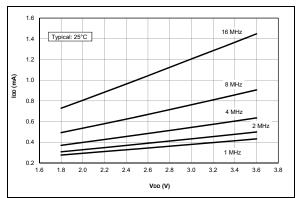

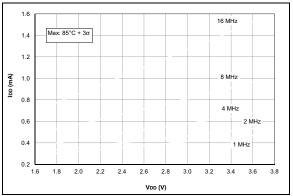

FIGURE 35-23: IDD Typical, HFINTOSC Mode, PIC16LF1717/8/9 Only.

FIGURE 35-24: IDD Maximum, HFINTOSC Mode, PIC16LF1717/8/9 Only.

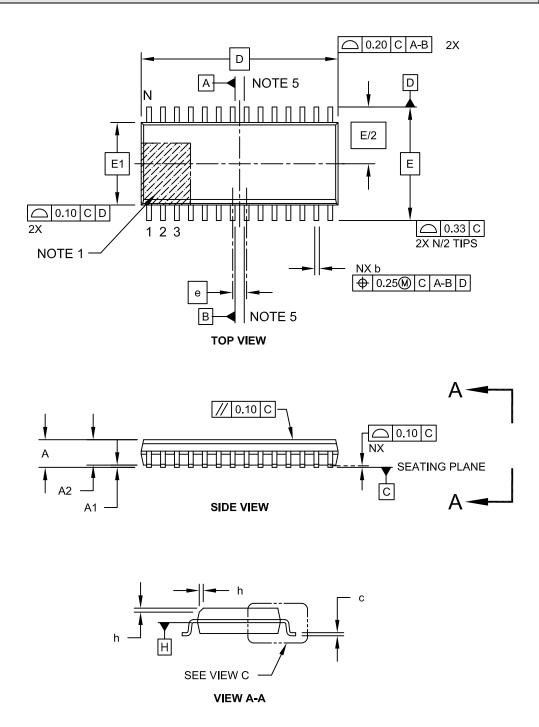

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

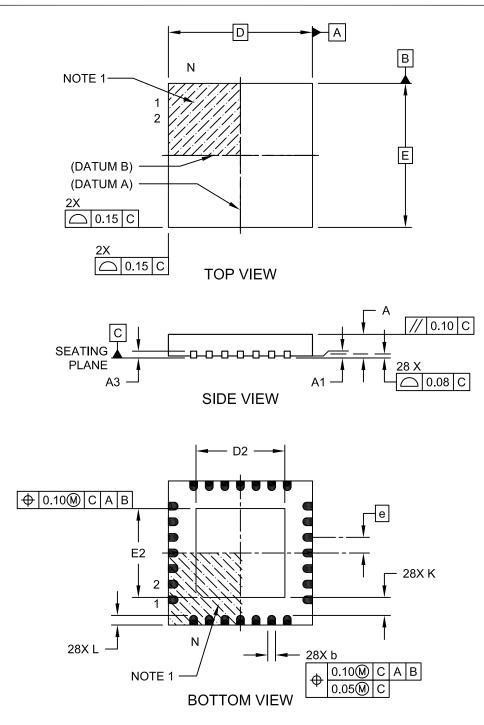

## 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2