#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                |                                                                           |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1717-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name               | Function           | Input<br>Type | Output<br>Type | Description                                        |

|--------------------|--------------------|---------------|----------------|----------------------------------------------------|

| OUT <sup>(2)</sup> | C1OUT              |               | CMOS           | Comparator 1 output.                               |

|                    | C2OUT              |               | CMOS           | Comparator 2 output.                               |

|                    | CCP1               |               | CMOS           | Compare/PWM1 output.                               |

|                    | CCP2               |               | CMOS           | Compare/PWM2 output.                               |

|                    | NCO10UT            |               | CMOS           | Numerically controlled oscillator output.          |

|                    | PWM3OUT            |               | CMOS           | PWM3 output.                                       |

|                    | PWM4OUT            |               | CMOS           | PWM4 output.                                       |

|                    | COG1A              |               | CMOS           | Complementary output generator output A.           |

|                    | COG1B              |               | CMOS           | Complementary output generator output B.           |

|                    | COG1C              |               | CMOS           | Complementary output generator output C.           |

|                    | COG1D              |               | CMOS           | Complementary output generator output D.           |

|                    | SDA <sup>(3)</sup> |               | OD             | I <sup>2</sup> C Data output.                      |

|                    | SCK                |               | CMOS           | SPI clock output.                                  |

|                    | SCL <sup>(3)</sup> |               | OD             | I <sup>2</sup> C clock output.                     |

|                    | SDO                |               | CMOS           | SPI data output.                                   |

|                    | TX/CK              |               | CMOS           | EUSART asynchronous TX data/synchronous clock out. |

|                    | DT <sup>(3)</sup>  |               | CMOS           | EUSART synchronous data output.                    |

|                    | CLC10UT            |               | CMOS           | Configurable Logic Cell 1 output.                  |

|                    | CLC2OUT            |               | CMOS           | Configurable Logic Cell 2 output.                  |

|                    | CLC3OUT            |               | CMOS           | Configurable Logic Cell 3 output.                  |

|                    | CLC4OUT            |               | CMOS           | Configurable Logic Cell 4 output.                  |

#### TABLE 1-3: PIC16(L)F1717/9 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

configuration memory will be erased.

#### REGISTER 4-1: **CONFIG1: CONFIGURATION WORD 1 (CONTINUED)** bit 7 **CP:** Code Protection bit<sup>(1)</sup> 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled MCLRE: MCLR/VPP Pin Function Select bit bit 6 If LVP bit = 1: This bit is ignored. If LVP bit = 0: 1 = MCLR/VPP pin function is MCLR; Weak pull-up enabled. 0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUE3 bit. bit 5 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled 0 = PWRT enabled bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit 11 = WDT enabled 10 = WDT enabled while running and disabled in Sleep 01 = WDT controlled by the SWDTEN bit in the WDTCON register 00 = WDT disabled bit 2-0 FOSC<2:0>: Oscillator Selection bits 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin 110 = ECM: External Clock, Medium Power mode (0.5-4 MHz): device clock supplied to CLKIN pin 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin 100 = INTOSC oscillator: I/O function on CLKIN pin 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins Note 1: The entire Flash program memory will be erased when the code protection is turned off during an erase. When a Bulk Erase Program Memory command is executed, the entire program Flash memory and

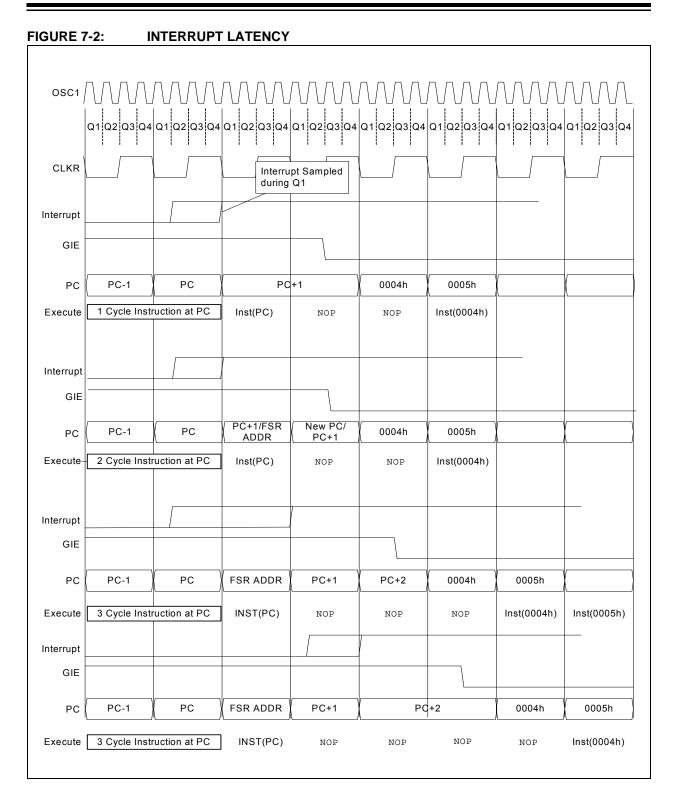

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

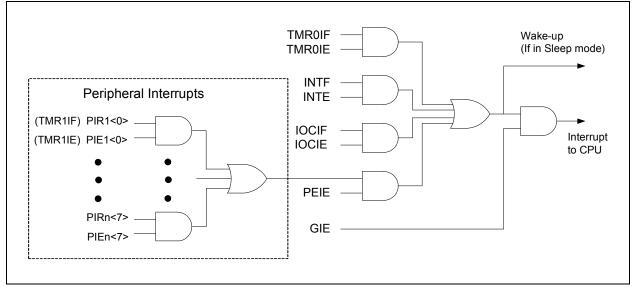

A block diagram of the interrupt logic is shown in Figure 7-1.

## FIGURE 7-1: INTERRUPT LOGIC

# PIC16(L)F1717/8/9

| REGISTE<br>R/W-0/ |                                            |                              |                |                   |                   |                   |                   |

|-------------------|--------------------------------------------|------------------------------|----------------|-------------------|-------------------|-------------------|-------------------|

| OSFIF             |                                            | R/W-0/0<br>C1IF              | U-0            | R/W-0/0<br>BCL1IF | R/W-0/0<br>TMR6IF | R/W-0/0<br>TMR4IF | R/W-0/0<br>CCP2IF |

|                   | 0211                                       | CHE                          | —              | DOLTIF            | TIVITOIT          | 110117411         |                   |

| bit 7             |                                            |                              |                |                   |                   |                   | bit 0             |

| Legend:           |                                            |                              |                |                   |                   |                   |                   |

| R = Reada         | able bit                                   | W = Writable                 | bit            | U = Unimple       | mented bit, read  | 1 as '0'          |                   |

|                   | unchanged                                  | x = Bit is unkr              | nown           | •                 | at POR and BO     |                   | other Resets      |

| '1' = Bit is      | set                                        | '0' = Bit is clea            | ared           |                   |                   |                   |                   |

|                   |                                            |                              |                |                   |                   |                   |                   |

| bit 7             | <b>OSFIF:</b> Oscill                       | ator Fail Interru            | upt Flag bit   |                   |                   |                   |                   |

|                   | 1 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| bit 6             | 0 = Interrupt i                            | rator C2 Interru             | unt Elog hit   |                   |                   |                   |                   |

| DILO              | 1 = Interrupt i                            |                              | ipt i lag bit  |                   |                   |                   |                   |

|                   | 0 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| bit 5             | C1IF: Compa                                | rator C1 Interru             | upt Flag bit   |                   |                   |                   |                   |

|                   | 1 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| L:1 /             | 0 = Interrupt i                            |                              | o'             |                   |                   |                   |                   |

| bit 4<br>bit 3    | -                                          | ted: Read as '               |                | aa hit            |                   |                   |                   |

| DIUS              | 1 = Interrupt i                            | SP Bus Collisio<br>s pending | n interrupt Fi | ay bit            |                   |                   |                   |

|                   | 0 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| bit 2             | TMR6IF: Time                               | er6 to PR6 Inte              | rrupt Flag bit | :                 |                   |                   |                   |

|                   | 1 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| hit 1             | 0 = Interrupt i                            |                              | rrunt Eloa bit |                   |                   |                   |                   |

| bit 1             | 1 = Interrupt i                            | er4 to PR4 Inte<br>s pending | пирі гіад ві   |                   |                   |                   |                   |

|                   | 0 = Interrupt i                            |                              |                |                   |                   |                   |                   |

| bit 0             | CCP2IF: CCF                                | 2 Interrupt Fla              | g bit          |                   |                   |                   |                   |

|                   | 1 = Interrupt i                            |                              |                |                   |                   |                   |                   |

|                   | 0 = Interrupt i                            | s not pending                |                |                   |                   |                   |                   |

|                   |                                            |                              |                |                   |                   |                   |                   |

| Note:             | Interrupt flag bits a condition occurs, re |                              |                |                   |                   |                   |                   |

|                   | its corresponding e                        |                              |                |                   |                   |                   |                   |

|                   | Enable bit, GIE, o                         | f the INTCON                 |                |                   |                   |                   |                   |

|                   | User software appropriate interru          | should ensu                  |                |                   |                   |                   |                   |

|                   | prior to enabling a                        |                              |                |                   |                   |                   |                   |

|                   |                                            |                              |                |                   |                   |                   |                   |

## REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

## 8.2 Low-Power Sleep Mode

The PIC16F1717/8/9 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1717/8/9 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

# 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

## 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use only with the following peripherals:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- External interrupt pin/Interrupt-on-Change pins

- Timer1 (with external clock source < 100 kHz)

- Note: The PIC16LF1717/8/9 does not have a configurable Low-Power Sleep mode. PIC16LF1717/8/9 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F1717/8/9. See Section 34.0 "Electrical Specifications" for more information.

#### 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:5>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

## **15.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFV  | R<1:0> | ADFVF | R<1:0> | 165                 |

Legend: Shaded cells are unused by the temperature indicator module.

PIC16(L)F1717/8/9

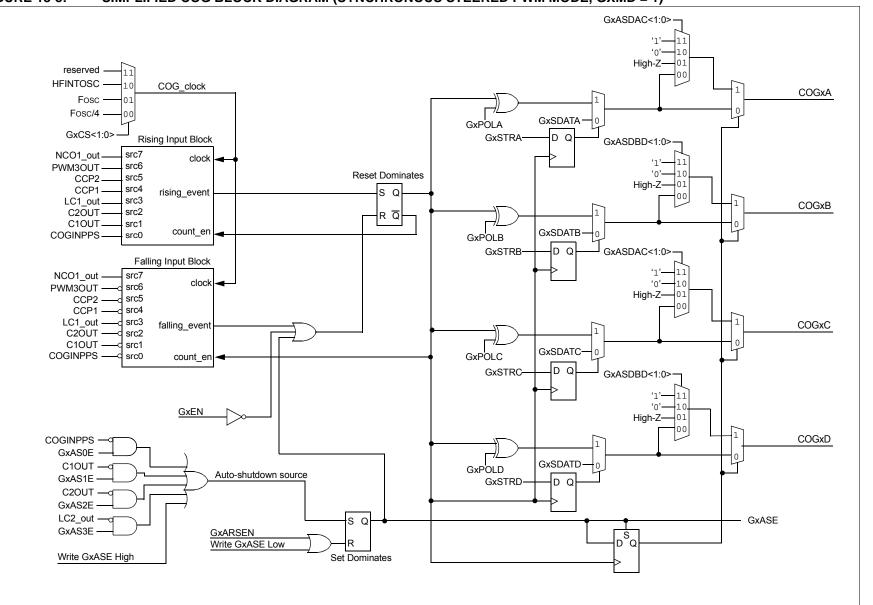

## FIGURE 18-3: SIMPLIFIED COG BLOCK DIAGRAM (SYNCHRONOUS STEERED PWM MODE, GXMD = 1)

## 18.8 Auto-shutdown Control

Auto-shutdown is a method to immediately override the COG output levels with specific overrides that allow for safe shutdown of the circuit.

The shutdown state can be either cleared automatically or held until cleared by software. In either case, the shutdown overrides remain in effect until the first rising event after the shutdown is cleared.

#### 18.8.1 SHUTDOWN

The shutdown state can be entered by either of the following two mechanisms:

- · Software generated

- External Input

#### 18.8.1.1 Software Generated Shutdown

Setting the GxASE bit of the COGxASD0 register (Register 18-7) will force the COG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist until the first rising event after the GxASE bit is cleared by software.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the first rising event after the shutdown input clears. See Figure 18-15 and **Section 18.8.3.2 "Auto-Restart"**.

#### 18.8.1.2 External Shutdown Source

External shutdown inputs provide the fastest way to safely suspend COG operation in the event of a Fault condition. When any of the selected shutdown inputs goes true, the output drive latches are reset and the COG outputs immediately go to the selected override levels without software delay.

Any combination of the input sources can be selected to cause a shutdown condition. Shutdown occurs when the selected source is low. Shutdown input sources include:

- Any input pin selected with the COGxPPS control

- C2OUT

- C10UT

- CLC2OUT

Shutdown inputs are selected independently with bits of the COGxASD1 register (Register 18-8).

| Note: | edge s | own input<br>sensitive.<br>ared as lo | The sh | nutdov | vn sta | ate car | nnot  |

|-------|--------|---------------------------------------|--------|--------|--------|---------|-------|

|       |        | persists,<br>hutdown,                 | exc    | ept    | by     | disab   | oling |

## 18.8.2 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown is active, are controlled by the GxASDAC<1:0> and GxASDBC<1:0> bits of the COGxASD0 register (Register 18-7). GxASDAC<1:0> controls the COGxA and COGxC override levels and GxASDBC<1:0> controls the COGxB and COGxD override levels. There are four override options for each output pair:

- · Forced low

- · Forced high

- Tri-state

- PWM inactive state (same state as that caused by a falling event)

Note: The polarity control does not apply to the forced low and high override levels but does apply to the PWM inactive state.

## 18.8.3 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the COGxASD0 register. Waveforms of a software controlled automatic restart are shown in Figure 18-15.

#### 18.8.3.1 Software Controlled Restart

When the GxARSEN bit of the COGxASD0 register is cleared, software must clear the GxASE bit to restart COG operation after an auto-shutdown event.

The COG will resume operation on the first rising event after the GxASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be false, otherwise, the GxASE bit will remain set.

#### 18.8.3.2 Auto-Restart

When the GxARSEN bit of the COGxASD0 register is set, the COG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically and the COG will resume operation on the first rising event after all selected shutdown inputs go false.

#### REGISTER 18-4: COGxRSIM: COG RISING EVENT SOURCE INPUT MODE REGISTER

bit 0

GxRSIM0: COGx Rising Event Input Source 0 Mode bit

GxRIS0 = 1:

1 = Pin selected with COGxPPS control low-to-high transition will cause a rising event after rising event phase delay

0 = Pin selected with COGxPPS control high level will cause an immediate rising event GxRIS0 = 0:

Pin selected with COGxPPS control has no effect on rising event

#### REGISTER 18-10: COGxDBR: COG RISING EVENT DEAD-BAND COUNT REGISTER

| U-0                               | U-0   | R/W-x/u           | R/W-x/u                                                             | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u     |  |  |

|-----------------------------------|-------|-------------------|---------------------------------------------------------------------|------------------------------------|---------|---------|-------------|--|--|

| —                                 | —     |                   |                                                                     | GxDB                               | R<5:0>  |         |             |  |  |

| bit 7                             |       |                   |                                                                     |                                    |         |         | bit 0       |  |  |

|                                   |       |                   |                                                                     |                                    |         |         |             |  |  |

| Legend:                           |       |                   |                                                                     |                                    |         |         |             |  |  |

| R = Readable bit W = Writable bit |       |                   |                                                                     | U = Unimplemented bit, read as '0' |         |         |             |  |  |

| u = Bit is uncha                  | anged | x = Bit is unkr   | K = Bit is unknown -n/n = Value at POR and BOR/Value at all other F |                                    |         |         | ther Resets |  |  |

| '1' = Bit is set                  |       | '0' = Bit is clea | '0' = Bit is cleared q = Value depends on condition                 |                                    |         |         |             |  |  |

bit 7-6 Unimplemented: Read as '0' bit 5-0 GxDBR<5:0>: Rising Event Dead-band Count Value bits GxRDBS = 1: = Number of delay chain element periods to delay primary output after rising event GxRDBS = 0: = Number of COGx clock periods to delay primary output after rising event

#### REGISTER 18-11: COGxDBF: COG FALLING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

|       | —   |         |         | GxDB    | F<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

## bit 7-6 Unimplemented: Read as '0'

bit 5-0 GxDBF<5:0>: Falling Event Dead-band Count Value bits

GxFDBS = 1:

= Number of delay chain element periods to delay complementary output after falling event input GxFDBS = 0:

= Number of COGx clock periods to delay complementary output after falling event input

| r                |         |                    |         |                |                  |                  |              |

|------------------|---------|--------------------|---------|----------------|------------------|------------------|--------------|

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|                  |         |                    | NCOxIN  | C<15:8>        |                  |                  |              |

| bit 7            |         |                    |         |                |                  |                  | bit 0        |

|                  |         |                    |         |                |                  |                  |              |

| Legend:          |         |                    |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable b     | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unknown |         | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ired    |                |                  |                  |              |

# REGISTER 20-7: NCOxINCH: NCOx INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

bit 7-0 NCOxINC<15:8>: NCOx Increment, High Byte

Note 1: Write the NCOxINCH register first, then the NCOxINCL register. See Section 20.1.4 "Increment Registers" for more information.

## REGISTER 20-8: NCOxINCU: NCOx INCREMENT REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCOxIN  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxINC<19:16>: NCOx Increment, Upper Byte

Note 1: Write the NCOxINCU register first, then the NCOxINCL register. See Section 20.1.4 "Increment Registers" for more information.

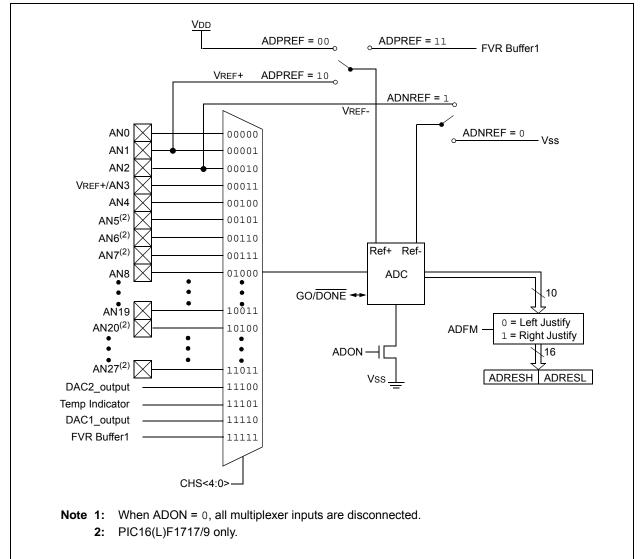

## 21.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 21-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 21-1: ADC BLOCK DIAGRAM

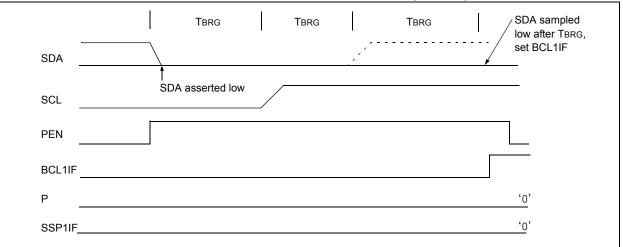

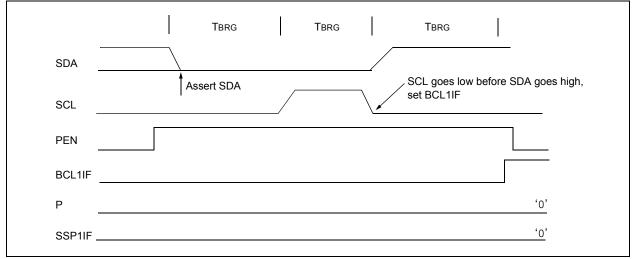

#### 30.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSP1ADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 30-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 30-39).

### FIGURE 30-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

## FIGURE 30-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

## 30.8 Register Definitions: MSSP Control

| REGISTER 3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |                                                                         |                                                   |                    |                      | D 0/0     |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|--------------------|----------------------|-----------|--|

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R-0/0                                                                                           | R-0/0                                                                   | R-0/0                                             | R-0/0              | R-0/0                | R-0/0     |  |

| SMP              | CKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D/A                                                                                             | Р                                                                       | S                                                 | R/W                | UA                   | BF        |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |                                                                         |                                                   |                    |                      | bit (     |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| R = Readable b   | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable b                                                                                  | pit                                                                     | U = Unimplen                                      | nented bit, read a | as '0'               |           |  |

| u = Bit is uncha |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | x = Bit is unkn                                                                                 |                                                                         | •                                                 | -                  | /Value at all othe   | er Resets |  |

| '1' = Bit is set | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cleared                                                                            |                                                                         |                                                   |                    |                      |           |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| bit 7            | $\frac{SPI Master mo}{1 = Input data}$ $0 = Input data$ $\frac{SPI Slave moo}{SMP must be}$ $\frac{In I^2C Master o}{1 = Slew rate}$                                                                                                                                                                                                                                                                                                                                                    | sampled at end<br>sampled at mid<br>de:<br>cleared when S<br>or Slave mode:<br>control disabled | l of data outpu<br>dle of data ou<br>PI is used in \$<br>d for Standard | tput time<br>Slave mode                           | 00 kHz and 1 M     | Hz)                  |           |  |

| bit 6            | <b>CKE:</b> SPI Cloc<br>In <u>SPI Master</u><br>1 = Transmit o<br>0 = Transmit o<br>In $I^2C^{\text{TM}}$ mode<br>1 = Enable inp                                                                                                                                                                                                                                                                                                                                                        | ck Edge Select<br>or Slave mode:<br>occurs on transit<br>occurs on transit<br>only:             | bit (SPI mode<br>ion from activ<br>ion from Idle t<br>thresholds are    | only)<br>e to Idle clock st<br>to active clock st | ate                | ation                |           |  |

| bit 5            | <b>D/A:</b> Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                                                                                                                                                                                                                                  |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| bit 4            | <ul> <li>P: Stop bit</li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul>                                                                                                                                                                                                       |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| bit 3            | <ul> <li>Start bit</li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                                                                                                                                       |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| bit 2            | This bit holds t<br>match to the n<br>$ln l^2C$ Slave m<br>1 = Read<br>0 = Write<br>$ln l^2C$ Master<br>1 = Transmit<br>0 = Transmit                                                                                                                                                                                                                                                                                                                                                    | ext Start bit, Sto<br><u>iode:</u><br><u>mode:</u><br>is in progress<br>is not in progress      | mation follow <u>i</u><br>op bit, or not A                              | ng the last addre<br>CK bit.                      |                    | it is only valid fro |           |  |

| bit 1            | <ul> <li>UA: Update Address bit (10-bit I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the user needs to update the address in the SSP1ADD register</li> <li>0 = Address does not need to be updated</li> </ul>                                                                                                                                                                                                                                                                  |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

| bit 0            | <ul> <li>BF: Buffer Full Status bit<br/><u>Receive (SPI and I<sup>2</sup>C modes):</u> <ol> <li>= Receive complete, SSP1BUF is full</li> <li>= Receive not complete, SSP1BUF is empty</li> </ol> </li> <li><u>Transmit (I<sup>2</sup>C mode only):</u> <ol> <li>= Data transmit in progress (does not include the <u>ACK</u> and Stop bits), SSP1BUF is full</li> <li>= Data transmit complete (does not include the <u>ACK</u> and Stop bits), SSP1BUF is empty</li> </ol> </li> </ul> |                                                                                                 |                                                                         |                                                   |                    |                      |           |  |

#### REGISTER 30-2: SSP1CON1: SSP CONTROL REGISTER 1 (CONTINUED)

- Note 1: In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSP1BUF register.

- 2: When enabled, these pins must be properly configured as input or output. Use SSPSSPPS, SSPCLKPPS, SSPDATPPS, and RxyPPS to select the pins.

- 3: When enabled, the SDA and SCL pins must be configured as inputs. Use SSPCLKPPS, SSPDATPPS, and RxyPPS to select the pins.

- 4: SSP1ADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- 5: SSP1ADD value of '0' is not supported. Use SSPM = 0000 instead.

### TABLE 34-19: 8-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

VDD = 3.0V, TA = 25°C

See Section 35.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

|               |      |                              |      | •       |       |       |          |

|---------------|------|------------------------------|------|---------|-------|-------|----------|

| Param.<br>No. | Sym. | Characteristics              | Min. | Тур.    | Max.  | Units | Comments |

| DAC01*        | Clsb | Step Size                    | —    | VDD/256 | _     | V     |          |

| DAC02*        | CACC | Absolute Accuracy            |      | _       | ± 1.5 | LSb   |          |

| DAC03*        | CR   | Unit Resistor Value (R)      | _    | 600     | _     | Ω     |          |

| DAC04*        | CST  | Settling Time <sup>(1)</sup> | —    | —       | 10    | μS    |          |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<7:0> transitions from ' $0 \times 00$ ' to ' $0 \times FF$ '.

## TABLE 34-20: 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

## Standard Operating Conditions (unless otherwise stated) $V_{DD} = 3.0V$ , TA = 25°C

See Section 35.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

| Sym. | Characteristics              | Min.                                                                                                                                | Тур.                                                                                                                                                                        | Max.                                                                                                                                                                                    | Units                                                                                                                                                                                                                                                                                        | Comments                                                                                                                    |

|------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| CLSB | Step Size                    | -                                                                                                                                   | VDD/32                                                                                                                                                                      | -                                                                                                                                                                                       | V                                                                                                                                                                                                                                                                                            |                                                                                                                             |

| CACC | Absolute Accuracy            | _                                                                                                                                   | —                                                                                                                                                                           | $\pm 0.5$                                                                                                                                                                               | LSb                                                                                                                                                                                                                                                                                          |                                                                                                                             |

| CR   | Unit Resistor Value (R)      | _                                                                                                                                   | 6000                                                                                                                                                                        | _                                                                                                                                                                                       | Ω                                                                                                                                                                                                                                                                                            |                                                                                                                             |

| CST  | Settling Time <sup>(1)</sup> | _                                                                                                                                   | —                                                                                                                                                                           | 10                                                                                                                                                                                      | μS                                                                                                                                                                                                                                                                                           |                                                                                                                             |

|      | CLSB<br>CACC<br>CR           | CLSB     Step Size       CACC     Absolute Accuracy       CR     Unit Resistor Value (R)       CST     Settling Time <sup>(1)</sup> | CLSB       Step Size       —         CACC       Absolute Accuracy       —         CR       Unit Resistor Value (R)       —         CST       Settling Time <sup>(1)</sup> — | CLSB     Step Size     —     VDD/32       CACC     Absolute Accuracy     —     —       CR     Unit Resistor Value (R)     —     6000       CST     Settling Time <sup>(1)</sup> —     — | CLSB         Step Size         —         VDD/32         —           CACC         Absolute Accuracy         —         —         ± 0.5           CR         Unit Resistor Value (R)         —         6000         —           CST         Settling Time <sup>(1)</sup> —         —         10 | CLSBStep Size—VDD/32—VCACCAbsolute Accuracy——± 0.5LSbCRUnit Resistor Value (R)—6000—ΩCSTSettling Time <sup>(1)</sup> ——10µs |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<7:0> transitions from ' $0 \times 00$ ' to ' $0 \times FF$ '.

## TABLE 34-21: ZERO-CROSS PIN SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |        |                            |      |      |      |       |          |

|----------------------------------------------------------------------------------|--------|----------------------------|------|------|------|-------|----------|

| Param.<br>No.                                                                    | Sym.   | Characteristics            | Min. | Тур. | Max. | Units | Comments |

| ZC01                                                                             | ZCPINV | Voltage on Zero-Cross Pin  |      | 0.75 | _    | V     |          |

| ZC02                                                                             | ZCSRC  | Source current             |      | 300  | _    | μA    |          |

| ZC03                                                                             | ZCSNK  | Sink current               | _    | 300  | _    | μA    |          |

| ZC04                                                                             | Zcisw  | Response Time Rising Edge  | _    | 1    | _    | μS    |          |

|                                                                                  |        | Response Time Falling Edge |      | 1    | _    | μS    |          |

| ZC05                                                                             | ZCOUT  | Response Time Rising Edge  | _    | 1    | —    | μS    |          |

|                                                                                  |        | Response Time Falling Edge | _    | 1    | _    | μS    |          |

These parameters are characterized but not tested.

# 35.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

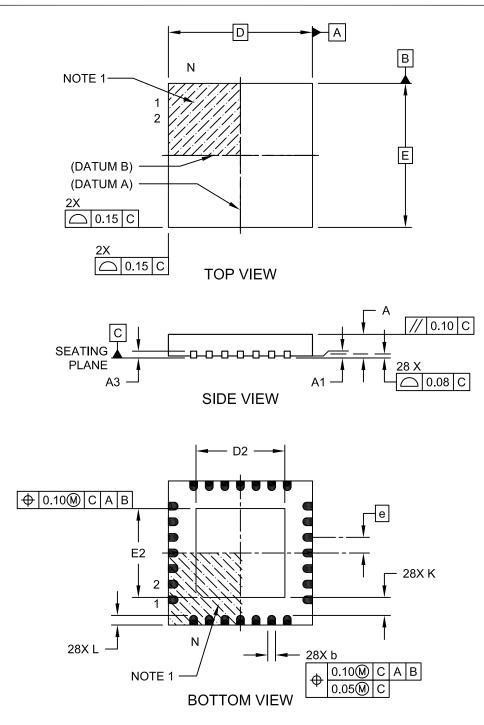

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2