Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

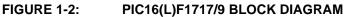

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1717-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1717/8/9

#### **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Enhanced Mid-Range CPU                                                    |     |

| 3.0  | Memory Organization                                                       |     |

| 4.0  | Device Configuration                                                      | 55  |

| 5.0  | Resets                                                                    | 60  |

| 6.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

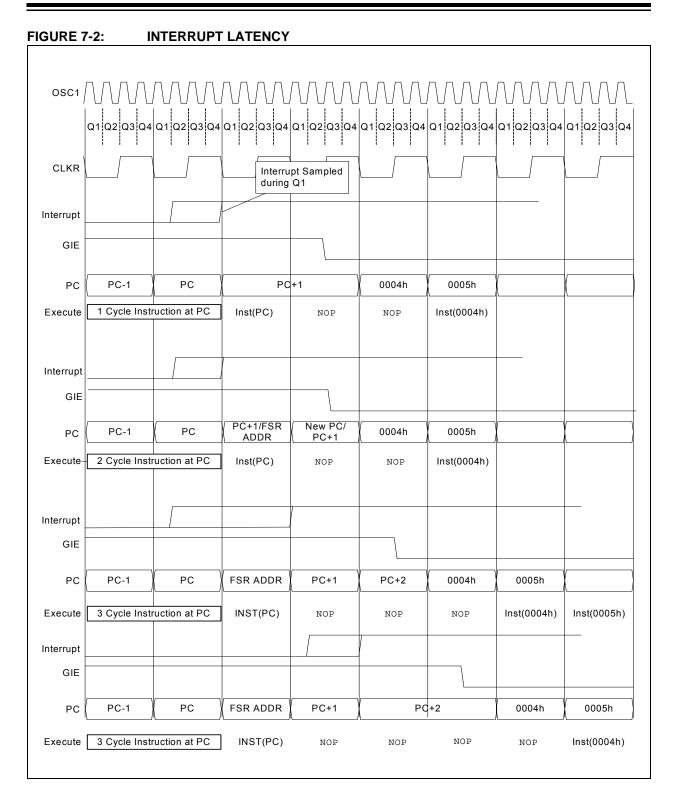

| 7.0  | Interrupts                                                                |     |

| 8.0  | Power-Down Mode (Sleep)                                                   |     |

| 9.0  | Watchdog Timer (WDT)                                                      | 102 |

| 10.0 | Flash Program Memory Control                                              | 106 |

| 11.0 |                                                                           |     |

| 12.0 |                                                                           | 150 |

| 13.0 | Interrupt-On-Change                                                       | 156 |

| 14.0 | Fixed Voltage Reference (FVR)                                             | 163 |

| 15.0 | Temperature Indicator Module                                              | 166 |

|      | Comparator Module                                                         |     |

| 17.0 | Pulse Width Modulation (PWM)                                              | 177 |

| 18.0 | Complementary Output Generator (COG) Module                               |     |

| 19.0 |                                                                           |     |

| 20.0 | Numerically Controlled Oscillator (NCO) Module                            | 233 |

| 21.0 | Analog-to-Digital Converter (ADC) Module                                  |     |

| 22.0 |                                                                           | 255 |

| 23.0 | 8-Bit Digital-to-Analog Converter (DAC1) Module                           | 258 |

|      | · · · · · · · · · · · · · · · · · · ·                                     |     |

| 25.0 | Zero-Cross Detection (ZCD) Module                                         |     |

| 26.0 | Timer0 Module                                                             |     |

| 27.0 | Timer1 Module with Gate Control                                           |     |

| 28.0 |                                                                           |     |

| 29.0 | Capture/Compare/PWM Modules                                               |     |

| 30.0 | Master Synchronous Serial Port (MSSP) Module                              |     |

| 31.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 351 |

| 32.0 | In-Circuit Serial Programming (ICSP™)                                     | 381 |

| 33.0 | Instruction Set Summary                                                   | 383 |

| 34.0 | Electrical Specifications                                                 | 397 |

| 35.0 | DC and AC Characteristics Graphs and Charts                               | 432 |

| 36.0 | Development Support                                                       | 454 |

| 37.0 | Packaging Information                                                     | 458 |

| Appe | endix A: Data Sheet Revision History                                      | 479 |

# PIC16(L)F1717/8/9

| Name                                            | Function | Input<br>Type | Output<br>Type | Description                                  |

|-------------------------------------------------|----------|---------------|----------------|----------------------------------------------|

| RB1/AN10/C1IN3-/C2IN3-/                         | RB1      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA2OUT                                         | AN10     | AN            | _              | ADC Channel 10 input.                        |

|                                                 | C1IN3-   | AN            | —              | Comparator C1 negative input.                |

|                                                 | C2IN3-   | AN            | —              | Comparator C2 negative input.                |

|                                                 | OPA2OUT  |               | AN             | Operational Amplifier 2 output.              |

| RB2/AN8/OPA2IN-                                 | RB2      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN8      | AN            | _              | ADC Channel 8 input.                         |

|                                                 | OPA2IN-  | AN            | —              | Operational Amplifier 2 inverting input.     |

| RB3/AN9/C1IN2-/C2IN2-/                          | RB3      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA2IN+                                         | AN9      | AN            | _              | ADC Channel 9 input.                         |

|                                                 | C1IN2-   | AN            | _              | Comparator C1 negative input.                |

|                                                 | C2IN2-   | AN            | _              | Comparator C2 negative input.                |

|                                                 | OPA2IN+  | AN            | _              | Operational Amplifier 2 non-inverting input. |

| RB4/AN11                                        | RB4      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN11     | AN            | _              | ADC Channel 11 input.                        |

| RB5/AN13/T1G <sup>(1)</sup>                     | RB5      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN13     | AN            |                | ADC Channel 13 input.                        |

|                                                 | T1G      | TTL/ST        |                | Timer1 gate input.                           |

| RB6/CLCIN2 <sup>(1)</sup> /ICSPCLK              | RB6      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | CLCIN2   | TTL/ST        |                | Configurable Logic Cell source input.        |

|                                                 | ICSPCLK  | ST            |                | Serial Programming Clock.                    |

| RB7/DAC1OUT2/DAC2OUT2/                          | RB7      | TTL/ST        | CMOS           | General purpose I/O.                         |

| CLCIN3 <sup>(1)</sup> /ICSPDAT                  | DAC1OUT2 | _             | AN             | Digital-to-Analog Converter output.          |

|                                                 | DAC2OUT2 | _             | AN             | Digital-to-Analog Converter output.          |

|                                                 | CLCIN3   | TTL/ST        |                | Configurable Logic Cell source input.        |

|                                                 | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                              |

| RC0/T1CKI <sup>(1)</sup> /SOSCO                 | RC0      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | T1CKI    | ST            |                | Timer1 clock input.                          |

|                                                 | SOSCO    | XTAL          | XTAL           | Secondary Oscillator Connection.             |

| RC1/SOSCI/CCP2 <sup>(1)</sup>                   | RC1      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | SOSCI    | XTAL          | XTAL           | Secondary Oscillator Connection.             |

|                                                 | CCP2     | TTL/ST        |                | Capture input.                               |

| RC2/AN14/CCP1 <sup>(1)</sup>                    | RC2      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN14     | AN            | _              | ADC Channel 14 input.                        |

|                                                 | CCP1     | TTL/ST        | _              | Capture input.                               |

| RC3/AN15/SCK <sup>(1)</sup> /SCL <sup>(1)</sup> | RC3      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN15     | AN            |                | ADC Channel 15 input.                        |

|                                                 | SCK      | TTL/ST        | —              | SPI clock input.                             |

|                                                 | 0.01     | 120           |                |                                              |

OD **Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ TTL = TTL compatible input ST

l<sup>2</sup>C

SCL

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers. 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

I<sup>2</sup>C clock.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

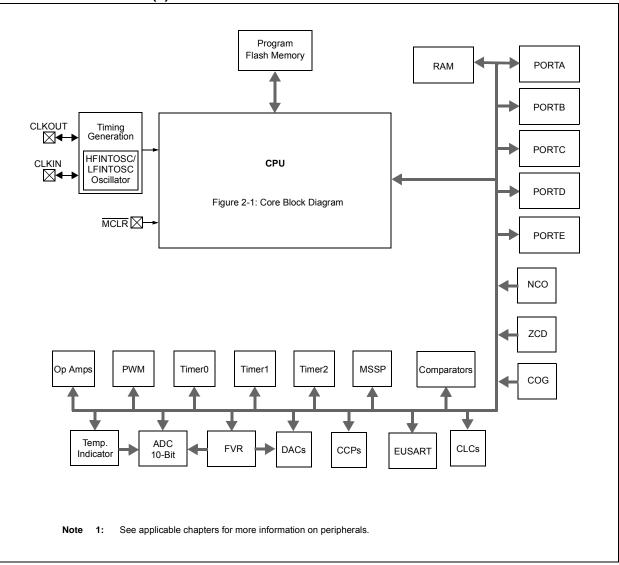

#### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

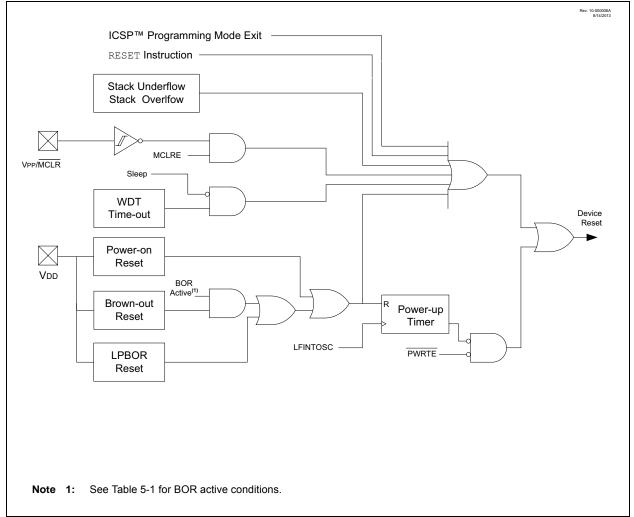

# 5.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# PIC16(L)F1717/8/9

| r          |         |        |        |        |        |         |        |        |                     |

|------------|---------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 90                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 270                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 91                  |

| PIE2       | OSFIE   | C2IE   | C1IE   | _      | BCL1IE | TMR6IE  | TMR4IE | CCP2IE | 92                  |

| PIE3       | _       | NCOIE  | COGIE  | ZCDIE  | CLC4IE | CLC3IE  | CLC2IE | CLC1IE | 93                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 94                  |

| PIR2       | OSFIF   | C2IF   | C1IF   |        | BCL1IF | TMR6IF  | TMR4IF | CCP2IF | 95                  |

| PIR3       | _       | NCOIF  | COGIF  | ZCDIF  | CLC4IF | CLC3IF  | CLC2IF | CLC1IF | 96                  |

| TABLE 7-1: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

#### 9.3 Time-out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

#### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See STATUS Register (Register 3-1) for more information.

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |  |

|----------------------------------------------------------|------------------------------|--|

| WDTE<1:0> = 00                                           |                              |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |

| CLRWDT Command                                           | Cleared                      |  |

| Oscillator Fail Detected                                 |                              |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |

| U-0                                   | U-0   | U-0             | U-0  | R/W-1/1      | R/W-1/1              | R/W-1/1              | R/W-1/1              |  |

|---------------------------------------|-------|-----------------|------|--------------|----------------------|----------------------|----------------------|--|

| —                                     | _     | _               | _    | WPUE3        | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> |  |

| bit 7 bit 0                           |       |                 |      |              |                      |                      |                      |  |

|                                       |       |                 |      |              |                      |                      |                      |  |

| Legend:                               |       |                 |      |              |                      |                      |                      |  |

| R = Readable                          | bit   | W = Writable    | bit  | U = Unimplei | mented bit, read     | as '0'               |                      |  |

| u = Bit is unch                       | anged | x = Bit is unkr | nown | -n/n = Value | at POR and BO        | R/Value at all c     | ther Resets          |  |

| '1' = Bit is set '0' = Bit is cleared |       |                 |      |              |                      |                      |                      |  |

#### **REGISTER 11-37: WPUE: WEAK PULL-UP PORTE REGISTER**<sup>(1,2)</sup>

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WPUE<3:0>: Weak Pull-up Register bits 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- 3: PIC16(L)F1717/9 only.

#### REGISTER 11-38: ODCONE: PORTE OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ODE2    | ODE1    | ODE0    |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ODE<2:0>:** PORTE Open-Drain Enable bits For RE<2:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** PIC16(L)F1717/9 only.

### 25.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The ZCDxOUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The ZCDxOUT bit is affected by the polarity bit.

## 25.3 ZCD Logic Polarity

The ZCDxPOL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the ZCDxPOL bit is set, a ZCDxOUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The ZCDxPOL bit affects the ZCD interrupts. See **Section 25.4 "ZCD Interrupts"**.

### 25.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The ZCDxINTP enables rising edge interrupts and the ZCDxINTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- ZCDIE bit of the PIE3 register

- ZCDxINTP bit of the ZCDxCON register (for a rising edge detection)

- ZCDxINTN bit of the ZCDxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

Changing the ZCDxPOL bit will cause an interrupt, regardless of the level of the ZCDxEN bit.

The ZCDIF bit of the PIR3 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

### 25.5 Correcting for ZCPINV Offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms other than square waves this voltage offset from zero causes the zero-cross event to occur either too early or too late. When the waveform is varying relative to Vss then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 25-2.

#### EQUATION 25-2: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$T_{offset} = \frac{\operatorname{asin}\left(\frac{Z_{cpinv}}{V_{peak}}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$T_{offset} = \frac{\operatorname{asin}\left(\frac{VDD - Z_{cpinv}}{V_{peak}}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the ZCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 25-3.

### EQUATION 25-3: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{pullup} = \frac{R_{series}(V_{pullup} - Z_{cpinv})}{Z_{cpinv}}$$

When External Signal is relative to VDD:

$$R_{pulldown} = \frac{R_{series}(Z_{cpinv})}{(VDD - Z_{cpinv})}$$

The pull-up and pull-down resistor values are significantly affected by small variations of ZCPINV. Measuring ZCPINV can be difficult, especially when the waveform is relative to VDD. However, by combining Equation 25-2 and Equation 25-3 the resistor value

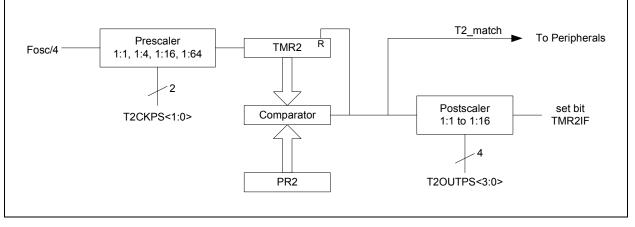

## 28.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- · Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2, respectively

- Optional use as the shift clock for the MSSP module

See Figure 28-1 for a block diagram of Timer2.

Three identical Timer2 modules are implemented on this device. To maintain consistency with earlier devices, the timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6.

### 29.4 Register Definitions: CCP Control

#### U-0 U-0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 DCxB<1:0> CCPxM<3:0> \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other Reset u = Bit is unchanged x = Bit is unknown '1' = Bit is set '0' = Bit is cleared bit 7-6 Unimplemented: Read as '0' bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits Capture mode: Unused Compare mode: Unused PWM mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. bit 3-0 CCPxM<3:0>: CCPx Mode Select bits 11xx = PWM mode 1011 = Compare mode: Auto-conversion Trigger (sets CCPxIF bit), starts ADC conversion if TRIGSEL = CCPx (see Register 21-3) 1010 = Compare mode: generate software interrupt only 1001 = Compare mode: clear output on compare match (set CCPxIF) 1000 = Compare mode: set output on compare match (set CCPxIF) 0111 = Capture mode: every 16th rising edge 0110 = Capture mode: every 4th rising edge 0101 = Capture mode: every rising edge 0100 = Capture mode: every falling edge 0011 = Reserved 0010 = Compare mode: toggle output on match 0001 = Reserved 0000 = Capture/Compare/PWM off (resets CCPx module)

#### **REGISTER 29-1: CCPxCON: CCPx CONTROL REGISTER**

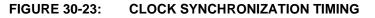

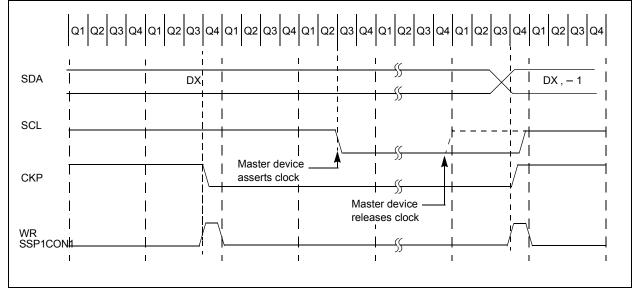

# 30.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 30-23).

## 30.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSP1CON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSP1IF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSP1BUF register to initiate transmission before the Start condition is complete. In this case, the SSP1BUF will not be written to and the WCOL bit will be set, indicating that a write to the SSP1BUF did not occur

- 2: Master mode suspends Start/Stop detection when sending the Start/Stop condition by means of the SEN/PEN control bits. The SSPxIF bit is set at the end of the Start/Stop generation when hardware clears the control bit.

#### 30.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 30.7** "**Baud Rate Generator**" for more detail.

## 30.8 Register Definitions: MSSP Control

| REGISTER 3       |                                                                                                                                      |                                                                                                    |                                                                          |                                                  |                                          | D 0/0           | D 0/0     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|-----------------|-----------|

| R/W-0/0          | R/W-0/0                                                                                                                              | R-0/0                                                                                              | R-0/0                                                                    | R-0/0                                            | R-0/0                                    | R-0/0           | R-0/0     |

| SMP              | CKE                                                                                                                                  | D/A                                                                                                | Р                                                                        | S                                                | R/W                                      | UA              | BF        |

| bit 7            |                                                                                                                                      |                                                                                                    |                                                                          |                                                  |                                          |                 | bit (     |

| Legend:          |                                                                                                                                      |                                                                                                    |                                                                          |                                                  |                                          |                 |           |

| R = Readable b   | pit                                                                                                                                  | W = Writable b                                                                                     | oit                                                                      | U = Unimplem                                     | nented bit, read a                       | as '0'          |           |

| u = Bit is uncha |                                                                                                                                      | x = Bit is unkn                                                                                    |                                                                          |                                                  | t POR and BOR                            |                 | er Resets |

| '1' = Bit is set | 0                                                                                                                                    | '0' = Bit is clea                                                                                  | ared                                                                     |                                                  |                                          |                 |           |

|                  |                                                                                                                                      |                                                                                                    |                                                                          |                                                  |                                          |                 |           |

| bit 7            | $\frac{SPI Master mo}{1 = Input data}$ $0 = Input data$ $\frac{SPI Slave moo}{SMP must be}$ $\frac{In I^2C Master o}{1 = Slew rate}$ | sampled at end<br>sampled at mid<br>de:<br>cleared when S<br>or Slave mode:<br>control disabled    | l of data outpu<br>ldle of data ou<br>PI is used in \$<br>d for Standard | tput time<br>Slave mode                          | 00 kHz and 1 M<br>Hz)                    | Hz)             |           |

| bit 6            | <b>CKE:</b> SPI Cloc<br>In <u>SPI Master</u><br>1 = Transmit o<br>0 = Transmit o<br>In $I^2C^{\text{TM}}$ mode<br>1 = Enable inp     | ck Edge Select<br>or Slave mode:<br>occurs on transit<br>occurs on transit<br>only:                | bit (SPI mode<br>tion from activ<br>tion from Idle t<br>thresholds are   | only)<br>e to Idle clock st<br>o active clock st | ate                                      | ation           |           |

| bit 5            | 1 = Indicates t                                                                                                                      |                                                                                                    | e received or t                                                          | ransmitted was a ransmitted was a                |                                          |                 |           |

| bit 4            | 1 = Indicates t                                                                                                                      |                                                                                                    | as been detec                                                            | MSSP module<br>ted last (this bit                | is disabled, SSP<br>is '0' on Reset)     | EN is cleared.) |           |

| bit 3            | 1 = Indicates t                                                                                                                      |                                                                                                    | as been detec                                                            | MSSP module<br>ted last (this bit                | is disabled, SSP<br>is '0' on Reset)     | EN is cleared.) |           |

| bit 2            | This bit holds t<br>match to the n<br>$ln l^2C$ Slave m<br>1 = Read<br>0 = Write<br>$ln l^2C$ Master<br>1 = Transmit<br>0 = Transmit | ext Start bit, Sto<br><u>iode:</u><br><u>mode:</u><br>is in progress<br>is not in progress         | mation follow <u>i</u><br>op bit, or not A                               | ng the last addre<br>CK bit.                     | ess match. This b<br>EN will indicate if | ·               |           |

| bit 1            | <b>UA:</b> Update A<br>1 = Indicates t                                                                                               | ddress bit (10-b                                                                                   | it I <sup>2</sup> C mode or<br>eds to update                             | ıly)                                             | he SSP1ADD re                            |                 |           |

| bit 0            | 1 = Receive co<br>0 = Receive no<br><u>Transmit (I<sup>2</sup>C)</u><br>1 = Data trans                                               | and I <sup>2</sup> C modes)<br>omplete, SSP1E<br>ot complete, SS<br>mode only):<br>mit in progress | BUF is full<br>P1BUF is em<br>(does not incl                             | ude th <u>e ACK</u> an                           | d Stop bits), SSF<br>Stop bits), SSP1    |                 |           |

# 34.0 ELECTRICAL SPECIFICATIONS

## 34.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                 | 40°C to +125°C       |

|------------------------------------------------|----------------------|

| Storage temperature                            |                      |

| Voltage on pins with respect to Vss            |                      |

| on VDD pin                                     |                      |

| PIC16F1717/8/9                                 | 0.3V to +6.5V        |

| PIC16LF1717/8/9                                | -0.3V to +4.0V       |

| on MCLR pin                                    | -0.3V to +9.0V       |

| on all other pins                              | 0.3V to (VDD + 0.3V) |

| Maximum current                                |                      |

| on Vss pin <sup>(1)</sup>                      |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                   | 340 mA               |

| $-40^{\circ}C \leq T_A \leq +125^{\circ}C$     | 140 mA               |

| on VDD pin <sup>(1)</sup> PIC16(L)F1718 only   |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                   | 250 mA               |

| $-40^{\circ}C \leq TA \leq +125^{\circ}C$      | 85 mA                |

| on VDD pin <sup>(1)</sup> PIC16(L)F1717/9 only |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                   | 350 mA               |

| -40°C $\leq$ Ta $\leq$ +125°C                  | 120 mA               |

| Sunk by any standard I/O pin                   | 50 mA                |

| Sourced by any standard I/O pin                | 50 mA                |

| Sourced by any Op Amp output pin               | 100 mA               |

| Clamp current, IK (VPIN < 0 or VPIN > VDD)     | ±20 mA               |

| Total power dissipation <sup>(2)</sup>         |                      |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 34-6 to calculate device specifications.

2: Power dissipation is calculated as follows:

Pdis =  $VDD^* \{Idd - \Sigma Ioh\} + \Sigma \{VDD - Voh\}^* Ioh\} + \Sigma (Vol^* Iol).$

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

## 34.2 Standard Operating Conditions

| The standard operating co | conditions for any device are defined as:     |        |

|---------------------------|-----------------------------------------------|--------|

| Operating Voltage:        | $VDDMIN \leq VDD \leq VDDMAX$                 |        |

| Operating Temperature:    |                                               |        |

| VDD — Operating Supply    | bly Voltage <sup>(1)</sup>                    |        |

| PIC16LF1717/8/9           | )                                             |        |

| Vddmin (F                 | (Fosc $\leq$ 16 MHz)                          | +1.8V  |

| Vddmin (F                 | (Fosc > 16 MHz)                               | +2.5V  |

| VDDMAX                    |                                               | +3.6V  |

| PIC16F1717/8/9            |                                               |        |

| Vddmin (F                 | (Fosc $\leq$ 16 MHz)                          | +2.3V  |

| Vddmin (>                 | (> 16 MHz)                                    | +2.5V  |

| VDDMAX                    |                                               | +5.5V  |

| TA — Operating Ambien     | nt Temperature Range                          |        |

| Industrial Temperat       | ature                                         |        |

| TA_MIN                    |                                               | 40°C   |

| Та_мах                    |                                               | +85°C  |

| Extended Tempera          | ature                                         |        |

| TA_MIN                    |                                               | 40°C   |

| Та_мах                    |                                               | +125°C |

| Note 1: See Paramete      | ter D001, DS Characteristics: Supply Voltage. |        |

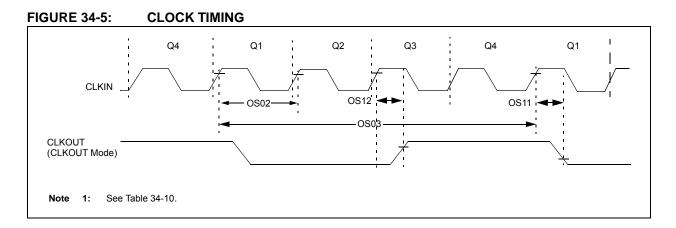

#### TABLE 34-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No. | Sym.          | Characteristic                              | Min. | Тур.†  | Max.     | Units | Conditions                |

|---------------|---------------|---------------------------------------------|------|--------|----------|-------|---------------------------|

| OS01          | Fosc          | External CLKIN Frequency <sup>(1)</sup>     | DC   |        | 0.5      | MHz   | External Clock (ECL)      |

|               |               |                                             | DC   |        | 4        | MHz   | External Clock (ECM)      |

|               |               |                                             | DC   |        | 20       | MHz   | External Clock (ECH)      |

|               |               | Oscillator Frequency <sup>(1)</sup>         | —    | 32.768 | _        | kHz   | LP Oscillator             |

|               |               |                                             | 0.1  | _      | 4        | MHz   | XT Oscillator             |

|               |               |                                             | 1    |        | 4        | MHz   | HS Oscillator             |

|               |               |                                             | 1    | _      | 20       | MHz   | HS Oscillator, VDD > 2.7V |

|               |               |                                             | DC   | _      | 4        | MHz   | EXTRC, VDD > 2.0V         |

| OS02          | Tosc          | External CLKIN Period <sup>(1)</sup>        | 27   |        | ×        | μS    | LP Oscillator             |

|               |               |                                             | 250  |        | $\infty$ | ns    | XT Oscillator             |

|               |               |                                             | 50   | —      | $\infty$ | ns    | HS Oscillator             |

|               |               |                                             | 50   |        | $\infty$ | ns    | External Clock (EC)       |

|               |               | Oscillator Period <sup>(1)</sup>            | —    | 30.5   | —        | μS    | LP Oscillator             |

|               |               |                                             | 250  | —      | 10,000   | ns    | XT Oscillator             |

|               |               |                                             | 50   | —      | 1,000    | ns    | HS Oscillator             |

|               |               |                                             | 250  | —      | —        | ns    | EXTRC                     |

| OS03          | Тсү           | Instruction Cycle Time <sup>(1)</sup>       | 125  | TCY    | DC       | ns    | Tcy = 4/Fosc              |

| OS04*         | TosH,<br>TosL | External CLKIN High,                        | 2    | _      | —        | μS    | LP Oscillator             |

|               |               | External CLKIN Low                          | 100  | —      | —        | ns    | XT Oscillator             |

|               |               |                                             | 20   | —      | —        | ns    | HS Oscillator             |

| OS05*         | TosR,<br>TosF | External CLKIN Rise,<br>External CLKIN Fall | 0    |        | ×        | ns    | LP Oscillator             |

|               |               |                                             | 0    | —      | $\infty$ | ns    | XT Oscillator             |

|               |               |                                             | 0    | —      | $\infty$ | ns    | HS Oscillator             |

#### Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

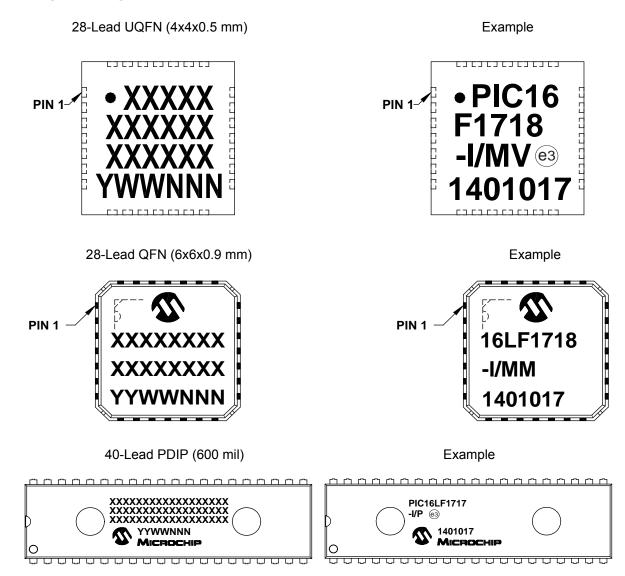

#### **Package Marking Information (Continued)**

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | Ť                                           | - X<br> <br>Reel Temperatur<br>Range                                                                                                                   | /XX<br> <br>e Package      | XXX<br> <br>Pattern | a)   | Indus<br>PDIP | 6LF1717- I/P<br>trial temperature<br>package                                                                                                                                                                                                                                                                                                                    |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F17                                    | 717, PIC16LF1717,<br>718, PIC16LF1718<br>719, PIC16LF1719                                                                                              |                            |                     | b)   | Exten         | 6F1718- E/SS<br>Ided temperature,<br>P package                                                                                                                                                                                                                                                                                                                  |

| Tape and Reel<br>Option: | Blank =<br>T =                              | Standard packaging<br>Tape and Reel <sup>(1)</sup>                                                                                                     | (tube or tray)             |                     |      |               |                                                                                                                                                                                                                                                                                                                                                                 |

| Temperature<br>Range:    |                                             | -40°C to +85°C<br>-40°C to +125°C                                                                                                                      | (Industrial)<br>(Extended) |                     |      |               |                                                                                                                                                                                                                                                                                                                                                                 |

| Package: <sup>(2)</sup>  | MV =<br>MM =<br>P =<br>PT =<br>SO =<br>SP = | UQFN, 28-lead 4x4<br>UQFN, 40-lead 5x5<br>QFN-S, 28-lead 6xt<br>PDIP, 40-lead<br>TQFP, 44-lead 10x<br>SOIC, 28-lead<br>SPDIP, 28-lead<br>SSOP, 28-lead | 5x0.5mm<br>6x0.9mm         |                     | Note | e 1:<br>2:    | Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option.<br>Small form-factor packaging options may<br>be available. Please check |

| Pattern:                 | QTP, SQT<br>(blank oth                      | FP, Code or Special F<br>nerwise)                                                                                                                      | Requirements               |                     |      |               | www.microchip.com/packaging for<br>small-form factor package availability, or<br>contact your local Sales Office.                                                                                                                                                                                                                                               |