Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1717t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, TO is set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

#### TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

## 7.6 Register Definitions: Interrupt Control

| R/W-0/0          | R/W-0/0                                                                                                                          | R/W-0/0                                                    | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0          | R-0/0                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------------------|------------------|----------------------|

| GIE              | PEIE                                                                                                                             | TMR0IE                                                     | INTE            | IOCIE            | TMR0IF           | INTF             | IOCIF <sup>(1)</sup> |

| bit 7            |                                                                                                                                  |                                                            |                 |                  |                  | ·                | bit 0                |

| Legend:          |                                                                                                                                  |                                                            |                 |                  |                  |                  |                      |

| R = Readable     | e bit                                                                                                                            | W = Writable                                               | bit             | U = Unimplei     | mented bit, read | l as '0'         |                      |

| u = Bit is uncl  | nanged                                                                                                                           | x = Bit is unkr                                            | nown            | -n/n = Value     | at POR and BO    | R/Value at all o | ther Resets          |

| '1' = Bit is set |                                                                                                                                  | '0' = Bit is cle                                           | ared            |                  |                  |                  |                      |

| bit 7            |                                                                                                                                  | nterrupt Enable<br>all active interru<br>all interrupts    |                 |                  |                  |                  |                      |

| bit 6            | 1 = Enables a                                                                                                                    | eral Interrupt E<br>all active periph<br>all peripheral ir | eral interrupts | 3                |                  |                  |                      |

| bit 5            | 1 = Enables t                                                                                                                    | er0 Overflow Ir<br>the Timer0 inter<br>the Timer0 inte     | rupt            | e bit            |                  |                  |                      |

| bit 4            | 1 = Enables t                                                                                                                    | ternal Interrupt<br>the INT externa<br>the INT externa     | l interrupt     |                  |                  |                  |                      |

| bit 3            |                                                                                                                                  |                                                            |                 |                  |                  |                  |                      |

| bit 2            | it 2 <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow |                                                            |                 |                  |                  |                  |                      |

| bit 1            | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur |                                                            |                 |                  |                  |                  |                      |

| bit 0            |                                                                                                                                  |                                                            |                 |                  |                  |                  |                      |

| Note 1. Th       | e IOCIE Elag bit                                                                                                                 | t is read-only a                                           | nd cleared wh   | en all the inter | runt-on-change   | flags in the IO  | VE registers         |

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the interrupt-on-change flags in the IOCxF registers have been cleared by software.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF                       | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL    | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary                                                                                                                                                                                                                                              |

|----------------------|-------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | MOVWF<br>MOVF<br>MOVWF<br>BCF                         | PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS   | ; Load upper 6 bits of erase address boundary<br>; Not configuration space                                                                                                                                                                                                                                                                               |

|                      | BSF<br>BSF                                            | PMCON1, FREE<br>PMCON1, WREN                 | ; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                                                          |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                            | PMCON1,WREN<br>INTCON,GIE                    | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                  |

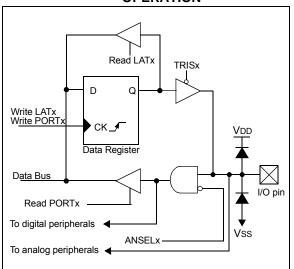

## 11.0 I/O PORTS

Each port has six standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- INLVLx (input level control)

- ODCONx registers (open-drain)

- SLRCONx registers (slew rate)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

TABLE 11-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE |

|---------------|-------|-------|-------|-------|-------|

| PIC16(L)F1717 | ٠     | ٠     | ٠     | ٠     | •     |

| PIC16(L)F1718 | •     | ٠     | ٠     |       | •     |

| PIC16(L)F1719 | •     | •     | ٠     | ٠     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

#### FIGURE 11-1: GENERIC I/O PORT OPERATION

## 11.1 PORTA Registers

## 11.1.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize PORTA.

Reading the PORTA register (Register 11-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

## 11.1.2 DIRECTION CONTROL

The TRISA register (Register 11-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (l<sup>2</sup>C)

**Note:** The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible and are the only pins on the device with this compatibility.

## 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

## EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

| ; suspend interrupts                     |

|------------------------------------------|

| bcf INTCON,GIE                           |

| ; BANKSEL PPSLOCK ; set bank             |

| ; required sequence, next 5 instructions |

| movlw 0x55                               |

| movwf PPSLOCK                            |

| movlw 0xAA                               |

| movwf PPSLOCK                            |

| ; Set PPSLOCKED bit to disable writes or |

| ; Clear PPSLOCKED bit to enable writes   |

| bsf PPSLOCK, PPSLOCKED                   |

| ; restore interrupts                     |

| bsf INTCON,GIE                           |

| DSI INICON, GIE                          |

## 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

## 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in pin allocation Table 1.

## 13.0 INTERRUPT-ON-CHANGE

All pins on all ports can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

## 13.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

### 13.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCxF bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the affected IOCxF register will be updated prior to the first instruction executed out of Sleep.

| R/W-0/0                                 | R/W-0/0 | R/W-0/0 | R/W-0/0                            | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|---------|---------|------------------------------------|-------------------------------------------------------|---------|---------|---------|

| IOCBP7                                  | IOCBP6  | IOCBP5  | IOCBP4                             | IOCBP3                                                | IOCBP2  | IOCBP1  | IOCBP0  |

| bit 7                                   |         |         |                                    |                                                       |         | bit 0   |         |

|                                         |         |         |                                    |                                                       |         |         |         |

| Legend:                                 |         |         |                                    |                                                       |         |         |         |

| R = Readable bit W = Writable bit       |         | bit     | U = Unimplemented bit, read as '0' |                                                       |         |         |         |

| u = Bit is unchanged x = Bit is unknown |         |         | nown                               | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |

#### REGISTER 13-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

bit 7-0 **IOCBP<7:0>:** Interrupt-on-Change PORTB Positive Edge Enable bits

'0' = Bit is cleared

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

1' = Bit is set

- **IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      | •          |            | •          |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

- IOCBF<7:0>: Interrupt-on-Change PORTB Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

### 19.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 19-1).

- Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

## 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## 19.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

## 19.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

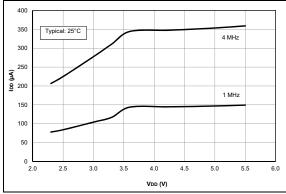

## 19.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### REGISTER 19-11: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | _   | MCL4OUT | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'         |

|---------|------------------------------------|

| bit 3   | MCL4OUT: Mirror copy of LC4OUT bit |

| bit 2   | MLC3OUT: Mirror copy of LC3OUT bit |

| bit 1   | MLC2OUT: Mirror copy of LC2OUT bit |

|         |                                    |

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

### TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name                  | Bit7     | Bit6     | Bit5     | Bit4     | Blt3     | Bit2        | Bit1       | Bit0     | Register<br>on Page |

|-----------------------|----------|----------|----------|----------|----------|-------------|------------|----------|---------------------|

| ANSELA                | _        |          | ANSA5    | ANSA4    | ANSA3    | ANSA2       | ANSA1      | ANSA0    | 125                 |

| ANSELB                | _        | _        | ANSB5    | ANSB4    | ANSB3    | ANSB2       | ANSB1      | ANSB0    | 131                 |

| ANSELC                | ANSC7    | ANSC6    | ANSC5    | ANSC4    | ANSC3    | ANSC2       | —          | —        | 136                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6    | ANSD5    | ANSD4    | ANSD3    | ANSD2       | ANSD1      | ANSD0    | 141                 |

| CLC1CON               | LC1EN    | _        | LC10UT   | LC1INTP  | LC1INTN  | L           | C1MODE<2:0 | )>       | 224                 |

| CLC2CON               | LC2EN    | -        | LC2OUT   | LC2INTP  | LC2INTN  | L           | C2MODE<2:0 | )>       | 224                 |

| CLC3CON               | LC3EN    | _        | LC3OUT   | LC3INTP  | LC3INTN  | L           | C3MODE<2:0 | )>       | 224                 |

| CLCDATA               | _        |          | _        |          | MCL4OUT  | MLC3OUT     | MLC2OUT    | MLC1OUT  | 231                 |

| CLC1GLS0              | LC1G1D4T | LC1G1D4N | LC1G1D3T | LC1G1D3N | LC1G1D2T | LC1G1D2N    | LC1G1D1T   | LC1G1D1N | 227                 |

| CLC1GLS1              | LC1G2D4T | LC1G2D4N | LC1G2D3T | LC1G2D3N | LC1G2D2T | LC1G2D2N    | LC1G2D1T   | LC1G2D1N | 228                 |

| CLC1GLS2              | LC1G3D4T | LC1G3D4N | LC1G3D3T | LC1G3D3N | LC1G3D2T | LC1G3D2N    | LC1G3D1T   | LC1G3D1N | 229                 |

| CLC1GLS3              | LC1G4D4T | LC1G4D4N | LC1G4D3T | LC1G4D3N | LC1G4D2T | LC1G4D2N    | LC1G4D1T   | LC1G4D1N | 230                 |

| CLC1POL               | LC1POL   | _        | _        | _        | LC1G4POL | LC1G3POL    | LC1G2POL   | LC1G1POL | 225                 |

| CLC1SEL0              | —        |          | _        |          |          | LC1D1S<4:0> | ,          |          | 225                 |

| CLC1SEL1              | —        |          |          |          |          | LC1D2S<4:0> |            |          | 226                 |

| CLC1SEL2              | —        |          | -        |          |          | LC1D3S<4:0> |            |          | 226                 |

| CLC1SEL3              | —        | -        | _        |          |          | LC1D4S<4:0> | •          |          | 226                 |

| CLC2GLS0              | LC2G1D4T | LC2G1D4N | LC2G1D3T | LC2G1D3N | LC2G1D2T | LC2G1D2N    | LC2G1D1T   | LC2G1D1N | 227                 |

| CLC2GLS1              | LC2G2D4T | LC2G2D4N | LC2G2D3T | LC2G2D3N | LC2G2D2T | LC2G2D2N    | LC2G2D1T   | LC2G2D1N | 228                 |

| CLC2GLS2              | LC2G3D4T | LC2G3D4N | LC2G3D3T | LC2G3D3N | LC2G3D2T | LC2G3D2N    | LC2G3D1T   | LC2G3D1N | 229                 |

| CLC2GLS3              | LC2G4D4T | LC2G4D4N | LC2G4D3T | LC2G4D3N | LC2G4D2T | LC2G4D2N    | LC2G4D1T   | LC2G4D1N | 230                 |

| CLC2POL               | LC2POL   | _        | _        |          | LC2G4POL | LC2G3POL    | LC2G2POL   | LC2G1POL | 225                 |

| CLC2SEL0              | —        | _        | —        |          |          | LC2D1S<4:0> | ,          |          | 225                 |

| CLC2SEL1              | —        | —        | —        |          |          | LC2D2S<4:0> | ,          |          | 226                 |

| CLC2SEL2              | _        | _        | _        |          |          | LC2D3S<4:0> | •          |          | 226                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for CLC module.

**Note 1:** PIC16(L)F1717/9 only.

## 22.3 Register Definitions: Op Amp Control

| R/W-0/0<br>OPAxSP                                                                                                                                                                  | U-0<br>—<br>W = Writable<br>x = Bit is unkn                                                          | R/W-0/0<br>OPAxUG<br>bit                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                            | U-0<br>—                                                                                                                                                                                                                   | R/W-0/0<br>OPAxC                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0/0<br>H<1:0><br>bit 0                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                    |                                                                                                      |                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                          | OPAxC                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ed                                                                                                                                                                                 |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        | bit C                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ed                                                                                                                                                                                 |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ed                                                                                                                                                                                 |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ed                                                                                                                                                                                 |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ed                                                                                                                                                                                 | x = Bit is unkn                                                                                      |                                                                                                                                                                                                                            | U = Unimpler                                                                                                                                                                                                                                                                                                   | mented bit, read                                                                                                                                                                                                           | as '0'                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                    |                                                                                                      | nown                                                                                                                                                                                                                       | -n/n = Value a                                                                                                                                                                                                                                                                                                 | at POR and BOI                                                                                                                                                                                                             | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                    | '0' = Bit is clea                                                                                    | ared                                                                                                                                                                                                                       | q = Value dep                                                                                                                                                                                                                                                                                                  | pends on condit                                                                                                                                                                                                            | ion                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                    |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PAxEN: Op                                                                                                                                                                          | Amp Enable b                                                                                         | it                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Op amp is                                                                                                                                                                          |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                    | s disabled and                                                                                       |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •                                                                                                                                                                                  | Amp Speed/Po                                                                                         |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                    | perates in high<br>. Do not use.                                                                     | GBWP mod                                                                                                                                                                                                                   | e                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| implement                                                                                                                                                                          | ted: Read as '                                                                                       | כ'                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>AxUG:</b> Op                                                                                                                                                                    | Amp Unity Ga                                                                                         | in Select bit                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>1 = OPA output is connected to inverting input. OPAxIN- pin is available for general purpose I/O.</li> <li>0 = Inverting input is connected to the OPAxIN- pin</li> </ul> |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Unimplemented: Read as '0'                                                                                                                                                         |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>OPAxCH&lt;1:0&gt;:</b> Non-inverting Channel Selection bits                                                                                                                     |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| = Non-inve<br>= Non-inve                                                                                                                                                           | erting input con<br>erting input con                                                                 | nects to DAC<br>nects to DAC                                                                                                                                                                                               | 1_output<br>2_output                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |