Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1717t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

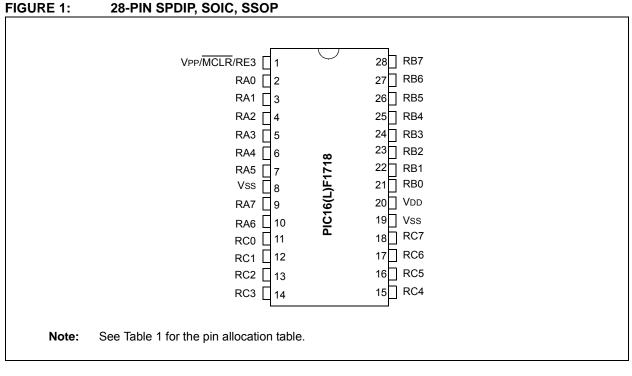

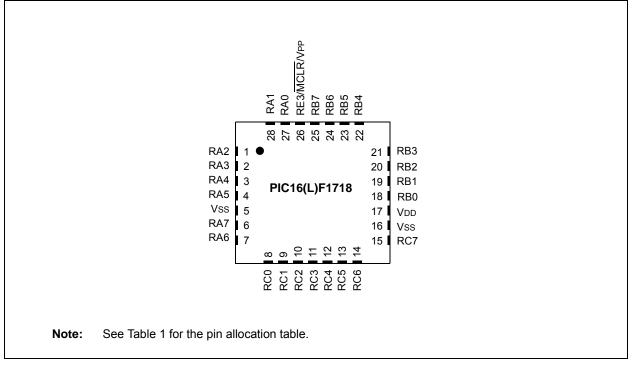

# **Pin Diagrams**

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1717/8/9 devices are described within this data sheet. They are available in the following package configurations:

- 28-pin SPDIP, SSOP, SOIC, QFN and UQFN

- 40-pin PDIP and UQFN

- 44-pin TQFP

Figure 1-1 and Figure 1-2 show block diagrams of the PIC16(L)F1717/8/9 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

## TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                        |                | PIC16(L)F1717 | PIC16(L)F1718 | PIC16(L)F1719                         |

|---------------------------------------------------|----------------|---------------|---------------|---------------------------------------|

| Analog-to-Digital Conve                           | rter (ADC)     | ٠             | ٠             | •                                     |

| Fixed Voltage Reference                           | e (FVR)        | ٠             | ٠             | •                                     |

| Zero-Cross Detection (Z                           | ZCD)           | ٠             | •             | •                                     |

| Temperature Indicator                             |                | ٠             | ٠             | •                                     |

| Complementary Output                              | Generator (C   | OG)           |               |                                       |

|                                                   | COG            | •             | ٠             | •                                     |

| Numerically Controlled                            | Oscillator (NC | O)            |               |                                       |

|                                                   | •              | ٠             | •             |                                       |

| Digital-to-Analog Conve                           | rter (DAC)     | -             |               |                                       |

|                                                   | •              | ٠             | •             |                                       |

|                                                   | DAC2           | •             | ٠             | •                                     |

| Capture/Compare/PWM                               | ) Mod          | ules          |               |                                       |

| · · ·                                             | CCP1           | •             | •             | •                                     |

|                                                   | CCP2           | •             | ٠             | •                                     |

| Comparators                                       |                |               |               |                                       |

|                                                   | C1             | •             | ٠             | •                                     |

|                                                   | C2             | •             | ٠             | •                                     |

| Configurable Logic Cell                           | (CLC)          |               |               |                                       |

|                                                   | CLC1           | •             | •             | •                                     |

|                                                   | CLC2           | •             | ٠             | •                                     |

|                                                   | CLC3           | •             | ٠             | •                                     |

|                                                   | CLC4           | •             | ٠             | •                                     |

| Enhanced Universal Syn<br>Receiver/Transmitter (E |                | ynchr         | onous         | 3                                     |

|                                                   | EUSART         | ٠             | ٠             | •                                     |

| Master Synchronous Se                             | erial Ports    |               |               |                                       |

|                                                   | MSSP           | •             | ٠             | •                                     |

| Op Amp                                            |                |               |               |                                       |

|                                                   | Op Amp 1       | •             | ٠             | •                                     |

|                                                   | Op Amp 2       | •             | ٠             | •                                     |

| Pulse-Width Modulator                             | (PWM)          |               |               |                                       |

|                                                   | PWM3           | •             | ٠             | •                                     |

|                                                   | PWM4           | •             | ٠             | •                                     |

| Timers                                            |                |               |               |                                       |

|                                                   | Timer0         | •             | ٠             | •                                     |

|                                                   | Timer1         | •             | ٠             | •                                     |

|                                                   | Timer2         | •             | ٠             | •                                     |

|                                                   |                | 1             |               | · · · · · · · · · · · · · · · · · · · |

# 5.3 Register Definitions: BOR Control

## REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u              | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|----------------------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS <sup>(1)</sup> | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |                      |     | ·   |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR.<br><u>If BOREN &lt;1:0&gt; in Configuration Words = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect.<br><u>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)<br>0 = Band gap operates normally, and may turn off |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                            |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

# 6.5 Fail-Safe Clock Monitor

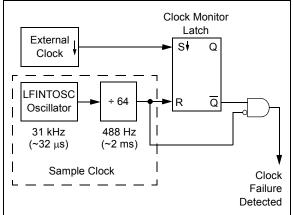

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Secondary Oscillator and RC).

FIGURE 6-9: FSCM BLOCK DIAGRAM

# 6.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 6-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

# 6.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

## 6.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

# 6.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Reset or Sleep). After an appropriate<br>amount of time, the user should check the<br>Status bits in the OSCSTAT register to<br>verify the oscillator start-up and that the<br>system clock switchover has successfully<br>completed. |

# 17.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 17-4.

# EQUATION 17-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 17-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 17-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

# 17.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

## 17.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

# 17.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

| R/W-0/0          | R/W-0/0                                                                                 | R/W-0/0                                                    | R/W-0/0                                                 | R/W-0/0                                               | R/W-0/0                       | R/W-0/0           | R/W-0/0    |

|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------|-------------------|------------|

| GxFSIM7          | GxFSIM6                                                                                 | GxFSIM5                                                    | GxFSIM4                                                 | GxFSIM3                                               | GxFSIM2                       | GxFSIM1           | GxFSIM0    |

| bit 7            |                                                                                         |                                                            |                                                         |                                                       |                               | •                 | bit (      |

|                  |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| Legend:          |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| R = Readable I   | pit                                                                                     | W = Writable                                               | bit                                                     | U = Unimplem                                          | nented bit, read              | as '0'            |            |

| u = Bit is uncha | anged                                                                                   | x = Bit is unkr                                            | iown                                                    | -n/n = Value a                                        | t POR and BOP                 | R/Value at all ot | her Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is clea                                          | ared                                                    | q = Value dep                                         | ends on conditi               | on                |            |

| bit 7            | <u>GxFIS7 = 1:</u><br>1 = NCO1_or                                                       |                                                            | ansition will ca                                        |                                                       | vent after falling<br>vent    | event phase de    | elay       |

|                  | <u>GxFIS7 = 0:</u>                                                                      |                                                            |                                                         |                                                       |                               |                   |            |

|                  | _                                                                                       | s no effect on f                                           | -                                                       |                                                       |                               |                   |            |

| bit 6            |                                                                                         | Gx Falling Eve                                             | ent Input Sourc                                         | e 6 Mode bit                                          |                               |                   |            |

|                  | 0 = PWM3 ou<br>GxFIS6 = 0:                                                              |                                                            | vill cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| oit 5            |                                                                                         | Gx Falling Eve                                             |                                                         |                                                       |                               |                   |            |

|                  | 0 = CCP2 ou<br>GxFIS5 = 0:                                                              |                                                            | ill cause an im                                         | cause a falling<br>mediate falling                    | event after fallin<br>event   | ng event phase    | delay      |

| bit 4            | GxFSIM4: CC                                                                             | Gx Falling Eve                                             | ent Input Sourc                                         | e 4 Mode bit                                          |                               |                   |            |

|                  | 0 = CCP1 low GxFIS4 = 0:                                                                | gh-to-low transi<br>v level will caus<br>effect on falling | e an immediat                                           |                                                       | after falling ever            | nt phase delay    |            |

| bit 3            |                                                                                         | )Gx Falling Eve                                            |                                                         | e 3 Mode bit                                          |                               |                   |            |

|                  | $\frac{GxFIS3 = 1}{1 = CLC1 \text{ out}}$ $0 = CLC1 \text{ out}$ $\frac{GxFIS3 = 0}{2}$ | tput high-to-low                                           | transition will<br>ill cause an im                      |                                                       | event after fallir<br>event   | ng event phase    | delay      |

| bit 2            |                                                                                         | )Gx Falling Eve                                            | ent Input Sourc                                         | e 2 Mode bit                                          |                               |                   |            |

|                  | 0 = Compara GxFIS2 = 0:                                                                 |                                                            | will cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| bit 1            | <b>GxFSIM1:</b> CC<br><u>GxFIS1 = 1:</u><br>1 = Compara                                 | OGx Falling Eve<br>tor 1 high-to-lo<br>tor 1 low level v   | nt Input Source<br>w transition wil<br>will cause an ir | e 1 Mode bit<br>I cause a falling<br>nmediate falling | g event after fall<br>g event | ing event phase   | e delay    |

# REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

| R/W-0/0        |             | U-0                 | U-0              | R/W-x/u          | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|----------------|-------------|---------------------|------------------|------------------|------------------|------------------|--------------|

| LCxPOL         |             |                     |                  | LCxG4POL         | LCxG3POL         | LCxG2POL         | LCxG1POL     |

| bit 7          |             |                     |                  |                  |                  |                  | bit (        |

|                |             |                     |                  |                  |                  |                  |              |

| Legend:        |             |                     |                  |                  |                  |                  |              |

| R = Reada      | ble bit     | W = Writable        | bit              | U = Unimpler     | mented bit, read | d as '0'         |              |

| u = Bit is u   | nchanged    | x = Bit is unkr     | nown             | -n/n = Value     | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is s | set         | '0' = Bit is clea   | ared             |                  |                  |                  |              |

|                |             |                     |                  |                  |                  |                  |              |

| bit 7          | LCxPOL: LO  | COUT Polarity C     | ontrol bit       |                  |                  |                  |              |

|                | 1 = The out | put of the logic of | cell is inverted | b                |                  |                  |              |

|                | 0 = The out | put of the logic of | cell is not inve | erted            |                  |                  |              |

| bit 6-4        | Unimpleme   | nted: Read as '     | 0'               |                  |                  |                  |              |

| bit 3          | LCxG4POL    | : Gate 4 Output     | Polarity Cont    | rol bit          |                  |                  |              |

|                | 1 = The out | put of gate 4 is i  | nverted wher     | n applied to the | logic cell       |                  |              |

|                | 0 = The out | put of gate 4 is r  | not inverted     |                  |                  |                  |              |

| bit 2          | LCxG3POL    | : Gate 3 Output     | Polarity Cont    | rol bit          |                  |                  |              |

|                |             | put of gate 3 is i  |                  | n applied to the | logic cell       |                  |              |

|                | 0 = The out | put of gate 3 is r  | not inverted     |                  |                  |                  |              |

| bit 1          | LCxG2POL    | : Gate 2 Output     | Polarity Cont    | rol bit          |                  |                  |              |

|                |             | put of gate 2 is i  |                  | n applied to the | logic cell       |                  |              |

|                | 0 = The out | put of gate 2 is r  | not inverted     |                  |                  |                  |              |

| bit 0          | LCxG1POL    | : Gate 1 Output     | Polarity Cont    | rol bit          |                  |                  |              |

|                |             | put of gate 1 is i  |                  | n applied to the | logic cell       |                  |              |

|                | 0 = The out | put of gate 1 is r  | not inverted     |                  |                  |                  |              |

|                |             |                     |                  |                  |                  |                  |              |

# REGISTER 19-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

# REGISTER 19-3: CLCxSEL0: GENERIC CLCx DATA 1 SELECT REGISTER

| U-0                                     | U-0                               | U-0 | R/W-x/u                                               | R/W-x/u                            | R/W-x/u     | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|-----------------------------------|-----|-------------------------------------------------------|------------------------------------|-------------|---------|---------|--|

| —                                       | —                                 | —   |                                                       |                                    | LCxD1S<4:0> |         |         |  |

| bit 7                                   |                                   | ·   |                                                       |                                    |             |         | bit 0   |  |

|                                         |                                   |     |                                                       |                                    |             |         |         |  |

| Legend:                                 |                                   |     |                                                       |                                    |             |         |         |  |

| R = Readable b                          | R = Readable bit W = Writable bit |     | bit                                                   | U = Unimplemented bit, read as '0' |             |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                                   |     | -n/n = Value at POR and BOR/Value at all other Resets |                                    |             |         |         |  |

bit 7-5 Unimplemented: Read as '0'

'1' = Bit is set

bit 4-0 LCxD1S<4:0>: CLCx Data1 Input Selection bits See Table 19-1.

'0' = Bit is cleared

| R/W-x/u          | R/W-x/u     | R/W-x/u                              | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------------|--------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG2D4T         | LCxG2D4N    | LCxG2D3T                             | LCxG2D3N        | LCxG2D2T       | LCxG2D2N         | LCxG2D1T         | LCxG2D1N    |

| bit 7            |             |                                      |                 |                |                  |                  | bit         |

| Legend:          |             |                                      |                 |                |                  |                  |             |

| R = Readable     | bit         | W = Writable                         | bit             | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged       | x = Bit is unkr                      | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set | -           | '0' = Bit is clea                    | ared            |                |                  |                  |             |

| bit 7            |             | Gate 2 Data 4 1                      | True (non-inve  | rted) hit      |                  |                  |             |

| bit i            |             | is gated into L0                     | ,               |                |                  |                  |             |

|                  |             | is not gated int                     |                 |                |                  |                  |             |

| bit 6            | LCxG2D4N:   | Gate 2 Data 4 I                      | Negated (inver  | rted) bit      |                  |                  |             |

|                  | 1 = LCxD4N  | is gated into L                      | CxG2            |                |                  |                  |             |

|                  | 0 = LCxD4N  | is not gated inf                     | to LCxG2        |                |                  |                  |             |

| bit 5            | LCxG2D3T: 0 | Gate 2 Data 3 1                      | True (non-invei | rted) bit      |                  |                  |             |

|                  |             | is gated into L0                     |                 |                |                  |                  |             |

|                  |             | is not gated int                     |                 |                |                  |                  |             |

| bit 4            |             | Gate 2 Data 3 I                      | •               | rted) bit      |                  |                  |             |

|                  |             | is gated into Lo<br>is not gated inf |                 |                |                  |                  |             |

| bit 3            |             | •                                    |                 | ate al \ la it |                  |                  |             |

| DIL 3            |             | Bate 2 Data 2 1<br>is gated into L0  |                 | ned) bit       |                  |                  |             |

|                  |             | is not gated into L                  |                 |                |                  |                  |             |

| bit 2            |             | Gate 2 Data 2 I                      |                 | rted) bit      |                  |                  |             |

| 5112             |             | is gated into L                      | •               |                |                  |                  |             |

|                  |             | is not gated int                     |                 |                |                  |                  |             |

| bit 1            | LCxG2D1T: 0 | Gate 2 Data 1 1                      | True (non-invei | rted) bit      |                  |                  |             |

|                  | 1 = LCxD1T  | is gated into L0                     | CxG2            |                |                  |                  |             |

|                  | 0 = LCxD1T  | is not gated int                     | o LCxG2         |                |                  |                  |             |

| bit 0            | LCxG2D1N:   | Gate 2 Data 1 I                      | Negated (inver  | rted) bit      |                  |                  |             |

|                  |             | is gated into L                      |                 |                |                  |                  |             |

|                  | 0 = LCxD1N  | is not nated inf                     |                 |                |                  |                  |             |

# REGISTER 19-8: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

# 21.4 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 21-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 21-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 21-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

## EQUATION 21-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = VCHOLD \qquad ;[1] VCHOLD charged to within 1/2 lsb$$

$$VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD \qquad ;[2] VCHOLD charge response to VAPPLIED$$

$$VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

# 27.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 27-1 displays the Timer1 enable selections.

| TABLE 27-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 27.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 27-2 displays the clock source selections.

### 27.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

## 27.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

## TABLE 27-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                   |  |

|-------------|---------|--------------------------------|--|

| 11          | x       | LFINTOSC                       |  |

| 10          | 0       | External Clocking on T1CKI Pin |  |

| 01          | x       | System Clock (Fosc)            |  |

| 00          | x       | Instruction Clock (Fosc/4)     |  |

# 27.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 27.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 27.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 27.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |  |  |  |

|-------|-------------------------------------------|--|--|--|

|       | asynchronous operation, it is possible to |  |  |  |

|       | skip an increment. When switching from    |  |  |  |

|       | asynchronous to synchronous operation,    |  |  |  |

|       | it is possible to produce an additional   |  |  |  |

|       | increment.                                |  |  |  |

## 27.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 27.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

# 27.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 27-3 for timing details.

TABLE 27-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |  |

|------------|--------|-----|------------------|--|

| $\uparrow$ | 0      | 0   | Counts           |  |

| $\uparrow$ | 0      | 1   | Holds Count      |  |

| $\uparrow$ | 1      | 0   | Holds Count      |  |

| 1          | 1      | 1   | Counts           |  |

# 29.4 Register Definitions: CCP Control

#### U-0 U-0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 DCxB<1:0> CCPxM<3:0> \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other Reset u = Bit is unchanged x = Bit is unknown '1' = Bit is set '0' = Bit is cleared bit 7-6 Unimplemented: Read as '0' bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits Capture mode: Unused Compare mode: Unused PWM mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. bit 3-0 CCPxM<3:0>: CCPx Mode Select bits 11xx = PWM mode 1011 = Compare mode: Auto-conversion Trigger (sets CCPxIF bit), starts ADC conversion if TRIGSEL = CCPx (see Register 21-3) 1010 = Compare mode: generate software interrupt only 1001 = Compare mode: clear output on compare match (set CCPxIF) 1000 = Compare mode: set output on compare match (set CCPxIF) 0111 = Capture mode: every 16th rising edge 0110 = Capture mode: every 4th rising edge 0101 = Capture mode: every rising edge 0100 = Capture mode: every falling edge 0011 = Reserved 0010 = Compare mode: toggle output on match 0001 = Reserved 0000 = Capture/Compare/PWM off (resets CCPx module)

### **REGISTER 29-1: CCPxCON: CCPx CONTROL REGISTER**

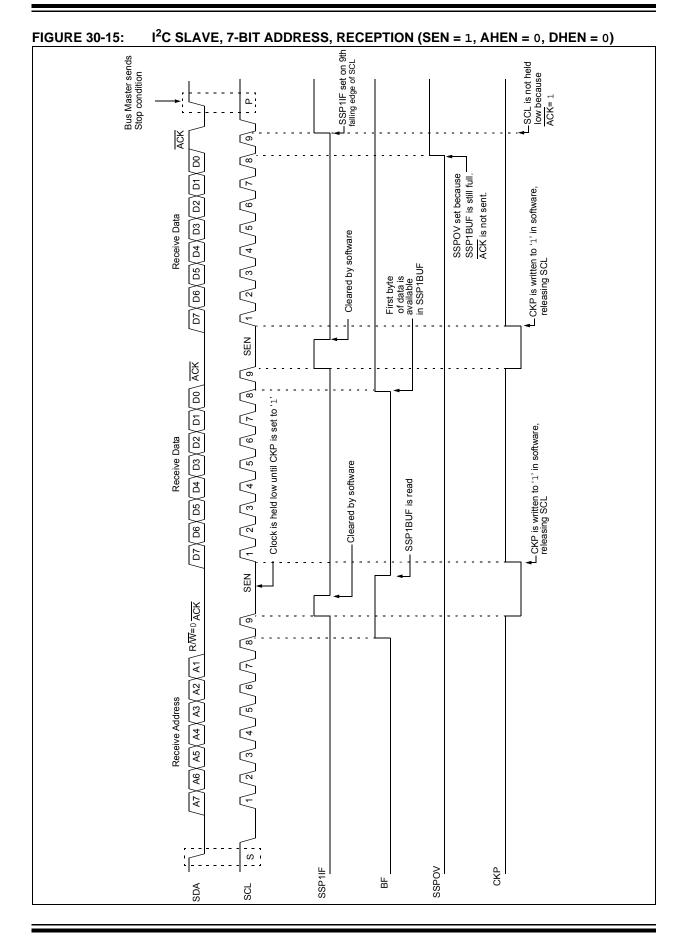

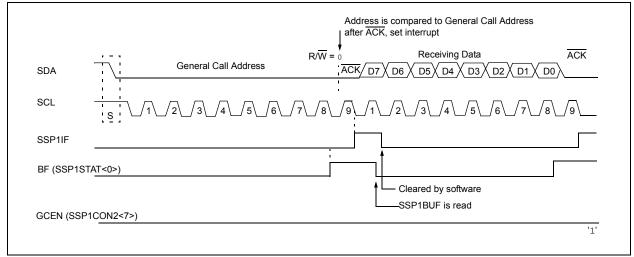

### 30.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 30-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

# FIGURE 30-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

## 30.5.9 SSP MASK REGISTER

An SSP Mask (SSP1MSK) register (Register 30-5) is available in  $I^2C$  Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of SSP1ADD<7:1>.

- 10-bit Address mode: address compare of SSP1ADD<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

# 31.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUD1CON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RC1REG is read after the overflow occurs, but before the fifth rising edge, the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character's fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared, those will be falsely detected as start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF.

- 2. If RCIDL is zero then wait for RCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

## 31.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUD1CON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 31-7), and asynchronously if the device is in Sleep mode (Figure 31-8). The interrupt condition is cleared by reading the RC1REG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

## 31.4.3.1 Special Considerations

### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RC1REG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# 31.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

# 31.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RC1STA and TX1STA Control registers must be configured for Synchronous Slave Reception (see Section 31.5.2.4 "Synchronous Slave Reception Setup").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RC1REG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

## 31.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RC1STA and TX1STA Control registers must be configured for synchronous slave transmission (see Section 31.5.2.2 "Synchronous Slave Transmission Setup").

- The TXIF interrupt flag must be cleared by writing the output data to the TX1REG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TX1REG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TX1REG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# TABLE 34-4: I/O PORTS (CONTINUED)

| Standar       | d Operati | ing Conditions (unless otherv      | vise stated)  |       |      |       |                                                                         |

|---------------|-----------|------------------------------------|---------------|-------|------|-------|-------------------------------------------------------------------------|

| Param.<br>No. | Sym.      | Characteristic                     | Min.          | Тур.† | Max. | Units | Conditions                                                              |

|               | IPUR      | Weak Pull-up Current               |               |       |      |       |                                                                         |

| D070*         |           |                                    | 25            | 100   | 200  | μA    | VDD = 3.3V, VPIN = Vss                                                  |

|               |           |                                    | 25            | 140   | 300  | μA    | VDD = 5.0V, VPIN = Vss                                                  |

|               | Vol       | Output Low Voltage <sup>(4)</sup>  |               |       |      |       |                                                                         |

| D080          |           | I/O ports                          | —             | -     | 0.6  | V     | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |

|               | Voн       | Output High Voltage <sup>(4)</sup> |               |       |      |       |                                                                         |

| D090          |           | I/O ports                          | Vdd - 0.7     | —     | _    | V     | IOH = 3.5mA, VDD = 5V<br>IOH = 3mA, VDD = 3.3V<br>IOH = 1mA, VDD = 1.8V |

|               |           | Capacitive Loading Specs or        | n Output Pins |       |      |       |                                                                         |

| D101*         | COSC2     | OSC2 pin                           | _             | —     | 15   | pF    | In XT, HS and LP modes<br>when external clock is<br>used to drive OSC1  |

| D101A*        | Сю        | All I/O pins                       |               |       | 50   | pF    | —                                                                       |

Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in EXTRC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

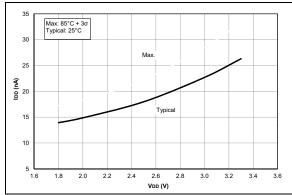

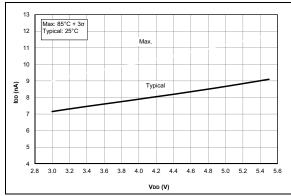

FIGURE 35-37: IPD, Fixed Voltage Reference (FVR), PIC16LF1717/8/9 Only.

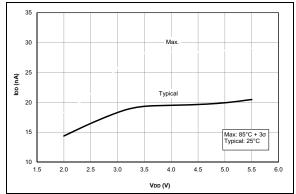

FIGURE 35-38: IPD, Fixed Voltage Reference (FVR), PIC16F1717/8/9 Only.

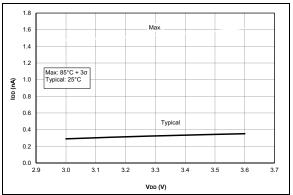

FIGURE 35-39: IPD, Brown-out Reset (BOR), BORV = 1, PIC16LF1717/8/9 Only.

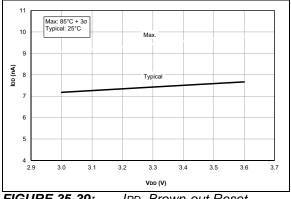

FIGURE 35-40: IPD, Brown-out Reset (BOR), BORV = 1, PIC16F1717/8/9 Only.

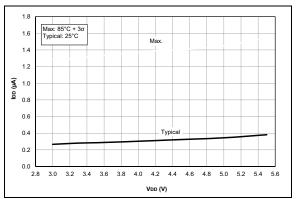

**FIGURE 35-41:** IPD, LP Brown-out Reset (LPBOR = 0), PIC16LF1717/8/9 Only.

FIGURE 35-42: IPD, LP Brown-out Reset (LPBOR = 0), PIC16F1717/8/9 Only.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

## ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15