Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 28-PIN ALLOCATION TABLE (PIC16(L)F1718) TABLE 1:

| I/O <sup>(2)</sup> | SPDIP,SOIC,<br>SSOP | QFN, UQFN | ADC  | Reference          | Comparator       | Op Amp  | DAC                  | Zero Cross | Timers                        |    | CCL               | NCO | PWM | 900  |                   | MSSP                   | EUSART | CLC                   | Interrupt                 | Pull-up | Basic          |

|--------------------|---------------------|-----------|------|--------------------|------------------|---------|----------------------|------------|-------------------------------|----|-------------------|-----|-----|------|-------------------|------------------------|--------|-----------------------|---------------------------|---------|----------------|

| RA0                | 2                   | 27        | AN0  |                    | C1IN0-<br>C2IN0- |         |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN0 <sup>(1)</sup> | IOC                       | Y       |                |

| RA1                | 3                   | 28        | AN1  |                    | C1IN1-<br>C2IN1- | OPA1OUT |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN1 <sup>(1)</sup> | юс                        | Y       |                |

| RA2                | 4                   | 1         | AN2  | V <sub>REF</sub> - | C1IN0+<br>C2IN0+ |         | DAC1OUT1             |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       |                |

| RA3                | 5                   | 2         | AN3  | V <sub>REF</sub> + | C1IN1+           |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RA4                | 6                   | 3         |      |                    |                  | OPA1IN+ |                      |            | T0CKI <sup>(1)</sup>          |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RA5                | 7                   | 4         | AN4  |                    |                  | OPA1IN- | DAC2OUT1             |            |                               |    |                   |     |     |      |                   | nSS <sup>(1)</sup>     |        |                       | IOC                       | Υ       |                |

| RA6                | 10                  | 7         |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       | OSC2<br>CLKOUT |

| RA7                | 9                   | 6         |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       | OSC1<br>CLKIN  |

| RB0                | 21                  | 18        | AN12 |                    | C2IN1+           |         |                      | ZCD        |                               |    |                   |     |     | COG1 | IN <sup>(1)</sup> |                        |        |                       | INT <sup>(1)</sup><br>IOC | Y       |                |

| RB1                | 22                  | 19        | AN10 |                    | C1IN3-<br>C2IN3- | OPA2OUT |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RB2                | 23                  | 20        | AN8  |                    |                  | OPA2IN- |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RB3                | 24                  | 21        | AN9  |                    | C1IN2-<br>C2IN2- | OPA2IN+ |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       |                |

| RB4                | 25                  | 22        | AN11 |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RB5                | 26                  | 23        | AN13 |                    |                  |         |                      |            | T1G <sup>(1)</sup>            |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RB6                | 27                  | 24        |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN2 <sup>(1)</sup> | IOC                       | Υ       | ICSPCLK        |

| RB7                | 28                  | 25        |      |                    |                  |         | DAC1OUT2<br>DAC2OUT2 |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN3 <sup>(1)</sup> | юс                        | Y       | ICSPDAT        |

| RC0                | 11                  | 8         |      |                    |                  |         |                      |            | T1CKI <sup>(1)</sup><br>SOSCO |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RC1                | 12                  | 9         |      |                    |                  |         |                      |            | sosci                         | СС | P2 <sup>(1)</sup> |     |     |      |                   |                        |        |                       | .IOC                      | Υ       |                |

| RC2                | 13                  | 10        | AN14 |                    |                  |         |                      |            |                               | СС | P1 <sup>(1)</sup> |     |     |      |                   |                        |        |                       | - IOC                     | Υ       |                |

| RC3                | 14                  | 11        | AN15 |                    |                  |         |                      |            | · · · ·                       |    |                   |     |     |      |                   | SCL/SCK <sup>(1)</sup> |        |                       | IOC .                     | Υ       |                |

DS40001740B-page 4

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Alternate outputs are excluded from solid shaded areas.

5: Alternate inputs are excluded from dot shaded areas.

| Name                                            | Function           | Input<br>Type    | Output<br>Type | Description                                        |

|-------------------------------------------------|--------------------|------------------|----------------|----------------------------------------------------|

| RC4/AN16/SDI <sup>(1)</sup> /SDA <sup>(1)</sup> | RC4                | TTL/ST           | CMOS           | General purpose I/O.                               |

|                                                 | AN16               | AN               |                | ADC Channel 16 input.                              |

|                                                 | SDI                | TTL/ST           | _              | SPI Data input.                                    |

|                                                 | SDA                | l <sup>2</sup> C | _              | I <sup>2</sup> C Data input.                       |

| RC5/AN17                                        | RC5                | TTL/ST           | CMOS           | General purpose I/O.                               |

|                                                 | AN17               | AN               | _              | ADC Channel 17 input.                              |

| RC6/AN18/CK <sup>(1)</sup>                      | RC6                | TTL/ST           | CMOS           | General purpose I/O.                               |

|                                                 | AN18               | AN               | —              | ADC Channel 18 input.                              |

|                                                 | СК                 | TTL/ST           |                | EUSART synchronous clock.                          |

| RC7/AN19/RX <sup>(1)</sup>                      | RC7                | TTL/ST           | CMOS           | General purpose I/O.                               |

|                                                 | AN19               | AN               | _              | ADC Channel 19 input.                              |

|                                                 | RX                 | TTL/ST           | _              | EUSART receive.                                    |

| RE3/MCLR/VPP                                    | RE3                | TTL/ST           |                | General purpose input.                             |

|                                                 | MCLR               | ST               | _              | Master clear input.                                |

|                                                 | VPP                | HV               |                | Programming enable.                                |

| Vdd                                             | Vdd                | Power            |                | Positive supply.                                   |

| Vss                                             | Vss                | Power            |                | Ground reference.                                  |

| OUT <sup>(2)</sup>                              | C10UT              |                  | CMOS           | Comparator 1 output.                               |

|                                                 | C2OUT              |                  | CMOS           | Comparator 2 output.                               |

|                                                 | CCP1               |                  | CMOS           | Compare/PWM1 output.                               |

|                                                 | CCP2               |                  | CMOS           | Compare/PWM2 output.                               |

|                                                 | NCO10UT            |                  | CMOS           | Numerically controlled oscillator output.          |

|                                                 | PWM3OUT            |                  | CMOS           | PWM3 output.                                       |

|                                                 | PWM4OUT            |                  | CMOS           | PWM4 output.                                       |

|                                                 | COG1A              |                  | CMOS           | Complementary output generator output A.           |

|                                                 | COG1B              |                  | CMOS           | Complementary output generator output B.           |

|                                                 | COG1C              |                  | CMOS           | Complementary output generator output C.           |

|                                                 | COG1D              |                  | CMOS           | Complementary output generator output D.           |

|                                                 | SDA <sup>(3)</sup> |                  | OD             | I <sup>2</sup> C Data output.                      |

|                                                 | SCK                |                  | CMOS           | SPI clock output.                                  |

|                                                 | SCL <sup>(3)</sup> |                  | OD             | l <sup>2</sup> C clock output.                     |

|                                                 | SDO                |                  |                | •                                                  |

|                                                 | TX/CK              |                  | CMOS           | EUSART asynchronous TX data/synchronous clock out. |

|                                                 | DT <sup>(3)</sup>  |                  | CMOS           | EUSART synchronous data output.                    |

|                                                 | CLC1OUT            |                  | CMOS           | Configurable Logic Cell 1 output.                  |

|                                                 | CLC2OUT            |                  | CMOS           | Configurable Logic Cell 2 output.                  |

|                                                 | CLC3OUT            |                  | CMOS           | Configurable Logic Cell 3 output.                  |

|                                                 | CLC4OUT            |                  | CMOS           | Configurable Logic Cell 4 output.                  |

#### TABLE 1-2: PIC16(L)F1718 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

### TABLE 1-3: PIC16(L)F1717/9 PINOUT DESCRIPTION

| Name                             | Function | Input<br>Type | Output<br>Type | Description                                  |

|----------------------------------|----------|---------------|----------------|----------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/           | RA0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| CLCIN0 <sup>(1)</sup>            | AN0      | AN            | _              | ADC Channel 0 input.                         |

|                                  | C1IN0-   | AN            | _              | Comparator C2 negative input.                |

|                                  | C2IN0-   | AN            | —              | Comparator C3 negative input.                |

|                                  | CLCIN0   | TTL/ST        | —              | Configurable Logic Cell source input.        |

| RA1/AN1/C1IN1-/C2IN1-/           | RA1      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA1OUT/CLCIN1 <sup>(1)</sup>    | AN1      | AN            | _              | ADC Channel 1 input.                         |

|                                  | C1IN1-   | AN            | _              | Comparator C1 negative input.                |

|                                  | C2IN1-   | AN            | —              | Comparator C2 negative input.                |

|                                  | OPA10UT  | _             | AN             | Operational Amplifier 1 output.              |

|                                  | CLCIN1   | TTL/ST        | —              | Configurable Logic Cell source input.        |

| RA2/AN2/VREF-/C1IN0+/C2IN0+/     | RA2      | TTL/ST        | CMOS           | General purpose I/O.                         |

| DAC1OUT1                         | AN2      | AN            | —              | ADC Channel 2 input.                         |

|                                  | VREF-    | AN            | —              | ADC Negative Voltage Reference input.        |

|                                  | C1IN0+   | AN            | —              | Comparator C2 positive input.                |

|                                  | C2IN0+   | AN            | —              | Comparator C3 positive input.                |

|                                  | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

| RA3/AN3/VREF+/C1IN1+             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | AN3      | AN            | —              | ADC Channel 3 input.                         |

|                                  | VREF+    | AN            | —              | ADC Voltage Reference input.                 |

|                                  | C1IN1+   | AN            | _              | Comparator C1 positive input.                |

| RA4/OPA1IN+/T0CKI <sup>(1)</sup> | RA4      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OPA1IN+  | AN            | _              | Operational Amplifier 1 non-inverting input. |

|                                  | TOCKI    | TTL/ST        | —              | Timer0 gate input.                           |

| RA5/AN4/OPA1IN-/DAC2OUT1/        | RA5      | TTL/ST        | CMOS           | General purpose I/O.                         |

| <u>SS</u> (1)                    | AN4      | AN            | —              | ADC Channel 4 input.                         |

|                                  | OPA1IN-  | AN            | —              | Operational Amplifier 1 inverting input.     |

|                                  | DAC2OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

|                                  | SS       | —             | —              | Slave Select enable input.                   |

| RA6/OSC2/CLKOUT                  | RA6      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKOUT   | _             | CMOS           | Fosc/4 output.                               |

| RA7/OSC1/CLKIN                   | RA7      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC1     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKIN    | ST            | —              | External clock input (EC mode).              |

| RB0/AN12/C2IN1+/ZCD/             | RB0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| COGIN <sup>(1)</sup>             | AN12     | AN            | —              | ADC Channel 12 input.                        |

|                                  | C2IN1+   | AN            | —              | Comparator C2 positive input.                |

|                                  | ZCD      | AN            | _              | Zero-Cross Detection Current Source/Sink.    |

|                                  | COGIN    | TTL/ST        |                | Complementary Output Generator input.        |

.egend:AN = Analog input or outputCMOS = CMOS compatible input or outputOD = Open-DrainTTL = TTL compatible inputST = Schmitt Trigger input with CMOS levelsI<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>CHV = High VoltageXTAL = Crystal levels

**Note 1:** Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1717/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

### 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect **Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |  |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|--|

| PIC16(L)F1717   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |  |

| PIC16(L)F1718/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |  |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

# PIC16(L)F1717/8/9

| Addr.                                                                                                                    | Name                   | Bit 7        | Bit 6           | Bit 5          | Bit 4         | Bit 3             | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on all<br>other Resets |

|--------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|-----------------|----------------|---------------|-------------------|----------------------|----------------------|----------------------|----------------------|------------------------------|

| Bank                                                                                                                     | 4                      |              |                 |                |               |                   |                      |                      |                      |                      |                              |

| 20Ch                                                                                                                     | WPUA                   | WPUA7        | WPUA6           | WPUA5          | WPUA4         | WPUA3             | WPUA2                | WPUA1                | WPUA0                | 1111 1111            | 1111 1111                    |

| 20Dh                                                                                                                     | WPUB                   | WPUB7        | WPUB6           | WPUB5          | WPUB4         | WPUB3             | WPUB2                | WPUB1                | WPUB0                | 1111 1111            | 1111 1111                    |

| 20Eh                                                                                                                     | WPUC                   | WPUC7        | WPUC6           | WPUC5          | WPUC4         | WPUC3             | WPUC2                | WPUC1                | WPUC0                | 1111 1111            | 1111 1111                    |

| 20Fh                                                                                                                     | WPUD <sup>(1)</sup>    | WPUD7        | WPUD6           | WPUD5          | WPUD4         | WPUD3             | WPUD2                | WPUD1                | WPUD0                | 1111 1111            | 1111 1111                    |

| 210h                                                                                                                     | WPUE                   | —            | —               | _              |               | WPUE3             | WPUE2 <sup>(1)</sup> | WPUE1 <sup>(1)</sup> | WPUE0 <sup>(1)</sup> | 1111                 | 1111                         |

| 211h                                                                                                                     | SSP1BUF                | Synchronous  | s Serial Port R | eceive Buffer/ | Transmit Regi | ster              |                      |                      |                      | XXXX XXXX            | uuuu uuuu                    |

| 212h                                                                                                                     | SSP1ADD                |              |                 |                | ADI           | )<7:0>            |                      |                      |                      | XXXX XXXX            | 0000 0000                    |

| 213h                                                                                                                     | SSP1MSK                |              |                 |                | MSI           | <b>&lt;</b> <7:0> |                      |                      |                      | XXXX XXXX            | 1111 1111                    |

| 214h                                                                                                                     | SSP1STAT               | SMP          | CKE             | D/Ā            | Р             | S                 | R/W                  | UA                   | BF                   | 0000 0000            | 0000 0000                    |

| 215h                                                                                                                     | SSP1CON1               | WCOL         | SSPOV           | SSPEN          | CKP           |                   | SSP                  | M<3:0>               |                      | 0000 0000            | 0000 0000                    |

| 216h                                                                                                                     | SSP1CON2               | GCEN         | ACKSTAT         | ACKDT          | ACKEN         | RCEN              | PEN                  | RSEN                 | SEN                  | 0000 0000            | 0000 0000                    |

| 217h                                                                                                                     | SSP1CON3               | ACKTIM       | PCIE            | SCIE           | BOEN          | SDAHT             | SBCDE                | AHEN                 | DHEN                 | 0000 0000            | 0000 0000                    |

| 218h                                                                                                                     |                        |              | 1.1             |                |               |                   |                      |                      |                      |                      |                              |

| 21Fh                                                                                                                     | _                      | Unimplemen   | implemented     |                |               |                   |                      |                      |                      | _                    | _                            |

| Bank                                                                                                                     | 5                      |              |                 |                |               |                   |                      |                      |                      |                      | •                            |

| 28Ch                                                                                                                     | ODCONA                 | ODA7         | ODA6            | ODA5           | ODA4          | ODA3              | ODA2                 | ODA1                 | ODA0                 | 0000 0000            | 0000 0000                    |

| 28Dh                                                                                                                     | ODCONB                 | ODB7         | ODB6            | ODB5           | ODB4          | ODB3              | ODB2                 | ODB1                 | ODB0                 | 0000 0000            | 0000 0000                    |

| 28Eh                                                                                                                     | ODCONC                 | ODC7         | ODC6            | ODC5           | ODC4          | ODC3              | ODC2                 | ODC1                 | ODC0                 | 0000 0000            | 0000 0000                    |

| 28Fh                                                                                                                     | ODCOND <sup>(1)</sup>  | ODD7         | ODD6            | ODD5           | ODD4          | ODD3              | ODD2                 | ODD1                 | ODD0                 | 0000 0000            | 0000 0000                    |

| 290h                                                                                                                     | ODCONE <sup>(1)</sup>  | —            | _               | —              |               | _                 | ODE2                 | ODE1                 | ODE0                 | 000                  | 000                          |

| 291h                                                                                                                     | CCPR1L                 | Capture/Con  | npare/PWM R     | egister 1 (LSB | )             |                   |                      |                      |                      | XXXX XXXX            | uuuu uuuu                    |

| 292h                                                                                                                     | CCPR1H                 | Capture/Con  | npare/PWM R     | egister 1 (MSE | 3)            |                   |                      |                      |                      | XXXX XXXX            | uuuu uuuu                    |

| 293h                                                                                                                     | CCP1CON                | —            | —               | DC1B           | <1:0>         |                   | CCP                  | 1M<3:0>              |                      | 00 0000              | 00 0000                      |

| 294h                                                                                                                     | _                      | Unimplemen   | ited            |                |               |                   |                      |                      |                      | _                    | _                            |

| 297h                                                                                                                     | 0000001                | Oanture (Oan |                 | :              | \<br>\        |                   |                      |                      |                      |                      |                              |

| 298h                                                                                                                     | CCPR2L                 |              | npare/PWM R     |                |               |                   |                      |                      |                      | XXXX XXXX            | uuuu uuuu                    |

| 299h                                                                                                                     | CCPR2H                 | Capture/Con  | npare/PWM R     | <b>.</b> .     | ,             |                   | 000                  | 201-0-0-             |                      | XXXX XXXX            | uuuu uuuu                    |

| 29Ah                                                                                                                     | CCP2CON                | -            | —               | DC2B           | <1:0>         |                   | CCP2                 | 2M<3:0>              |                      | 00 0000              | 00 0000                      |

| 29Bh<br><br>29Dh                                                                                                         | _                      | Unimplemen   | ited            |                |               |                   |                      |                      |                      | —                    | —                            |

| 29Eh                                                                                                                     | CCPTMRS                | P4TSE        | L<1:0>          | P3TSE          | L<1:0>        | C2TSE             | L<1:0>               | C1TS                 | EL<1:0>              | 0000 0000            | 0000 0000                    |

| 29Fh                                                                                                                     | _                      | Unimplemen   | ited            |                |               |                   |                      |                      |                      | _                    | _                            |

| Bank                                                                                                                     | 6                      |              |                 |                |               |                   |                      |                      |                      | •                    |                              |

| 30Ch                                                                                                                     | SLRCONA                | SLRA7        | SLRA6           | SLRA5          | SLRA4         | SLRA3             | SLRA2                | SLRA1                | SLRA0                | 1111 1111            | 0000 0000                    |

| 30Dh                                                                                                                     | SLRCONB                | SLRB7        | SLRB6           | SLRB5          | SLRB4         | SLRB3             | SLRB2                | SLRB1                | SLRB0                | 1111 1111            | 0000 0000                    |

| 30Eh                                                                                                                     | SLRCONC                | SLRC7        | SLRC6           | SLRC5          | SLRC4         | SLRC3             | SLRC2                | SLRC1                | SLRC0                | 1111 1111            | 0000 0000                    |

| 30Fh                                                                                                                     | SLRCOND <sup>(1)</sup> | SLRD7        | SLRD6           | SLRD5          | SLRD4         | SLRD3             | SLRD2                | SLRD1                | SLRD0                | 1111 1111            | 0000 0000                    |

| 310h                                                                                                                     | SLRCONE <sup>(1)</sup> | —            | —               | —              | —             | —                 | SLRE2                | SLRE1                | SLRE0                | 111                  | 000                          |

| 310h         SLRCONE(")         —         —         —         —         SLRE2         SLRE1         SLRE0           311h |                        |              |                 |                |               |                   | -                    | _                    | _                    |                      |                              |

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

gend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented on PIC16(L)F1718. 2: Unimplemented on PIC16LF1717/8/9

| U-0                               | R/W-0/0                                       | R/W-0/0                             | R/W-0/0        | R/W-0/0      | REGISTER 3       | R/W-0/0  | R/W-0/0     |

|-----------------------------------|-----------------------------------------------|-------------------------------------|----------------|--------------|------------------|----------|-------------|

| _                                 | NCOIE                                         | COGIE                               | ZCDIE          | CLC4IE       | CLC3IE           | CLC2IE   | CLC1IE      |

| bit 7                             |                                               |                                     |                |              |                  |          | bit (       |

| Legend:                           |                                               |                                     |                |              |                  |          |             |

| R = Readable bit W = Writable bit |                                               |                                     |                | U = Unimpler | nented bit, read | l as '0' |             |

| u = Bit is unchanged              |                                               | x = Bit is unki                     |                | •            | at POR and BO    |          | ther Resets |

| '1' = Bit is :                    | •                                             | '0' = Bit is cle                    |                |              |                  |          |             |

|                                   |                                               |                                     |                |              |                  |          |             |

| bit 7                             | Unimplemer                                    | nted: Read as '                     | o'             |              |                  |          |             |

| bit 6                             |                                               | D Interrupt Enat                    | ole bit        |              |                  |          |             |

|                                   |                                               | errupt enabled errupt disabled      |                |              |                  |          |             |

| bit 5                             | COGIE: COG Auto-Shutdown Interrupt Enable bit |                                     |                |              |                  |          |             |

| 1 = COG interrupt enabled         |                                               |                                     |                |              |                  |          |             |

|                                   | 0 = COG int                                   | errupt disabled                     |                |              |                  |          |             |

| bit 4                             |                                               | -Cross Detectio                     | n Interrupt Er | able bit     |                  |          |             |

|                                   |                                               | errupt enabled                      |                |              |                  |          |             |

| L:1 0                             |                                               | errupt disabled                     | -  -  - :4     |              |                  |          |             |

| bit 3                             |                                               | C4 Interrupt Ena                    | adie dit       |              |                  |          |             |

|                                   |                                               | terrupt enabled<br>terrupt disabled |                |              |                  |          |             |

| bit 2                             |                                               | C3 Interrupt Ena                    |                |              |                  |          |             |

|                                   |                                               | terrupt enabled                     |                |              |                  |          |             |

|                                   | 0 = CLC3 in                                   | terrupt disabled                    |                |              |                  |          |             |

| bit 1                             | CLC2IE: CLC                                   | C2 Interrupt Ena                    | able bit       |              |                  |          |             |

|                                   |                                               | terrupt enabled                     |                |              |                  |          |             |

|                                   |                                               | terrupt disabled                    |                |              |                  |          |             |

| bit 0                             |                                               | C1 Interrupt Ena                    | able bit       |              |                  |          |             |

|                                   |                                               | terrupt enabled<br>terrupt disabled |                |              |                  |          |             |

|                                   |                                               | ion upi disabled                    |                |              |                  |          |             |

| Note:                             | Bit PEIE of the IN                            | ITCON register                      | must be        |              |                  |          |             |

|                                   | set to enable any                             | peripheral inter                    | rupt.          |              |                  |          |             |

### REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

## 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the CP bit of Configuration Words.

#### **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

## 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

| R/W-0/0      | R/W-0/0     | R/W-0/0      | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |

|--------------|-------------|--------------|---------|--------------|------------------|---------|---------|--|

| ODB7         | ODB6        | ODB5         | ODB4    | ODB3         | ODB2             | ODB1    | ODB0    |  |

| bit 7        | bit 7 bit 0 |              |         |              |                  |         |         |  |

|              |             |              |         |              |                  |         |         |  |

| Legend:      |             |              |         |              |                  |         |         |  |

| Legena:      |             |              |         |              |                  |         |         |  |

| R = Readable | bit         | W = Writable | bit     | U = Unimplen | nented bit, read | as '0'  |         |  |

#### REGISTER 11-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

bit 7-0 **ODB<7:0>:** PORTB Open-Drain Enable bits For RB<7:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only)

'0' = Bit is cleared

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 11-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRB<7:0>: PORTB Slew Rate Enable bits

For RB<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 11-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

'1' = Bit is set

.

INLVLB<7:0>: PORTB Input Level Select bits

For RB<7:0> pins, respectively

1 = Port pin digital input operates with ST thresholds

0 = Port pin digital input operates with TTL thresholds

#### 16.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See **Section 14.0** "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 23.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 16.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- Analog Ground

Some inverting input selections share a pin with the operational amplifier output function. Enabling both functions at the same time will direct the operational amplifier output to the comparator inverting input.

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

### 16.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 34-18: Comparator Specifications for more details.

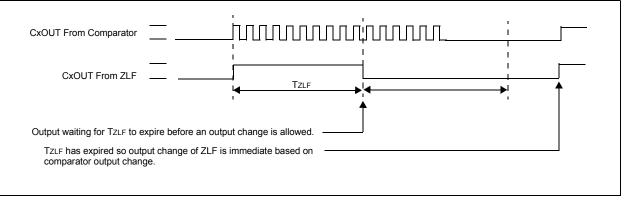

### 16.9 Zero Latency Filter

In high-speed operation, and under proper circuit conditions, it is possible for the comparator output to oscillate. This oscillation can have adverse effects on the hardware and software relying on this signal. Therefore, a digital filter has been added to the comparator output to suppress the comparator output oscillation. Once the comparator output changes, the output is prevented from reversing the change for a nominal time of 20 ns. This allows the comparator output to stabilize without affecting other dependent devices. Refer to Figure 16-3.

## FIGURE 16-3: COMPARATOR ZERO LATENCY FILTER OPERATION

| R/W-x/u          | R/W-x/u     | R/W-x/u                              | R/W-x/u        | R/W-x/u                               | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------------|--------------------------------------|----------------|---------------------------------------|------------------|------------------|-------------|

| LCxG4D4T         | LCxG4D4N    | LCxG4D3T                             | LCxG4D3N       | LCxG4D2T                              | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |

| bit 7            |             | •                                    |                | · · · · · · · · · · · · · · · · · · · |                  | •                | bit         |

| Legend:          |             |                                      |                |                                       |                  |                  |             |

| R = Readable     | bit         | W = Writable                         | bit            | U = Unimpler                          | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged       | x = Bit is unkr                      | nown           | -n/n = Value a                        | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |             | '0' = Bit is cle                     | ared           |                                       |                  |                  |             |

|                  |             |                                      |                |                                       |                  |                  |             |

| bit 7            |             | Gate 4 Data 4 1                      |                | rted) bit                             |                  |                  |             |

|                  |             | is gated into L0<br>is not gated int |                |                                       |                  |                  |             |

| bit 6            |             | Gate 4 Data 4                        |                | ted) bit                              |                  |                  |             |

| bit o            |             | is gated into L                      | •              | ted) bit                              |                  |                  |             |

|                  |             | is not gated int                     |                |                                       |                  |                  |             |

| bit 5            | LCxG4D3T: ( | Gate 4 Data 3 1                      | True (non-inve | rted) bit                             |                  |                  |             |

|                  | 1 = LCxD3T  | is gated into L0                     | CxG4           |                                       |                  |                  |             |

|                  | 0 = LCxD3T  | is not gated int                     | o LCxG4        |                                       |                  |                  |             |

| bit 4            |             | Gate 4 Data 3                        | •              | rted) bit                             |                  |                  |             |

|                  |             | is gated into L                      |                |                                       |                  |                  |             |

| <b>h</b> # 0     |             | is not gated inf                     |                | ate al \ h it                         |                  |                  |             |

| bit 3            |             | Gate 4 Data 2 1<br>is gated into L0  | •              | nted) bit                             |                  |                  |             |

|                  |             | is not gated into L                  |                |                                       |                  |                  |             |

| bit 2            |             | Gate 4 Data 2                        |                | rted) bit                             |                  |                  |             |

|                  |             | is gated into L                      | •              | ,                                     |                  |                  |             |

|                  | 0 = LCxD2N  | is not gated int                     | to LCxG4       |                                       |                  |                  |             |

| bit 1            | LCxG4D1T: ( | Gate 4 Data 1 1                      | True (non-inve | rted) bit                             |                  |                  |             |

|                  |             | is gated into LO                     |                |                                       |                  |                  |             |

|                  |             | is not gated int                     |                |                                       |                  |                  |             |

| bit 0            |             | Gate 4 Data 1                        | •              | rted) bit                             |                  |                  |             |

|                  |             | is gated into Lo<br>is not gated inf |                |                                       |                  |                  |             |

|                  |             | ie not gated in                      |                |                                       |                  |                  |             |

### REGISTER 19-10: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

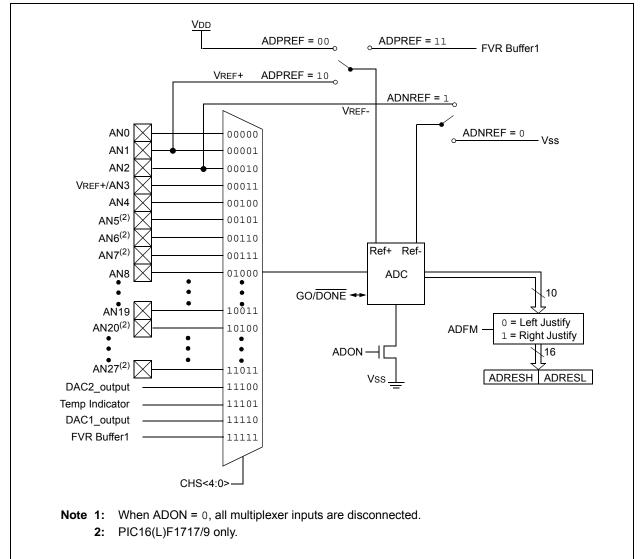

## 21.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 21-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 21-1: ADC BLOCK DIAGRAM

| R/W-0/0                 | U-0                                      | R/W-0/0                                                                                                                                              | R/W-0/0                                                                    | R/W-0/0                       | R/W-0/0          | U-0             | R/W-0/0      |

|-------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|------------------|-----------------|--------------|

| DAC2EN                  | _                                        | DAC2OE1                                                                                                                                              | DAC2OE2                                                                    | DAC                           | 2PSS<1:0>        | _               | DAC2NSS      |

| bit 7                   |                                          | ·                                                                                                                                                    |                                                                            |                               |                  |                 | bit 0        |

| Legend:                 |                                          |                                                                                                                                                      |                                                                            |                               |                  |                 |              |

| R = Readable            | e bit                                    | W = Writable                                                                                                                                         | bit                                                                        | U = Unimpl                    | emented bit, rea | ıd as '0'       |              |

| u = Bit is unch         | nanged                                   | x = Bit is unkr                                                                                                                                      | iown                                                                       | -n/n = Value                  | e at POR and B   | OR/Value at all | other Resets |

| '1' = Bit is set        | •                                        | '0' = Bit is clea                                                                                                                                    | ared                                                                       |                               |                  |                 |              |

| bit 6<br>bit 5<br>bit 4 | DAC2OE1<br>1 = DAC<br>0 = DAC<br>DAC2OE2 | s disabled<br>ented: Read as '0<br>: DAC2 Voltage Ou<br>voltage level is also<br>voltage level is disc<br>: DAC2 Voltage Ou<br>voltage level is also | utput Enable bit<br>o an output on t<br>connected from<br>utput Enable bit | the DAC2OU<br>the DAC2OU<br>t | JT1 pin          |                 |              |

| bit 3-2                 | DAC2PSS                                  |                                                                                                                                                      |                                                                            |                               | JT2 pin          |                 |              |

| bit 1<br>bit 0          | •                                        | ented: Read as '0<br>: DAC2 Negative S                                                                                                               |                                                                            | pits                          |                  |                 |              |

#### 24.6 Register Definitions: DAC Control REGISTER 24-1: DAC2CON0: VOLTAGE REFERENCE CONTROL REGIST

#### REGISTER 24-2: DAC2CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|----------|---------|---------|

| —     | _   | —   |         |         | DAC2R<4: | 0>      |         |

| bit 7 |     |     |         |         |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DAC2R<4:0>: DAC Voltage Output Select bits

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC2 MODULE

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|-------|---------|------------|--------------|-------|-------|---------|---------------------|

| DAC2CON0 | DAC2EN | _     | DAC2OE1 | DAC2OE2    | DAC2PSS<1:0> |       | _     | DAC2NSS | 263                 |

| DAC2CON1 | _      | _     |         | DAC2R<4:0> |              |       |       |         | 263                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

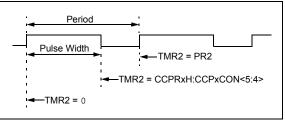

#### 29.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 29-3 shows a typical waveform of the PWM signal.

#### 29.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

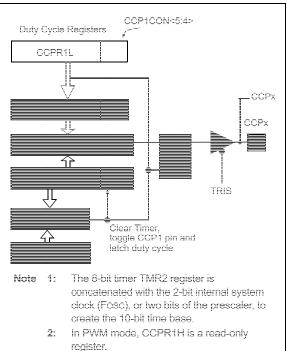

Figure 29-4 shows a simplified block diagram of PWM operation.

#### FIGURE 29-3: CCP PWM OUTPUT SIGNAL

#### FIGURE 29-4: SIMPLIFIED PWM BLOCK DIAGRAM

## PIC16(L)F1717/8/9

#### 30.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

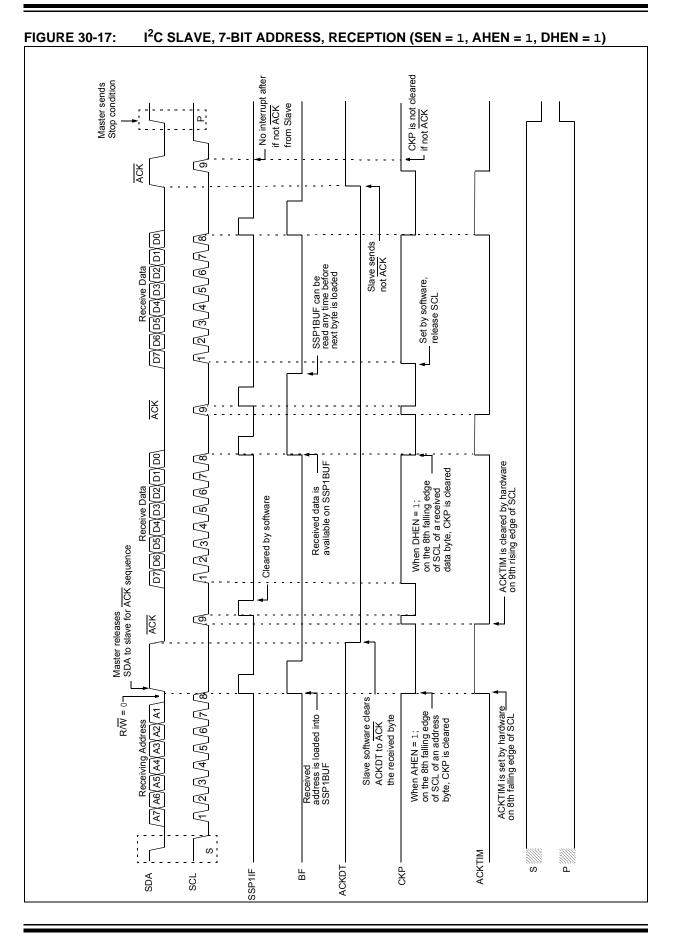

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 30-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSP1STAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSP1BUF clearing the BF flag.

- 7. Slave loads low address into SSP1ADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSP1ADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSP1IF is set.

- **Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSP1ADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSP1BUF clearing BF.

- 12. Slave loads high address into SSP1ADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSP1CON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSP1BUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

#### 30.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSP1ADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 30-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 30-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| R/W-0/0          | R/W-0/0                     | R/W-0/0                           | R/W-0/0            | R/W-0/0         | R-0/0            | R-0/0            | R-0/0       |

|------------------|-----------------------------|-----------------------------------|--------------------|-----------------|------------------|------------------|-------------|

| SPEN             | RX9                         | SREN                              | CREN               | ADDEN           | FERR             | OERR             | RX9D        |

| bit 7            |                             | ·                                 |                    |                 |                  |                  | bit C       |

|                  |                             |                                   |                    |                 |                  |                  |             |

| Legend:          |                             |                                   |                    |                 |                  |                  |             |

| R = Readable     | e bit                       | W = Writable                      | bit                | U = Unimpler    | mented bit, read | as '0'           |             |

| u = Bit is unc   | hanged                      | x = Bit is unki                   | nown               | -n/n = Value    | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set | t                           | '0' = Bit is cle                  | ared               |                 |                  |                  |             |

|                  |                             |                                   |                    |                 |                  |                  |             |

| bit 7            |                             | Port Enable bi                    | t                  |                 |                  |                  |             |

|                  | 1 = Serial po               | rt enabled<br>rt disabled (he     | ld in Reset)       |                 |                  |                  |             |