#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6×6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4 Register Definitions: Status

| U-0            | U-0                | U-0                                | R-1/q           | R-1/q             | R/W-0/u                    | R/W-0/u             | R/W-0/u          |

|----------------|--------------------|------------------------------------|-----------------|-------------------|----------------------------|---------------------|------------------|

| 00             |                    |                                    |                 |                   | Z                          | DC <sup>(1)</sup>   | C <sup>(1)</sup> |

| <br>bit 7      | _                  | _                                  | 10              | FD                | 2                          | DC                  | bit              |

|                |                    |                                    |                 |                   |                            |                     |                  |

| Legend:        |                    |                                    |                 |                   |                            |                     |                  |

| R = Readat     | ole bit            | W = Writable                       | bit             | U = Unimpler      | mented bit, read           | l as '0'            |                  |

| u = Bit is ur  | nchanged           | x = Bit is unkr                    | nown            | -n/n = Value      | at POR and BO              | R/Value at all o    | ther Resets      |

| '1' = Bit is s | et                 | '0' = Bit is cle                   | ared            | q = Value de      | pends on condit            | ion                 |                  |

|                |                    |                                    |                 |                   |                            |                     |                  |

| bit 7-5        | Unimplemen         | ted: Read as '                     | 0'              |                   |                            |                     |                  |

| bit 4          | TO: Time-Out       | t bit                              |                 |                   |                            |                     |                  |

|                |                    | er-up, CLRWDT                      |                 | SLEEP instruc     | tion                       |                     |                  |

|                |                    | ime-out occurre                    | ed              |                   |                            |                     |                  |

| bit 3          | PD: Power-D        | 0                                  |                 |                   |                            |                     |                  |

|                |                    | er-up or by the tion of the SLE    |                 |                   |                            |                     |                  |

| bit 2          | Z: Zero bit        |                                    |                 |                   |                            |                     |                  |

|                |                    | t of an arithme<br>t of an arithme |                 |                   | ero                        |                     |                  |

| bit 1          | DC: Digit Car      | ry/Digit Borrow                    | bit (ADDWF, A   | DDLW, SUBLW,      | SUBWF instructi            | ons) <sup>(1)</sup> |                  |

|                | 1 = A carry-o      | ut from the 4th                    | low-order bit   | of the result oc  | curred                     |                     |                  |

|                |                    | out from the 4t                    |                 |                   |                            |                     |                  |

| bit 0          | C: Carry/Borr      | ow bit <sup>(1)</sup> (addw        | IF, ADDLW, SU   | BLW, SUBWF in     | structions) <sup>(1)</sup> |                     |                  |

|                |                    | ut from the Mo                     |                 |                   |                            |                     |                  |

|                | 0 = No carry-      | out from the M                     | ost Significant | t bit of the resu | lt occurred                |                     |                  |

| Note 1:        | For Borrow, the pa | larity is reverse                  | ed. A subtract  | ion is executed   | d by adding the            | two's complem       | ent of the       |

#### REGISTER 3-1: STATUS: STATUS REGISTER

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

## 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F170X Memory Programming Specification"* (DS41683).

# 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

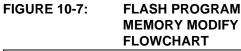

# 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

DS40001740B-page 116

| R/W-0/0          | R/W-0/0                                 | R/W-0/0              | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|-----------------------------------------|----------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| IOCCP7           | IOCCP6                                  | IOCCP5               | IOCCP4  | IOCCP3                                                | IOCCP2  | IOCCP1  | IOCCP0  |  |

| bit 7            |                                         |                      |         |                                                       |         |         | bit 0   |  |

|                  |                                         |                      |         |                                                       |         |         |         |  |

| Legend:          |                                         |                      |         |                                                       |         |         |         |  |

| R = Readable     | Readable bit W = Writable bit           |                      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unch  | u = Bit is unchanged x = Bit is unknown |                      | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set |                                         | '0' = Bit is cleared |         |                                                       |         |         |         |  |

#### REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

bit 7-0

bit 7-0

**IOCCP<7:0>:** Interrupt-on-Change PORTC Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

IOCCN<7:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCCF7     | IOCCF6     | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCCF<7:0>: Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

- 0 = No change was detected, or the user cleared the detected change.

# 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- ADC positive reference

- Comparator positive input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

# 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, comparators, and DAC is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 21.0** "**Analog-to-Digital Converter (ADC) Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference **Section 23.0 "8-Bit Digital-to-Analog Converter (DAC1) Module"** and **Section 16.0 "Comparator Module"** for additional information.

# 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See Figure 35-76: FVR Stabilization Period, PIC16LF1717/8/9 Only.

# 17.2 Register Definitions: PWM Control

| REGISTER         | 1/-I. <b>FVVIV</b> |                   | CONTROL         | CEGISTER        |                  |                  |              |

|------------------|--------------------|-------------------|-----------------|-----------------|------------------|------------------|--------------|

| R/W-0/0          | U-0                | R-0/0             | R/W-0/0         | U-0             | U-0              | U-0              | U-0          |

| PWMxEN           | —                  | PWMxOUT           | PWMxPOL         |                 | —                | —                | _            |

| bit 7            |                    |                   |                 |                 |                  |                  | bit 0        |

|                  |                    |                   |                 |                 |                  |                  |              |

| Legend:          |                    |                   |                 |                 |                  |                  |              |

| R = Readable     | e bit              | W = Writable      | bit             | U = Unimpler    | nented bit, read | d as '0'         |              |

| u = Bit is unch  | nanged             | x = Bit is unkr   | nown            | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                    | '0' = Bit is cle  | ared            |                 |                  |                  |              |

|                  |                    |                   |                 |                 |                  |                  |              |

| bit 7            | PWMxEN: P          | WM Module En      | able bit        |                 |                  |                  |              |

|                  | 1 = PWM mo         | odule is enable   | d               |                 |                  |                  |              |

|                  | 0 = PWM mo         | odule is disable  | d               |                 |                  |                  |              |

| bit 6            | Unimplemen         | ted: Read as '    | 0'              |                 |                  |                  |              |

| bit 5            | PWMxOUT:           | >WM module o      | utput level whe | en bit is read. |                  |                  |              |

| bit 4            | PWMxPOL:           | PWMx Output I     | Polarity Select | bit             |                  |                  |              |

|                  | 1 = PWM ou         | tput is active lo | W.              |                 |                  |                  |              |

|                  | 0 = PWM ou         | tput is active hi | gh.             |                 |                  |                  |              |

| bit 3-0          | Unimplemen         | ted: Read as '    | 0'              |                 |                  |                  |              |

# REGISTER 17-1: PWMxCON: PWM CONTROL REGISTER

# REGISTER 17-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxD   | CH<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

# bit 7-0 **PWMxDCH<7:0>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

# REGISTER 17-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxDC  | CL<7:6> | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | PWMxDCL<7:6>: PWM Duty Cycle Least Significant bits                                    |

|---------|----------------------------------------------------------------------------------------|

|         | These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register. |

| bit 5-0 | Unimplemented: Read as '0'                                                             |

# REGISTER 19-11: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | _   | MCL4OUT | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'         |

|---------|------------------------------------|

| bit 3   | MCL4OUT: Mirror copy of LC4OUT bit |

| bit 2   | MLC3OUT: Mirror copy of LC3OUT bit |

| bit 1   | MLC2OUT: Mirror copy of LC2OUT bit |

|         |                                    |

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

# TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name                  | Bit7     | Bit6     | Bit5     | Bit4     | Blt3     | Bit2        | Bit1       | Bit0     | Register<br>on Page |

|-----------------------|----------|----------|----------|----------|----------|-------------|------------|----------|---------------------|

| ANSELA                | _        |          | ANSA5    | ANSA4    | ANSA3    | ANSA2       | ANSA1      | ANSA0    | 125                 |

| ANSELB                | _        | _        | ANSB5    | ANSB4    | ANSB3    | ANSB2       | ANSB1      | ANSB0    | 131                 |

| ANSELC                | ANSC7    | ANSC6    | ANSC5    | ANSC4    | ANSC3    | ANSC2       | —          | —        | 136                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6    | ANSD5    | ANSD4    | ANSD3    | ANSD2       | ANSD1      | ANSD0    | 141                 |

| CLC1CON               | LC1EN    | _        | LC10UT   | LC1INTP  | LC1INTN  | L           | C1MODE<2:0 | )>       | 224                 |

| CLC2CON               | LC2EN    | -        | LC2OUT   | LC2INTP  | LC2INTN  | L           | C2MODE<2:0 | )>       | 224                 |

| CLC3CON               | LC3EN    | _        | LC3OUT   | LC3INTP  | LC3INTN  | L           | C3MODE<2:0 | )>       | 224                 |

| CLCDATA               | _        |          | _        |          | MCL4OUT  | MLC3OUT     | MLC2OUT    | MLC1OUT  | 231                 |

| CLC1GLS0              | LC1G1D4T | LC1G1D4N | LC1G1D3T | LC1G1D3N | LC1G1D2T | LC1G1D2N    | LC1G1D1T   | LC1G1D1N | 227                 |

| CLC1GLS1              | LC1G2D4T | LC1G2D4N | LC1G2D3T | LC1G2D3N | LC1G2D2T | LC1G2D2N    | LC1G2D1T   | LC1G2D1N | 228                 |

| CLC1GLS2              | LC1G3D4T | LC1G3D4N | LC1G3D3T | LC1G3D3N | LC1G3D2T | LC1G3D2N    | LC1G3D1T   | LC1G3D1N | 229                 |

| CLC1GLS3              | LC1G4D4T | LC1G4D4N | LC1G4D3T | LC1G4D3N | LC1G4D2T | LC1G4D2N    | LC1G4D1T   | LC1G4D1N | 230                 |

| CLC1POL               | LC1POL   | _        | _        | _        | LC1G4POL | LC1G3POL    | LC1G2POL   | LC1G1POL | 225                 |

| CLC1SEL0              | —        |          | _        |          |          | LC1D1S<4:0> | ,          |          | 225                 |

| CLC1SEL1              | —        |          |          |          |          | LC1D2S<4:0> |            |          | 226                 |

| CLC1SEL2              | —        |          | -        |          |          | LC1D3S<4:0> |            |          | 226                 |

| CLC1SEL3              | —        | -        | _        |          |          | LC1D4S<4:0> | •          |          | 226                 |

| CLC2GLS0              | LC2G1D4T | LC2G1D4N | LC2G1D3T | LC2G1D3N | LC2G1D2T | LC2G1D2N    | LC2G1D1T   | LC2G1D1N | 227                 |

| CLC2GLS1              | LC2G2D4T | LC2G2D4N | LC2G2D3T | LC2G2D3N | LC2G2D2T | LC2G2D2N    | LC2G2D1T   | LC2G2D1N | 228                 |

| CLC2GLS2              | LC2G3D4T | LC2G3D4N | LC2G3D3T | LC2G3D3N | LC2G3D2T | LC2G3D2N    | LC2G3D1T   | LC2G3D1N | 229                 |

| CLC2GLS3              | LC2G4D4T | LC2G4D4N | LC2G4D3T | LC2G4D3N | LC2G4D2T | LC2G4D2N    | LC2G4D1T   | LC2G4D1N | 230                 |

| CLC2POL               | LC2POL   | _        | _        |          | LC2G4POL | LC2G3POL    | LC2G2POL   | LC2G1POL | 225                 |

| CLC2SEL0              | —        | _        | —        |          |          | LC2D1S<4:0> | ,          |          | 225                 |

| CLC2SEL1              | —        | —        | —        |          |          | LC2D2S<4:0> | ,          |          | 226                 |

| CLC2SEL2              | _        | _        | _        |          |          | LC2D3S<4:0> | •          |          | 226                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for CLC module.

**Note 1:** PIC16(L)F1717/9 only.

| Name                 | Bit 7  | Bit 6            | Bit 5  | Bit 4  | Bit 3   | Bit 2      | Bit 1    | Bit 0  | Register<br>on Page |

|----------------------|--------|------------------|--------|--------|---------|------------|----------|--------|---------------------|

| INTCON               | GIE    | PEIE             | TMR0IE | INTE   | IOCIE   | TMR0IF     | INTF     | IOCIF  | 90                  |

| NCO1ACCU             |        | _                | _      |        |         | NCO1AC     | C<19:16> |        | 239                 |

| NCO1ACCH             |        |                  |        | NCO1AC | C<15:8> |            |          |        | 239                 |

| NCO1ACCL             |        |                  |        | NCO1A  | CC<7:0> |            |          |        | 238                 |

| NCO1CLK              | N      | 1PWS<2:0         | >      | _      | _       | _          | N1CK     | S<1:0> | 238                 |

| NCO1CON              | N1EN   | _                | N1OUT  | N1POL  | —       | —          | —        | N1PFM  | 237                 |

| NCO1INCU             |        | — NCO1INC<19:16> |        |        |         |            |          | 240    |                     |

| NCO1INCH             |        |                  |        | NCO1IN | C<15:8> |            |          |        | 240                 |

| NCO1INCL             |        |                  |        | NCO1IN | NC<7:0> |            |          |        | 239                 |

| PIE3                 | _      | NCOIE            | COGIE  | ZCDIE  | CLC4IE  | CLC3IE     | CLC2IE   | CLC1IE | 93                  |

| PIR3                 | —      | NCOIF            | COGIF  | ZCDIF  | CLC4IF  | CLC3IF     | CLC2IF   | CLC1IF | 96                  |

| TRISA                | TRISA7 | TRISA6           | TRISA5 | TRISA4 | TRISA3  | TRISA2     | TRISA1   | TRISA0 | 124                 |

| TRISC                | TRISC7 | TRISC6           | TRISC5 | TRISC4 | TRISC3  | TRISC2     | TRISC1   | TRISC0 | 135                 |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6           | TRISD5 | TRISD4 | TRISD3  | TRISD2     | TRISD1   | TRISD0 | 140                 |

| RxyPPS               |        |                  | _      |        | F       | RxyPPS<4:0 | >        |        | 153                 |

TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOX

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCOx module.

Note 1: PIC16(L)F1717/9 only.

# 26.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

# 26.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

# 26.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in Table 34-12: Timer0 and Timer1 External Clock Requirements.

# 26.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

#### 27.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 27-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 27-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

# 27.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

## 27.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 27.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 16.4.1 "Comparator Output Synchronization"**.

#### 27.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 16.4.1 "Comparator Output Synchronization"**.

# 27.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 27-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

#### 27.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 27-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 27-6 for timing details.

# 27.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 27.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| Name    | Bit 7                                                                           | Bit 6  | Bit 5  | Bit 4  | Bit 3          | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|---------------------------------------------------------------------------------|--------|--------|--------|----------------|--------|--------|--------|---------------------|

| ANSELA  | _                                                                               | _      | ANSA5  | ANSA4  | ANSA3          | ANSA2  | ANSA1  | ANSA0  | 125                 |

| ANSELB  | _                                                                               | _      | ANSB5  | ANSB4  | ANSB3          | ANSB2  | ANSB1  | ANSB0  | 131                 |

| ANSELC  | ANSC7                                                                           | ANSC6  | ANSC5  | ANSC4  | ANSC3          | ANSC2  | _      | _      | 136                 |

| CCP1CON | _                                                                               | _      | DC1B   | s<1:0> |                | CCP1N  | 1<3:0> |        | 294                 |

| CCP2CON | _                                                                               | _      | DC2B   | s<1:0> |                | CCP2N  | 1<3:0> |        | 294                 |

| INTCON  | GIE                                                                             | PEIE   | TMR0IE | INTE   | IOCIE          | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE                                                                         | ADIE   | RCIE   | TXIE   | SSP1IE         | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF                                                                         | ADIF   | RCIF   | TXIF   | SSP1IF         | CCP1IF | TMR2IF | TMR1IF | 94                  |

| TMR1H   | IR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |        |        |        |                |        |        | 271*   |                     |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register     |        |        |        |                | 271*   |        |        |                     |

| TRISA   | TRISA7                                                                          | TRISA6 | TRISA5 | TRISA4 | TRISA3         | TRISA2 | TRISA1 | TRISA0 | 124                 |

| TRISB   | TRISB7                                                                          | TRISB6 | TRISB5 | TRISB4 | TRISB3         | TRISB2 | TRISB1 | TRISB0 | 130                 |

| TRISC   | TRISC7                                                                          | TRISC6 | TRISC5 | TRISC4 | TRISC3         | TRISC2 | TRISC1 | TRISC0 | 135                 |

| T1CON   | TMR1C                                                                           | S<1:0> | T1CKP  | S<1:0> | T1OSCEN        | T1SYNC |        | TMR10N | 279                 |

| T1GCON  | TMR1GE                                                                          | T1GPOL | T1GTM  | T1GSPM | T1GGO/<br>DONE | T1GVAL | T1GS   | S<1:0> | 280                 |

## TABLE 27-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

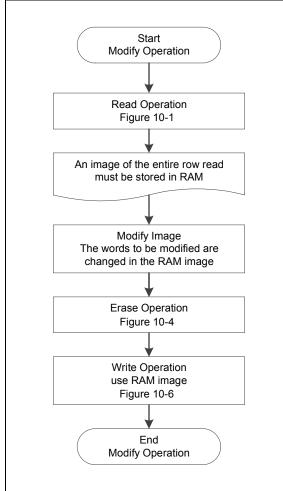

# 29.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 29-2 shows a simplified diagram of the compare operation.

#### FIGURE 29-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# 29.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

# 29.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. See Section 27.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 29.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

# 29.2.4 AUTO-CONVERSION TRIGGER

When Auto-Conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The auto-conversion trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The auto-conversion trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Refer to **Section 29.2.4 "Auto-Conversion Trigger"** for more information.

- Note 1: The auto-conversion trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the auto-conversion trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

# 29.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

# 31.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

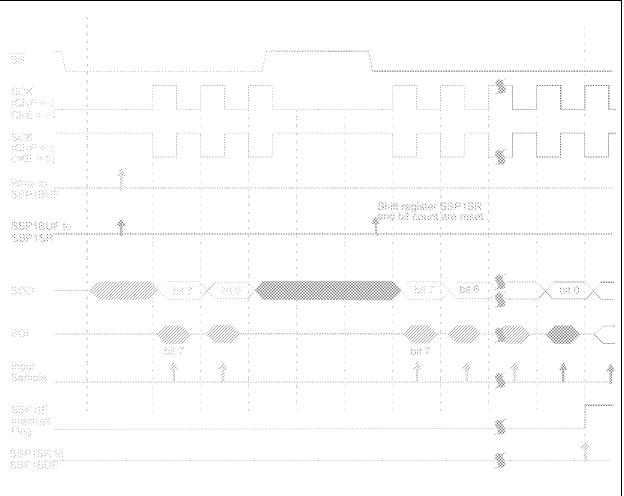

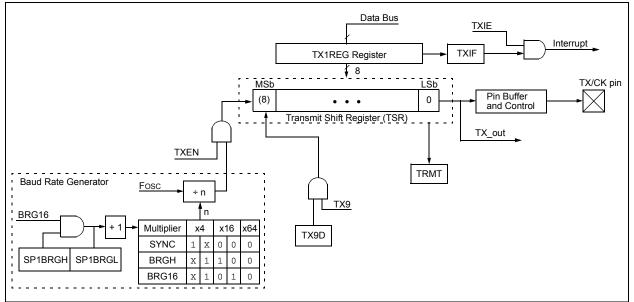

Block diagrams of the EUSART transmitter and receiver are shown in Figure 31-1 and Figure 31-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

• Configurable Logic Cell (CLC)

#### FIGURE 31-1: EUSART TRANSMIT BLOCK DIAGRAM

# 31.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SP1BRGH, SP1BRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

Table 31-3 contains the formulas for determining the baud rate. Example 31-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 31-5. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SP1BRGH, SP1BRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

# EXAMPLE 31-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SP1BRGH:SP1BRGL:

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $= \frac{\frac{16000000}{9600}}{64} - 1$                                |

| $= [25.042] = 25$ Calculated Baud Rate $= \frac{1600000}{64(25+1)}$     |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<6:3>) \rightarrow PC<14:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ \text{0} \rightarrow \underline{\text{WDT}} \text{ prescaler,} \\ \text{1} \rightarrow \underline{\text{TO}} \\ \text{1} \rightarrow \overline{\text{PD}} \\ \hline \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                                  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$ are set.                                                                                         |

| CALLW                            | Subroutine Call With W                                                                                                                                                                                                                          | COMF             | Complement f                                                                                                                                                |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                          | [ label ] CALLW                                                                                                                                                                                                                                 | Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |

| Operands:                        | None                                                                                                                                                                                                                                            | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |

| Operation:                       | $\begin{array}{l} (PC) +1 \rightarrow TOS, \\ (W) \rightarrow PC < 7:0 >, \end{array}$                                                                                                                                                          | Operation:       | $(\bar{f}) \rightarrow (destination)$                                                                                                                       |

|                                  | $(PCLATH < 6:0 >) \rightarrow PC < 14:8 >$                                                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                           |

| Status Affected:<br>Description: | None<br>Subroutine call with W. First, the<br>return address (PC + 1) is pushed<br>onto the return stack. Then, the<br>contents of W is loaded into PC<7:0>,<br>and the contents of PCLATH into<br>PC<14:8>. CALLW is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |  |

|------------------|-----------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |

| Status Affected: | Z                                                                     |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

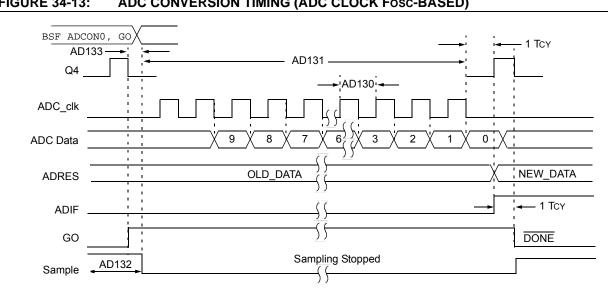

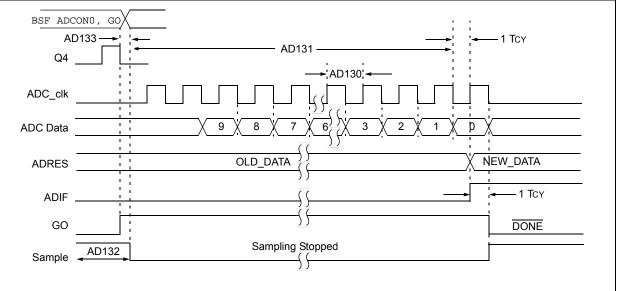

#### FIGURE 34-13: ADC CONVERSION TIMING (ADC CLOCK Fosc-BASED)

Note 1: If the ADC clock source is selected as FRC, a time of TcY is added before the ADC clock starts. This allows the SLEEP instruction to be executed.

Note: Unless otherwise noted, VIN = 5V, FOSC = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

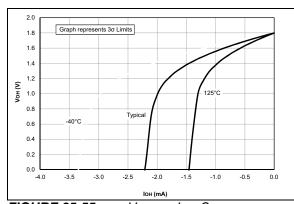

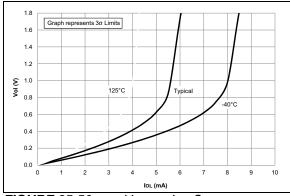

**FIGURE 35-55:** VOH vs. IOH Over Temperature, VDD = 1.8V, PIC16LF1717/8/9 Only.

**FIGURE 35-56:** VOL vs. IOL Over Temperature, VDD = 1.8V, PIC16LF1717/8/9 Only.

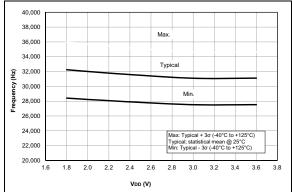

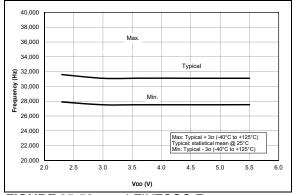

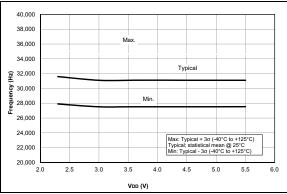

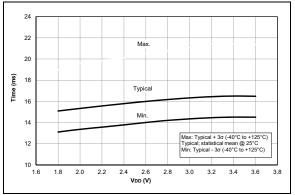

FIGURE 35-57: LFINTOSC Frequency, PIC16LF1717/8/9 Only.

FIGURE 35-58: LFINTOSC Frequency, PIC16F1717/8/9 Only.

FIGURE 35-59: WDT Time-Out Period, PIC16F1717/8/9 Only.

FIGURE 35-60: WDT Time-Out Period, PIC16LF1717/8/9 Only.

# 37.2 Package Details

The following sections give the technical details of the packages.

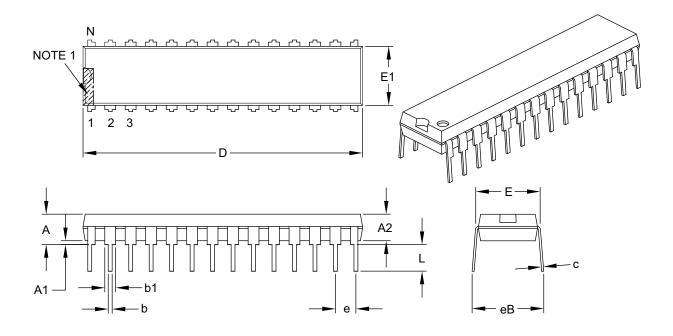

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |          | INCHES |       |

|----------------------------|-------|----------|--------|-------|

| Dimension Limits           |       | MIN      | NOM    | MAX   |

| Number of Pins             | N     | 28       |        |       |

| Pitch                      | e     | .100 BSC |        |       |

| Top to Seating Plane       | А     | -        | -      | .200  |

| Molded Package Thickness   | A2    | .120     | .135   | .150  |

| Base to Seating Plane      | A1    | .015     | -      | -     |

| Shoulder to Shoulder Width | E     | .290     | .310   | .335  |

| Molded Package Width       | E1    | .240     | .285   | .295  |

| Overall Length             | D     | 1.345    | 1.365  | 1.400 |

| Tip to Seating Plane       | L     | .110     | .130   | .150  |

| Lead Thickness             | С     | .008     | .010   | .015  |

| Upper Lead Width           | b1    | .040     | .050   | .070  |

| Lower Lead Width           | b     | .014     | .018   | .022  |

| Overall Row Spacing §      | eB    | _        | _      | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

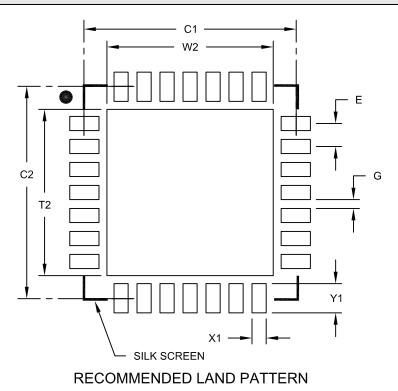

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |    | MILLIM   | ETERS |      |

|----------------------------|----|----------|-------|------|

| Units<br>Dimension Limits  |    | MIN      | NOM   | MAX  |

| Contact Pitch              | E  | 0.65 BSC |       |      |

| Optional Center Pad Width  | W2 |          |       | 4.70 |

| Optional Center Pad Length | T2 |          |       | 4.70 |

| Contact Pad Spacing        | C1 |          | 6.00  |      |

| Contact Pad Spacing        | C2 |          | 6.00  |      |

| Contact Pad Width (X28)    | X1 |          |       | 0.40 |

| Contact Pad Length (X28)   | Y1 |          |       | 0.85 |

| Distance Between Pads      | G  | 0.25     |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A