Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

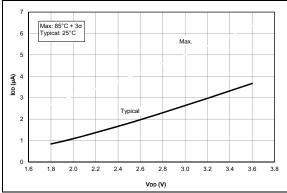

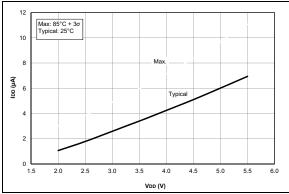

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1718) (CONTINUED)

|                    |                     |           |      |           |       |            |        | ( - · ( ) |            | -   |        |       |      |      | '       |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         |           |         |                         |

|--------------------|---------------------|-----------|------|-----------|-------|------------|--------|-----------|------------|-----|--------|-------|------|------|---------|----------------|---------|-------|--------|-------|-----------------------------|------------------------|----------------------------------------|-------------------|-------------------|---------|---------|---------|---------|-----------|---------|-------------------------|

| I/O <sup>(2)</sup> | SPDIP,SOIC,<br>SSOP | QFN, UQFN | ADC  | Reference |       | Comparator | Op Amp | DAC       | Zero Cross |     | Timers |       | auu  | 5    | NCO     | MM             |         |       | 900    |       |                             | MSSP                   |                                        |                   | EUSAKI            |         | ر<br>د  |         |         | Interrupt | Pull-up | Basic                   |

| RC4                | 15                  | 12        | AN16 |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        | DI <sup>(1)</sup><br>DA <sup>(1)</sup> |                   |                   |         |         |         |         | IOC       | Υ       |                         |

| RC5                | 16                  | 13        | AN17 |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         | IOC       | Υ       |                         |

| RC6                | 17                  | 14        | AN18 |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        | С                 | K <sup>(3)</sup>  |         |         |         |         | IOC       | Υ       |                         |

| RC7                | 18                  | 15        | AN19 |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        | R                 | X <sup>(3)</sup>  |         |         |         |         | - IQC -   | Υ       |                         |

| RE3                | 1                   | 26        |      |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         | юс        | Y       | MCLR<br>V <sub>PP</sub> |

| V <sub>DD</sub>    | 20                  | 17        |      |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         |           |         | V <sub>DD</sub>         |

| V <sub>SS</sub>    | 8                   | 5         |      |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         |           |         | $V_{SS}$                |

| V SS               | 19                  | 16        |      |           |       |            |        |           |            |     |        |       |      |      |         |                |         |       |        |       |                             |                        |                                        |                   |                   |         |         |         |         |           |         |                         |

| OUT <sup>(4)</sup> |                     |           |      |           | CIOUT | C2OUT      |        |           |            |     |        |       | CCP1 | CCP2 | NCO10UT | <b>PWM3OUT</b> | PWM40UT | COG1A | COG1B  | COG1C | C0G1D<br>SDA <sup>(3)</sup> | SCK/SCI <sup>(3)</sup> | SDO                                    | TX/CK             | DT <sup>(3)</sup> | CLC40UT | CLC3OUT | CLC2OUT | CLC10UT |           |         |                         |

| IN <sup>(5)</sup>  |                     |           |      |           |       |            |        |           |            | T1G | T1CKI  | TOCKI | CCP1 | CCP2 |         |                |         |       | COG1IN |       |                             | SCK/SCI <sup>(3)</sup> | SS                                     | RX <sup>(3)</sup> | сĶ                | CLCINO  | CLCIN1  | CLCIN2  | CLCIN3  | INT       |         |                         |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Alternate outputs are excluded from solid shaded areas.

5: Alternate inputs are excluded from dot shaded areas.

| Name                                            | Function | Input<br>Type | Output<br>Type | Description                                  |

|-------------------------------------------------|----------|---------------|----------------|----------------------------------------------|

| RB1/AN10/C1IN3-/C2IN3-/                         | RB1      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA2OUT                                         | AN10     | AN            | _              | ADC Channel 10 input.                        |

|                                                 | C1IN3-   | AN            | —              | Comparator C1 negative input.                |

|                                                 | C2IN3-   | AN            | —              | Comparator C2 negative input.                |

|                                                 | OPA2OUT  |               | AN             | Operational Amplifier 2 output.              |

| RB2/AN8/OPA2IN-                                 | RB2      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN8      | AN            | _              | ADC Channel 8 input.                         |

|                                                 | OPA2IN-  | AN            | —              | Operational Amplifier 2 inverting input.     |

| RB3/AN9/C1IN2-/C2IN2-/                          | RB3      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA2IN+                                         | AN9      | AN            | _              | ADC Channel 9 input.                         |

|                                                 | C1IN2-   | AN            | _              | Comparator C1 negative input.                |

|                                                 | C2IN2-   | AN            | _              | Comparator C2 negative input.                |

|                                                 | OPA2IN+  | AN            | _              | Operational Amplifier 2 non-inverting input. |

| RB4/AN11                                        | RB4      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN11     | AN            | _              | ADC Channel 11 input.                        |

| RB5/AN13/T1G <sup>(1)</sup>                     | RB5      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN13     | AN            |                | ADC Channel 13 input.                        |

|                                                 | T1G      | TTL/ST        |                | Timer1 gate input.                           |

| RB6/CLCIN2 <sup>(1)</sup> /ICSPCLK              | RB6      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | CLCIN2   | TTL/ST        |                | Configurable Logic Cell source input.        |

|                                                 | ICSPCLK  | ST            |                | Serial Programming Clock.                    |

| RB7/DAC1OUT2/DAC2OUT2/                          | RB7      | TTL/ST        | CMOS           | General purpose I/O.                         |

| CLCIN3 <sup>(1)</sup> /ICSPDAT                  | DAC1OUT2 | _             | AN             | Digital-to-Analog Converter output.          |

|                                                 | DAC2OUT2 | _             | AN             | Digital-to-Analog Converter output.          |

|                                                 | CLCIN3   | TTL/ST        |                | Configurable Logic Cell source input.        |

|                                                 | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                              |

| RC0/T1CKI <sup>(1)</sup> /SOSCO                 | RC0      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | T1CKI    | ST            |                | Timer1 clock input.                          |

|                                                 | SOSCO    | XTAL          | XTAL           | Secondary Oscillator Connection.             |

| RC1/SOSCI/CCP2 <sup>(1)</sup>                   | RC1      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | SOSCI    | XTAL          | XTAL           | Secondary Oscillator Connection.             |

|                                                 | CCP2     | TTL/ST        |                | Capture input.                               |

| RC2/AN14/CCP1 <sup>(1)</sup>                    | RC2      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN14     | AN            | _              | ADC Channel 14 input.                        |

|                                                 | CCP1     | TTL/ST        | _              | Capture input.                               |

| RC3/AN15/SCK <sup>(1)</sup> /SCL <sup>(1)</sup> | RC3      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                 | AN15     | AN            | —              | ADC Channel 15 input.                        |

|                                                 | SCK      | TTL/ST        | —              | SPI clock input.                             |

|                                                 | 0.01     | 120           |                |                                              |

OD **Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ TTL = TTL compatible input ST

l<sup>2</sup>C

SCL

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers. 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

I<sup>2</sup>C clock.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

# PIC16(L)F1717/8/9

|          | .E 3-12: S            | 1            |       |       |       |       | CONTINU    |       |       | 1                    | i                            |

|----------|-----------------------|--------------|-------|-------|-------|-------|------------|-------|-------|----------------------|------------------------------|

| Addr.    | Name                  | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other Resets |

| Bank 2   | 9                     | •            |       |       |       |       |            |       |       | •                    |                              |

| E8Ch     |                       |              |       |       |       |       |            |       |       |                      |                              |

| <br>E8Fh | _                     | Unimplemen   | ited  |       |       |       |            |       |       | _                    | —                            |

| E90h     | RA0PPS                | _            | _     | _     |       |       | RA0PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E91h     | RA1PPS                | —            | _     | —     |       |       | RA1PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E92h     | RA2PPS                | _            | _     | _     |       |       | RA2PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E93h     | RA3PPS                | _            | _     | —     |       |       | RA3PPS4:0  | >     |       | 0 0000               | u uuuu                       |

| E94h     | RA4PPS                | _            | —     | —     |       |       | RA4PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E95h     | RA5PPS                | —            | _     | —     |       |       | RA5PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E96h     | RA6PPS                | —            | —     | —     |       |       | RA6PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E97h     | RA7PPS                | —            | —     | —     |       |       | RA7PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E98h     | RB0PPS                | —            | —     | —     |       |       | RB0PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| E99h     | RB1PPS                | —            | —     | —     |       |       | RB1PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Ah     | RB2PPS                | —            | —     | —     |       |       | RB2PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Bh     | RB3PPS                | -            | -     | _     |       |       | RB3PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Ch     | RB4PPS                | —            | _     | _     |       |       | RB4PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Dh     | RB5PPS                | _            | _     | _     |       |       | RB5PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Eh     | RB6PPS                | —            | _     | _     |       |       | RB6PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| E9Fh     | RB7PPS                | —            | _     | _     |       |       | RB7PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA0h     | RC0PPS                | _            | —     | —     |       |       | RC0PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA1h     | RC1PPS                | _            | —     | —     |       |       | RC1PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA2h     | RC2PPS                | _            | —     | —     |       |       | RC2PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA3h     | RC3PPS                | _            | —     | —     |       |       | RC3PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA4h     | RC4PPS                | _            | —     | —     |       |       | RC4PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA5h     | RC5PPS                | —            | —     | —     |       |       | RC5PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA6h     | RC6PPS                | _            | —     | —     |       |       | RC6PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EA7h     | RC7PPS                | -            | _     | —     |       |       | RC7PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EA8h     | RD0PPS <sup>(1)</sup> | —            | —     | —     |       |       | RD0PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EA9h     | RD1PPS <sup>(1)</sup> | —            | —     | _     |       |       | RD1PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EAAh     | RD2PPS <sup>(1)</sup> | —            | —     | —     |       |       | RD2PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EABh     | RD3PPS <sup>(1)</sup> | -            | _     | —     |       |       | RD3PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EACh     | RD4PPS <sup>(1)</sup> | _            | _     | _     |       |       | RD4PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EADh     | RD5PPS <sup>(1)</sup> | _            | _     | _     |       |       | RD5PPS<4:0 | )>    |       | 0 0000               | u uuuu                       |

| EAEh     | RD6PPS <sup>(1)</sup> | _            |       | _     |       |       | RD6PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EAFh     |                       |              | _     |       |       |       | RD7PPS<4:0 |       |       | 0 0000               | u uuuu                       |

|          | RD7PPS <sup>(1)</sup> | —            |       |       |       |       |            |       |       |                      |                              |

| EB0h     | RE0PPS <sup>(1)</sup> | —            | _     | _     |       |       | RE0PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EB1h     | RE1PPS <sup>(1)</sup> | -            | —     | —     |       |       | RE1PPS<4:0 |       |       | 0 0000               | u uuuu                       |

| EB2h     | RE2PPS <sup>(1)</sup> | —            | —     | —     |       |       | RE2PPS<4:0 | >     |       | 0 0000               | u uuuu                       |

| EB3h     | _                     | Unimplemen   | ited  |       |       |       |            |       |       |                      |                              |

| <br>EEFh | _                     | onimpierrier | iteu  |       |       |       |            |       |       |                      | _                            |

TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented on PIC16(L)F1718.

2: Unimplemented on PIC16LF1717/8/9

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F170X Memory Programming Specification"* (DS41683).

# 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

# 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2.

When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

#### TABLE 10-2:USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8005h-8006h | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

| * PROG_ADD                             |                                            | 1 word of program memory at the memory address:<br>Dh-08h) data will be returned in the variables;<br>LO                                                                       |

|----------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BANKSEL<br>MOVLW<br>MOVWF<br>CLRF      | PMADRL<br>PROG_ADDR_LO<br>PMADRL<br>PMADRH | ; Select correct Bank<br>;<br>; Store LSB of address<br>; Clear MSB of address                                                                                                 |

| BSF<br>BCF<br>BSF<br>NOP<br>NOP<br>BSF | INTCON, GIE                                | <pre>; Select Configuration Space<br/>; Disable interrupts<br/>; Initiate read<br/>; Executed (See Figure 10-2)<br/>; Ignored (See Figure 10-2)<br/>; Restore interrupts</pre> |

| MOVF<br>MOVWF<br>MOVF<br>MOVWF         | PROG_DATA_LO                               | ; Get MSB of word                                                                                                                                                              |

| U-0              | U-0   | R/W-1/1           | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|------------------|-------|-------------------|---------|----------------|------------------|------------------|--------------|

| —                | —     | ANSB5             | ANSB4   | ANSB3          | ANSB2            | ANSB1            | ANSB0        |

| bit 7            |       | •                 |         |                |                  |                  | bit 0        |

|                  |       |                   |         |                |                  |                  |              |

| Legend:          |       |                   |         |                |                  |                  |              |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                  |                  |              |

|                  |       |                   |         |                |                  |                  |              |

#### REGISTER 11-12: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6

Unimplemented: Read as '0'

bit 5-0

ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 11-13: WPUB: WEAK PULL-UP PORTB REGISTER<sup>(1,2)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- **Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- **2:** The weak pull-up device is automatically disabled if the pin is configured as an output.

# 13.0 INTERRUPT-ON-CHANGE

All pins on all ports can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

# 13.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

# 13.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

### 13.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCxF bits.

# 13.4 Clearing Interrupt Flags

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the affected IOCxF register will be updated prior to the first instruction executed out of Sleep.

| R/W-0/0          | R/W-0/0                                                                                 | R/W-0/0                                                    | R/W-0/0                                                 | R/W-0/0                                               | R/W-0/0                       | R/W-0/0           | R/W-0/0    |

|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------|-------------------|------------|

| GxFSIM7          | GxFSIM6                                                                                 | GxFSIM5                                                    | GxFSIM4                                                 | GxFSIM3                                               | GxFSIM2                       | GxFSIM1           | GxFSIM0    |

| bit 7            |                                                                                         |                                                            |                                                         |                                                       |                               | •                 | bit (      |

|                  |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| Legend:          |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| R = Readable I   | pit                                                                                     | W = Writable                                               | bit                                                     | U = Unimplem                                          | nented bit, read              | as '0'            |            |

| u = Bit is uncha | anged                                                                                   | x = Bit is unkr                                            | iown                                                    | -n/n = Value a                                        | t POR and BOP                 | R/Value at all ot | her Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is clea                                          | ared                                                    | q = Value dep                                         | ends on conditi               | on                |            |

| bit 7            | <u>GxFIS7 = 1:</u><br>1 = NCO1_or                                                       |                                                            | ansition will ca                                        |                                                       | vent after falling<br>vent    | event phase de    | elay       |

|                  | <u>GxFIS7 = 0:</u>                                                                      |                                                            |                                                         |                                                       |                               |                   |            |

|                  | _                                                                                       | s no effect on f                                           | -                                                       |                                                       |                               |                   |            |

| bit 6            |                                                                                         | Gx Falling Eve                                             | ent Input Sourc                                         | e 6 Mode bit                                          |                               |                   |            |

|                  | 0 = PWM3 ou<br>GxFIS6 = 0:                                                              |                                                            | vill cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| oit 5            |                                                                                         | Gx Falling Eve                                             |                                                         |                                                       |                               |                   |            |

|                  | 0 = CCP2 ou<br>GxFIS5 = 0:                                                              |                                                            | rill cause an im                                        | cause a falling<br>mediate falling                    | event after fallin<br>event   | ng event phase    | delay      |

| bit 4            | GxFSIM4: CC                                                                             | Gx Falling Eve                                             | ent Input Sourc                                         | e 4 Mode bit                                          |                               |                   |            |

|                  | 0 = CCP1 low GxFIS4 = 0:                                                                | gh-to-low transi<br>v level will caus<br>effect on falling | e an immediat                                           |                                                       | after falling ever            | nt phase delay    |            |

| bit 3            |                                                                                         | )Gx Falling Eve                                            |                                                         | e 3 Mode bit                                          |                               |                   |            |

|                  | $\frac{GxFIS3 = 1}{1 = CLC1 \text{ out}}$ $0 = CLC1 \text{ out}$ $\frac{GxFIS3 = 0}{2}$ | tput high-to-low                                           | transition will<br>ill cause an im                      |                                                       | event after fallir<br>event   | ng event phase    | delay      |

| bit 2            |                                                                                         | )Gx Falling Eve                                            | ent Input Sourc                                         | e 2 Mode bit                                          |                               |                   |            |

|                  | 0 = Compara GxFIS2 = 0:                                                                 |                                                            | will cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| bit 1            | <b>GxFSIM1:</b> CC<br><u>GxFIS1 = 1:</u><br>1 = Compara                                 | OGx Falling Eve<br>tor 1 high-to-lo<br>tor 1 low level v   | nt Input Source<br>w transition wil<br>will cause an ir | e 1 Mode bit<br>I cause a falling<br>nmediate falling | g event after fall<br>g event | ing event phase   | e delay    |

# REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

# 19.6 Register Definitions: CLC Control

| R/W-0/0        |               | R-0/0                               | R/W-0/0         | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0     |

|----------------|---------------|-------------------------------------|-----------------|------------------|-----------------|-------------------|-------------|

|                |               | LCxOUT                              | LCxINTP         | LCXINTN          |                 | LCxMODE<2:0>      |             |

| bit 7          |               |                                     |                 |                  |                 |                   | bit         |

|                |               |                                     |                 |                  |                 |                   |             |

| Legend:        |               |                                     |                 |                  |                 |                   |             |

| R = Readab     | ole bit       | W = Writable                        | bit             | U = Unimpler     | nented bit, rea | d as '0'          |             |

| u = Bit is ur  | nchanged      | x = Bit is unki                     | nown            | -n/n = Value a   | at POR and BC   | DR/Value at all c | ther Resets |

| '1' = Bit is s | et            | '0' = Bit is cle                    | ared            |                  |                 |                   |             |

|                |               |                                     |                 |                  |                 |                   |             |

| bit 7          | LCxEN: Cont   | figurable Logic                     | Cell Enable b   | it               |                 |                   |             |

|                |               | able logic cell i                   |                 |                  |                 |                   |             |

| <b>h</b> # C   | •             | able logic cell i                   |                 | a has logic zero | output          |                   |             |

| bit 6          | •             | ted: Read as '                      |                 |                  |                 |                   |             |

| bit 5          |               | nfigurable Logi                     |                 | •                | from love out   |                   |             |

|                | -             | gic cell output                     |                 | •                | —               |                   |             |

| bit 4          |               | onfigurable Log                     |                 | 0 0              |                 | e bit             |             |

|                |               | will be set wher<br>will not be set | r a rising edge | e occurs on icx  | _oui            |                   |             |

| bit 3          | LCxINTN: Co   | onfigurable Log                     | ic Cell Negativ | ve Edae Goina    | Interrupt Enab  | ole bit           |             |

|                |               | will be set when                    | •               | • •              | •               |                   |             |

|                | 0 = CLCxIF    | will not be set                     |                 |                  | _               |                   |             |

| bit 2-0        | LCxMODE<2     | 2:0>: Configura                     | ble Logic Cell  | Functional Mo    | de bits         |                   |             |

|                |               | 1-input transpa                     |                 | h S and R        |                 |                   |             |

|                |               | J-K flip-flop wi                    |                 |                  |                 |                   |             |

|                |               | 2-input D flip-f                    |                 | ID               |                 |                   |             |

|                | 011 = Cell is | •                                   |                 |                  |                 |                   |             |

|                | 010 = Cell is |                                     |                 |                  |                 |                   |             |

|                | 001 = Cell is | •                                   |                 |                  |                 |                   |             |

|                | 000 = Cell is | AND-OR                              |                 |                  |                 |                   |             |

#### REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-x/u          | R/W-x/u     | R/W-x/u                              | R/W-x/u        | R/W-x/u                               | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------------|--------------------------------------|----------------|---------------------------------------|------------------|------------------|-------------|

| LCxG4D4T         | LCxG4D4N    | LCxG4D3T                             | LCxG4D3N       | LCxG4D2T                              | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |

| bit 7            |             | •                                    |                | · · · · · · · · · · · · · · · · · · · |                  | •                | bit         |

| Legend:          |             |                                      |                |                                       |                  |                  |             |

| R = Readable     | bit         | W = Writable                         | bit            | U = Unimpler                          | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged       | x = Bit is unkr                      | nown           | -n/n = Value a                        | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |             | '0' = Bit is cle                     | ared           |                                       |                  |                  |             |

|                  |             |                                      |                |                                       |                  |                  |             |

| bit 7            |             | Gate 4 Data 4 1                      |                | rted) bit                             |                  |                  |             |

|                  |             | is gated into L0<br>is not gated int |                |                                       |                  |                  |             |

| bit 6            |             | Gate 4 Data 4                        |                | ted) bit                              |                  |                  |             |

| bit o            |             | is gated into L                      | •              | ted) bit                              |                  |                  |             |

|                  |             | is not gated int                     |                |                                       |                  |                  |             |

| bit 5            | LCxG4D3T: ( | Gate 4 Data 3 1                      | True (non-inve | rted) bit                             |                  |                  |             |

|                  | 1 = LCxD3T  | is gated into L0                     | CxG4           |                                       |                  |                  |             |

|                  | 0 = LCxD3T  | is not gated int                     | o LCxG4        |                                       |                  |                  |             |

| bit 4            |             | Gate 4 Data 3                        | •              | rted) bit                             |                  |                  |             |

|                  |             | is gated into L                      |                |                                       |                  |                  |             |

| <b>h</b> # 0     |             | is not gated inf                     |                | ate al \ h it                         |                  |                  |             |

| bit 3            |             | Gate 4 Data 2 1<br>is gated into L0  | •              | nted) bit                             |                  |                  |             |

|                  |             | is not gated into L                  |                |                                       |                  |                  |             |

| bit 2            |             | Gate 4 Data 2                        |                | rted) bit                             |                  |                  |             |

|                  |             | is gated into L                      | •              | ,                                     |                  |                  |             |

|                  | 0 = LCxD2N  | is not gated int                     | to LCxG4       |                                       |                  |                  |             |

| bit 1            | LCxG4D1T: ( | Gate 4 Data 1 1                      | True (non-inve | rted) bit                             |                  |                  |             |

|                  |             | is gated into LO                     |                |                                       |                  |                  |             |

|                  |             | is not gated int                     |                |                                       |                  |                  |             |

| bit 0            |             | Gate 4 Data 1                        | •              | rted) bit                             |                  |                  |             |

|                  |             | is gated into Lo<br>is not gated inf |                |                                       |                  |                  |             |

|                  |             | ie not gated in                      |                |                                       |                  |                  |             |

# REGISTER 19-10: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

#### REGISTER 19-11: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | _   | MCL4OUT | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'         |

|---------|------------------------------------|

| bit 3   | MCL4OUT: Mirror copy of LC4OUT bit |

| bit 2   | MLC3OUT: Mirror copy of LC3OUT bit |

| bit 1   | MLC2OUT: Mirror copy of LC2OUT bit |

|         |                                    |

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

### TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name                  | Bit7     | Bit6     | Bit5     | Bit4        | Blt3     | Bit2        | Bit1       | Bit0     | Register<br>on Page |

|-----------------------|----------|----------|----------|-------------|----------|-------------|------------|----------|---------------------|

| ANSELA                | _        | -        | ANSA5    | ANSA4       | ANSA3    | ANSA2       | ANSA1      | ANSA0    | 125                 |

| ANSELB                | _        | _        | ANSB5    | ANSB4       | ANSB3    | ANSB2       | ANSB1      | ANSB0    | 131                 |

| ANSELC                | ANSC7    | ANSC6    | ANSC5    | ANSC4       | ANSC3    | ANSC2       | —          | —        | 136                 |

| ANSELD <sup>(1)</sup> | ANSD7    | ANSD6    | ANSD5    | ANSD4       | ANSD3    | ANSD2       | ANSD1      | ANSD0    | 141                 |

| CLC1CON               | LC1EN    |          | LC10UT   | LC1INTP     | LC1INTN  | L           | C1MODE<2:0 | )>       | 224                 |

| CLC2CON               | LC2EN    | _        | LC2OUT   | LC2INTP     | LC2INTN  | L           | C2MODE<2:0 | )>       | 224                 |

| CLC3CON               | LC3EN    |          | LC3OUT   | LC3INTP     | LC3INTN  | L           | C3MODE<2:0 | )>       | 224                 |

| CLCDATA               | _        |          |          |             | MCL4OUT  | MLC3OUT     | MLC2OUT    | MLC1OUT  | 231                 |

| CLC1GLS0              | LC1G1D4T | LC1G1D4N | LC1G1D3T | LC1G1D3N    | LC1G1D2T | LC1G1D2N    | LC1G1D1T   | LC1G1D1N | 227                 |

| CLC1GLS1              | LC1G2D4T | LC1G2D4N | LC1G2D3T | LC1G2D3N    | LC1G2D2T | LC1G2D2N    | LC1G2D1T   | LC1G2D1N | 228                 |

| CLC1GLS2              | LC1G3D4T | LC1G3D4N | LC1G3D3T | LC1G3D3N    | LC1G3D2T | LC1G3D2N    | LC1G3D1T   | LC1G3D1N | 229                 |

| CLC1GLS3              | LC1G4D4T | LC1G4D4N | LC1G4D3T | LC1G4D3N    | LC1G4D2T | LC1G4D2N    | LC1G4D1T   | LC1G4D1N | 230                 |

| CLC1POL               | LC1POL   |          |          |             | LC1G4POL | LC1G3POL    | LC1G2POL   | LC1G1POL | 225                 |

| CLC1SEL0              | _        |          |          |             |          | LC1D1S<4:0> | •          |          | 225                 |

| CLC1SEL1              | —        | _        |          |             |          | LC1D2S<4:0> | •          |          | 226                 |

| CLC1SEL2              | _        |          |          |             |          | LC1D3S<4:0> | •          |          | 226                 |

| CLC1SEL3              |          |          |          |             |          | LC1D4S<4:0> | ,          |          | 226                 |

| CLC2GLS0              | LC2G1D4T | LC2G1D4N | LC2G1D3T | LC2G1D3N    | LC2G1D2T | LC2G1D2N    | LC2G1D1T   | LC2G1D1N | 227                 |

| CLC2GLS1              | LC2G2D4T | LC2G2D4N | LC2G2D3T | LC2G2D3N    | LC2G2D2T | LC2G2D2N    | LC2G2D1T   | LC2G2D1N | 228                 |

| CLC2GLS2              | LC2G3D4T | LC2G3D4N | LC2G3D3T | LC2G3D3N    | LC2G3D2T | LC2G3D2N    | LC2G3D1T   | LC2G3D1N | 229                 |

| CLC2GLS3              | LC2G4D4T | LC2G4D4N | LC2G4D3T | LC2G4D3N    | LC2G4D2T | LC2G4D2N    | LC2G4D1T   | LC2G4D1N | 230                 |

| CLC2POL               | LC2POL   | _        | -        | _           | LC2G4POL | LC2G3POL    | LC2G2POL   | LC2G1POL | 225                 |

| CLC2SEL0              | —        | _        | _        | LC2D1S<4:0> |          |             |            | 225      |                     |

| CLC2SEL1              | —        | —        | —        |             |          | LC2D2S<4:0> | ,          |          | 226                 |

| CLC2SEL2              | _        | _        | _        |             |          | LC2D3S<4:0> | •          |          | 226                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for CLC module.

**Note 1:** PIC16(L)F1717/9 only.

|                                   |                                              |                   |                                    | •                                                     | •       |         |         |

|-----------------------------------|----------------------------------------------|-------------------|------------------------------------|-------------------------------------------------------|---------|---------|---------|

| R/W-x/u                           | R/W-x/u                                      | R/W-x/u           | R/W-x/u                            | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |

| ADRES                             | S<1:0>                                       | —                 | —                                  | —                                                     |         |         | —       |

| bit 7                             |                                              |                   |                                    |                                                       |         |         | bit 0   |

|                                   |                                              |                   |                                    |                                                       |         |         |         |

| Legend:                           |                                              |                   |                                    |                                                       |         |         |         |

| R = Readable bit W = Writable bit |                                              | bit               | U = Unimplemented bit, read as '0' |                                                       |         |         |         |

| u = Bit is unch                   | u = Bit is unchanged x = Bit is unknown      |                   | iown                               | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |

| '1' = Bit is set                  |                                              | '0' = Bit is clea | ared                               |                                                       |         |         |         |

|                                   |                                              |                   |                                    |                                                       |         |         |         |

| bit 7-6                           | bit 7-6 ADRES<1:0>: ADC Result Register bits |                   |                                    |                                                       |         |         |         |

#### **REGISTER 21-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| bit 7-6 | ADRES<1:0>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Lower two bits of 10-bit conversion result |

| bit 5-0 | Reserved: Do not use.                      |

#### REGISTER 21-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| —       | —       |         | —       | —       |         | ADRE    | S<9:8>  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-2 Reserved: Do not use.

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

#### REGISTER 21-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<7:0> |         |         |         |         |         |         |         |

| bit 7 bit  |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

# 27.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 27-1 displays the Timer1 enable selections.

| TABLE 27-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 27.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 27-2 displays the clock source selections.

#### 27.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 27.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 27-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                   |  |  |

|-------------|---------|--------------------------------|--|--|

| 11          | x       | LFINTOSC                       |  |  |

| 10          | 0       | External Clocking on T1CKI Pin |  |  |

| 01          | x       | System Clock (Fosc)            |  |  |

| 00          | x       | Instruction Clock (Fosc/4)     |  |  |

# 27.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 27.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 27.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 27.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 27.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 27.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 27.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 27-3 for timing details.

TABLE 27-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

#### REGISTER 30-5: SSP1MSK: SSP MASK REGISTER

| R/W-1/1                             | R/W-1/1                                                                                                                                                                                                                                                       | R/W-1/1                                         | R/W-1/1                                               | R/W-1/1                                         | R/W-1/1                               | R/W-1/1                    | R/W-1/1 |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|---------------------------------------|----------------------------|---------|--|

|                                     |                                                                                                                                                                                                                                                               |                                                 | MSł                                                   | <<7:0>                                          |                                       |                            |         |  |

| bit 7                               |                                                                                                                                                                                                                                                               |                                                 |                                                       |                                                 |                                       |                            | bit C   |  |

| Legend:                             |                                                                                                                                                                                                                                                               |                                                 |                                                       |                                                 |                                       |                            |         |  |

| R = Readabl                         | e bit                                                                                                                                                                                                                                                         | W = Writable                                    | bit                                                   | U = Unimplen                                    | mented bit, read                      | l as '0'                   |         |  |

| u = Bit is unchanged x = Bit is unk |                                                                                                                                                                                                                                                               | nown                                            | -n/n = Value at POR and BOR/Value at all other Resets |                                                 |                                       |                            |         |  |

| '1' = Bit is se                     | t                                                                                                                                                                                                                                                             | '0' = Bit is cle                                | ared                                                  |                                                 |                                       |                            |         |  |

| bit 7-1                             | <b>MSK&lt;7:1&gt;:</b><br>1 = The rec<br>0 = The rec                                                                                                                                                                                                          | Mask bits<br>eived address b<br>eived address b | it n is compai<br>it n is not use                     | red to SSP1ADI<br>ed to detect I <sup>2</sup> C | D <n> to detect<br/>address match</n> | I <sup>2</sup> C address m | atch    |  |

| bit 0                               | <b>MSK&lt;0&gt;:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSP1ADD<0> to detect I <sup>2</sup> C address match |                                                 |                                                       |                                                 |                                       |                            |         |  |

0 = The received address bit 0 is not used to detect  $I^2C$  address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

#### REGISTER 30-6: SSP1ADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADD     | <7:0>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

# 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 10-Bit Slave mode – Least Significant Address Byte: