#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-6: PIC16(L)F1718/9 MEMORY MAP, BANK 8-23

|               | BANK 8                        |               | BANK 9                        |              | BANK 10                       |               | BANK 11                       |              | BANK 12                       |              | BANK 13                       |              | BANK 14                       |               | BANK 15                       |

|---------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|

| 400h          |                               | 480h          |                               | 500h         |                               | 580h          |                               | 600h         |                               | 680h         |                               | 700h         |                               | 780h          |                               |

|               | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |

| 40Bh          |                               | 48Bh          |                               | 50Bh         |                               | 58Bh          |                               | 60Bh         |                               | 68Bh         |                               | 70Bh         |                               | 78Bh          |                               |

| 40Ch          | _                             | 48Ch          | —                             | 50Ch         | _                             | 58Ch          | —                             | 60Ch         |                               | 68Ch         | —                             | 70Ch         |                               | 78Ch          | _                             |

| 40Dh          | —                             | 48Dh          | —                             | 50Dh         | —                             | 58Dh          | —                             | 60Dh         |                               | 68Dh         | —                             | 70Dh         |                               | 78Dh          | —                             |

| 40Eh          | —                             | 48Eh          | _                             | 50Eh         | —                             | 58Eh          | _                             | 60Eh         | _                             | 68Eh         |                               | 70Eh         | _                             | 78Eh          | _                             |

| 40Fh          | —                             | 48Fh          | _                             | 50Fh         | —                             | 58Fh          | _                             | 60Fh         | _                             | 68Fh         | —                             | 70Fh         | _                             | 78Fh          | _                             |

| 410h          | —                             | 490h          | _                             | 510h         |                               | 590h          | —                             | 610h         | _                             | 690h         | -                             | 710h         | _                             | 790h          | _                             |

| 411h          | _                             | 491h          |                               | 511h         | OPA1CON                       | 591h          |                               | 611h         |                               | 691h         | COG1PHR<br>COG1PHF            | 711h         |                               | 791h          |                               |

| 412h          | —                             | 492h          | _                             | 512h         | _                             | 592h          |                               | 612h         |                               | 692h         |                               | 712h         |                               | 792h          | _                             |

| 413h          | _                             | 493h          |                               | 513h         | _                             | 593h          | _                             | 613h         |                               | 693h         | COG1BLKR<br>COG1BLKF          | 713h         |                               | 793h          |                               |

| 414h          | <br>TMR4                      | 494h          |                               | 514h         | <br>OPA2CON                   | 594h          |                               | 614h         |                               | 694h         | COGIDER                       | 714h         |                               | 794h<br>795h  |                               |

| 415h          |                               | 495h          |                               | 515h         |                               | 595h          |                               | 615h         |                               | 695h         | COG1DBR                       | 715h         |                               |               |                               |

| 416h<br>417h  | PR4<br>T4CON                  | 496h<br>497h  |                               | 516h<br>517h | _                             | 596h<br>597h  | _                             | 616h<br>617h | PWM3DCL                       | 696h<br>697h | COG1CON0                      | 716h<br>717h |                               | 796h<br>797h  | _                             |

| 41711<br>418h |                               | 49711<br>498h | NC01ACCL                      | 517n<br>518h |                               | 597n<br>598h  |                               | 618h         | PWM3DCL<br>PWM3DCH            | 698h         | COG1CON0                      | 717h         |                               | 797n<br>798h  |                               |

| 41011<br>419h |                               | 49011<br>499h | NCO1ACCE<br>NCO1ACCH          | 510h         |                               | 590h          |                               | 619h         | PWM3DCH<br>PWM3CON            | 699h         | COG1RIS                       | 719h         |                               | 7901<br>799h  |                               |

| 41911<br>41Ah |                               | 49911<br>49Ah | NCO1ACCU                      | 519h         |                               | 59911<br>59Ah |                               | 61Ah         | PWM4DCL                       | 69Ah         | COG1RSIM                      | 71Ah         |                               | 79911<br>79Ah |                               |

| 41An          |                               | 49An<br>49Bh  | NCOTINCL                      | 51An<br>51Bh |                               | 59An<br>59Bh  |                               | 61Bh         | PWM4DCL<br>PWM4DCH            | 69Bh         | COG1FIS                       | 71Bh         |                               | 79An<br>79Bh  |                               |

| 41Ch          | <br>TMR6                      | 49Ch          | NCO1INCH                      | 51Ch         |                               | 59Ch          |                               | 61Ch         | PWM4CON                       | 69Ch         | COG1FSIM                      | 71Ch         |                               | 79Ch          |                               |

| 41Dh          | PR6                           | 49Dh          | NCO1INCU                      | 51Dh         |                               | 59Dh          |                               | 61Dh         |                               | 69Dh         | COG1ASD0                      | 71Dh         |                               | 79Dh          |                               |

| 41Eh          | TECON                         | 49Eh          | NCO1CON                       | 51Eh         |                               | 59Eh          |                               | 61Eh         |                               | 69Eh         | COG1ASD1                      | 71Eh         |                               | 79Eh          |                               |

| 41Fh          | _                             | 49Fh          | NCO1CLK                       | 51Fh         |                               | 59Fh          |                               | 61Fh         |                               | 69Fh         | COG1STR                       | 71Fh         |                               | 79Eh          |                               |

| 420h          |                               | 4A0h          | NOOTOEN                       | 520h         |                               | 5A0h          |                               | 620h         |                               | 6A0h         | 00010111                      | 720h         |                               | 7A0h          |                               |

| -             | General                       | -             | General                       |              | General                       |               | General                       |              | General                       |              | General                       | _            | General                       | -             | General                       |

|               | Purpose                       |               | Purpose                       |              | Purpose                       |               | Purpose                       |              | Purpose                       |              | Purpose                       |              | Purpose                       |               | Purpose                       |

|               | Register                      |               | Register                      |              | Register                      |               | Register                      |              | Register                      |              | Register                      |              | Register                      |               | Register                      |

|               | 80 Bytes                      |               | 80 Bytes                      |              | 80 Bytes                      |               | 80 Bytes                      |              | 80 Bytes                      |              | 80 Bytes                      |              | 80 Bytes                      |               | 80 Bytes                      |

| 46Fh          |                               | 4EFh          |                               | 56Fh         |                               | 5EFh          |                               | 66Fh         |                               | 6EFh         |                               | 76Fh         |                               | 7EFh          |                               |

| 470h          |                               | 4F0h          |                               | 570h         |                               | 5F0h          |                               | 670h         |                               | 6F0h         |                               | 770h         |                               | 7F0h          |                               |

|               | Accesses                      |               | Accesses                      |              | Accesses                      |               | Accesses                      |              | Accesses                      |              | Accesses                      |              | Accesses                      |               | Accesses                      |

|               | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |

| 47Fh          |                               | 4FFh          |                               | 57Fh         |                               | 5FFh          |                               | 67Fh         |                               | 6FFh         |                               | 77Fh         |                               | 7FFh          |                               |

|               | BANK 16                       |               | BANK 17                       |              | BANK 18                       |               | BANK 19                       |              | BANK 20                       |              | BANK 21                       |              | BANK 22                       |               | BANK 23                       |

| 800h          |                               | 880h          |                               | 900h         |                               | 980h          |                               | A00h         |                               | A80h         |                               | B00h         |                               | B80h          |                               |

|               | Core Registers                |               | Core Registers                |              | Core Registers                |               | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |               | Core Registers                |

|               | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |

| 80Bh          |                               | 88Bh          |                               | 90Bh         |                               | 98Bh          |                               | A0Bh         |                               | A8Bh         |                               | B0Bh         |                               | B8Bh          |                               |

| 80Ch          | General                       | 88Ch          | General                       | 90Ch         | General                       | 98Ch          | General                       | A0Ch         | General                       | A8Ch         | General                       | B0Ch         | General                       | B8Ch          | General                       |

|               | Purpose                       | 50.011        | Purpose                       | 20011        | Purpose                       | 20011         | Purpose                       |              | Purpose                       | 1.0011       | Purpose                       | 20011        | Purpose                       | 20011         | Purpose                       |

|               | Register                      |               | Register                      |              | Register                      |               | Register                      |              | Register                      |              | Register                      |              | Register                      |               | Register                      |

|               | 80 Bytes                      | 000           | 80 Bytes                      |              | 80 Bytes                      | 9EFh          | 80 Bytes                      |              | 80 Bytes                      | AEFh         | 80 Bytes                      | DOC          | 80 Bytes                      | BEFh          | 80 Bytes                      |

| 86Fh          | <b>,</b>                      | 8EFh          | <b>,</b>                      | 96Fh         | <b>,</b>                      | -             | <b>,</b>                      | A6Fh         | ,                             |              | ,                             | B6Fh         | ,                             |               | <b>,</b>                      |

| 870h          | A                             | 8F0h          | A                             | 970h         | A                             | 9F0h          | A                             | A70h         | A                             | AF0h         | A                             | B70h         | A                             | BF0h          | A                             |

|               | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |

|               | /011 - /FII                   |               | 7011 - 7F11                   |              | /011 - /FII                   |               | /011 - /FII                   |              | -                             | :            | -                             |              | -                             |               | / UII - / FII                 |

| 87Fh          |                               | 8FFh          |                               | 97Fh         |                               | 9FFh          |                               | A7Fh         |                               | AFFh         |                               | B7Fh         |                               | BFFh          |                               |

Legend: = Unimplemented data memory locations, read as '0'.

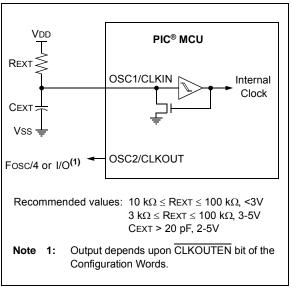

#### 6.2.1.6 External RC Mode

The external Resistor-Capacitor (EXTRC) mode supports the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 6-6 shows the external RC mode connections.

FIGURE 6-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- Threshold voltage variation

- Component tolerances

- Packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

## 6.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See **Section 6.3** "**Clock Switching**" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- 2. The **MFINTOSC** (Medium Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

# 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

### 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

### 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 27.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 6.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

# 6.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

#### 8.3 **Register Definitions: Voltage Regulator Control**

| U-0                                                                                           | U-0 | U-0               | U-0  | U-0          | U-0              | R/W-0/0     | R/W-1/1  |

|-----------------------------------------------------------------------------------------------|-----|-------------------|------|--------------|------------------|-------------|----------|

| —                                                                                             | —   | —                 | —    | —            | —                | VREGPM      | Reserved |

| bit 7                                                                                         |     |                   |      |              |                  |             | bit 0    |

|                                                                                               |     |                   |      |              |                  |             |          |

| Legend:                                                                                       |     |                   |      |              |                  |             |          |

| R = Readable                                                                                  | bit | W = Writable      | bit  | U = Unimpler | nented bit, read | as '0'      |          |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |     |                   |      |              |                  | ther Resets |          |

| '1' = Bit is set                                                                              |     | '0' = Bit is clea | ared |              |                  |             |          |

#### VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup> **REGISTER 8-1:**

bit 7-2 Unimplemented: Read as '0'

| hit | 1 |

|-----|---|

| DIL |   |

- VREGPM: Voltage Regulator Power Mode Selection bit 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- 0 = Normal-Power mode enabled in Sleep<sup>(2)</sup>

- Draws higher current in Sleep, faster wake-up

bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: PIC16F1717/8/9 only.

2: See Section 34.0 "Electrical Specifications".

#### **TABLE 8-1:** SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0    | Register<br>on Page |

|------------------------|-------|-------|-------|-------|--------|-------|--------|----------|---------------------|

| STATUS                 | _     | _     |       | TO    | PD     | Z     | DC     | С        | 28                  |

| VREGCON <sup>(1)</sup> | _     | _     | _     | _     | _      |       | VREGPM | Reserved | 101                 |

| WDTCON                 | _     |       |       | V     | SWDTEN | 104   |        |          |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode. Note 1: PIC16F1717/8/9 only.

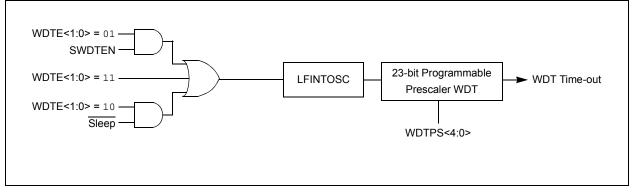

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

# FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

#### 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Table 34-8: Oscillator Parameters for the LFINTOSC specification.

# 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | v      | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

TABLE 9-1: WDT OPERATING MODES

| U-0              | U-0   | R/W-1/1           | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|------------------|-------|-------------------|---------|----------------|------------------|------------------|--------------|

| —                | —     | ANSB5             | ANSB4   | ANSB3          | ANSB2            | ANSB1            | ANSB0        |

| bit 7            |       | •                 |         |                |                  |                  | bit 0        |

|                  |       |                   |         |                |                  |                  |              |

| Legend:          |       |                   |         |                |                  |                  |              |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                  |                  |              |

|                  |       |                   |         |                |                  |                  |              |

#### REGISTER 11-12: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6

Unimplemented: Read as '0'

bit 5-0

ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 11-13: WPUB: WEAK PULL-UP PORTB REGISTER<sup>(1,2)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- **Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- **2:** The weak pull-up device is automatically disabled if the pin is configured as an output.

# 11.10 Register Definitions: PORTE

| U-0              | U-0   | U-0               | U-0  | R/W-x/u        | R/W-x/u            | R/W-x/u            | R/W-x/u            |

|------------------|-------|-------------------|------|----------------|--------------------|--------------------|--------------------|

| —                | —     | —                 | -    | RE3            | RE2 <sup>(2)</sup> | RE1 <sup>(2)</sup> | RE0 <sup>(2)</sup> |

| bit 7            |       |                   |      |                |                    |                    | bit 0              |

|                  |       |                   |      |                |                    |                    |                    |

| Legend:          |       |                   |      |                |                    |                    |                    |

| R = Readable b   | oit   | W = Writable I    | bit  | U = Unimpler   | nented bit, read   | as '0'             |                    |

| u = Bit is uncha | anged | x = Bit is unkn   | iown | -n/n = Value a | at POR and BOI     | R/Value at all o   | ther Resets        |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                |                    |                    |                    |

#### **REGISTER 11-33: PORTE: PORTE REGISTER**

| bit 7-4 | Unimplemented: Read as '0'                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | <b>RE&lt;3:0&gt;</b> : PORTE General Purpose I/O Pin bits <sup>(1)</sup><br>1 = Port pin is $\geq$ VIH<br>0 = Port pin is $\leq$ VIL |

- **Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

- 2: PIC16(L)F1717/9 only.

#### REGISTER 11-34: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1    | R/W-1/1               | R/W-1/1               | R/W-1/1               |

|-------|-----|-----|-----|--------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | —   | TRISE3 | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |        |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 3-0 **TRISE<3:0>:** PORTE Tri-State Control bits 1 = PORTE pin configured as an input (tri-stated) 0 = PORTE pin configured as an output

Note 1: PIC16(L)F1717/9 only.

# PIC16(L)F1717/8/9

| R/W-0/0          | R/W-0/0                                                                                                                    | R/W-0/0                                                     | R/W-0/0 | R/W-0/0       | R/W-0/0           | R/W-0/0    | R/W-0/0     |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|---------------|-------------------|------------|-------------|--|--|--|

| GxFIS7           | GxFIS6                                                                                                                     | GxFIS5                                                      | GxFIS4  | GxFIS3        | GxFIS2            | GxFIS1     | GxFIS0      |  |  |  |

| bit 7            |                                                                                                                            |                                                             |         |               |                   |            | bit 0       |  |  |  |

|                  |                                                                                                                            |                                                             |         |               |                   |            |             |  |  |  |

| Legend:          |                                                                                                                            |                                                             |         |               |                   |            |             |  |  |  |

| R = Readable     |                                                                                                                            | W = Writable                                                |         |               | nented bit, read  |            |             |  |  |  |

| u = Bit is unch  | anged                                                                                                                      | x = Bit is unki                                             |         |               | at POR and BO     |            | ther Resets |  |  |  |

| '1' = Bit is set |                                                                                                                            | '0' = Bit is cle                                            | ared    | q = Value dep | pends on condit   | ion        |             |  |  |  |

|                  |                                                                                                                            |                                                             |         |               |                   |            |             |  |  |  |

| bit 7            |                                                                                                                            | Gx Falling Ever                                             | •       |               |                   |            |             |  |  |  |

|                  |                                                                                                                            | out is enabled a<br>out has no effect                       |         |               |                   |            |             |  |  |  |

| bit 6            | _                                                                                                                          | Gx Falling Ever                                             | -       |               |                   |            |             |  |  |  |

|                  |                                                                                                                            | utput is enable                                             | •       |               |                   |            |             |  |  |  |

|                  |                                                                                                                            | = PWM3 has no effect on the falling event                   |         |               |                   |            |             |  |  |  |

| bit 5            | GxFIS5: CO                                                                                                                 | GxFIS5: COGx Falling Event Input Source 5 Enable bit        |         |               |                   |            |             |  |  |  |

|                  | 1 = CCP2 output is enabled as a falling event input                                                                        |                                                             |         |               |                   |            |             |  |  |  |

|                  |                                                                                                                            | utput has no eff                                            |         | •             |                   |            |             |  |  |  |

| bit 4            |                                                                                                                            | <b>ExFIS4:</b> COGx Falling Event Input Source 4 Enable bit |         |               |                   |            |             |  |  |  |

|                  | <ul> <li>1 = CCP1 is enabled as a falling event input</li> <li>0 = CCP1 has no effect on the falling event</li> </ul>      |                                                             |         |               |                   |            |             |  |  |  |

| bit 3            |                                                                                                                            | xFIS3: COGx Falling Event Input Source 3 Enable bit         |         |               |                   |            |             |  |  |  |

|                  | 1 = CLC1 output is enabled as a falling event input                                                                        |                                                             |         |               |                   |            |             |  |  |  |

|                  | 0 = CLC1 output has no effect on the falling event                                                                         |                                                             |         |               |                   |            |             |  |  |  |

| bit 2            |                                                                                                                            | GxFIS2: COGx Falling Event Input Source 2 Enable bit        |         |               |                   |            |             |  |  |  |

|                  | 1 = Comparator 2 output is enabled as a falling event input                                                                |                                                             |         |               |                   |            |             |  |  |  |

| bit 1            | •                                                                                                                          | = Comparator 2 output has no effect on the falling event    |         |               |                   |            |             |  |  |  |

|                  | <b>GxFIS1:</b> COGx Falling Event Input Source 1 Enable bit<br>1 = Comparator 1 output is enabled as a falling event input |                                                             |         |               |                   |            |             |  |  |  |

|                  |                                                                                                                            | ator 1 output is                                            |         |               |                   |            |             |  |  |  |

| bit 0            | •                                                                                                                          | Gx Falling Ever                                             |         | •             |                   |            |             |  |  |  |

|                  |                                                                                                                            | •                                                           |         |               | led as falling ev | vent input |             |  |  |  |

|                  | 0 = Pin seled                                                                                                              |                                                             |         | <b>.</b>      |                   |            |             |  |  |  |

# REGISTER 18-5: COG FALLING EVENT INPUT SELECTION REGISTER

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0                                             | R/W-0/0  | R/W-0/0         | R/W-0/0          | U-0               | U-0          |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------|-----------------|------------------|-------------------|--------------|--|

| GxASE            | GxARSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GxASDE                                              | 3D<1:0>  | GxASDAC<1:0>    |                  | —                 |              |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |          |                 |                  |                   | bit 0        |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |          |                 |                  |                   |              |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |          |                 |                  |                   |              |  |

| R = Readable     | Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |          |                 |                  |                   |              |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                                                                                                                                                                                                                    | x = Bit is unkr                                     | iown     | -n/n = Value at | POR and BOR      | /Value at all oth | ner Resets   |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is clea                                   | ared     | q = Value depe  | ends on conditio | n                 |              |  |

| bit 7            | bit 7 <b>GxASE:</b> Auto-Shutdown Event Status bit<br>1 = COG is in the shutdown state<br>0 = COG is either not in the shutdown state or will exit the shutdown state on the next rising even                                                                                                                                                                                                                                                             |                                                     |          |                 |                  |                   | sing event   |  |

| bit 6            | 1 = Auto-rest                                                                                                                                                                                                                                                                                                                                                                                                                                             | uto-Restart En<br>art is enabled<br>art is disabled | able bit |                 |                  |                   |              |  |

| bit 5-4          | <ul> <li>GxASDBD&lt;1:0&gt;: COGxB and COGxD Auto-shutdown Override Level Select bits</li> <li>11 = A logic '1' is placed on COGxB and COGxD when shutdown is active</li> <li>10 = A logic '0' is placed on COGxB and COGxD when shutdown is active</li> <li>01 = COGxB and COGxD are tri-stated when shutdown is active</li> <li>00 = The inactive state of the pin, including polarity, is placed on COGxB and COGxD when shutdown is active</li> </ul> |                                                     |          |                 |                  |                   |              |  |

| bit 3-2          |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |          |                 |                  |                   | hen shutdown |  |

| bit 1-0          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |          |                 |                  |                   |              |  |

# REGISTER 18-7: COGxASD0: COG AUTO-SHUTDOWN CONTROL REGISTER 0

#### REGISTER 18-14: COGxPHR: COG RISING EDGE PHASE DELAY COUNT REGISTER

| U-0     | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|-----|---------|---------|---------|---------|---------|---------|

| _       | _   |         |         | GxPH    | IR<5:0> |         |         |

| bit 7   |     |         |         |         |         |         | bit 0   |

|         |     |         |         |         |         |         |         |

| Legend: |     |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

GxPHR<5:0>: Rising Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay rising edge event

#### REGISTER 18-15: COGxPHF: COG FALLING EDGE PHASE DELAY COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   |         |         | GxPH    | F<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

GxPHF<5:0>: Falling Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay falling edge event

## 19.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 19-1).

- Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

# 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 19.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

# 19.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 19.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 21.2 ADC Operation

#### 21.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 21.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

# 21.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 21.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

### 21.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 21.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The auto-conversion trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Table 21-2 for auto-conversion sources.

#### TABLE 21-2: AUTO-CONVERSION SOURCES

| 0000020     |  |  |  |  |  |  |

|-------------|--|--|--|--|--|--|

| Signal Name |  |  |  |  |  |  |

| —           |  |  |  |  |  |  |

| —           |  |  |  |  |  |  |

| T0_overflow |  |  |  |  |  |  |

| T1_overflow |  |  |  |  |  |  |

| T2_match    |  |  |  |  |  |  |

| T4_match    |  |  |  |  |  |  |

| T6_match    |  |  |  |  |  |  |

| sync_C1OUT  |  |  |  |  |  |  |

| sync_C2OUT  |  |  |  |  |  |  |

| LC1_out     |  |  |  |  |  |  |

| LC2_out     |  |  |  |  |  |  |

| LC3_out     |  |  |  |  |  |  |

| LC4_out     |  |  |  |  |  |  |

|             |  |  |  |  |  |  |

# 26.2 Register Definitions: Option Register

| R/W-1/1         | R/W-1/1                  | R/W-1/1                                                                                                      | R/W-1/1  | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |

|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------------|----------|----------------|------------------|------------------|--------------|--|--|--|

| WPUEN           | INTEDG                   | TMR0CS                                                                                                       | TMR0SE   | PSA            |                  | PS<2:0>          |              |  |  |  |

| bit 7           |                          |                                                                                                              |          |                |                  |                  | bit (        |  |  |  |

|                 |                          |                                                                                                              |          |                |                  |                  |              |  |  |  |

| Legend:         |                          |                                                                                                              |          |                |                  |                  |              |  |  |  |

| R = Readabl     | e bit                    | W = Writable                                                                                                 | bit      | U = Unimpler   | nented bit, read | d as '0'         |              |  |  |  |

| u = Bit is und  | hanged                   | x = Bit is unk                                                                                               | nown     | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is se | t                        | '0' = Bit is cle                                                                                             | ared     |                |                  |                  |              |  |  |  |

|                 |                          |                                                                                                              |          |                |                  |                  |              |  |  |  |

| bit 7           | WPUEN: We                | ak Pull-Up Ena                                                                                               | able bit |                |                  |                  |              |  |  |  |

|                 |                          | 1 = All weak pull-ups are disabled (except $\overline{MCLR}$ , if it is enabled)                             |          |                |                  |                  |              |  |  |  |

|                 | -                        | ak pull-ups are enabled by individual WPUx latch values                                                      |          |                |                  |                  |              |  |  |  |

| bit 6           |                          | INTEDG: Interrupt Edge Select bit                                                                            |          |                |                  |                  |              |  |  |  |

|                 | •                        | 1 = Interrupt on rising edge of INT pin                                                                      |          |                |                  |                  |              |  |  |  |

| bit 5           |                          | <ul> <li>0 = Interrupt on falling edge of INT pin</li> <li>TMR0CS: Timer0 Clock Source Select bit</li> </ul> |          |                |                  |                  |              |  |  |  |

| DIL D           |                          | n on TOCKI pin                                                                                               |          |                |                  |                  |              |  |  |  |

|                 |                          | nstruction cycle                                                                                             |          | 4)             |                  |                  |              |  |  |  |

| bit 4           | TMR0SE: Til              | TMR0SE: Timer0 Source Edge Select bit                                                                        |          |                |                  |                  |              |  |  |  |

|                 | 1 = Incremer             | 1 = Increment on high-to-low transition on T0CKI pin                                                         |          |                |                  |                  |              |  |  |  |

|                 | 0 = Incremer             | 0 = Increment on low-to-high transition on T0CKI pin                                                         |          |                |                  |                  |              |  |  |  |

| bit 3           | PSA: Presca              | PSA: Prescaler Assignment bit                                                                                |          |                |                  |                  |              |  |  |  |

|                 |                          | 1 = Prescaler is not assigned to the Timer0 module                                                           |          |                |                  |                  |              |  |  |  |

|                 |                          | 0 = Prescaler is assigned to the Timer0 module                                                               |          |                |                  |                  |              |  |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pr | PS<2:0>: Prescaler Rate Select bits                                                                          |          |                |                  |                  |              |  |  |  |

|                 | Bit                      | Value Timer0                                                                                                 | Rate     |                |                  |                  |              |  |  |  |

|                 |                          | 000 1:2                                                                                                      |          |                |                  |                  |              |  |  |  |

|                 |                          | 001 1:4                                                                                                      |          |                |                  |                  |              |  |  |  |

|                 |                          | 010 1:8<br>011 1:1                                                                                           |          |                |                  |                  |              |  |  |  |

|                 |                          | 1.00                                                                                                         |          |                |                  |                  |              |  |  |  |

# REGISTER 26-1: OPTION\_REG: OPTION REGISTER

| TABLE 26-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0 |

|-------------|---------------------------------------------|

|             |                                             |

1 : 32 1 : 64

1:128

1:256

| Name       | Bit 7     | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|-----------|-------------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE       | PEIE        | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 90                  |

| OPTION_REG | WPUEN     | INTEDG      | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 270                 |

| TMR0       | Timer0 Mo | odule Regis | ter    |        |        |        |         |        | 268*                |

| TRISA      | TRISA7    | TRISA6      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 124                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

100

101

110

111

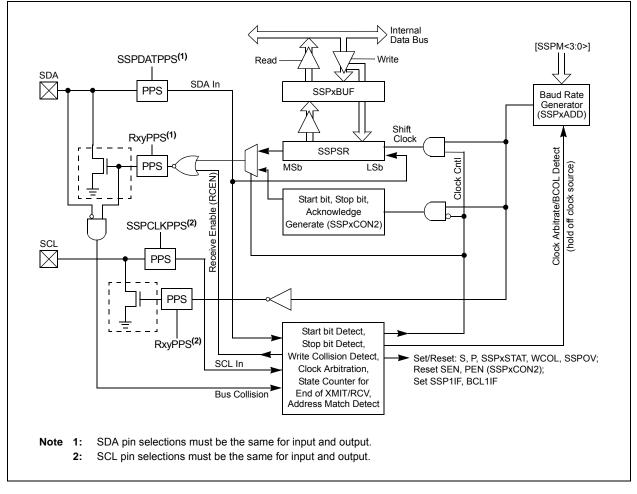

The  $I^2C$  interface supports the following modes and features:

- · Master mode

- · Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- · Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 30-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 30-3 is a diagram of the  $I^2C$  interface module in Slave mode.

# FIGURE 30-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

# PIC16(L)F1717/8/9

#### 31.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RC1STA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RC1REG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RC1STA register which resets the EUSART. Clearing the CREN bit of the RC1STA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |

|-------|------------------------------------------|

|       | FIFO have framing errors, repeated reads |

|       | of the RC1REG will not clear the FERR    |

|       | bit.                                     |

#### 31.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RC1STA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RC1STA register or by resetting the EUSART by clearing the SPEN bit of the RC1STA register.

#### 31.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RC1REG.

#### 31.1.2.7 Address Detection