Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

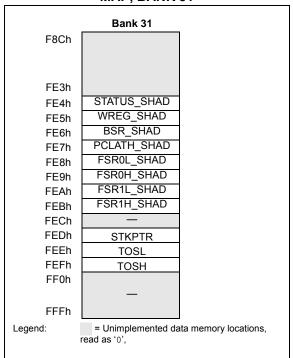

TABLE 3-10: PIC16(L)F1717/8/9 MEMORY MAP, BANK 31

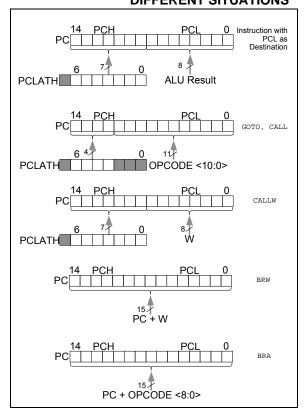

#### 3.5 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.5.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.5.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, "Implementing a Table Read" (DS00556).

#### 3.5.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.5.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching,  $_{\rm BRW}$  and  $_{\rm BRA}$ . The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

#### 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- · Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

### 6.3.1 SYSTEM CLOCK SELECT (SCS)

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

#### Note:

Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

### 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

#### 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 27.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

### 6.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

### 6.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

#### REGISTER 11-3: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| LATA7       | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7 bit 0 |         |         |         |         |         |         |         |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 LATA<7:0>: RA<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     |     | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0

ANSA<5:0>: Analog Select between Analog or Digital Function on Pins RA<5:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 11.3 PORTB Registers

#### 11.3.1 DATA REGISTER

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.3.2 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.3 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.4 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.3.5 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 11.3.6 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 11.3.7 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "Peripheral Pin Select (PPS) Module" for more information. Analog input functions, such as ADC and op amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

#### 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Note:

The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible and are the only pins on the device with this compatibility.

#### 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

### EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

```

; suspend interrupts

bcf

INTCON, GIE

BANKSEL PPSLOCK ; set bank

; required sequence, next 5 instructions

movlw

0x55

movwf

PPSLOCK

mov1w

AA \times 0

movwf PPSLOCK

; Set PPSLOCKED bit to disable writes or

; Clear PPSLOCKED bit to enable writes

PPSLOCK, PPSLOCKED

; restore interrupts

INTCON, GIE

bsf

```

#### 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

#### 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

#### 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in pin allocation Table 1.

#### 16.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 16-1) contains Control and Status bits for the following:

- Fnable

- Output

- · Output Polarity

- · Zero Latency Filter

- · Speed/Power Selection

- · Hysteresis Enable

- · Output Synchronization

The CMxCON1 register (see Register 16-2) contains Control bits for the following:

- · Interrupt Enable

- · Interrupt Edge Polarity

- · Positive Input Channel Selection

- · Negative Input Channel Selection

#### 16.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 16.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · Desired pin PPS control

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

Note 1: The internal output of the comparator is latched with each instruction cycle.

Unless otherwise specified, external outputs are not latched.

#### 16.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 16-2 shows the output state versus input conditions, including polarity control.

TABLE 16-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVn > CxVp     | 0     | 0     |

| CxVn < CxVp     | 0     | 1     |

| CxVn > CxVp     | 1     | 1     |

| CxVn < CxVp     | 1     | 0     |

### 16.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1', which selects the Normal-Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name                 | Bit 7          | Bit 6   | Bit 5   | Bit 4        | Bit 3        | Bit 2                 | Bit 1                 | Bit 0                 | Register on Page |

|----------------------|----------------|---------|---------|--------------|--------------|-----------------------|-----------------------|-----------------------|------------------|

| CCPTMRS              | P4TSE          | L<1:0>  | P3TSE   | L<1:0>       | C2TSE        | L<1:0>                | C1TSE                 | L<1:0>                | 286              |

| PR2                  |                |         | Tim     | er2 module P | eriod Regist | er                    |                       |                       | 282              |

| PWM3CON              | PWM3EN         | _       | PWM3OUT | PWM3POL      | _            | _                     | _                     | _                     | 181              |

| PWM3DCH              |                |         |         | PWM3DC       | H<7:0>       |                       |                       |                       | 181              |

| PWM3DCL              | PWM3DCL<1:0> — |         |         | _            | _            | _                     | _                     | _                     | 181              |

| PWM4CON              | PWM4EN         | _       | PWM4OUT | PWM4POL      | _            | _                     | _                     | _                     | 181              |

| PWM4DCH              | PWM4DCH<7:0>   |         |         |              |              |                       |                       | 181                   |                  |

| PWM4DCL              | PWM4D          | CL<1:0> | _       | _            | _            | _                     | _                     | _                     | 181              |

| TRISA                | TRISA7         | TRISA6  | TRISA5  | TRISA4       | TRISA3       | TRISA2                | TRISA1                | TRISA0                | 124              |

| TRISB                | TRISB7         | TRISB6  | TRISB5  | TRISB4       | TRISB3       | TRISB2                | TRISB1                | TRISB0                | 130              |

| TRISC                | TRISC7         | TRISC6  | TRISC5  | TRISC4       | TRISC3       | TRISC2                | TRISC1                | TRISC0                | 135              |

| TRISD <sup>(1)</sup> | TRISD7         | TRISD6  | TRISD5  | TRISD4       | TRISD3       | TRISD2                | TRISD1                | TRISD0                | 140              |

| TRISE                | _              | _       | _       | _            | TRISE3       | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 145              |

| RxyPPS               |                |         | _       |              | R            | kyPPS<4:0>            |                       |                       | 153              |

| T2CON                | _              |         | T2OUTI  | PS<3:0>      |              | TMR2ON                | T2CKP                 | S<1:0>                | 284              |

| TMR2                 |                | ·       |         | Timer2 modul | le Register  | ·                     | ·                     |                       | 282              |

**Legend:** – = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM

Note 1: PIC16(L)F1717/9 only.

#### REGISTER 18-5: COGxFIS: COG FALLING EVENT INPUT SELECTION REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| GxFIS7  | GxFIS6  | GxFIS5  | GxFIS4  | GxFIS3  | GxFIS2  | GxFIS1  | GxFIS0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7  | GxFIS7: COGx Falling Event Input Source 7 Enable bit                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------|

|        | <ul><li>1 = NCO1_out is enabled as a falling event input</li><li>0 = NCO1 out has no effect on the falling event</li></ul> |

| 1 '' 0 | _                                                                                                                          |

| bit 6  | GxFIS6: COGx Falling Event Input Source 6 Enable bit                                                                       |

|        | 1 = PWM3 output is enabled as a falling event input                                                                        |

|        | 0 = PWM3 has no effect on the falling event                                                                                |

| bit 5  | GxFIS5: COGx Falling Event Input Source 5 Enable bit                                                                       |

|        | 1 = CCP2 output is enabled as a falling event input                                                                        |

|        | 0 = CCP2 output has no effect on the falling event                                                                         |

| bit 4  | GxFIS4: COGx Falling Event Input Source 4 Enable bit                                                                       |

|        | 1 = CCP1 is enabled as a falling event input                                                                               |

|        | 0 = CCP1 has no effect on the falling event                                                                                |

| bit 3  | GxFIS3: COGx Falling Event Input Source 3 Enable bit                                                                       |

|        | 1 = CLC1 output is enabled as a falling event input                                                                        |

|        | 0 = CLC1 output has no effect on the falling event                                                                         |

| bit 2  | GxFIS2: COGx Falling Event Input Source 2 Enable bit                                                                       |

|        | 1 = Comparator 2 output is enabled as a falling event input                                                                |

|        | 0 = Comparator 2 output has no effect on the falling event                                                                 |

| bit 1  | GxFIS1: COGx Falling Event Input Source 1 Enable bit                                                                       |

|        | 1 = Comparator 1 output is enabled as a falling event input                                                                |

|        | 0 = Comparator 1 output has no effect on the falling event                                                                 |

| bit 0  | GxFIS0: COGx Falling Event Input Source 0 Enable bit                                                                       |

|        | 1 = Pin selected with COGxPPS control register is enabled as falling event input                                           |

|        | 0 = Pin selected with COGxPPS control has no effect on the falling event                                                   |

#### REGISTER 18-10: COGxDBR: COG RISING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|

| _     | _   |         | GxDBR<5:0> |         |         |         |         |  |

| bit 7 |     |         |            |         |         |         | bit 0   |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 GxDBR<5:0>: Rising Event Dead-band Count Value bits

GxRDBS = 1:

= Number of delay chain element periods to delay primary output after rising event

GxRDBS = 0:

= Number of COGx clock periods to delay primary output after rising event

#### REGISTER 18-11: COGxDBF: COG FALLING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|

| _     | _   |         | GxDBF<5:0> |         |         |         |         |  |

| bit 7 |     | •       |            |         |         |         | bit 0   |  |

| Lec | ae | n | d |   |

|-----|----|---|---|---|

| ;   | "  |   | • | • |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 GxDBF<5:0>: Falling Event Dead-band Count Value bits

GxFDBS = 1:

Number of delay chain element periods to delay complementary output after falling event input GxFDBS = 0:

= Number of COGx clock periods to delay complementary output after falling event input

#### 19.6 Register Definitions: CLC Control

#### REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 |

|---------|-----|--------|---------|---------|---------|-------------|---------|

| LCxEN   | _   | LCxOUT | LCxINTP | LCxINTN | L       | CxMODE<2:0> | •       |

| bit 7   | •   |        |         |         |         |             | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | LCxEN: Configurable Logic Cell Enable bit                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Configurable logic cell is enabled and mixing input signals</li><li>0 = Configurable logic cell is disabled and has logic zero output</li></ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 5   | LCxOUT: Configurable Logic Cell Data Output bit                                                                                                             |

|         | Read-only: logic cell output data, after LCxPOL; sampled from lcx_out wire.                                                                                 |

| bit 4   | LCxINTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit                                                                                   |

|         | 1 = CLCxIF will be set when a rising edge occurs on lcx_out                                                                                                 |

|         | 0 = CLCxIF will not be set                                                                                                                                  |

| bit 3   | LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit                                                                                   |

|         | 1 = CLCxIF will be set when a falling edge occurs on lcx_out                                                                                                |

|         | 0 = CLCxIF will not be set                                                                                                                                  |

| bit 2-0 | LCxMODE<2:0>: Configurable Logic Cell Functional Mode bits                                                                                                  |

|         | 111 = Cell is 1-input transparent latch with S and R                                                                                                        |

|         | 110 = Cell is J-K flip-flop with R                                                                                                                          |

|         | 101 = Cell is 2-input D flip-flop with R                                                                                                                    |

|         | 100 = Cell is 1-input D flip-flop with S and R                                                                                                              |

|         | 011 = Cell is S-R latch                                                                                                                                     |

|         | 010 = Cell is 4-input AND                                                                                                                                   |

|         | 001 = Cell is OR-XOR                                                                                                                                        |

|         | 000 = Cell is AND-OR                                                                                                                                        |

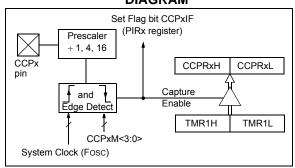

### 29.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1 and CCP2).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

#### 29.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 29-1 shows a simplified diagram of the capture operation.

#### 29.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

# FIGURE 29-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

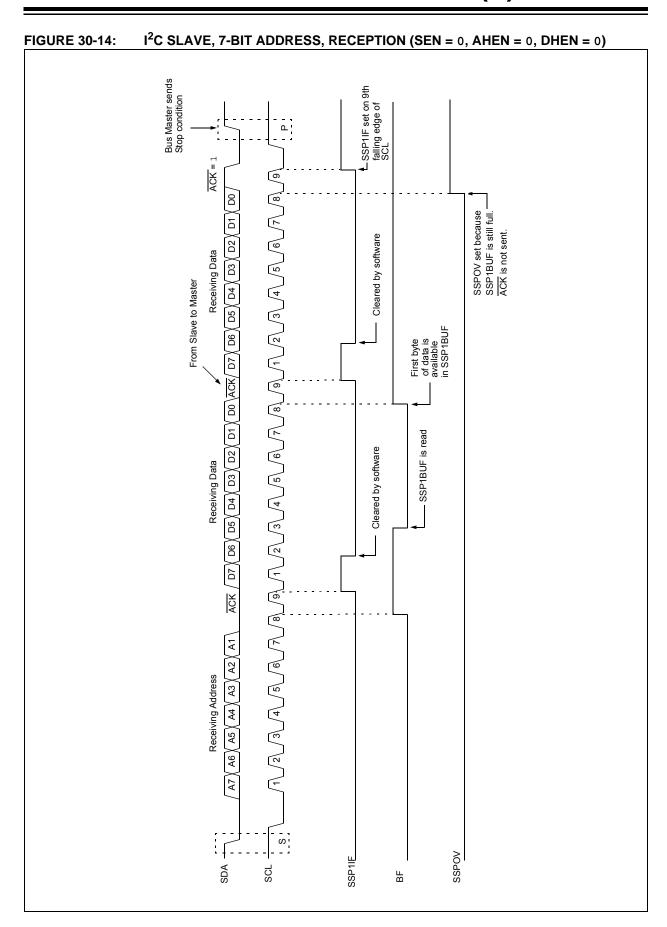

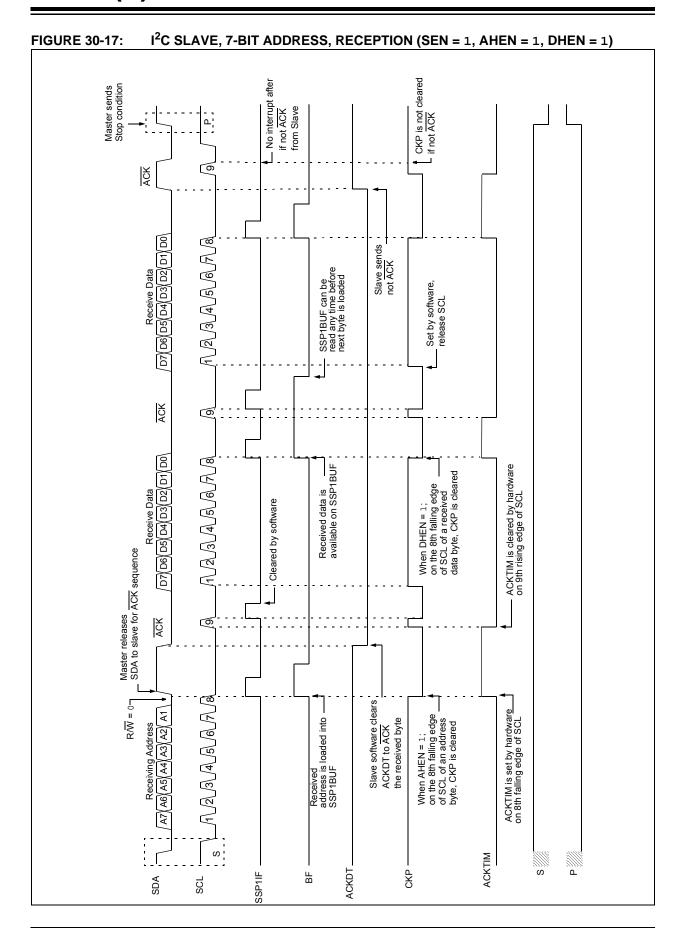

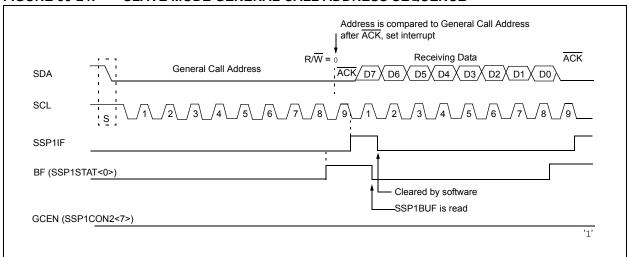

### 30.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the  $R/\overline{W}$  bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 30-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 30-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 30.5.9 SSP MASK REGISTER

An SSP Mask (SSP1MSK) register (Register 30-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of SSP1ADD<7:1>.

- 10-bit Address mode: address compare of SSP1ADD<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name      | Bit 7                                                    | Bit 6           | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>Page |

|-----------|----------------------------------------------------------|-----------------|--------|--------|--------|--------|--------|--------|----------------------------|

| ANSELB    | _                                                        | _               | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 131                        |

| ANSELC    | ANSC7                                                    | ANSC6           | ANSC5  | ANSC4  | ANSC3  | ANSC2  | _      | _      | 136                        |

| INTCON    | GIE                                                      | PEIE            | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                         |

| PIE1      | TMR1GIE                                                  | ADIE            | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 91                         |

| PIE2      | OSFIE                                                    | C2IE            | C1IE   | _      | BCL1IE | TMR6IE | TMR4IE | CCP2IE | 92                         |

| PIR1      | TMR1GIF                                                  | ADIF            | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 94                         |

| PIR2      | OSFIF                                                    | C2IF            | C1IF   | _      | BCL1IF | TMR6IF | TMR4IF | CCP2IF | 95                         |

| RxyPPS    | _                                                        | — — RxyPPS<4:0> |        |        |        | 153    |        |        |                            |

| SSPCLKPPS | _                                                        | SSPCLKPPS<4:0>  |        |        |        | 152    |        |        |                            |

| SSPDATPPS | SSPDATPPS<4:0>                                           |                 |        |        | 152    |        |        |        |                            |

| SSP1ADD   |                                                          | ADD<7:0>        |        |        |        |        | 350    |        |                            |

| SSP1BUF   | Synchronous Serial Port Receive Buffer/Transmit Register |                 |        |        | 299*   |        |        |        |                            |

| SSP1CON1  | WCOL                                                     | SSPOV           | SSPEN  | CKP    |        | SSPN   | 1<3:0> |        | 346                        |

| SSP1CON2  | GCEN                                                     | ACKSTAT         | ACKDT  | ACKEN  | RCEN   | PEN    | RSEN   | SEN    | 348                        |

| SSP1CON3  | ACKTIM                                                   | PCIE            | SCIE   | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN   | 349                        |

| SSP1MSK   | MSK<7:0>                                                 |                 |        |        |        | 350    |        |        |                            |

| SSP1STAT  | SMP                                                      | CKE             | D/A    | Р      | S      | R/W    | UA     | BF     | 345                        |

| TRISB     | TRISB7                                                   | TRISB6          | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 130                        |

| TRISC     | TRISC7                                                   | TRISC6          | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 135                        |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

<sup>\*</sup> Page provides register information.

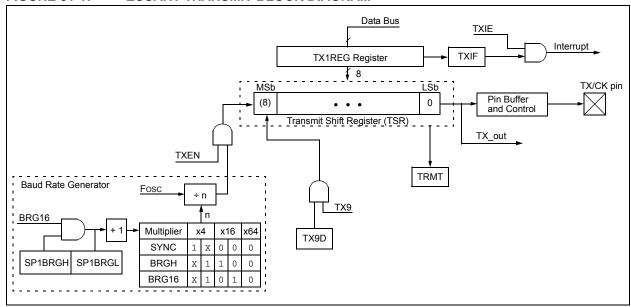

# 31.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 31-1 and Figure 31-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

• Configurable Logic Cell (CLC)

FIGURE 31-1: EUSART TRANSMIT BLOCK DIAGRAM

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVIW ++FSRn<br>[ label ] MOVIWFSRn<br>[ label ] MOVIW FSRn++<br>[ label ] MOVIW FSRn<br>[ label ] MOVIW k[FSRn]                                                                                                                 |

| Operands:        | $n \in [0,1]$<br>$mm \in [00,01, 10, 11]$<br>$-32 \le k \le 31$                                                                                                                                                                            |

| Operation:       | INDFn → W Effective address is determined by • FSR + 1 (preincrement) • FSR - 1 (predecrement) • FSR + k (relative offset) After the Move, the FSR value will be either: • FSR + 1 (all increments) • FSR - 1 (all decrements) • Unchanged |

| Status Affected: | Z                                                                                                                                                                                                                                          |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to

wrap-around.

#### MOVLB Move literal to BSR

| Syntax: [ label ] MOVLB | k |

|-------------------------|---|

|-------------------------|---|

$\label{eq:continuous} \begin{array}{ll} \text{Operands:} & 0 \leq k \leq 31 \\ \text{Operation:} & k \rightarrow BSR \\ \text{Status Affected:} & \text{None} \end{array}$

Description: The 5-bit literal 'k' is loaded into the

Bank Select Register (BSR).

| MOVLP            | Move literal to PCLATH                                    |

|------------------|-----------------------------------------------------------|

| Syntax:          | [ label ] MOVLP k                                         |

| Operands:        | $0 \leq k \leq 127$                                       |

| Operation:       | $k \rightarrow PCLATH$                                    |

| Status Affected: | None                                                      |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register. |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction W = 0x5A                                                                |

| Move W to f                                                                           |

|---------------------------------------------------------------------------------------|

| [ label ] MOVWF f                                                                     |

| $0 \leq f \leq 127$                                                                   |

| $(W) \rightarrow (f)$                                                                 |

| None                                                                                  |

| Move data from W register to register 'f'.                                            |

| 1                                                                                     |

| 1                                                                                     |

| MOVWF OPTION_REG                                                                      |

| Before Instruction  OPTION_REG = 0xFF  W = 0x4F  After Instruction  OPTION_REG = 0x4F |

|                                                                                       |

W = 0x4F

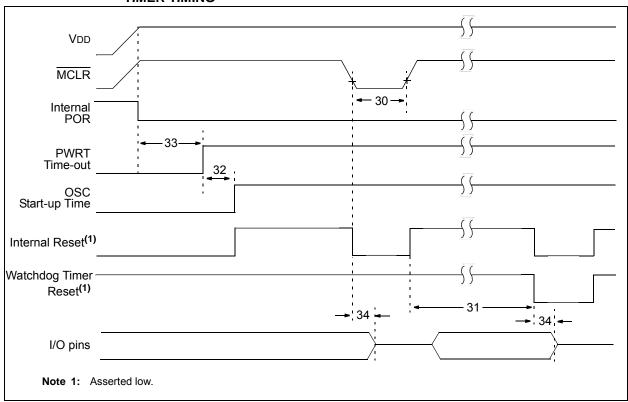

FIGURE 34-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### 36.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 36.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 36.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 36.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility