#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

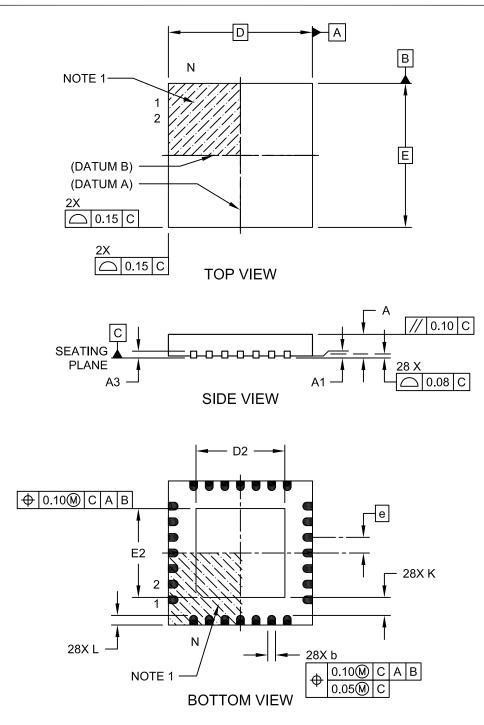

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1718t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O <sup>(2)</sup> | PDIP | TQFP | UQFN     | ADC  | Reference |       | comparator | Op Amp | DAC | Zero Cross |           | Timers |         | CCP  | 5    | NCO     | DVMM           |         |       | 000    |       |       | MSSP                   |                                |                   | EUSARI            |         | נ       | CLC            |         | Interrupt     | Pullup | Basic                   |

|--------------------|------|------|----------|------|-----------|-------|------------|--------|-----|------------|-----------|--------|---------|------|------|---------|----------------|---------|-------|--------|-------|-------|------------------------|--------------------------------|-------------------|-------------------|---------|---------|----------------|---------|---------------|--------|-------------------------|

| RC4                | 23   | 42   | 38       | AN16 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       | SD<br>SD               | (1)<br><b>A</b> <sup>(1)</sup> | -                 |                   |         |         |                |         | IOC           | Υ      |                         |

| RC5                | 24   | 43   | 39       | AN17 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         | IOC           | Y      |                         |

| RC6                | 25   | 44   | 40       | AN18 |           |       |            |        |     |            |           |        | · · · · |      |      |         |                |         |       |        |       |       |                        |                                | : с               | K <sup>(3)</sup>  |         |         |                |         | IOC           | Y      |                         |

| RC7                | 26   | 1    | 1        | AN19 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                | : R               | X <sup>(3)</sup>  |         |         |                |         | IOC           | Y      |                         |

| RD0                | 19   | 38   | 34       | AN20 |           |       |            |        |     |            | • • • •   |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   | :•:•    |         |                |         | • • • • • •   | Y      |                         |

| RD1                | 20   | 39   | 35       | AN21 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         | • • • • • • • | Υ      |                         |

| RD2                | 21   | 40   | 36       | AN22 |           |       |            |        |     |            | · · ·     |        | · · ·   |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   | · · · . | · . · . |                |         |               | Υ      |                         |

| RD3                | 22   | 41   | 37       | AN23 |           |       |            |        |     |            |           |        | · · · · |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               | Υ      |                         |

| RD4                | 27   | 2    | 2        | AN24 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               | Y      |                         |

| RD5                | 28   | 3    | 3        | AN25 |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         | • . • . • . • | Y      |                         |

| RD6                | 29   | 4    | 4        | AN26 |           |       |            |        |     |            |           |        | : . : . |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   | : . : . |         |                |         |               | Y      |                         |

| RD7                | 30   | 5    | 5        | AN27 |           |       |            |        |     |            |           |        | • • •   |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         | • • • • |                |         |               | Y      |                         |

| RE0                | 8    | 25   | 23       | AN5  |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               | Y      |                         |

| RE1                | 9    | 26   | 24       | AN6  |           |       |            |        |     |            | • ] • ] • |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         | • • • • • •   | Y      |                         |

| RE2                | 10   | 27   | 24<br>25 | AN7  |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               | Y      |                         |

| RE3                | 1    | 18   | 16       |      |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         | IOC           | Y      | MCLR<br>V <sub>PP</sub> |

| V                  | 11   | 7    | 7        |      |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               |        | V <sub>DD</sub>         |

| V <sub>DD</sub>    | 32   | 28   | 26       |      |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               |        |                         |

|                    | 12   | 6    | 6        |      |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               |        | Vss                     |

| $V_{SS}$           | 31   | 29   | 27       |      |           |       |            |        |     |            |           |        |         |      |      |         |                |         |       |        |       |       |                        |                                |                   |                   |         |         |                |         |               |        |                         |

| OUT <sup>(4)</sup> |      |      |          |      |           | C10UT | C20UT      |        |     |            |           |        |         | CCP1 | CCP2 | NC010UT | <b>PWM3OUT</b> | PWM40UT | COG1A | COG1B  | COG1C | CUG1D | SCK/SCI <sup>(3)</sup> | SDO                            | TX/CK             | DT <sup>(3)</sup> | CLC4OUT | CLC3OUT | <b>CLC2OUT</b> | CLC10UT |               |        |                         |

| 1N <sup>(5)</sup>  |      |      |          |      |           |       |            |        |     |            | T1G       | T1CKI  | TOCKI   | CCP1 | CCP2 |         |                |         |       | COG1IN |       |       | SCK/SCI <sup>(3)</sup> | SS                             | RX <sup>(3)</sup> | СК                | CLCINO  | CLCIN1  | CLCIN2         | CLCIN3  | INT           |        |                         |

#### TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1717/9) (CONTINUED)

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Alternate outputs are excluded from solid shaded areas.

5: Alternate inputs are excluded from dot shaded areas.

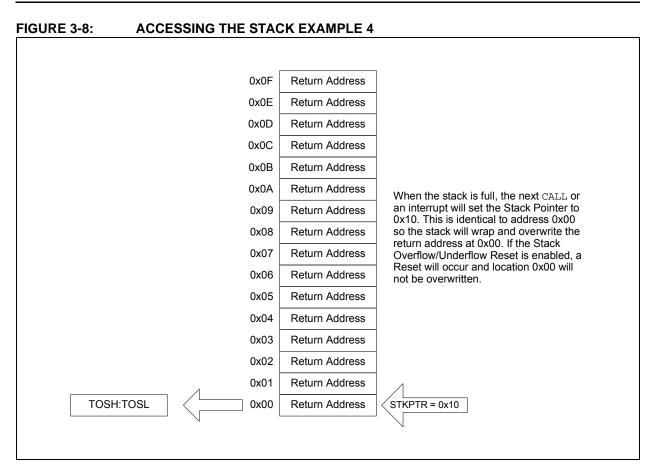

### 3.6.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.7 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

#### 6.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 6-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 6-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 6-1.

Start-up delay specifications are located in the oscillator tables of **Section 34.0** "**Electrical Specifications**".

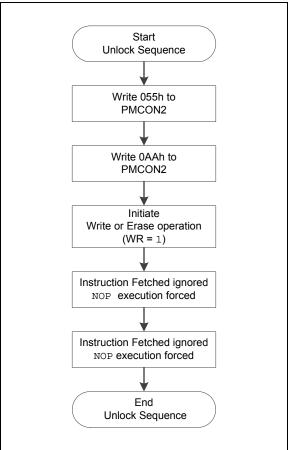

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

#### FIGURE 10-3:

#### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF                       | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL    | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary                                                                                                                                                                                                                                                    |

|----------------------|-------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | MOVWF<br>MOVF<br>MOVWF<br>BCF                         | PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS   | ; Load upper 6 bits of erase address boundary<br>; Not configuration space                                                                                                                                                                                                                                                                                     |

|                      | BSF<br>BSF                                            | PMCON1, FREE<br>PMCON1, WREN                 | ; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                                                                |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                            | PMCON1,WREN<br>INTCON,GIE                    | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                        |

### REGISTER 11-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>

| — | — | _ | — | LATE2 | LATE1 | LATE0 |

|---|---|---|---|-------|-------|-------|

|   |   |   |   |       |       | bit 0 |

|   |   |   |   |       |       |       |

|   |   |   |   |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

Note 1: PIC16(L)F1717/9 only.

#### REGISTER 11-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(1)</sup> D =Digital I/O. Pin is assigned to port or digital special function.

1 =Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: PIC16(L)F1717/9 only.

| R/W-0/0          | R/W-0/0      | R/W-0/0                                 | R/W-0/0        | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |

|------------------|--------------|-----------------------------------------|----------------|-----------------|-----------------|----------------|--------------|

| CxINTP           | CxINTN       |                                         | CxPCH<2:0>     | •               |                 | CxNCH<2:0>     |              |

| bit 7            |              |                                         |                |                 |                 |                | bit          |

| Lagandi          |              |                                         |                |                 |                 |                |              |

| Legend:          |              |                                         |                |                 |                 |                |              |

| R = Readable     |              | W = Writable                            |                | •               | mented bit, rea |                |              |

| u = Bit is unc   | •            | x = Bit is unkr                         |                | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |

| '1' = Bit is set |              | '0' = Bit is clea                       | ared           |                 |                 |                |              |

| bit 7            | CxINTP: Co   | mparator Interru                        | pt on Positive | e Going Edge E  | nable bits      |                |              |

|                  |              | F interrupt flag v<br>rupt flag will be |                |                 |                 |                |              |

| bit 6            | CxINTN: Co   | mparator Interru                        | ipt on Negativ | e Going Edge I  | Enable bits     |                |              |

|                  |              | F interrupt flag                        |                |                 |                 |                |              |

|                  | 0 = No inter | rupt flag will be                       | set on a nega  | tive going edge | e of the CxOUT  | bit            |              |

| bit 5-3          | CxPCH<2:0    | Comparator I                            | Positive Input | Channel Select  | t bits          |                |              |

|                  | -            | connects to AG                          |                |                 |                 |                |              |

|                  |              | connects to FV                          |                |                 |                 |                |              |

|                  |              | connects to DA connects to DA           |                |                 |                 |                |              |

|                  |              | unconnected, i                          |                |                 |                 |                |              |

|                  |              | unconnected, i                          |                |                 |                 |                |              |

|                  |              | connects to Cx                          |                |                 |                 |                |              |

|                  | 000 = CxVP   | connects to Cx                          | IN0+ pin       |                 |                 |                |              |

| bit 2-0          | CxNCH<2:0    | >: Comparator I                         | Vegative Input | t Channel Seleo | ct bits         |                |              |

|                  | 111 = CxVN   | connects to AG                          | SND            |                 |                 |                |              |

|                  |              | connects to FV                          |                |                 |                 |                |              |

|                  |              | unconnected, i                          | •              |                 |                 |                |              |

|                  |              | unconnected, i                          |                |                 |                 |                |              |

|                  |              | connects to Cx                          |                |                 |                 |                |              |

|                  |              | connects to Cx<br>connects to Cx        | •              |                 |                 |                |              |

|                  |              |                                         |                |                 |                 |                |              |

#### REGISTER 16-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

#### REGISTER 18-14: COGxPHR: COG RISING EDGE PHASE DELAY COUNT REGISTER

| U-0     | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|-----|---------|---------|---------|---------|---------|---------|

| _       | _   |         |         | GxPH    | IR<5:0> |         |         |

| bit 7   |     |         |         |         |         |         | bit 0   |

|         |     |         |         |         |         |         |         |

| Legend: |     |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

GxPHR<5:0>: Rising Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay rising edge event

#### REGISTER 18-15: COGxPHF: COG FALLING EDGE PHASE DELAY COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |  |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|--|--|--|--|--|

| —     | —   |         | GxPHF<5:0> |         |         |         |         |  |  |  |  |  |  |

| bit 7 |     |         |            |         |         |         | bit 0   |  |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

GxPHF<5:0>: Falling Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay falling edge event

### 26.2 Register Definitions: Option Register

| R/W-1/1         | R/W-1/1                  | R/W-1/1                                                                                                       | R/W-1/1         | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |

|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|

| WPUEN           | INTEDG                   | TMR0CS                                                                                                        | TMR0SE          | PSA            |                  | PS<2:0>          |              |  |  |

| bit 7           |                          |                                                                                                               |                 |                |                  |                  | bit (        |  |  |

|                 |                          |                                                                                                               |                 |                |                  |                  |              |  |  |

| Legend:         |                          |                                                                                                               |                 |                |                  |                  |              |  |  |

| R = Readabl     | e bit                    | W = Writable                                                                                                  | bit             | U = Unimpler   | nented bit, read | d as '0'         |              |  |  |

| u = Bit is und  | hanged                   | x = Bit is unk                                                                                                | nown            | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |  |  |

| '1' = Bit is se | t                        | '0' = Bit is cle                                                                                              | ared            |                |                  |                  |              |  |  |

|                 |                          |                                                                                                               |                 |                |                  |                  |              |  |  |

| bit 7           | WPUEN: We                | ak Pull-Up Ena                                                                                                | able bit        |                |                  |                  |              |  |  |

|                 |                          | pull-ups are dis                                                                                              |                 |                |                  |                  |              |  |  |

|                 | -                        | Il-ups are enab                                                                                               | -               | ial WPUx latch | values           |                  |              |  |  |

| bit 6           |                          | ITEDG: Interrupt Edge Select bit                                                                              |                 |                |                  |                  |              |  |  |

|                 | •                        | <ul> <li>1 = Interrupt on rising edge of INT pin</li> <li>0 = Interrupt on falling edge of INT pin</li> </ul> |                 |                |                  |                  |              |  |  |

| bit 5           |                          | mer0 Clock Sou                                                                                                | •               |                |                  |                  |              |  |  |

| DIL D           |                          | n on TOCKI pin                                                                                                |                 |                |                  |                  |              |  |  |

|                 |                          | nstruction cycle                                                                                              |                 | 4)             |                  |                  |              |  |  |

| bit 4           | TMR0SE: Til              | mer0 Source E                                                                                                 | dge Select bit  |                |                  |                  |              |  |  |

|                 | 1 = Incremer             | nt on high-to-low                                                                                             | v transition on | T0CKI pin      |                  |                  |              |  |  |

|                 | 0 = Incremer             | nt on low-to-hig                                                                                              | h transition on | T0CKI pin      |                  |                  |              |  |  |

| bit 3           | PSA: Presca              | ler Assignment                                                                                                | bit             |                |                  |                  |              |  |  |

|                 |                          | r is not assigne                                                                                              |                 |                |                  |                  |              |  |  |

|                 |                          | r is assigned to                                                                                              |                 | odule          |                  |                  |              |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pr | escaler Rate Se                                                                                               | elect bits      |                |                  |                  |              |  |  |

|                 | Bit                      | Value Timer0                                                                                                  | Rate            |                |                  |                  |              |  |  |

|                 |                          | 000 1:2                                                                                                       |                 |                |                  |                  |              |  |  |

|                 |                          | 001 1:4                                                                                                       |                 |                |                  |                  |              |  |  |

|                 |                          | 010 1:8<br>011 1:1                                                                                            |                 |                |                  |                  |              |  |  |

|                 |                          | 1.00                                                                                                          |                 |                |                  |                  |              |  |  |

#### REGISTER 26-1: OPTION\_REG: OPTION REGISTER

| TABLE 26-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0 |

|-------------|---------------------------------------------|

|             |                                             |

1 : 32 1 : 64

1:128

1:256

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|------------------------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 90                  |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 270                 |

| TMR0       | Timer0 Module Register |        |        |        |        | 268*   |         |        |                     |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 124                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

100

101

110

111

| Name    | Bit 7                                                                           | Bit 6          | Bit 5      | Bit 4        | Bit 3          | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|---------|---------------------------------------------------------------------------------|----------------|------------|--------------|----------------|----------|--------|--------|---------------------|

| ANSELA  | _                                                                               | _              | ANSA5      | ANSA4        | ANSA3          | ANSA2    | ANSA1  | ANSA0  | 125                 |

| ANSELB  | _                                                                               | _              | ANSB5      | ANSB4        | ANSB3          | ANSB2    | ANSB1  | ANSB0  | 131                 |

| ANSELC  | ANSC7                                                                           | ANSC6          | ANSC5      | ANSC4        | ANSC3          | ANSC2    | _      | _      | 136                 |

| CCP1CON | _                                                                               | _              | DC1B       | s<1:0>       |                | CCP1N    | 1<3:0> |        | 294                 |

| CCP2CON | _                                                                               | _              | DC2B       | s<1:0>       |                | CCP2N    | 1<3:0> |        | 294                 |

| INTCON  | GIE                                                                             | PEIE           | TMR0IE     | INTE         | IOCIE          | TMR0IF   | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE                                                                         | ADIE           | RCIE       | TXIE         | SSP1IE         | CCP1IE   | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF                                                                         | ADIF           | RCIF       | TXIF         | SSP1IF         | CCP1IF   | TMR2IF | TMR1IF | 94                  |

| TMR1H   | IR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                |            |              |                |          | 271*   |        |                     |

| TMR1L   | Holding Re                                                                      | gister for the | Least Sign | ificant Byte | of the 16-bit  | TMR1 Reg | ister  |        | 271*                |

| TRISA   | TRISA7                                                                          | TRISA6         | TRISA5     | TRISA4       | TRISA3         | TRISA2   | TRISA1 | TRISA0 | 124                 |

| TRISB   | TRISB7                                                                          | TRISB6         | TRISB5     | TRISB4       | TRISB3         | TRISB2   | TRISB1 | TRISB0 | 130                 |

| TRISC   | TRISC7                                                                          | TRISC6         | TRISC5     | TRISC4       | TRISC3         | TRISC2   | TRISC1 | TRISC0 | 135                 |

| T1CON   | TMR1C                                                                           | S<1:0>         | T1CKP      | S<1:0>       | T1OSCEN        | T1SYNC   |        | TMR10N | 279                 |

| T1GCON  | TMR1GE                                                                          | T1GPOL         | T1GTM      | T1GSPM       | T1GGO/<br>DONE | T1GVAL   | T1GS   | S<1:0> | 280                 |

#### TABLE 27-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

#### 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 27.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: |                                         |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 29.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | S;Load the W reg with   |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

#### 29.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by FOSC/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

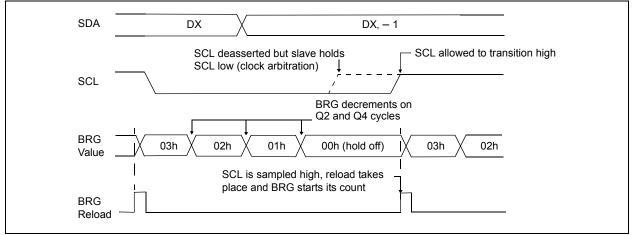

#### 30.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 30-25).

#### 30.6.3 WCOL STATUS FLAG

If the user writes the SSP1BUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSP1BUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,          |  |  |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|--|--|

|       | writing to the lower five bits of SSP1CON2         |  |  |  |  |  |  |

|       | is disabled until the Start condition is complete. |  |  |  |  |  |  |

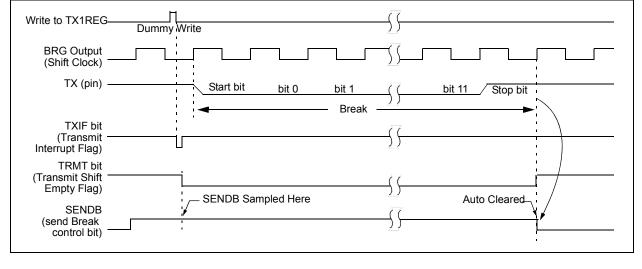

#### 31.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TX1STA register. The Break character transmission is then initiated by a write to the TX1REG. The value of data written to TX1REG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TX1STA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 31-9 for the timing of the Break character sequence.

#### 31.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TX1REG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TX1REG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TX1REG becomes empty, as indicated by the TXIF, the next data byte can be written to TX1REG.

#### 31.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RC1STA register and the received data as indicated by RC1REG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RC1REG = 00h

The second method uses the Auto-Wake-up feature described in **Section 31.4.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUD1CON register before placing the EUSART in Sleep mode.

#### FIGURE 31-9: SEND BREAK CHARACTER SEQUENCE

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         |                                                                        |

|-------------------------------------------------|------------------------------------------------------------------------|

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                        |

| SREN bit                                        | .0,<br>                                                                |

| RCIF bit<br>(Interrupt) ———<br>Read             |                                                                        |

| RC1REG<br>Note: Timing diag                     | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

#### FIGURE 31-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### TABLE 31-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

|          | _            | _                 |        |            |            |        |        |        |                     |

|----------|--------------|-------------------|--------|------------|------------|--------|--------|--------|---------------------|

| Name     | Bit 7        | Bit 6             | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

| ANSELB   |              | _                 | ANSB5  | ANSB4      | ANSB3      | ANSB2  | ANSB1  | ANSB0  | 131                 |

| ANSELC   | ANSC7        | ANSC6             | ANSC5  | ANSC4      | ANSC3      | ANSC2  | —      | —      | 136                 |

| BAUD1CON | ABDOVF       | RCIDL             | —      | SCKP       | BRG16      | _      | WUE    | ABDEN  | 362                 |

| INTCON   | GIE          | PEIE              | TMR0IE | INTE       | IOCIE      | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1     | TMR1GIE      | ADIE              | RCIE   | TXIE       | SSP1IE     | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1     | TMR1GIF      | ADIF              | RCIF   | TXIF       | SSP1IF     | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RC1REG   |              |                   | EUSA   | ART Receiv | e Data Reg | ister  |        |        | 356*                |

| RC1STA   | SPEN         | RX9               | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 361                 |

| RXPPS    | —            | — — — RXPPS<4:0>  |        |            |            |        | 152    |        |                     |

| RxyPPS   | —            | — — — RxyPPS<4:0> |        |            |            | 153    |        |        |                     |

| SP1BRGL  |              | SP1BRG<7:0>       |        |            |            |        | 363*   |        |                     |

| SP1BRGH  | SP1BRG<15:8> |                   |        |            |            | 363*   |        |        |                     |

| TRISB    | TRISB7       | TRISB6            | TRISB5 | TRISB4     | TRISB3     | TRISB2 | TRISB1 | TRISB0 | 130                 |

| TRISC    | TRISC7       | TRISC6            | TRISC5 | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 135                 |

| TX1STA   | CSRC         | TX9               | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 360                 |

|          |              |                   |        |            |            |        |        |        |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception. \* Page provides register information.

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                               |

| Example:         | RETFIE                                                                                                                                                                                                          |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                        |

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS\toPC$                                                                                                                                            |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RETLW            | Return with literal in W                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                               |  |  |  |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                          |                  | d ∈ [0,1]                                                                                                                                                                                                         |  |  |  |

|                  | $TOS \rightarrow PC$                                                                                                                                                          | Operation:       | See description below                                                                                                                                                                                             |  |  |  |

| Status Affected: | None                                                                                                                                                                          | Status Affected: | C                                                                                                                                                                                                                 |  |  |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                             |                  | C Register f                                                                                                                                                                                                      |  |  |  |

| Cycles:          | 2                                                                                                                                                                             |                  |                                                                                                                                                                                                                   |  |  |  |

| Example:         | CALL TABLE;W contains table                                                                                                                                                   | Words:           | 1                                                                                                                                                                                                                 |  |  |  |

| ,·               | ;offset value                                                                                                                                                                 | Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |

|                  | <ul> <li>;W now has table value</li> </ul>                                                                                                                                    | Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |

| TABLE            | •                                                                                                                                                                             |                  | Before Instruction                                                                                                                                                                                                |  |  |  |

|                  | ADDWF PC ;W = offset                                                                                                                                                          |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |

|                  | RETLW k1 ;Begin table                                                                                                                                                         |                  | C = 0<br>After Instruction                                                                                                                                                                                        |  |  |  |

|                  | RETLW k2 ;                                                                                                                                                                    |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |

|                  | •                                                                                                                                                                             |                  | W = 1100 1100                                                                                                                                                                                                     |  |  |  |

|                  | •<br>RETLW kn ; End of table                                                                                                                                                  |                  | C = 1                                                                                                                                                                                                             |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                                                   |  |  |  |

| <b>TABLE 34-2:</b> | SUPPLY CURRENT ( | (IDD) <sup>(1,2)</sup> |

|--------------------|------------------|------------------------|

|--------------------|------------------|------------------------|

| PIC16LF1717/8/9 |                 | Standard Operating Conditions (unless otherwise stated) |       |      |       |     |                                                              |  |  |  |  |

|-----------------|-----------------|---------------------------------------------------------|-------|------|-------|-----|--------------------------------------------------------------|--|--|--|--|

| PIC16F1         | 717/8/9         |                                                         |       |      |       |     |                                                              |  |  |  |  |

| Param. Device   |                 | Min.                                                    | Typ.† | Max. | Units |     | Conditions                                                   |  |  |  |  |

| No.             | Characteristics |                                                         | 190.1 | max. | onno  | Vdd | Note                                                         |  |  |  |  |

| D009            | LDO Regulator   | _                                                       | 75    | —    | μA    |     | High-Power mode, normal operation                            |  |  |  |  |

|                 |                 | —                                                       | 15    | —    | μA    |     | Sleep, VREGCON<1> = 0                                        |  |  |  |  |

|                 |                 | _                                                       | 0.3   | —    | μA    |     | Sleep, VREGCON<1> = 1                                        |  |  |  |  |

| D010            |                 | _                                                       | 8     | —    | μA    | 1.8 | Fosc = 32 kHz,                                               |  |  |  |  |

|                 |                 | —                                                       | 12    | —    | μA    | 3.0 | LP Oscillator mode ( <b>Note 4</b> ),<br>-40°C ≤ TA ≤ +85°C  |  |  |  |  |

| D010            |                 | _                                                       | 15    |      | μA    | 2.3 | Fosc = 32 kHz,                                               |  |  |  |  |

|                 |                 | _                                                       | 17    |      | μA    | 3.0 | LP Oscillator mode ( <b>Note 4, Note 5</b> ),                |  |  |  |  |

|                 |                 |                                                         | 21    |      | μA    | 5.0 | -40°C ≤ TA ≤ +85°C                                           |  |  |  |  |

| D012            |                 | _                                                       | 140   | —    | μA    | 1.8 | Fosc = 4 MHz,                                                |  |  |  |  |

|                 |                 | —                                                       | 250   | —    | μA    | 3.0 | XT Oscillator mode                                           |  |  |  |  |

| D012            |                 |                                                         | 210   |      | μA    | 2.3 | Fosc = 4 MHz,                                                |  |  |  |  |

|                 |                 |                                                         | 280   | —    | μA    | 3.0 | XT Oscillator mode ( <b>Note 5</b> )                         |  |  |  |  |

|                 |                 |                                                         | 340   |      | μA    | 5.0 |                                                              |  |  |  |  |

| D014            |                 |                                                         | 115   | —    | μA    | 1.8 | Fosc = 4 MHz,                                                |  |  |  |  |

|                 |                 | —                                                       | 210   | —    | μA    | 3.0 | External Clock (ECM),<br>Medium Power mode                   |  |  |  |  |

| D014            |                 |                                                         | 180   | _    | μA    | 2.3 | Fosc = 4 MHz,                                                |  |  |  |  |

|                 |                 |                                                         | 240   | —    | μA    | 3.0 | External Clock (ECM),<br>Medium Power mode ( <b>Note 5</b> ) |  |  |  |  |

|                 |                 |                                                         | 300   |      | μA    | 5.0 |                                                              |  |  |  |  |

| D015            |                 |                                                         | 2.1   | —    | mA    | 3.0 | Fosc = 32 MHz,                                               |  |  |  |  |

|                 |                 |                                                         | 2.5   | —    | mA    | 3.6 | External Clock (ECH),<br>High-Power mode                     |  |  |  |  |

| D015            |                 |                                                         | 2.1   | —    | mA    | 3.0 | Fosc = 32 MHz,                                               |  |  |  |  |

|                 |                 | -                                                       | 2.2   | —    | mA    | 5.0 | External Clock (ECH),<br>High-Power mode ( <b>Note 5</b> )   |  |  |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

**2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in  $k\Omega$

4: FVR and BOR are disabled.

**5:** 0.1  $\mu$ F capacitor on VCAP.

6: 8 MHz clock with 4x PLL enabled.

| PIC16LF1717/8/9<br>PIC16F1717/8/9 |                     | Standard Operating Conditions (unless otherwise stated) |       |        |       |     |                                      |  |  |  |

|-----------------------------------|---------------------|---------------------------------------------------------|-------|--------|-------|-----|--------------------------------------|--|--|--|

|                                   |                     |                                                         |       |        |       |     |                                      |  |  |  |

| Param. Device                     |                     | Min.                                                    | True  | Max.   | Units |     | Conditions                           |  |  |  |

| No.                               | No. Characteristics | WIITI.                                                  | Тур.† | IVIAX. | Units | Vdd | Note                                 |  |  |  |

| D017                              |                     | —                                                       | 130   |        | μA    | 1.8 | Fosc = 500 kHz,                      |  |  |  |

|                                   |                     | _                                                       | 150   |        | μA    | 3.0 | MFINTOSC mode                        |  |  |  |

| D017                              |                     | —                                                       | 150   |        | μA    | 2.3 | Fosc = 500 kHz,                      |  |  |  |

|                                   |                     | —                                                       | 170   |        | μA    | 3.0 | MFINTOSC mode ( <b>Note 5</b> )      |  |  |  |

|                                   |                     | —                                                       | 220   |        | μA    | 5.0 |                                      |  |  |  |

| D019                              |                     | _                                                       | 0.8   |        | mA    | 1.8 | Fosc = 16 MHz,                       |  |  |  |

|                                   |                     |                                                         | 1.2   |        | mA    | 3.0 | HFINTOSC mode                        |  |  |  |

| D019                              |                     |                                                         | 1.0   |        | mA    | 2.3 | Fosc = 16 MHz,                       |  |  |  |

|                                   |                     |                                                         | 1.3   |        | mA    | 3.0 | HFINTOSC mode ( <b>Note 5</b> )      |  |  |  |

|                                   |                     |                                                         | 1.4   | —      | mA    | 5.0 |                                      |  |  |  |

| D020                              |                     |                                                         | 2.1   | —      | mA    | 3.0 | Fosc = 32 MHz,                       |  |  |  |

|                                   |                     | —                                                       | 2.5   | —      | mA    | 3.6 | HFINTOSC mode                        |  |  |  |

| D020                              |                     |                                                         | 2.1   | —      | mA    | 3.0 | Fosc = 32 MHz,                       |  |  |  |

|                                   |                     | —                                                       | 2.2   | —      | mA    | 5.0 | HFINTOSC mode                        |  |  |  |

| D022                              |                     |                                                         | 2.1   | —      | mA    | 3.0 | Fosc = 32 MHz,                       |  |  |  |

|                                   |                     | —                                                       | 2.5   | —      | mA    | 3.6 | HS Oscillator mode ( <b>Note 6</b> ) |  |  |  |

| D022                              | -                   |                                                         | 2.1   |        | mA    | 3.0 | Fosc = 32 MHz                        |  |  |  |

|                                   |                     | —                                                       | 2.2   | —      | mA    | 5.0 | HS Oscillator mode (Note 5, Note 6)  |  |  |  |

### TABLE 34-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

**2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in  $k\Omega$