Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

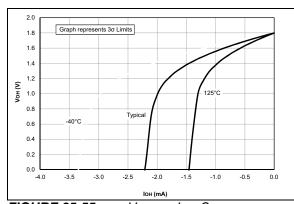

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

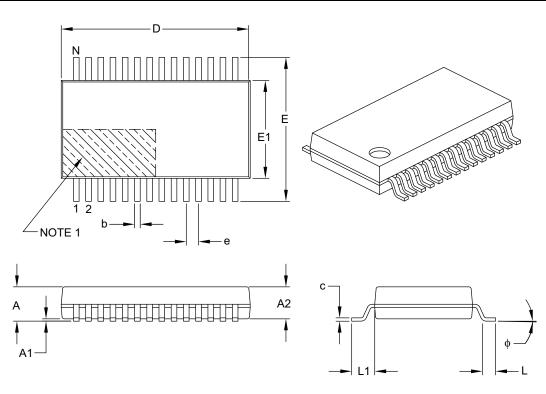

| Mounting Type              | Surface Mount                                                              |

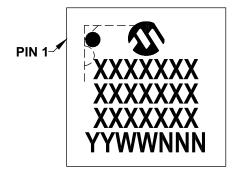

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1719-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

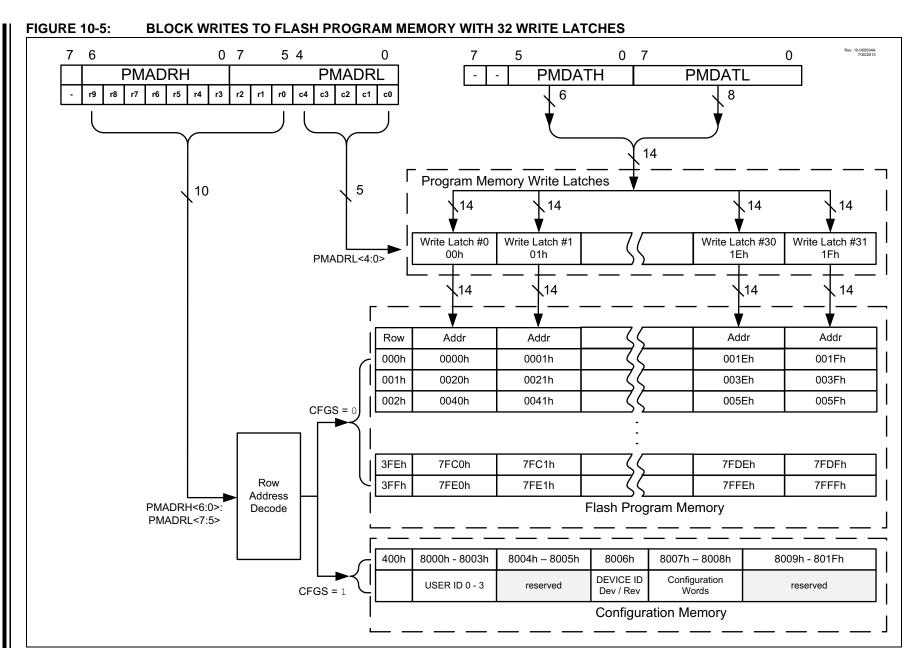

#### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1717/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

#### 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect **Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|

| PIC16(L)F1717   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |

| PIC16(L)F1718/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

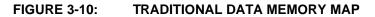

#### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

|                   |                                                                                                                                | R/P-1                                                                                                                                                                                                                          | R/P-1                                                                                                                                                    | R/P-1                                                                                                   | R/P-1                                                                                               | R/P-1                                                                       | R/P-1 |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|--|

|                   |                                                                                                                                | LVP <sup>(1)</sup>                                                                                                                                                                                                             | DEBUG <sup>(2)</sup>                                                                                                                                     | LPBOR                                                                                                   | BORV <sup>(3)</sup>                                                                                 | STVREN                                                                      | PLLEN |  |

|                   |                                                                                                                                | bit 13                                                                                                                                                                                                                         |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             | bit 8 |  |

| R/P-1             | U-1                                                                                                                            | U-1                                                                                                                                                                                                                            | U-1                                                                                                                                                      | U-1                                                                                                     | R/P-1                                                                                               | R/P-1                                                                       | R/P-1 |  |

| ZCDDIS            | _                                                                                                                              | _                                                                                                                                                                                                                              | _                                                                                                                                                        | _                                                                                                       | PPS1WAY                                                                                             | WRT<1:0>                                                                    |       |  |

| bit 7             |                                                                                                                                |                                                                                                                                                                                                                                |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             | bit   |  |

| Legend:           |                                                                                                                                |                                                                                                                                                                                                                                |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |  |

| R = Readable      | bit                                                                                                                            | P = Programm                                                                                                                                                                                                                   | able bit                                                                                                                                                 | U = Unimpleme                                                                                           | ented bit, read as                                                                                  | '1'                                                                         |       |  |

| '0' = Bit is clea | ared                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                               |                                                                                                                                                          | -n = Value wher                                                                                         | n blank or after B                                                                                  | ulk Erase                                                                   |       |  |

| bit 13            | 1 = Low-volta                                                                                                                  | Itage Programmin<br>ige programming e<br>age on MCLR mus                                                                                                                                                                       | enabled                                                                                                                                                  | gramming                                                                                                |                                                                                                     |                                                                             |       |  |

| bit 12            | <b>DEBUG:</b> In-C<br>1 = In-Circuit                                                                                           | Circuit Debugger N<br>Debugger disable<br>Debugger enable                                                                                                                                                                      | lode bit <sup>(2)</sup><br>d, ICSPCLK and                                                                                                                | ICSPDAT are ge                                                                                          |                                                                                                     | •                                                                           |       |  |

| bit 11            | 1 = Low-Pow                                                                                                                    | -Power BOR Enal<br>er Brown-out Rese<br>er Brown-out Rese                                                                                                                                                                      | et is disabled                                                                                                                                           |                                                                                                         |                                                                                                     |                                                                             |       |  |

| bit 10            | 1 = Brown-ou                                                                                                                   | n-out Reset Voltag<br>it Reset voltage (V<br>it Reset voltage (V                                                                                                                                                               | BOR), low trip poi                                                                                                                                       |                                                                                                         |                                                                                                     |                                                                             |       |  |

| bit 9             | 1 = Stack Ove                                                                                                                  | ack Overflow/Unde<br>erflow or Underflow<br>erflow or Underflow                                                                                                                                                                | w will cause a Re                                                                                                                                        | set                                                                                                     |                                                                                                     |                                                                             |       |  |

| bit 8             | <b>PLLEN:</b> PLL<br>1 = 4xPLL en<br>0 = 4xPLL dis                                                                             | abled                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |  |

| bit 7             | <b>ZCDDIS:</b> ZCI<br>1 = ZCD disa<br>0 = ZCD alwa                                                                             | bled. ZCD can be                                                                                                                                                                                                               | enabled by settin                                                                                                                                        | ig the ZCDSEN b                                                                                         | bit of ZCDCON                                                                                       |                                                                             |       |  |

| bit 6-3           | Unimplemen                                                                                                                     | ted: Read as '1'                                                                                                                                                                                                               |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |  |

| bit 2             | 1 = The PPS<br>future ch                                                                                                       | PSLOCK Bit One-<br>LOCK bit can only<br>nanges to PPS reg<br>LOCK bit can be s                                                                                                                                                 | y be set once afte<br>gisters are preven                                                                                                                 | er an unlocking s<br>ted                                                                                |                                                                                                     |                                                                             |       |  |

| bit 1-0           | WRT<1:0>: F<br>8 kW Flash m<br>11 = Wri<br>10 = 000<br>01 = 000<br>00 = 000<br>16 kW Flash<br>11 = Wri<br>10 = 000<br>01 = 000 | Flash Memory Self<br><u>hemory (PIC16(L))</u><br>ite protection off<br>00h to 01FFh write<br>00h to 1FFh write<br><u>memory (PIC16(L</u><br>ite protection off<br>00h to 01FFh write<br>00h to 1FFh write<br>00h to 3FFh write | -Write Protection<br>-1717)<br>-protected, 02001<br>-protected, 10001<br>-protected, no ad<br><u>)F1718/9)</u><br>-protected, 02001<br>-protected, 20001 | bits<br>h to 1FFFh may b<br>h to 1FFFh may b<br>ldresses may be<br>h to 3FFFh may b<br>h to 3FFFh may b | be modified by Pl<br>be modified by Pl<br>modified by PMC<br>be modified by Pl<br>be modified by Pl | MCON control<br>MCON control<br>CON control<br>MCON control<br>MCON control |       |  |

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

3: See VBOR parameter for specific trip point voltages.

# PIC16(L)F1717/8/9

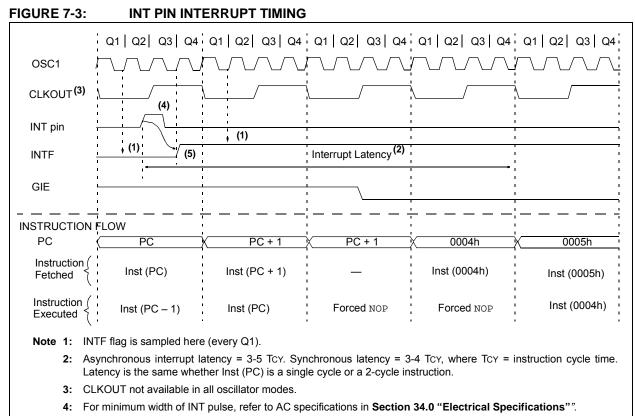

**5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

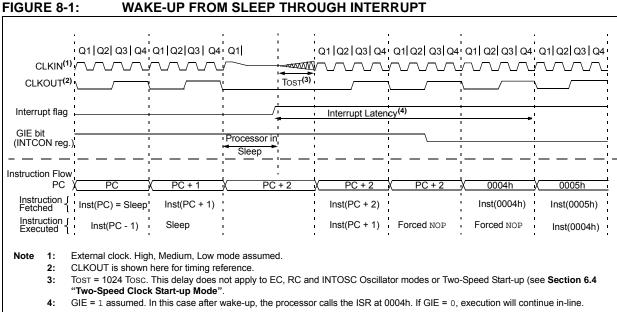

#### 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 8.0** "**Power-Down Mode (Sleep)**" for more details.

#### 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- · If the interrupt occurs before the execution of a

- SLEEP instruction - SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be

- cleared • If the interrupt occurs during or after the

- execution of a SLEEP instruction - SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a **SLEEP** instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

9IC16(L)F1717/8/9

#### 11.2 Register Definitions: PORTA

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u                                               | R-x/u                              | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| RA7                                     | RA6     | RA5               | RA4                                                   | RA3                                | RA2     | RA1     | RA0     |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |

| R = Readable bit W = Writable bit       |         |                   |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

#### REGISTER 11-1: PORTA: PORTA REGISTER

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISA<7:0>:** PORTA Tri-State Control bit 1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

## REGISTER 11-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>

| — | — | _ | — | LATE2 | LATE1 | LATE0 |

|---|---|---|---|-------|-------|-------|

|   |   |   |   |       |       | bit 0 |

|   |   |   |   |       |       |       |

|   |   |   |   |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

Note 1: PIC16(L)F1717/9 only.

#### REGISTER 11-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(1)</sup> D =Digital I/O. Pin is assigned to port or digital special function.

1 =Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: PIC16(L)F1717/9 only.

#### REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

GxFSIM0: COGx Falling Event Input Source 0 Mode bit

GxFIS0 = 1:

bit 0

- 1 = Pin selected with COGxPPS control high-to-low transition will cause a falling event after falling event phase delay

- 0 = Pin selected with COGxPPS control low level will cause an immediate falling event

GxFIS0 = 0:

Pin selected with COGxPPS control has no effect on falling event

#### 22.3 Register Definitions: Op Amp Control

| R/W-0/0<br>OPAxSP                     | U-0<br>—<br>W = Writable<br>x = Bit is unkn                                                          | R/W-0/0<br>OPAxUG                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                            | U-0<br>—                                                                                                                                                                                                                   | R/W-0/0<br>OPAxC                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0/0<br>H<1:0><br>bit 0                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                       |                                                                                                      |                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                          | OPAxC                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| ed                                    |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        | bit C                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ed                                    |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ed                                    |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ed                                    |                                                                                                      | bit                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ed                                    | x = Bit is unkn                                                                                      |                                                                                                                                                                                                                            | U = Unimpler                                                                                                                                                                                                                                                                                                   | mented bit, read                                                                                                                                                                                                           | as '0'                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       |                                                                                                      | nown                                                                                                                                                                                                                       | -n/n = Value at POR and BOR/Value at all other Res                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       | '0' = Bit is clea                                                                                    | ared                                                                                                                                                                                                                       | q = Value dep                                                                                                                                                                                                                                                                                                  | pends on condit                                                                                                                                                                                                            | ion                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PAxEN: Op                             | Amp Enable b                                                                                         | it                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1 = Op amp is enabled                 |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       | s disabled and                                                                                       |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| OPAxSP: Op Amp Speed/Power Select bit |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       | perates in high<br>. Do not use.                                                                     | GBWP mod                                                                                                                                                                                                                   | e                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| implement                             | ted: Read as '                                                                                       | כ'                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| OPAxUG: Op Amp Unity Gain Select bit  |                                                                                                      |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| •                                     |                                                                                                      | 0                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                              | pin is available                                                                                                                                                                                                           | for general pur                                                                                                                                                                                                                                                                                                                                                                                        | pose I/O.                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| implement                             | ted: Read as '                                                                                       | כ'                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                       |                                                                                                      | •                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                | t                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| = Non-inve<br>= Non-inve              | erting input con<br>erting input con                                                                 | nects to DAC<br>nects to DAC                                                                                                                                                                                               | 1_output<br>2_output                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| >><br>=<br>=<br>>>                    | AxUG: Op<br>OPA outp<br>Inverting i<br>mplemen<br>AxCH<1:0<br>= Non-inve<br>= Non-inve<br>= Non-inve | AxUG: Op Amp Unity Ga<br>OPA output is connected<br>Inverting input is connect<br>mplemented: Read as 'u<br>AxCH<1:0>: Non-invertin<br>= Non-inverting input con<br>= Non-inverting input con<br>= Non-inverting input con | AxUG: Op Amp Unity Gain Select bit<br>OPA output is connected to inverting inverting input is connected to the OP<br>mplemented: Read as '0'<br>AxCH<1:0>: Non-inverting Channel Se<br>= Non-inverting input connects to FVR<br>= Non-inverting input connects to DAC<br>= Non-inverting input connects to DAC | AxUG: Op Amp Unity Gain Select bit<br>OPA output is connected to inverting input. OPAxIN-<br>Inverting input is connected to the OPAxIN- pin<br>mplemented: Read as '0'<br>AxCH<1:0>: Non-inverting Channel Selection bits | AxUG: Op Amp Unity Gain Select bit<br>OPA output is connected to inverting input. OPAxIN- pin is available<br>Inverting input is connected to the OPAxIN- pin<br>mplemented: Read as '0'<br>AxCH<1:0>: Non-inverting Channel Selection bits<br>= Non-inverting input connects to FVR Butter 2 output<br>= Non-inverting input connects to DAC1_output<br>= Non-inverting input connects to DAC2_output | AxUG: Op Amp Unity Gain Select bit<br>OPA output is connected to inverting input. OPAxIN- pin is available for general pur<br>Inverting input is connected to the OPAxIN- pin<br>mplemented: Read as '0'<br>AxCH<1:0>: Non-inverting Channel Selection bits<br>= Non-inverting input connects to FVR Butter 2 output<br>= Non-inverting input connects to DAC1_output<br>= Non-inverting input connects to DAC2_output |  |

#### REGISTER 22-1: OPAxCON: OPERATIONAL AMPLIFIERS (OPAx) CONTROL REGISTERS

TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name     | Bit 7      | Bit 6  | Bit 5   | Bit 4   | Bit 3                  | Bit 2          | Bit 1        | Bit 0   | Register<br>on Page |

|----------|------------|--------|---------|---------|------------------------|----------------|--------------|---------|---------------------|

| ANSELA   | —          | —      | ANSA5   | ANSA4   | ANSA3                  | ANSA2          | ANSA1        | ANSA0   | 125                 |

| ANSELB   | —          | _      | ANSB5   | ANSB4   | ANSB3                  | ANSB2          | ANSB1        | ANSB0   | 131                 |

| DAC1CON0 | DAC1EN     | _      | DAC10E1 | DAC10E2 | DAC1PSS<1:0>           |                | —            | DAC1NSS | 260                 |

| DAC1CON1 | DAC1R<7:0> |        |         |         |                        |                | 260          |         |                     |

| FVRCON   | FVREN      | FVRRDY | TSEN    | TSRNG   | CDAFVR<1:0> ADFVR<1:0> |                |              | /R<1:0> | 165                 |

| OPA1CON  | OPA1EN     | OPA1SP | _       | OPA1UG  | _                      | _              | OPA1PCH<1:0> |         | 257                 |

| OPA2CON  | OPA2EN     | OPA2SP | _       | OPA2UG  | _                      | — OPA2PCH<1:0> |              | 257     |                     |

| TRISA    | TRISB7     | TRISB6 | TRISB5  | TRISB4  | TRISB3                 | TRISB2         | TRISB1       | TRISB0  | 124                 |

| TRISB    | TRISC7     | TRISC6 | TRISC5  | TRISC4  | TRISC3                 | TRISC2         | TRISC1       | TRISC0  | 130                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

can be determined from the time difference between the ZCDOUT high and low periods. Note that the time difference,  $\Delta T$ , is 4\*T<sub>offset</sub>. The equation for determining the pull-up and pull-down resistor values from the high and low ZCDOUT periods is shown in Equation 25-4. The ZCDOUT signal can be directly observed on a pin by routing the ZCDOUT signal through one of the CLCs.

#### EQUATION 25-4:

$$R = R_{series} \left( \frac{V_{bias}}{V_{peak} \left( \sin \left( \pi Freq \frac{(\Delta T)}{2} \right) \right)} - 1 \right)$$

R is pull-up or pull-down resistor

$V_{\text{bias}}$  is  $V_{\text{pullup}}$  when R is pull-up or VDD when R is pull-down

$\Delta T$  is the ZCDOUT high and low period difference

### 25.6 Handling V<sub>peak</sub> variations

If the peak amplitude of the external voltage is expected to vary then the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of ± 600 µA for the maximum expected voltage and high enough to be detected accurately at the minimum peak voltage. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm$  600  $\mu$ A and the minimum is at least  $\pm$  100  $\mu$ A compute the series resistance as shown in Equation 25-5. The compensating pull-up for this series resistance can be determined with pull-up value Equation 25-3 because the is independent from the peak voltage.

#### EQUATION 25-5: SERIES R FOR V RANGE

$$R_{series} = \frac{V_{maxpeak} + V_{minpeak}}{7 \times 10^{-4}}$$

#### 25.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

#### 25.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-On-Reset (POR). When the ZCDDIS Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCDDIS Configuration bit is set, the ZCDxEN bit of the ZCDxCON register must be set to enable the ZCD module.

#### 31.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RC1STA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RC1REG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RC1STA register which resets the EUSART. Clearing the CREN bit of the RC1STA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

|       | FIFO have framing errors, repeated reads |  |  |  |  |

|       | of the RC1REG will not clear the FERR    |  |  |  |  |

|       | bit.                                     |  |  |  |  |

#### 31.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RC1STA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RC1STA register or by resetting the EUSART by clearing the SPEN bit of the RC1STA register.

#### 31.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RC1REG.

#### 31.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RC1STA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 31.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SP1BRGH, SP1BRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

Table 31-3 contains the formulas for determining the baud rate. Example 31-1 provides a sample calculation for determining the baud rate and baud rate error.