Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

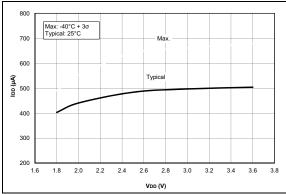

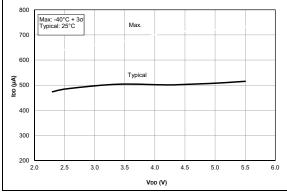

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1719-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3: PIC16(L)F1717/9 PINOUT DESCRIPTION (CONTINUED)

| Name                                            | Function           | Input<br>Type    | Output<br>Type | Description                  |

|-------------------------------------------------|--------------------|------------------|----------------|------------------------------|

| RC4/AN16/SDI <sup>(1)</sup> /SDA <sup>(1)</sup> | RC4                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN16               | AN               |                | ADC Channel 16 input.        |

|                                                 | SDI                | TTL/ST           |                | SPI Data input.              |

|                                                 | SDA <sup>(3)</sup> | l <sup>2</sup> C |                | I <sup>2</sup> C Data input. |

| RC5/AN17                                        | RC5                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN17               | AN               | _              | ADC Channel 17 input.        |

| RC6/AN18/CK <sup>(1)</sup>                      | RC6                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN18               | AN               |                | ADC Channel 18 input.        |

|                                                 | СК                 | TTL/ST           |                | EUSART synchronous clock.    |

| RC7/AN19/RX <sup>(1)</sup>                      | RC7                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN19               | AN               |                | ADC Channel 19 input.        |

|                                                 | RX                 | TTL/ST           |                | EUSART receive.              |

| RDO/AN20                                        | RD0                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN20               | AN               | _              | ADC Channel 20 input.        |

| RD1/AN21                                        | RD1                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN21               | AN               | _              | ADC Channel 21 input.        |

| RD2/AN22                                        | RD2                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN22               | AN               |                | ADC Channel 22 input.        |

| RD3/AN23                                        | RD3                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN23               | AN               |                | ADC Channel 23 input.        |

| RD4/AN24                                        | RD4                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN24               | AN               | _              | ADC Channel 24 input.        |

| RD5/AN25                                        | RD5                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN25               | AN               |                | ADC Channel 25 input.        |

| RD6/AN26                                        | RD6                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN26               | AN               | _              | ADC Channel 26 input.        |

| RD7/AN27                                        | RD7                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN27               | AN               | _              | ADC Channel 27 input.        |

| RE0/AN5                                         | RE0                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN5                | AN               |                | ADC Channel 5 input.         |

| RE1/AN6                                         | RE1                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN6                | AN               | —              | ADC Channel 6 input.         |

| RE2/AN7                                         | RE2                | TTL/ST           | CMOS           | General purpose I/O.         |

|                                                 | AN7                | AN               |                | ADC Channel 7 input.         |

| RE3/MCLR/VPP                                    | RE3                | TTL/ST           |                | General purpose input.       |

|                                                 | MCLR               | ST               |                | Master clear input.          |

|                                                 | VPP                | HV               |                | Programming voltage.         |

| Vdd                                             | VDD                | Power            | _              | Positive supply.             |

| Vss                                             | Vss                | Power            |                | Ground reference.            |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1717/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

### 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect Read with FSR" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|

| PIC16(L)F1717   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |

| PIC16(L)F1718/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

# PIC16(L)F1717/8/9

| Addr.              | Name     | Bit 7      | Bit 6    | Bit 5       | Bit 4         | Bit 3         | Bit 2           | Bit 1     | Bit 0    | Value on<br>POR, BOR | Value on all<br>other Resets |

|--------------------|----------|------------|----------|-------------|---------------|---------------|-----------------|-----------|----------|----------------------|------------------------------|

| Banl               | k 10     |            |          |             |               |               |                 |           |          | 1                    |                              |

| 50Ch               |          |            |          |             |               |               |                 |           |          |                      |                              |

| <br>510h           | _        | Unimplemen | ited     |             |               |               |                 |           |          | _                    | _                            |

| 511h               | OPA1CON  | OPA1EN     | OPA1SP   | —           | OPA1UG        | —             | —               | OPA1F     | PCH<1:0> | 00-000               | 00-000                       |

| 512h               |          |            | •        |             | •             |               | •               | •         |          |                      |                              |

| —<br>514h          | —        | Unimplemen | ited     |             |               |               |                 |           |          | _                    | -                            |

| 515h               | OPA2CON  | OPA2EN     | OPA2SP   | _           | OPA2UG        | _             | _               | OPA2F     | PCH<1:0> | 00-000               | 00-000                       |

| 516h               |          |            |          | 1           |               | 1             |                 |           |          |                      |                              |

| <br>51Fh           | -        | Unimplemen | ited     |             |               |               |                 |           |          | —                    | -                            |

| Banl               | k 11     |            |          |             |               |               |                 |           |          |                      |                              |

| 58Ch               |          |            |          |             |               |               |                 |           |          |                      |                              |

| to                 | —        | Unimplemen | ited     |             |               |               |                 |           |          | -                    | -                            |

| 59Fh<br>Banl       | (12)     |            |          |             |               |               |                 |           |          |                      |                              |

| 60Ch               |          |            |          |             |               |               |                 |           |          |                      |                              |

| to                 | —        | Unimplemen | ited     |             |               |               |                 |           |          | _                    | _                            |

| 616h               |          |            |          |             |               |               |                 |           |          |                      |                              |

| 617h               | PWM3DCL  | PWM3       | DC<1:0>  | —           |               |               | —               | —         | —        | xx                   | uu                           |

| 618h               | PWM3DCH  |            |          |             |               | DCH<7:0>      |                 |           |          | XXXX XXXX            | uuuu uuuu                    |

| 619h               | PWM3CON  | PWM3EN     | —        | PWM3OUT     | PWM3POL       | —             | _               | —         | —        | 0-x0                 | u-uu                         |

| 61Ah               | PWM4DCL  | PWM4L      | )CL<1:0> |             | —             | -             | _               | _         |          | xx                   | uu                           |

| 61Bh               | PWM4DCH  |            |          | DWARDUIT    |               | DCH<7:0>      |                 |           |          | XXXX XXXX            | uuuu uuuu                    |

| 61Ch               | PWM4CON  | PWM4EN     | —        | PWM4OUT     | PWM4POL       | —             | —               | —         | —        | 0-x0                 | u-uu                         |

| 61Dh               | —        | Unimplemen | ited     |             |               |               |                 |           |          | _                    | _                            |

| 61Fh               | 40       |            |          |             |               |               |                 |           |          |                      |                              |

| Bank               | C 13     |            |          |             |               |               |                 |           |          |                      |                              |

| 68Ch<br>to<br>690h | _        | Unimplemen | ited     |             |               |               |                 |           |          | -                    | -                            |

| 691h               | COG1PHR  | _          | —        | COG Rising  | Edge Phase D  | Delay Count R | egister         |           |          | xx xxxx              | uu uuuu                      |

| 692h               | COG1PHF  | —          | —        | COG Falling | Edge Phase [  | Delay Count R | egister         |           |          | xx xxxx              | uu uuuu                      |

| 693h               | COG1BLKR | —          | —        | COG Rising  | Edge Blanking | g Count Regis | ter             |           |          | xx xxxx              | uu uuuu                      |

| 694h               | COG1BLKF | _          | _        | COG Falling | Edge Blanking | g Count Regis | ter             |           |          | xx xxxx              | uu uuuu                      |

| 695h               | COG1DBR  | _          | _        | COG Rising  | Edge Dead-ba  | and Count Reg | gister          |           |          | xx xxxx              | uu uuuu                      |

| 696h               | COG1DBF  | —          | —        | COG Falling | Edge Dead-b   | and Count Re  | gister          |           |          | xx xxxx              | uu uuuu                      |

| 697h               | COG1CON0 | G1EN       | G1LD     | —           | G1CS          | S<1:0>        |                 | G1MD<2:0> | >        | 00-0 0000            | 00-0 0000                    |

| 698h               | COG1CON1 | G1RDBS     | G1FDBS   | _           | —             | G1POLD        | G1POLC          | G1POLB    | G1POLA   | 00 0000              | 00 0000                      |

| 699h               | COG1RIS  | G1RIS7     | G1RIS6   | G1RIS5      | G1RIS4        | G1RIS3        | G1RIS2          | G1RIS1    | G1RIS0   | 0000 0000            | -000 0000                    |

| 69Ah               | COG1RSIM | G1RSIM7    | G1RSIM6  | G1RSIM5     | G1RSIM4       | G1RSIM3       | G1RSIM2         | G1RSIM1   | G1RSIM0  | 0000 0000            | -000 0000                    |

| 69Bh               | COG1FIS  | G1FIS7     | G1FIS6   | G1FIS5      | G1FIS4        | G1FIS3        | G1FIS2          | G1FIS1    | G1FIS0   | 0000 0000            | -000 0000                    |

| 69Ch               | COG1FSIM | G1FSIM7    | G1FSIM6  | G1FSIM5     | G1FSIM4       | G1FSIM3       | G1FSIM2         | G1FSIM1   | G1FSIM0  | 0000 0000            | -000 0000                    |

| 69Dh               | COG1ASD0 | G1ASE      | G1ARSEN  |             | BD<1:0>       |               | AC<1:0>         | _         | _        | 0001 01              | 0001 01                      |

| 69Eh               | COG1ASD1 | _          | _        | _           |               | G1AS3E        | G1AS2E          | G1AS1E    | G1AS0E   | 0000                 | 0000                         |

| 69Fh               | COG1STR  | G1SDATD    | G1SDATC  | G1SDATB     | G1SDATA       | G1STRD        | G1STRC          | G1STRB    | G1STRA   | 0000 0001            | 0000 0001                    |

|                    |          | GIODAID    |          |             |               |               | d, read as '0', |           | 0.0114   |                      |                              |

#### **TABLE 3-12:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unknanged, q = value depends to Shaded locations are unimplemented, read as '0'. Unimplemented on PIC16(L)F1718.

Note 1:

2: Unimplemented on PIC16LF1717/8/9

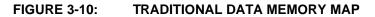

#### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

configuration memory will be erased.

#### REGISTER 4-1: **CONFIG1: CONFIGURATION WORD 1 (CONTINUED)** bit 7 **CP:** Code Protection bit<sup>(1)</sup> 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled MCLRE: MCLR/VPP Pin Function Select bit bit 6 If LVP bit = 1: This bit is ignored. If LVP bit = 0: 1 = MCLR/VPP pin function is MCLR; Weak pull-up enabled. 0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUE3 bit. bit 5 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled 0 = PWRT enabled bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit 11 = WDT enabled 10 = WDT enabled while running and disabled in Sleep 01 = WDT controlled by the SWDTEN bit in the WDTCON register 00 = WDT disabled bit 2-0 FOSC<2:0>: Oscillator Selection bits 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin 110 = ECM: External Clock, Medium Power mode (0.5-4 MHz): device clock supplied to CLKIN pin 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin 100 = INTOSC oscillator: I/O function on CLKIN pin 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins Note 1: The entire Flash program memory will be erased when the code protection is turned off during an erase. When a Bulk Erase Program Memory command is executed, the entire program Flash memory and

### 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 5-2.

### 5.14 Register Definitions: Power Control

#### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:          |                         |                                                        |                                                              |  |  |  |  |

|------------------|-------------------------|--------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| HC = Bit is cle  | eared by hardw          | are                                                    | HS = Bit is set by hardware                                  |  |  |  |  |

| R = Readable     | bit                     | W = Writable bit                                       | U = Unimplemented bit, read as '0'                           |  |  |  |  |

| u = Bit is unch  | nanged                  | x = Bit is unknown                                     | -m/n = Value at POR and BOR/Value at all other Resets        |  |  |  |  |

| '1' = Bit is set |                         | '0' = Bit is cleared                                   | q = Value depends on condition                               |  |  |  |  |

| <b>h</b> :+ 7    |                         |                                                        |                                                              |  |  |  |  |

| bit 7            |                         | ack Overflow Flag bit<br>Overflow occurred             |                                                              |  |  |  |  |

|                  |                         | Overflow has not occurred                              | d or cleared by firmware                                     |  |  |  |  |

| bit 6            |                         | ack Underflow Flag bit                                 | ,                                                            |  |  |  |  |

|                  | 1 = A Stack             | Underflow occurred                                     |                                                              |  |  |  |  |

|                  | 0 = A Stack             | Underflow has not occurre                              | ed or cleared by firmware                                    |  |  |  |  |

| bit 5            | Unimpleme               | nted: Read as '0'                                      |                                                              |  |  |  |  |

| bit 4            | RWDT: Wato              | hdog Timer Reset Flag bit                              | t                                                            |  |  |  |  |

|                  |                         | •                                                      | occurred or set to '1' by firmware                           |  |  |  |  |

|                  |                         | -                                                      | rred (cleared by hardware)                                   |  |  |  |  |

| bit 3            |                         | LR Reset Flag bit                                      |                                                              |  |  |  |  |

|                  |                         | Reset has not occurred or<br>Reset has occurred (clear |                                                              |  |  |  |  |

| bit 2            |                         | struction Flag bit                                     |                                                              |  |  |  |  |

| DIL Z            |                         | Ũ                                                      | executed or set to '1' by firmware                           |  |  |  |  |

|                  |                         |                                                        | cuted (cleared by hardware)                                  |  |  |  |  |

| bit 1            |                         | on Reset Status bit                                    |                                                              |  |  |  |  |

|                  | 1 = No Powe             | er-on Reset occurred                                   |                                                              |  |  |  |  |

|                  | 0 = A Power             | -on Reset occurred (must                               | be set in software after a Power-on Reset occurs)            |  |  |  |  |

| bit 0            | BOR: Brown              | -out Reset Status bit                                  |                                                              |  |  |  |  |

|                  |                         | n-out Reset occurred                                   |                                                              |  |  |  |  |

|                  | 0 = A Brown-<br>occurs) | -out Reset occurred (must                              | be set in software after a Power-on Reset or Brown-out Reset |  |  |  |  |

|                  | occurs)                 |                                                        |                                                              |  |  |  |  |

'1' = Bit is set

#### 13.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| R/W-0/0         R/W-0/0 <t< th=""><th>0</th><th>bit</th><th>W = Writable</th><th>bit</th><th>U = Unimplen</th><th>nented bit, read</th><th>as '0'</th><th></th></t<> | 0       | bit       | W = Writable | bit     | U = Unimplen | nented bit, read | as '0'  |         |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|--------------|---------|--------------|------------------|---------|---------|--|--|--|--|

| IOCAP7     IOCAP6     IOCAP5     IOCAP4     IOCAP3     IOCAP2     IOCAP1     IOCAP0       bit 7     bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Legend: |           |              |         |              |                  |         |         |  |  |  |  |

| IOCAP7 IOCAP6 IOCAP5 IOCAP4 IOCAP3 IOCAP2 IOCAP1 IOCAP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend: |           |              |         |              |                  |         |         |  |  |  |  |

| IOCAP7 IOCAP6 IOCAP5 IOCAP4 IOCAP3 IOCAP2 IOCAP1 IOCAP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |           |              |         |              |                  |         |         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 7   | •         |              |         |              |                  | bit 0   |         |  |  |  |  |

| R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IOCAP7  | IOCAP6    | IOCAP5       | IOCAP4  | IOCAP3       | IOCAP2           | IOCAP1  | IOCAP0  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 10,00,0,0 | R/W-0/0      | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |  |  |  |

bit 7-0 **IOCAP<7:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

'0' = Bit is cleared

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCAN7  | IOCAN6  | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 IOCAN<7:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCAF7     | IOCAF6     | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

**IOCAF<7:0>:** Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

| R/W-0/0          | R/W-0/0                                                                                 | R/W-0/0                                                    | R/W-0/0                                                 | R/W-0/0                                               | R/W-0/0                       | R/W-0/0           | R/W-0/0    |

|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------|-------------------|------------|

| GxFSIM7          | GxFSIM6                                                                                 | GxFSIM5                                                    | GxFSIM4                                                 | GxFSIM3                                               | GxFSIM2                       | GxFSIM1           | GxFSIM0    |

| bit 7            |                                                                                         |                                                            |                                                         |                                                       |                               | •                 | bit (      |

|                  |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| Legend:          |                                                                                         |                                                            |                                                         |                                                       |                               |                   |            |

| R = Readable I   | pit                                                                                     | W = Writable                                               | bit                                                     | U = Unimplem                                          | nented bit, read              | as '0'            |            |

| u = Bit is uncha | anged                                                                                   | x = Bit is unkr                                            | iown                                                    | -n/n = Value a                                        | t POR and BOP                 | R/Value at all ot | her Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is clea                                          | ared                                                    | q = Value dep                                         | ends on conditi               | on                |            |

| bit 7            | <u>GxFIS7 = 1:</u><br>1 = NCO1_or                                                       |                                                            | ansition will ca                                        |                                                       | vent after falling<br>vent    | event phase de    | elay       |

|                  | <u>GxFIS7 = 0:</u>                                                                      |                                                            |                                                         |                                                       |                               |                   |            |

|                  | _                                                                                       | s no effect on f                                           | -                                                       |                                                       |                               |                   |            |

| bit 6            |                                                                                         | Gx Falling Eve                                             | ent Input Sourc                                         | e 6 Mode bit                                          |                               |                   |            |

|                  | 0 = PWM3 ou<br>GxFIS6 = 0:                                                              |                                                            | vill cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| oit 5            |                                                                                         | Gx Falling Eve                                             |                                                         |                                                       |                               |                   |            |

|                  | 0 = CCP2 ou<br>GxFIS5 = 0:                                                              |                                                            | ill cause an im                                         | cause a falling<br>mediate falling                    | event after fallin<br>event   | ng event phase    | delay      |

| bit 4            | GxFSIM4: CC                                                                             | Gx Falling Eve                                             | ent Input Sourc                                         | e 4 Mode bit                                          |                               |                   |            |

|                  | 0 = CCP1 low GxFIS4 = 0:                                                                | gh-to-low transi<br>v level will caus<br>effect on falling | e an immediat                                           |                                                       | after falling ever            | nt phase delay    |            |

| bit 3            |                                                                                         | )Gx Falling Eve                                            |                                                         | e 3 Mode bit                                          |                               |                   |            |

|                  | $\frac{GxFIS3 = 1}{1 = CLC1 \text{ out}}$ $0 = CLC1 \text{ out}$ $\frac{GxFIS3 = 0}{2}$ | tput high-to-low                                           | transition will<br>ill cause an im                      |                                                       | event after fallir<br>event   | ng event phase    | delay      |

| bit 2            |                                                                                         | )Gx Falling Eve                                            | ent Input Sourc                                         | e 2 Mode bit                                          |                               |                   |            |

|                  | 0 = Compara GxFIS2 = 0:                                                                 |                                                            | will cause an ir                                        | nmediate falling                                      | g event after fall<br>g event | ing event phase   | e delay    |

| bit 1            | <b>GxFSIM1:</b> CC<br><u>GxFIS1 = 1:</u><br>1 = Compara                                 | OGx Falling Eve<br>tor 1 high-to-lo<br>tor 1 low level v   | nt Input Source<br>w transition wil<br>will cause an ir | e 1 Mode bit<br>I cause a falling<br>nmediate falling | g event after fall<br>g event | ing event phase   | e delay    |

## REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

# PIC16(L)F1717/8/9

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                     | R/W-0/u                                                                                                                                                   | R/W-0/u        | R/W/HC-0/u                  | R-x/x            | R/W-0/u        | R/W-0/u      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|------------------|----------------|--------------|--|--|--|--|

| TMR1GE           | T1GPOL                                                                                                                                                                                                                      | T1GTM                                                                                                                                                     | T1GSPM         | T1GGO/<br>DONE              | T1GVAL           | T1GS           | S<1:0>       |  |  |  |  |

| bit 7            |                                                                                                                                                                                                                             |                                                                                                                                                           |                |                             |                  |                | bit (        |  |  |  |  |

| Logondi          |                                                                                                                                                                                                                             |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

| Legend:          | , hit                                                                                                                                                                                                                       |                                                                                                                                                           | hit            |                             | optod bit room   |                |              |  |  |  |  |

| R = Readable     |                                                                                                                                                                                                                             | W = Writable                                                                                                                                              |                |                             | nented bit, read |                | athar Daaata |  |  |  |  |

| u = Bit is unch  | •                                                                                                                                                                                                                           | x = Bit is unki                                                                                                                                           |                |                             |                  | R/Value at all | Juner Reseis |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                             | '0' = Bit is cle                                                                                                                                          | areu           |                             | eared by hardw   | ale            |              |  |  |  |  |

| bit 7            |                                                                                                                                                                                                                             | mer1 Gate Ena                                                                                                                                             | ble bit        |                             |                  |                |              |  |  |  |  |

|                  | This bit is ign<br>If TMR1ON =                                                                                                                                                                                              | <u>If TMR1ON = 0</u> :<br>This bit is ignored<br><u>If TMR1ON = 1</u> :<br>1 = Timer1 counting is controlled by the Timer1 gate function                  |                |                             |                  |                |              |  |  |  |  |

|                  | 0 = Timer1 c                                                                                                                                                                                                                | ounts regardle                                                                                                                                            | ss of Timer1 g | ate function                |                  |                |              |  |  |  |  |

| bit 6            | T1GPOL: Timer1 Gate Polarity bit                                                                                                                                                                                            |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

|                  |                                                                                                                                                                                                                             | <ul><li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li><li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li></ul> |                |                             |                  |                |              |  |  |  |  |

| bit 5            | T1GTM: Timer1 Gate Toggle Mode bit                                                                                                                                                                                          |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

|                  | 0 = Timer1 C                                                                                                                                                                                                                |                                                                                                                                                           | de is disabled | and toggle flip-<br>g edge. | flop is cleared  |                |              |  |  |  |  |

| bit 4            | Timer1 gate flip-flop toggles on every rising edge.<br><b>T1GSPM:</b> Timer1 Gate Single-Pulse Mode bit                                                                                                                     |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

|                  |                                                                                                                                                                                                                             | Gate Single-Pul<br>Gate Single-Pul                                                                                                                        |                | abled and is co<br>abled    | ntrolling Timer  | 1 gate         |              |  |  |  |  |

| bit 3            | T1GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                                                                                                                                                                 |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

|                  | <ul> <li>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> </ul>                                          |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

| bit 2            | T1GVAL: Timer1 Gate Value Status bit                                                                                                                                                                                        |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

|                  | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L<br>Unaffected by Timer1 Gate Enable (TMR1GE)                                                                                           |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

| bit 1-0          | T1GSS<1:0>                                                                                                                                                                                                                  | : Timer1 Gate                                                                                                                                             | Source Select  | bits                        |                  |                |              |  |  |  |  |

|                  | <ul> <li>11 = Comparator 2 optionally synchronized output (sync_C2OUT)</li> <li>10 = Comparator 1 optionally synchronized output (sync_C1OUT)</li> <li>01 = Timer0 overflow output</li> <li>00 = Timer1 gate pin</li> </ul> |                                                                                                                                                           |                |                             |                  |                |              |  |  |  |  |

### REGISTER 27-2: T1GCON: TIMER1 GATE CONTROL REGISTER

## PIC16(L)F1717/8/9

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 29-4).

#### 29.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

### EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

TABLE 29-1:

EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 29.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 29.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

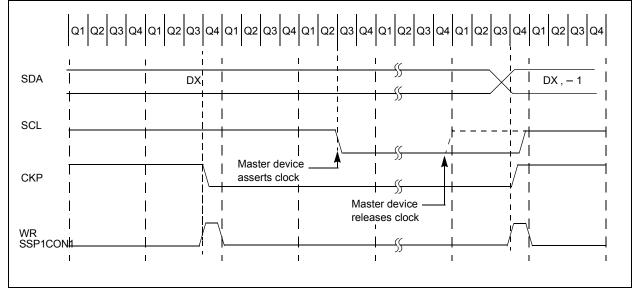

#### 30.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSP1CON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 30.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSP1STAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSP1BUF with data to transfer to the master. If the SEN bit of SSP1CON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSP1BUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSP1BUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 30.5.6.2 10-Bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSP1ADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 30.5.6.3 Byte NACKing

When AHEN bit of SSP1CON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSP1CON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

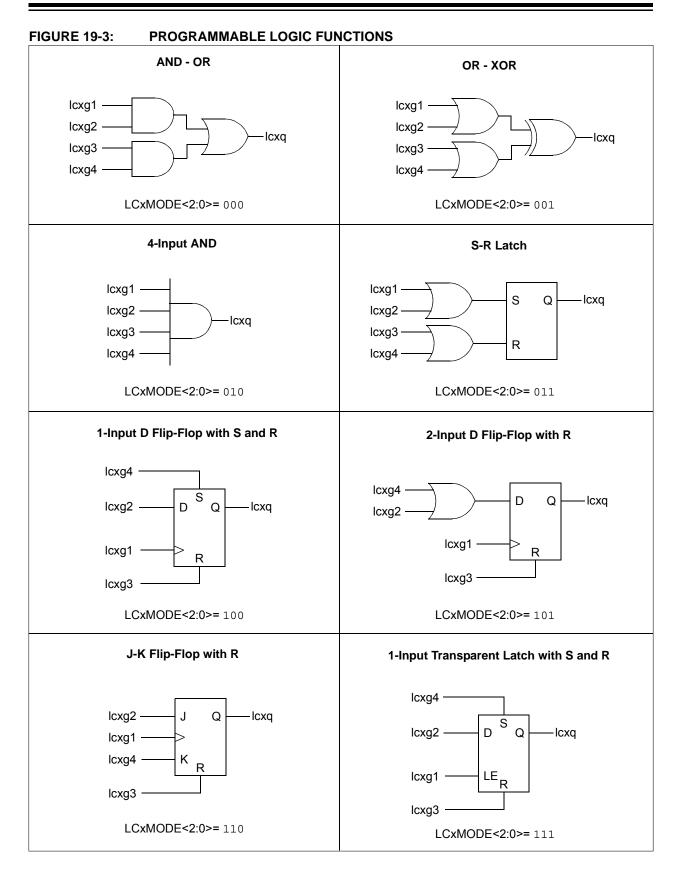

## 30.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 30-23).

#### 30.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSP1BUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSP1IF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSP1BUF, leaving SCL low and SDA unchanged (Figure 30-28).

After the write to the SSP1BUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSP1CON2 register. Following the falling edge of the ninth clock transmission of the address, the SSP1IF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSP1BUF takes place, holding SCL low and allowing SDA to float.

#### 30.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSP1STAT register is set when the CPU writes to SSP1BUF and is cleared when all eight bits are shifted out.

#### 30.6.6.2 WCOL Status Flag

If the user writes the SSP1BUF when a transmit is already in progress (i.e., SSP1SR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 30.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSP1CON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

30.6.6.4 Typical Transmit Sequence

- 1. The user generates a Start condition by setting the SEN bit of the SSP1CON2 register.

- 2. SSP1IF is set by hardware on completion of the Start.

- 3. SSP1IF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSP1BUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSP1BUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSP1CON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSP1IF bit.

- 9. The user loads the SSP1BUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSP1CON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSP1CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                   | R/W-0/0        | R/W-0/0        | R-0/0            | R-0/0            | R-0/0       |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN                                                                                                      | CREN           | ADDEN          | FERR             | OERR             | RX9D        |  |  |  |  |  |

| bit 7            |                                                                                                                                                    | ·                                                                                                         |                |                |                  |                  | bit C       |  |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                           |                |                |                  |                  |             |  |  |  |  |  |

| Legend:          |                                                                                                                                                    |                                                                                                           |                |                |                  |                  |             |  |  |  |  |  |

| R = Readable     | e bit                                                                                                                                              | W = Writable                                                                                              | bit            | U = Unimpler   | mented bit, read | as '0'           |             |  |  |  |  |  |

| u = Bit is unc   | hanged                                                                                                                                             | x = Bit is unki                                                                                           | nown           | -n/n = Value   | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |  |

| '1' = Bit is set | :                                                                                                                                                  | '0' = Bit is cle                                                                                          | ared           |                |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                           |                |                |                  |                  |             |  |  |  |  |  |

| bit 7            |                                                                                                                                                    | Port Enable bi                                                                                            | t              |                |                  |                  |             |  |  |  |  |  |

|                  | 1 = Serial po                                                                                                                                      | rt enabled<br>rt disabled (he                                                                             | ld in Reset)   |                |                  |                  |             |  |  |  |  |  |