Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1719-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1717/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

#### 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect **Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16(L)F1717   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |

| PIC16(L)F1718/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

|                   |                                                                                                                                | R/P-1                                                                                                                                                                                                                          | R/P-1                                                                                                                                                    | R/P-1                                                                                                   | R/P-1                                                                                               | R/P-1                                                                       | R/P-1 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|

|                   |                                                                                                                                | LVP <sup>(1)</sup>                                                                                                                                                                                                             | DEBUG <sup>(2)</sup>                                                                                                                                     | LPBOR                                                                                                   | BORV <sup>(3)</sup>                                                                                 | STVREN                                                                      | PLLEN |

|                   |                                                                                                                                | bit 13                                                                                                                                                                                                                         |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             | bit 8 |

| R/P-1             | U-1                                                                                                                            | U-1                                                                                                                                                                                                                            | U-1                                                                                                                                                      | U-1                                                                                                     | R/P-1                                                                                               | R/P-1                                                                       | R/P-1 |

| ZCDDIS            | _                                                                                                                              | _                                                                                                                                                                                                                              | _                                                                                                                                                        | _                                                                                                       | PPS1WAY                                                                                             | WRT                                                                         |       |

| bit 7             |                                                                                                                                |                                                                                                                                                                                                                                |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             | bit   |

| Legend:           |                                                                                                                                |                                                                                                                                                                                                                                |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |

| R = Readable      | bit                                                                                                                            | P = Programm                                                                                                                                                                                                                   | able bit                                                                                                                                                 | U = Unimpleme                                                                                           | ented bit, read as                                                                                  | '1'                                                                         |       |

| '0' = Bit is clea | ared                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                               |                                                                                                                                                          | -n = Value wher                                                                                         | n blank or after B                                                                                  | ulk Erase                                                                   |       |

| bit 13            | 1 = Low-volta                                                                                                                  | Itage Programmin<br>ige programming e<br>age on MCLR mus                                                                                                                                                                       | enabled                                                                                                                                                  | gramming                                                                                                |                                                                                                     |                                                                             |       |

| bit 12            | <b>DEBUG:</b> In-C<br>1 = In-Circuit                                                                                           | Circuit Debugger N<br>Debugger disable<br>Debugger enable                                                                                                                                                                      | lode bit <sup>(2)</sup><br>d, ICSPCLK and                                                                                                                | ICSPDAT are ge                                                                                          |                                                                                                     | •                                                                           |       |

| bit 11            | 1 = Low-Pow                                                                                                                    | -Power BOR Enal<br>er Brown-out Rese<br>er Brown-out Rese                                                                                                                                                                      | et is disabled                                                                                                                                           |                                                                                                         |                                                                                                     |                                                                             |       |

| bit 10            | 1 = Brown-ou                                                                                                                   | n-out Reset Voltag<br>it Reset voltage (V<br>it Reset voltage (V                                                                                                                                                               | BOR), low trip poi                                                                                                                                       |                                                                                                         |                                                                                                     |                                                                             |       |

| bit 9             | 1 = Stack Ove                                                                                                                  | ack Overflow/Unde<br>erflow or Underflow<br>erflow or Underflow                                                                                                                                                                | w will cause a Re                                                                                                                                        | set                                                                                                     |                                                                                                     |                                                                             |       |

| bit 8             | <b>PLLEN:</b> PLL<br>1 = 4xPLL en<br>0 = 4xPLL dis                                                                             | abled                                                                                                                                                                                                                          |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |

| bit 7             | <b>ZCDDIS:</b> ZCI<br>1 = ZCD disa<br>0 = ZCD alwa                                                                             | bled. ZCD can be                                                                                                                                                                                                               | enabled by settin                                                                                                                                        | ig the ZCDSEN b                                                                                         | bit of ZCDCON                                                                                       |                                                                             |       |

| bit 6-3           | Unimplemen                                                                                                                     | ted: Read as '1'                                                                                                                                                                                                               |                                                                                                                                                          |                                                                                                         |                                                                                                     |                                                                             |       |

| bit 2             | 1 = The PPS<br>future ch                                                                                                       | PSLOCK Bit One-<br>LOCK bit can only<br>nanges to PPS reg<br>LOCK bit can be s                                                                                                                                                 | y be set once afte<br>gisters are preven                                                                                                                 | er an unlocking s<br>ted                                                                                |                                                                                                     |                                                                             |       |

| bit 1-0           | WRT<1:0>: F<br>8 kW Flash m<br>11 = Wri<br>10 = 000<br>01 = 000<br>00 = 000<br>16 kW Flash<br>11 = Wri<br>10 = 000<br>01 = 000 | Flash Memory Self<br><u>hemory (PIC16(L))</u><br>ite protection off<br>00h to 01FFh write<br>00h to 1FFh write<br><u>memory (PIC16(L</u><br>ite protection off<br>00h to 01FFh write<br>00h to 1FFh write<br>00h to 3FFh write | -Write Protection<br>-1717)<br>-protected, 02001<br>-protected, 10001<br>-protected, no ad<br><u>)F1718/9)</u><br>-protected, 02001<br>-protected, 20001 | bits<br>h to 1FFFh may b<br>h to 1FFFh may b<br>ldresses may be<br>h to 3FFFh may b<br>h to 3FFFh may b | be modified by Pl<br>be modified by Pl<br>modified by PMC<br>be modified by Pl<br>be modified by Pl | MCON control<br>MCON control<br>CON control<br>MCON control<br>MCON control |       |

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

3: See VBOR parameter for specific trip point voltages.

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL or EXTRC modes) and switch automatically to the internal oscillator

- Oscillator Start-up Timer (OST), which ensures stability of crystal oscillator sources

The oscillator module can be configured in one of the following clock modes:

- ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. EXTRC External Resistor-Capacitor

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device.

Each mode is optimized for a different frequency range. The EXTRC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these three clock sources.

#### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3** "**Clock Switching**" for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 6.3** "Clock Switching" for more information.

#### 6.2.1.1 EC Mode

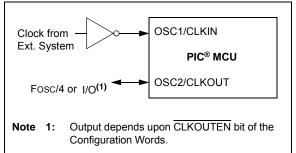

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

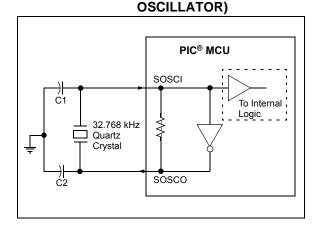

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (see Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### 6.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4x PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 34-9: PLL Clock Timing Specifications.

The 4x PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

#### 6.2.1.5 Secondary Oscillator

The secondary oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 6.3 "Clock Switching"** for more information.

#### FIGURE 6-5: QUARTZ CRYSTAL OPERATION (SECONDARY

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

| U-0              | U-0   | U-0               | U-0  | R/W-1/1      | R/W-1/1              | R/W-1/1              | R/W-1/1              |

|------------------|-------|-------------------|------|--------------|----------------------|----------------------|----------------------|

| —                | _     | _                 | _    | WPUE3        | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> |

| bit 7            |       | ·                 |      |              |                      | •                    | bit 0                |

|                  |       |                   |      |              |                      |                      |                      |

| Legend:          |       |                   |      |              |                      |                      |                      |

| R = Readable     | bit   | W = Writable      | bit  | U = Unimplei | mented bit, read     | as '0'               |                      |

| u = Bit is unch  | anged | x = Bit is unkr   | nown | -n/n = Value | at POR and BO        | R/Value at all c     | ther Resets          |

| '1' = Bit is set |       | '0' = Bit is clea | ared |              |                      |                      |                      |

#### **REGISTER 11-37: WPUE: WEAK PULL-UP PORTE REGISTER**<sup>(1,2)</sup>

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WPUE<3:0>: Weak Pull-up Register bits 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- 3: PIC16(L)F1717/9 only.

#### REGISTER 11-38: ODCONE: PORTE OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ODE2    | ODE1    | ODE0    |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ODE<2:0>:** PORTE Open-Drain Enable bits For RE<2:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** PIC16(L)F1717/9 only.

## PIC16(L)F1717/8/9

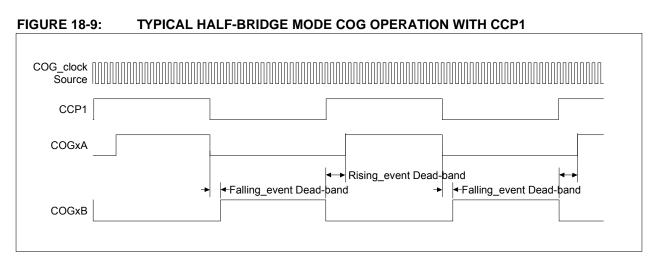

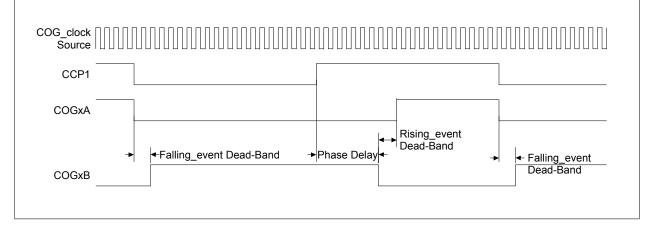

#### FIGURE 18-10: HALF-BRIDGE MODE COG OPERATION WITH CCP1 AND PHASE DELAY

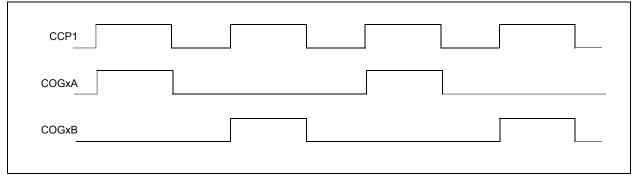

#### FIGURE 18-11: PUSH-PULL MODE COG OPERATION WITH CCP1

#### REGISTER 18-10: COGxDBR: COG RISING EVENT DEAD-BAND COUNT REGISTER

| U-0              | U-0                      | R/W-x/u           | R/W-x/u                                                                  | R/W-x/u       | R/W-x/u          | R/W-x/u  | R/W-x/u |  |  |

|------------------|--------------------------|-------------------|--------------------------------------------------------------------------|---------------|------------------|----------|---------|--|--|

| _                | _                        |                   |                                                                          | GxDB          | R<5:0>           |          |         |  |  |

| bit 7            |                          | ·                 |                                                                          |               |                  |          | bit 0   |  |  |

|                  |                          |                   |                                                                          |               |                  |          |         |  |  |

| Legend:          |                          |                   |                                                                          |               |                  |          |         |  |  |

| R = Readable     | bit                      | W = Writable      | bit                                                                      | U = Unimpler  | nented bit, read | l as '0' |         |  |  |

| u = Bit is uncha | = Bit is unchanged x = I |                   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |               |                  |          |         |  |  |

| '1' = Bit is set |                          | '0' = Bit is clea | ared                                                                     | g = Value deg | pends on condit  | ion      |         |  |  |

bit 7-6 Unimplemented: Read as '0' bit 5-0 GxDBR<5:0>: Rising Event Dead-band Count Value bits GxRDBS = 1: = Number of delay chain element periods to delay primary output after rising event GxRDBS = 0: = Number of COGx clock periods to delay primary output after rising event

#### REGISTER 18-11: COGxDBF: COG FALLING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

|       | —   |         |         | GxDB    | F<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 GxDBF<5:0>: Falling Event Dead-band Count Value bits

GxFDBS = 1:

= Number of delay chain element periods to delay complementary output after falling event input GxFDBS = 0:

= Number of COGx clock periods to delay complementary output after falling event input

| Name     | Bit 7   | Bit 6   | Bit 5   | Bit 4      | Bit 3   | Bit 2       | Bit 1     | Bit 0   | Register<br>on Page |

|----------|---------|---------|---------|------------|---------|-------------|-----------|---------|---------------------|

| ANSELA   | _       | -       | ANSA5   | ANSA4      | ANSA3   | ANSA2       | ANSA1     | ANSA0   | 125                 |

| ANSELB   | _       | _       | ANSB5   | ANSB4      | ANSB3   | ANSB2       | ANSB1     | ANSB0   | 131                 |

| ANSELC   | ANSC7   | ANSC6   | ANSC5   | ANSC4      | ANSC3   | ANSC2       | _         | _       | 136                 |

| COG1PHR  | _       | _       |         |            | G1PH    | R<5:0>      |           |         | 216                 |

| COG1PHF  | _       | _       |         |            | G1PH    | F<5:0>      |           |         | 216                 |

| COG1BLKR | _       | _       |         |            | G1BLK   | (R<5:0>     |           |         | 215                 |

| COG1BLKF | _       | _       |         |            | G1BLK   | (F<5:0>     |           |         | 215                 |

| COG1DBR  |         | _       |         |            | G1DB    | R<5:0>      |           |         | 214                 |

| COG1DBF  | _       | _       |         | G1DBF<5:0> |         |             |           |         |                     |

| COG1RIS  | G1RIS7  | G1RIS6  | G1RIS5  | G1RIS4     | G1RIS3  | G1RIS2      | G1RIS1    | G1RIS0  | 205                 |

| COG1RSIM | G1RSIM7 | G1RSIM6 | G1RSIM5 | G1RSIM4    | G1RSIM3 | G1RSIM2     | G1RSIM1   | G1RSIM0 | 206                 |

| COG1FIS  | G1FIS7  | G1FIS6  | G1FIS5  | G1FIS4     | G1FIS3  | G1FIS2      | G1FIS1    | G1FIS0  | 208                 |

| COG1FSIM | G1FSIM7 | G1FSIM6 | G1FSIM5 | G1FSIM4    | G1FSIM3 | G1FSIM2     | G1FSIM1   | G1FSIM0 | 209                 |

| COG1CON0 | G1EN    | G1LD    | —       | G1CS       | 6<1:0>  |             | G1MD<2:0> |         | 203                 |

| COG1CON1 | G1RDBS  | G1FDBS  |         | _          | G1POLD  | G1POLC      | G1POLB    | G1POLA  | 204                 |

| COG1ASD0 | G1ASE   | G1ARSEN | G1ASD   | BD<1:0>    | G1ASD   | AC<1:0>     | —         | —       | 211                 |

| COG1ASD1 |         | _       |         | _          | G1AS3E  | G1AS2E      | G1AS1E    | G1AS0E  | 212                 |

| COG1STR  | G1SDATD | G1SDATC | G1SDATB | G1SDATA    | G1STRD  | G1STRC      | G1STRB    | G1STRA  | 213                 |

| INTCON   | GIE     | PEIE    | T0IE    | INTE       | IOCIE   | TOIF        | INTF      | IOCIF   | 90                  |

| COG1PPS  | _       | —       | _       |            |         | COG1PPS<4:0 | >         |         | 136                 |

| PIE2     | OSFIE   | C2IE    | C1IE    | —          | BCL1IE  | TMR6IE      | TMR4IE    | CCP2IE  | 92                  |

| PIR2     | OSFIF   | C2IF    | C1IF    | —          | BCL1IF  | TMR6IF      | TMR4IF    | CCP2IF  | 95                  |

| RxyPPS   | -       | _       | _       |            |         | RxyPPS<4:0> |           |         | 153                 |

TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH COG

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by COG.

#### 20.8 Register Definitions: NCOx Control Registers

|                                  |             |                                                                                                       | CONTROL      | LOISTEN        |                  |                  |              |

|----------------------------------|-------------|-------------------------------------------------------------------------------------------------------|--------------|----------------|------------------|------------------|--------------|

| R/W-0/0                          | U-0         | R-0/0                                                                                                 | R/W-0/0      | U-0            | U-0              | U-0              | R/W-0/0      |

| NxEN                             | —           | NxOUT                                                                                                 | NxPOL        | _              | —                | —                | NxPFM        |

| bit 7                            |             |                                                                                                       |              |                |                  |                  | bit 0        |

|                                  |             |                                                                                                       |              |                |                  |                  |              |

| Legend:                          |             |                                                                                                       |              |                |                  |                  |              |

| R = Readable                     | e bit       | W = Writable                                                                                          | bit          | U = Unimpler   | nented bit, read | l as '0'         |              |

| u = Bit is unch                  | nanged      | x = Bit is unkr                                                                                       | nown         | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set                 |             | '0' = Bit is cle                                                                                      | ared         |                |                  |                  |              |

| bit 7<br>bit 6<br>bit 5<br>bit 4 | 0 = NCOx mo | odule is enable<br>odule is disable<br>ted: Read as '<br>ox Output bit<br>tput is high<br>tput is low | d            |                |                  |                  |              |

| DIT 4                            | 1 = NCOx ou | tput signal is a tput signal is a                                                                     | •            | ,              |                  |                  |              |

| bit 3-1                          | Unimplemen  | ted: Read as '                                                                                        | 0'           |                |                  |                  |              |

| bit 0                            | 1 = NCOx op | Dx Pulse Freque<br>erates in Pulse<br>erates in Fixed                                                 | Frequency mo | ode            |                  |                  |              |

#### REGISTER 20-1: NCOxCON: NCOx CONTROL REGISTER

| R/W-0/0         | R/W-0/0                                                             | R/W-0/0                                                                                                                 | U-0          | U-0            | U-0             | R/W-0/0          | R/W-0/0      |

|-----------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-----------------|------------------|--------------|

|                 | NxPWS<2:0>(                                                         | 1, 2)                                                                                                                   | —            | —              | —               | NxCKS<1:0>       |              |

| bit 7           |                                                                     |                                                                                                                         |              |                |                 |                  | bit C        |

| Legend:         |                                                                     |                                                                                                                         |              |                |                 |                  |              |

| R = Readab      | le bit                                                              | W = Writable b                                                                                                          | oit          | U = Unimplem   | ented bit, read | d as '0'         |              |

| u = Bit is un   | changed                                                             | x = Bit is unkn                                                                                                         | own          | -n/n = Value a | t POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | et                                                                  | '0' = Bit is clea                                                                                                       | red          |                |                 |                  |              |

|                 | 100 = 16 NC<br>011 = 8 NC<br>010 = 4 NC<br>001 = 2 NC<br>000 = 1 NC | COx clock periods<br>COx clock periods<br>COx clock periods<br>Ox clock periods<br>Ox clock periods<br>Ox clock periods | 3            |                |                 |                  |              |

| bit 4-2         | -                                                                   | nted: Read as '0                                                                                                        |              |                |                 |                  |              |

| bit 1-0         | 11 = Reser<br>10 = LC3_c<br>01 = Fosc                               |                                                                                                                         | Source Selec | ct bits        |                 |                  |              |

#### REGISTER 20-2: NCOxCLK: NCOx INPUT CLOCK CONTROL REGISTER

Note 1: NxPWS applies only when operating in Pulse Frequency mode.

2: If NCOx pulse width is greater than NCO\_overflow period, operation is undeterminate.

#### REGISTER 20-3: NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | NCOXA   | \CC<7:0>       |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | nanged  | x = Bit is unkn   | own     | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 NCOxACC<7:0>: NCOx Accumulator, Low Byte

#### 28.5 Register Definitions: Timer2 Control

#### REGISTER 28-1: T2CON: TIMER2 CONTROL REGISTER

| U-0                          | R/W-0/0                      | R/W-0/0           | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0      |

|------------------------------|------------------------------|-------------------|----------------|-----------------|------------------|---------|--------------|

| _                            |                              | T2OUTF            | PS<3:0>        |                 | TMR2ON           | T2CKF   | °S<1:0>      |

| bit 7                        | ·                            |                   |                |                 |                  |         | bit          |

|                              |                              |                   |                |                 |                  |         |              |

| <b>Legend:</b><br>R = Readab | le hit                       | W = Writable      | hit            | II = I Inimplei | mented bit, read | as '0'  |              |

| u = Bit is un                |                              | x = Bit is unkr   |                | -               | at POR and BO    |         | othor Docote |

|                              | •                            | 0' = Bit is clear |                | at FOR and BO   | N value at all   |         |              |

| '1' = Bit is s               | el                           | 0 = Bit is clea   | ared           |                 |                  |         |              |

| bit 7                        | Unimpleme                    | nted: Read as '   | 0'             |                 |                  |         |              |

| bit 6-3                      | T2OUTPS<                     | 3:0>: Timer2 Ou   | tput Postscale | er Select bits  |                  |         |              |

|                              | 1111 <b>= 1:16</b>           | Postscaler        |                |                 |                  |         |              |

|                              | 1110 <b>= 1:15</b>           | Postscaler        |                |                 |                  |         |              |

|                              | 1101 <b>= 1:14</b>           |                   |                |                 |                  |         |              |

|                              | 1100 = 1:13                  |                   |                |                 |                  |         |              |

|                              | 1011 = 1:12                  |                   |                |                 |                  |         |              |

|                              | 1010 = 1:11<br>1001 = 1:10   |                   |                |                 |                  |         |              |

|                              | 1001 = 1.10<br>1000 = 1.9 F  |                   |                |                 |                  |         |              |

|                              | 0111 = 1:8 F                 |                   |                |                 |                  |         |              |

|                              | 0110 = <b>1</b> : <b>7</b> F |                   |                |                 |                  |         |              |

|                              | 0101 = 1:6 F                 | Postscaler        |                |                 |                  |         |              |

|                              | 0100 = 1:5 F                 | Postscaler        |                |                 |                  |         |              |

|                              | 0011 = 1:4 F                 | Postscaler        |                |                 |                  |         |              |

|                              | 0010 = 1:3 F                 |                   |                |                 |                  |         |              |

|                              | 0001 = 1:2 F                 |                   |                |                 |                  |         |              |

| <b>L</b> H 0                 | 0000 = 1:1 F                 |                   |                |                 |                  |         |              |

| bit 2                        | TMR2ON: T                    |                   |                |                 |                  |         |              |

|                              | 1 = Timer2 i<br>0 = Timer2 i |                   |                |                 |                  |         |              |

| bit 1-0                      | T2CKPS<1:                    | 0>: Timer2 Cloc   | k Prescale Se  | elect bits      |                  |         |              |

|                              | 11 = Presca                  | ler is 64         |                |                 |                  |         |              |

|                              | 10 = Presca                  | ler is 16         |                |                 |                  |         |              |

|                              | 01 = Presca                  | ler is 4          |                |                 |                  |         |              |

|                              | 00 = Presca                  |                   |                |                 |                  |         |              |

## PIC16(L)F1717/8/9

#### 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 27.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 29.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | S;Load the W reg with   |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

#### 29.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by FOSC/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

# PIC16(L)F1717/8/9

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 29-4).

#### 29.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

#### EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

TABLE 29-1:

EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 29.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 29.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

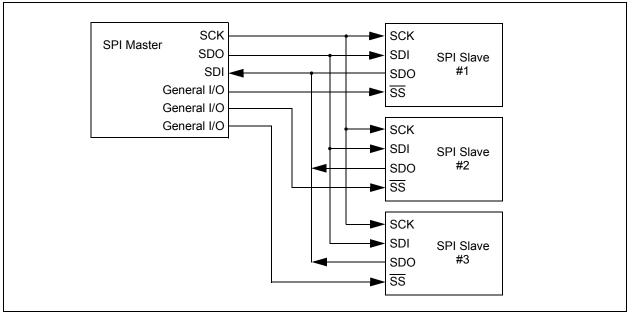

#### 30.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSP1STAT)

- MSSP Control register 1 (SSP1CON1)

- MSSP Control register 3 (SSP1CON3)

- MSSP Data Buffer register (SSP1BUF)

- MSSP Address register (SSP1ADD)

- MSSP Shift register (SSP1SR)

- (Not directly accessible)

SSP1CON1 and SSP1STAT are the control and STA-TUS registers in SPI mode operation. The SSP1CON1 register is readable and writable. The lower six bits of the SSP1STAT are read-only. The upper two bits of the SSP1STAT are read/write.

In one SPI master mode, SSP1ADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 30.7 "Baud Rate Generator"**.

SSP1SR is the shift register used for shifting data in and out. SSP1BUF provides indirect access to the SSP1SR register. SSP1BUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSP1SR and SSP1BUF together create a buffered receiver. When SSP1SR receives a complete byte, it is transferred to SSP1BUF and the SSP1IF interrupt is set.

During transmission, the SSP1BUF is not buffered. A write to SSP1BUF will write to both SSP1BUF and SSP1SR.

#### 30.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSP1CON1<5:0> and SSP1STAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSP1CON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSP1CONx registers and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- SDO must have corresponding TRIS bit cleared

SCK (Master mode) must have corresponding

- TRIS bit cleared

- SCK (Slave mode) must have corresponding <u>TRIS</u> bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

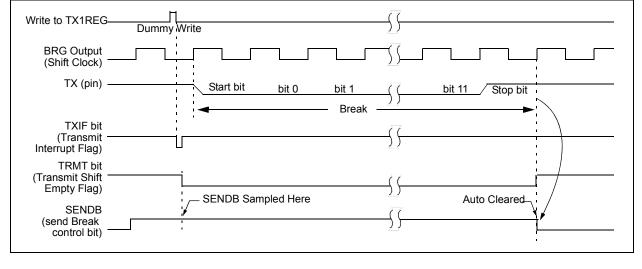

#### 31.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TX1STA register. The Break character transmission is then initiated by a write to the TX1REG. The value of data written to TX1REG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TX1STA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 31-9 for the timing of the Break character sequence.

#### 31.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TX1REG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TX1REG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TX1REG becomes empty, as indicated by the TXIF, the next data byte can be written to TX1REG.

#### 31.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RC1STA register and the received data as indicated by RC1REG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RC1REG = 00h

The second method uses the Auto-Wake-up feature described in **Section 31.4.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUD1CON register before placing the EUSART in Sleep mode.

#### FIGURE 31-9: SEND BREAK CHARACTER SEQUENCE

### TABLE 31-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name     | Bit 7   | Bit 6  | Bit 5  | Bit 4     | Bit 3        | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------|--------|--------|-----------|--------------|-----------|--------|--------|---------------------|

| ANSELB   | —       | —      | ANSB5  | ANSB4     | ANSB3        | ANSB2     | ANSB1  | ANSB0  | 131                 |

| ANSELC   | ANSC7   | ANSC6  | ANSC5  | ANSC4     | ANSC3        | ANSC2     | —      | —      | 136                 |

| BAUD1CON | ABDOVF  | RCIDL  | _      | SCKP      | BRG16        | _         | WUE    | ABDEN  | 362                 |

| INTCON   | GIE     | PEIE   | TMR0IE | INTE      | IOCIE        | TMR0IF    | INTF   | IOCIF  | 90                  |

| PIE1     | TMR1GIE | ADIE   | RCIE   | TXIE      | SSP1IE       | CCP1IE    | TMR2IE | TMR1IE | 91                  |

| PIR1     | TMR1GIF | ADIF   | RCIF   | TXIF      | SSP1IF       | CCP1IF    | TMR2IF | TMR1IF | 94                  |

| RC1STA   | SPEN    | RX9    | SREN   | CREN      | ADDEN        | FERR      | OERR   | RX9D   | 361                 |

| RxyPPS   | —       | —      | —      |           | R            | xyPPS<4:0 | >      |        | 153                 |

| SP1BRGL  |         |        |        | SP1BR     | G<7:0>       |           |        |        | 363                 |

| SP1BRGH  |         |        |        | SP1BR0    | 6<15:8>      |           |        |        | 363                 |

| TRISB    | TRISB7  | TRISB6 | TRISB5 | TRISB4    | TRISB3       | TRISB2    | TRISB1 | TRISB0 | 130                 |

| TRISC    | TRISC7  | TRISC6 | TRISC5 | TRISC4    | TRISC3       | TRISC2    | TRISC1 | TRISC0 | 135                 |

| TX1REG   |         |        | EUSA   | RT Transm | nit Data Reg | ister     |        |        | 353*                |

| TX1STA   | CSRC    | TX9    | TXEN   | SYNC      | SENDB        | BRGH      | TRMT   | TX9D   | 360                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission. \* Page provides register information.

| Name     | Bit 7   | Bit 6  | Bit 5  | Bit 4     | Bit 3        | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------|--------|--------|-----------|--------------|-----------|--------|--------|---------------------|

| ANSELB   | —       | —      | ANSB5  | ANSB4     | ANSB3        | ANSB2     | ANSB1  | ANSB0  | 131                 |

| ANSELC   | ANSC7   | ANSC6  | ANSC5  | ANSC4     | ANSC3        | ANSC2     | —      | —      | 136                 |

| BAUD1CON | ABDOVF  | RCIDL  | —      | SCKP      | BRG16        | _         | WUE    | ABDEN  | 362                 |

| CKPPS    | —       | —      | —      |           | (            | CKPPS<4:0 | >      |        | 152                 |

| INTCON   | GIE     | PEIE   | TMR0IE | INTE      | IOCIE        | TMR0IF    | INTF   | IOCIF  | 90                  |

| PIE1     | TMR1GIE | ADIE   | RCIE   | TXIE      | SSP1IE       | CCP1IE    | TMR2IE | TMR1IE | 91                  |

| PIR1     | TMR1GIF | ADIF   | RCIF   | TXIF      | SSP1IF       | CCP1IF    | TMR2IF | TMR1IF | 94                  |

| RC1STA   | SPEN    | RX9    | SREN   | CREN      | ADDEN        | FERR      | OERR   | RX9D   | 361                 |

| RxyPPS   | —       | —      | —      |           | F            | xyPPS<4:0 | >      |        | 153                 |

| TRISB    | TRISB7  | TRISB6 | TRISB5 | TRISB4    | TRISB3       | TRISB2    | TRISB1 | TRISB0 | 130                 |

| TRISC    | TRISC7  | TRISC6 | TRISC5 | TRISC4    | TRISC3       | TRISC2    | TRISC1 | TRISC0 | 135                 |

| TX1REG   |         |        | EUSA   | RT Transm | nit Data Reg | lister    |        |        | 353*                |

| TX1STA   | CSRC    | TX9    | TXEN   | SYNC      | SENDB        | BRGH      | TRMT   | TX9D   | 360                 |

|          |         |        |        |           |              |           |        |        |                     |

### TABLE 31-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission. \* Page provides register information.

### 31.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 31.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RC1REG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

#### 31.5.2.4 Synchronous Slave Reception Setup

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RC1STA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RC1REG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART.

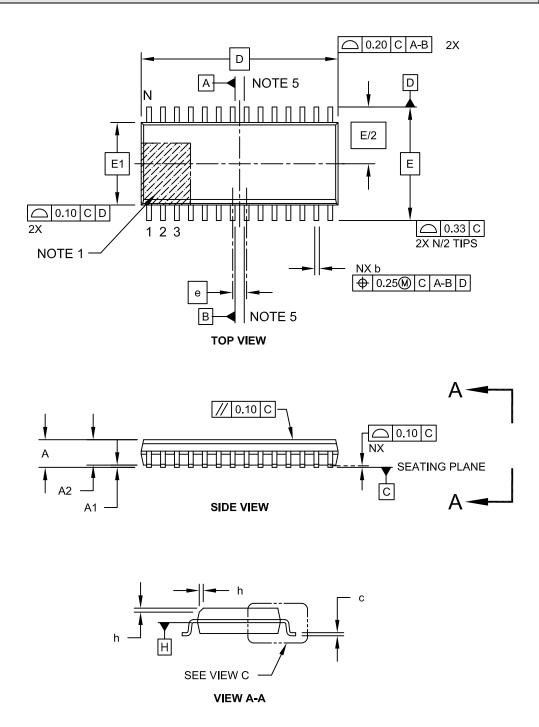

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15