Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d14a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SAM L10/L11 Family Pinouts

|            | Р          | in          |                           | Pin<br>Name            | Supply | A             |     |     | в <u>(</u> | <u>1)</u> |     |       | C <u>(2)(3)</u> | D(2)(3)                       | E             | G             | н              | I      | Reset<br>State   |

|------------|------------|-------------|---------------------------|------------------------|--------|---------------|-----|-----|------------|-----------|-----|-------|-----------------|-------------------------------|---------------|---------------|----------------|--------|------------------|

| SSOP2<br>4 | VQFN2<br>4 | WLCSP<br>32 | TQFP32<br>/<br>VQFN3<br>2 |                        |        | EIC           | REF | ADC | AC         | РТС       | DAC | OPAMP | SERCO<br>M      | SERCO<br>M<br>ALTER<br>NATIVE | тс            | RTC/<br>Debug | AC/<br>GCLK    | CCL    |                  |

| 3          | 24         | B2          | 31                        | PA30 /<br>SWCLK        | VDDIO  | EXTIN<br>T[6] |     |     |            | XY[18]    |     |       |                 | SERCO<br>M1/<br>PAD[2]        | TC1/<br>WO[0] | SWCLK         | GCLK_I<br>O[0] | IN[3]  | SWCLK<br>, I, PU |

| 4          | 1          | C3          | 32                        | PA31 /<br>SWDIO(<br>4) | VDDIO  | EXTIN<br>T[7] |     |     |            | XY[19]    |     |       |                 | SERCO<br>M1/<br>PAD[3]        | TC1/<br>WO[1] |               |                | OUT[1] | I/O, Hi-Z        |

- 1. All analog pin functions are on the peripheral function B. The peripheral function B must be selected to disable the digital control of the pin.

- 2. Refer to SERCOM Configurations to get the list of the supported features for each SERCOM instance.

- 3. 24-pin packages only have two SERCOM instances: SERCOM0 and SERCOM1.

- 4. The following pins are High Sink pins and have different properties than standard pins: PA16, PA17, PA22, PA23 and PA31.

## 4.2 Oscillators Pinout

The oscillators are not mapped to the I/O Pin Controller (PORT) functions and their multiplexing is controlled by the Oscillators Controller (OSCCTRL) and 32 kHz Oscillators Controller (OSC32KCTRL) registers.

#### Table 4-2. Oscillator Pinout

| Oscillator | Supply | Signal | I/O pin |

|------------|--------|--------|---------|

| XOSC       | VDDIO  | XIN    | PA14    |

|            |        | XOUT   | PA15    |

| XOSC32K    | VDDANA | XIN32  | PA00    |

|            |        | XOUT32 | PA01    |

To improve the cycle-to-cycle jitter of the XOSC32 oscillator, it is recommended to keep the neighboring pins of XIN32 and the following pins of XOUT32 as static as possible:

#### Table 4-3. XOSC32 Jitter Minimization

| Package Pin Count | Static Signal Recommended |

|-------------------|---------------------------|

| 32                | PA02, PA03                |

| 24                | PA02, PA03                |

## 4.3 Serial Wire Debug Interface Pinout

The SWCLK pin is by default assigned to the SWCLK peripheral function G to allow debugger probe detection.

A debugger probe detection (cold-plugging or hot-plugging) will automatically switch the SWDIO I/O pin to the SWDIO function, as long as the SWLCK peripheral function is selected.

## **PAC - Peripheral Access Controller**

- Bit 8 WDT Peripheral WDT Write Protection Status

- Bit 7 GCLK Peripheral GCLK Write Protection Status

- Bit 6 SUPC Peripheral SUPC Write Protection Status

- Bit 5 OSC32KCTRL Peripheral OSC32KCTRL Write Protection Status

- Bit 4 OSCCTRL Peripheral OSCCTRL Write Protection Status

- Bit 3 RSTC Peripheral RSTC Write Protection Status

- Bit 2 MCLK Peripheral MCLK Write Protection Status

- Bit 1 PM Peripheral PM Write Protection Status

- Bit 0 PAC Peripheral PAC Write Protection Status

#### 16.12.1 Control

| Name:     | CTRL                 |

|-----------|----------------------|

| Offset:   | 0x0000               |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3     | 2   | 1 | 0     |

|--------|---|---|---|---|-------|-----|---|-------|

|        |   |   |   |   | MBIST | CRC |   | SWRST |

| Access |   |   |   |   | W     | W   |   | W     |

| Reset  |   |   |   |   | 0     | 0   |   | 0     |

**Bit 3 – MBIST** Memory Built-In Self-Test Writing a '0' to this bit has no effect.

Writing a '1' to this bit starts the memory BIST algorithm.

**Bit 2 – CRC** 32-bit Cyclic Redundancy Check Writing a '0' to this bit has no effect.

Writing a '1' to this bit starts the cyclic redundancy check algorithm.

#### Bit 0 - SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets the module.

## SAM L10/L11 Family

## RTC – Real-Time Counter

| Value   | Name    | Description                 |

|---------|---------|-----------------------------|

| 0xB     | DIV1024 | CLK_RTC_CNT = GCLK_RTC/1024 |

| 0xC-0xF | -       | Reserved                    |

#### Bit 7 - MATCHCLR Clear on Match

This bit defines if the counter is cleared or not on a match.

This bit is not synchronized.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The counter is not cleared on a Compare/Alarm 0 match |

| 1     | The counter is cleared on a Compare/Alarm 0 match     |

#### Bits 3:2 - MODE[1:0] Operating Mode

This bit group defines the operating mode of the RTC.

This bit is not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT32 | Mode 0: 32-bit counter |

| 0x1   | COUNT16 | Mode 1: 16-bit counter |

| 0x2   | CLOCK   | Mode 2: Clock/calendar |

| 0x3   | -       | Reserved               |

#### Bit 1 - ENABLE Enable

Due to synchronization there is a delay between writing CTRLA.ENABLE and until the peripheral is enabled/disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                |

|-------|----------------------------|

| C     | The peripheral is disabled |

| 1     | The peripheral is enabled  |

#### Bit 0 - SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the RTC (except DBGCTRL) to their initial state, and the RTC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay between writing CTRLA.SWRST and until the reset is complete. CTRLA.SWRST will be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is not reset operation ongoing |

| 1     | The reset operation is ongoing       |

#### Bit 7 – DMAEN DMA Enable

The RTC can trigger a DMA request when the timestamp is ready in the TIMESTAMP register.

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | Tamper DMA request is disabled. Reading TIMESTAMP has no effect on<br>INTFLAG.TAMPER. |

| 1     | Tamper DMA request is enabled. Reading TIMESTAMP will clear INTFLAG.TAMPER.           |

#### Bit 6 – RTCOUT RTC Output Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The RTC active layer output is disabled. |

| 1     | The RTC active layer output is enabled.  |

#### Bit 5 – DEBASYNC Debouncer Asynchronous Enable

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | The tamper input debouncers operate synchronously.  |

| 1     | The tamper input debouncers operate asynchronously. |

#### Bit 4 – DEBMAJ Debouncer Majority Enable

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | The tamper input debouncers match three equal values.           |

| 1     | The tamper input debouncers match majority two of three values. |

#### Bit 0 - GP0EN General Purpose 0 Enable

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | COMP0 compare function enabled. GP0/GP1 disabled. |

| 1     | COMP0 compare function disabled. GP0/GP1 enabled. |

#### 27.10.12 Compare n Value in COUNT16 mode (CTRLA.MODE=1)

| Name:     | COMP                                     |

|-----------|------------------------------------------|

| Offset:   | 0x20 + n*0x02 [n=01]                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

|        |     |     |     | COMF | P[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        |     |     |     | COM  | P[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

#### Bits 15:0 - COMP[15:0] Compare Value

The 16-bit value of COMPn is continuously compared with the 16-bit COUNT value. When a match occurs, the Compare n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMPn) is set on the next counter cycle.

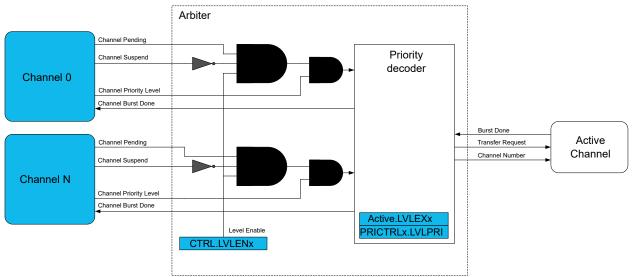

#### 28.6.2.4 Arbitration

If a DMA channel is enabled and not suspended when it receives a transfer trigger, it will send a transfer request to the arbiter. When the arbiter receives the transfer request it will include the DMA channel in the queue of channels having pending transfers, and the corresponding Pending Channel x bit in the Pending Channels registers (PENDCH.PENDCHx) will be set. Depending on the arbitration scheme, the arbiter will choose which DMA channel will be the next active channel. The active channel is the DMA channel being granted access to perform its next transfer. When the arbiter has granted a DMA channel access to the DMAC, the corresponding bit PENDCH.PENDCHx will be cleared. See also the following figure.

If the upcoming transfer is the first for the transfer request, the corresponding Busy Channel x bit in the Busy Channels register will be set (BUSYCH.BUSYCHx=1), and it will remain '1' for the subsequent granted transfers.

When the channel has performed its granted transfer(s) it will be either fed into the queue of channels with pending transfers, set to be waiting for a new transfer trigger, suspended, or disabled. This depends on the channel and block transfer configuration. If the DMA channel is fed into the queue of channels with pending transfers, the corresponding BUSYCH.BUSYCHx will remain '1'. If the DMA channel is set to wait for a new transfer trigger, suspended, or disabled, the corresponding BUSYCH.BUSYCHx will be cleared.

If a DMA channel is suspended while it has a pending transfer, it will be removed from the queue of pending channels, but the corresponding PENDCH.PENDCHx will remain set. When the same DMA channel is resumed, it will be added to the queue of pending channels again.

If a DMA channel gets disabled (CHCTRLA.ENABLE=0) while it has a pending transfer, it will be removed from the queue of pending channels, and the corresponding PENDCH.PENDCHx will be cleared.

#### Figure 28-4. Arbiter Overview

## Priority Levels

When a channel level is pending or the channel is transferring data, the corresponding Level Executing bit is set in the Active Channel and Levels register (ACTIVE.LVLEXx).

Each DMA channel supports a 4-level priority scheme. The priority level for a channel is configured by writing to the Channel Arbitration Level bit group in the Channel Control B register (CHCTRLB.LVL). As long as all priority levels are enabled, a channel with a higher priority level number will have priority over a channel with a lower priority level number. Each priority level x is enabled by setting the corresponding Priority Level x Enable bit in the Control register (CTRL.LVLENx=1).

#### 31.8.8 Permutation Write

Name:PERMWOffset:0x010Reset:0x00Property:PAC Write-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1         | 0 |

|--------|---|---|---|---|---|---|-----------|---|

|        |   |   |   |   |   |   | DATA[2:0] |   |

| Access |   |   |   |   |   | W | W         | W |

| Reset  |   |   |   |   |   | 0 | 0         | 0 |

|        |   |   |   |   |   |   |           |   |

**Bits 2:0 – DATA[2:0]** Permutation Write Data Data is the input value for the scrambler permutation function:

PERMR.DATA = Permutate(PERMW.DATA, DSCC.DSCKEY)

These bits will always return zero when read.

# SAM L10/L11 Family

## **PORT - I/O Pin Controller**

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | Input buffer for the I/O pin is disabled, and the input value will not be sampled.          |

| 1     | Input buffer for the I/O pin is enabled, and the input value will be sampled when required. |

#### Bit 0 – PMUXEN Peripheral Multiplexer Enable

This bit enables or disables the peripheral multiplexer selection set in the Peripheral Multiplexing register (PMUXn) to enable or disable alternative peripheral control over an I/O pin direction and output drive value.

Writing a zero to this bit allows the PORT to control the pad direction via the Data Direction register (DIR) and output drive value via the Data Output Value register (OUT). The peripheral multiplexer value in PMUXn is ignored. Writing '1' to this bit enables the peripheral selection in PMUXn to control the pad. In this configuration, the physical pin state may still be read from the Data Input Value register (IN) if PINCFGn.INEN is set.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The peripheral multiplexer selection is disabled, and the PORT registers control the direction |

|       | and output drive value.                                                                        |

| 1     | The peripheral multiplexer selection is enabled, and the selected peripheral function controls |

|       | the direction and output drive value.                                                          |

#### 33.7.8 Channel n Control

| Name:     | CHANNEL                          |

|-----------|----------------------------------|

| Offset:   | 0x20 + n*0x08 [n=07]             |

| Reset:    | 0x00008000                       |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding channel (CHANNELx) is set as Non-Secured in the NONSECCHAN register.

This register allows the user to configure channel n. To write to this register, do a single, 32-bit write of all the configuration data.

| Bit    | 31        | 30        | 29        | 28        | 27         | 26          | 25        | 24        |  |

|--------|-----------|-----------|-----------|-----------|------------|-------------|-----------|-----------|--|

|        |           |           |           |           |            |             |           |           |  |

| Access |           |           |           |           |            |             |           |           |  |

| Reset  |           |           |           |           |            |             |           |           |  |

|        |           |           |           |           |            |             |           |           |  |

| Bit    | 23        | 22        | 21        | 20        | 19         | 18          | 17        | 16        |  |

|        |           |           |           |           |            |             |           |           |  |

| Access |           |           |           |           |            |             |           |           |  |

| Reset  |           |           |           |           |            |             |           |           |  |

|        |           |           |           |           |            |             |           |           |  |

| Bit    | 15        | 14        | 13        | 12        | 11         | 10          | 9         | 8         |  |

|        | ONDEMAND  | RUNSTDBY  |           |           | EDGS       | EDGSEL[1:0] |           | PATH[1:0] |  |

| Access | RW/RW*/RW | RW/RW*/RW |           |           | RW/RW*/RW  | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW |  |

| Reset  | 1         | 0         |           |           | 0          | 0           | 0         | 0         |  |

|        |           |           |           |           |            |             |           |           |  |

| Bit    | 7         | 6         | 5         | 4         | 3          | 2           | 1         | 0         |  |

|        |           |           |           |           | EVGEN[5:0] |             |           |           |  |

| Access |           |           | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW  | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW |  |

| Reset  |           |           | 0         | 0         | 0          | 0           | 0         | 0         |  |

#### Bit 15 – ONDEMAND Generic Clock On Demand

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock |

|       | source is enabled.                                                                       |

| 1     | Generic clock is requested on demand while an event is handled                           |

#### Bit 14 – RUNSTDBY Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                      |

| 1     | The channel is not stopped in standby sleep mode and depends on the |

|       | CHANNEL.ONDEMAND bit.                                               |

## 34. SERCOM – Serial Communication Interface

## 34.1 Overview

There are up to three instances of the serial communication interface (SERCOM) peripheral.

A SERCOM can be configured to support a number of modes: I<sup>2</sup>C, SPI, and USART. When an instance of SERCOM is configured and enabled, all of the resources of that SERCOM instance will be dedicated to the selected mode.

The SERCOM serial engine consists of a transmitter and receiver, baud-rate generator and address matching functionality. It can use the internal generic clock or an external clock. Using an external clock allows the SERCOM to be operated in all Sleep modes.

#### **Related Links**

- 35. SERCOM USART SERCOM Synchronous and Asynchronous Receiver and Transmitter

- 36. SERCOM SPI SERCOM Serial Peripheral Interface

- 37. SERCOM I2C SERCOM Inter-Integrated Circuit

## 34.2 Features

- Interface for configuring into one of the following:

- Inter-Integrated Circuit (I<sup>2</sup>C) Two-wire Serial Interface

- System Management Bus (SMBus<sup>™</sup>) compatible

- Serial Peripheral Interface (SPI)

- Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

- Single transmit buffer and double receive buffer

- Baud-rate generator

- Address match/mask logic

- Operational in all Sleep modes with an external clock source

- Can be used with DMA

See the Related Links for full feature lists of the interface configurations.

#### **Related Links**

- 35. SERCOM USART SERCOM Synchronous and Asynchronous Receiver and Transmitter

- 36. SERCOM SPI SERCOM Serial Peripheral Interface

- 37. SERCOM I2C SERCOM Inter-Integrated Circuit

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

#### Bit 2 – BUFOVF Buffer Overflow

Reading this bit before reading the Data register will indicate the error status of the next character to be read.

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set when a buffer overflow condition is detected. A buffer overflow occurs when the receive buffer is full, there is a new character waiting in the receive shift register and a new start bit is detected.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

#### Bit 1 – FERR Frame Error

Reading this bit before reading the Data register will indicate the error status of the next character to be read.

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set if the received character had a frame error, i.e., when the first stop bit is zero.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

#### Bit 0 – PERR Parity Error

Reading this bit before reading the Data register will indicate the error status of the next character to be read.

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set if parity checking is enabled (CTRLA.FORM is 0x1, 0x5, or 0x7) and a parity error is detected.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

#### 37.8.5 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x18    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7     | 6 | 5 | 4 | 3 | 2    | 1      | 0    |

|--------|-------|---|---|---|---|------|--------|------|

|        | ERROR |   |   |   |   | DRDY | AMATCH | PREC |

| Access | R/W   |   |   |   |   | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   |   |   | 0    | 0      | 0    |

#### Bit 7 – ERROR Error

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. The corresponding bits in STATUS are SEXTTOUT, LOWTOUT, COLL, and BUSERR.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 2 – DRDY Data Ready

This flag is set when a I<sup>2</sup>C slave byte transmission is successfully completed.

The flag is cleared by hardware when either:

- Writing to the DATA register.

- Reading the DATA register with smart mode enabled.

- Writing a valid command to the CMD register.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Ready interrupt flag.

#### Bit 1 - AMATCH Address Match

This flag is set when the I<sup>2</sup>C slave address match logic detects that a valid address has been received.

The flag is cleared by hardware when CTRL.CMD is written.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Address Match interrupt flag. When cleared, an ACK/NACK will be sent according to CTRLB.ACKACT.

#### Bit 0 – PREC Stop Received

This flag is set when a stop condition is detected for a transaction being processed. A stop condition detected between a bus master and another slave will not set this flag, unless the PMBus Group Command is enabled in the Control B register (CTRLB.GCMD=1).

This flag is cleared by hardware after a command is issued on the next address match.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Stop Received interrupt flag.

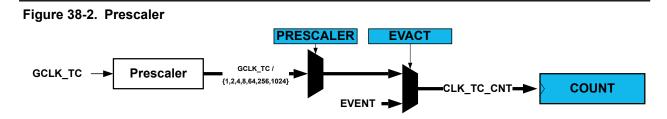

TC – Timer/Counter

#### 38.6.2.4 Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period Value and Period Buffer Value registers (PER and PERBUF).

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

- COUNT32: This mode is achieved by pairing two 16-bit TC peripherals. TCn is paired with TCn+1. TC2 does not support 32-bit resolution.

When paired, the TC peripherals are configured using the registers of the even-numbered TC. The odd-numbered partner will act as a slave, and the Slave bit in the Status register (STATUS.SLAVE) will be set. The register values of a slave will not reflect the registers of the 32-bit counter. Writing to any of the slave registers will not affect the 32-bit counter. Normal access to the slave COUNT and CCx registers is not allowed.

#### 38.6.2.5 Counter Operations

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TC clock input (CLK\_TC\_CNT). A counter clear or reload marks the end of the current counter cycle and the start of a new one.

The counting direction is set by the Direction bit in the Control B register (CTRLB.DIR). If this bit is zero the counter is counting up, and counting down if CTRLB.DIR=1. The counter will count up or down for each tick (clock or event) until it reaches TOP or ZERO. When it is counting up and TOP is reached, the counter will be set to zero at the next tick (overflow) and the Overflow Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF) will be set. When it is counting down, the counter is reloaded with the TOP value when ZERO is reached (underflow), and INTFLAG.OVF is set.

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e., a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. When starting the TC, the COUNT value will be either ZERO or TOP (depending on the counting direction set by CTRLBSET.DIR or CTRLBCLR.DIR), unless a different value has been written to it, or the TC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed when the counter is running. See also the following figure.

#### **Bits 3:2 – MODE[1:0]** Timer Counter Mode These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

#### 38.7.2.17 Channel x Compare Buffer Value, 16-bit Mode

| Name:     | CCBUFx               |

|-----------|----------------------|

| Offset:   | 0x30 + x*0x02 [x=01] |

| Reset:    | 0x0000               |

| Property: | Write-Synchronized   |

| Bit    | 15         | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|--------|------------|-----|-----|------|---------|-----|-----|-----|

|        |            |     |     | CCBU | F[15:8] |     |     |     |

| Access | R/W        | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |            |     |     |      |         |     |     |     |

| Bit    | 7          | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        | CCBUF[7:0] |     |     |      |         |     |     |     |

| Access | R/W        | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

Bits 15:0 – CCBUF[15:0] Channel x Compare Buffer Value

These bits hold the value of the Channel x Compare Buffer Value. When the buffer valid flag is '1' and double buffering is enabled (CTRLBCLR.LUPD=1), the data from buffer registers will be copied into the corresponding CCx register under UPDATE condition (CTRLBSET.CMD=0x3), including the software update command.

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 39.5.10 Analog Connections

Not applicable.

## **39.6 Functional Description**

#### **39.6.1** Principle of Operation

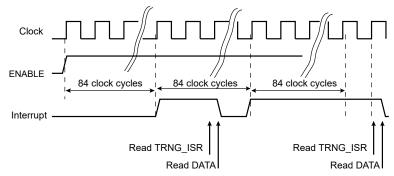

When the TRNG is enabled, the peripheral starts providing new 32-bit random numbers every 84 CLK\_TRNG\_APB clock cycles.

The TRNG can be configured to generate an interrupt or event when a new random number is available.

#### Figure 39-2. TRNG Data Generation Sequence

#### 39.6.2 Basic Operation

#### 39.6.2.1 Initialization

To operate the TRNG, do the following:

- Configure the clock source for CLK\_TRNG\_APB in the Main Clock Controller (MCLK) and enable the clock by writing a '1' to the TRNG bit in the APB Mask register of the MCLK.

- Optional: Enable the output event by writing a '1' to the EVCTRL.DATARDYEO bit.

- Optional: Enable the TRNG to Run in Standby sleep mode by writing a '1' to CTRLA.RUNSTDBY.

- Enable the TRNG operation by writing a '1' to CTRLA.ENABLE.

The following register is enable-protected, meaning that it can only be written when the TRNG is disabled (CTRLA.ENABLE is zero):

• Event Control register (EVCTRL)

Enable-protection is denoted by the Enable-Protected property in the register description.

### 39.6.2.2 Enabling, Disabling and Resetting

The TRNG is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TRNG is disabled by writing a zero to CTRLA.ENABLE.

#### 39.6.3 Interrupts

The TRNG has the following interrupt source:

Data Ready (DATARDY): Indicates that a new random number is available in the DATA register and ready to be read.

# SAM L10/L11 Family

## ADC – Analog-to-Digital Converter

| Result<br>Resolution | Number of<br>Samples to<br>Average | AVGCTRL.SAMPLENUM[3:0] | Number of<br>Automatic<br>Right Shifts | AVGCTRL.ADJRES[2:0] |

|----------------------|------------------------------------|------------------------|----------------------------------------|---------------------|

| 13 bits              | 4 <sup>1</sup> = 4                 | 0x2                    | 0                                      | 0x1                 |

| 14 bits              | 4 <sup>2</sup> = 16                | 0x4                    | 0                                      | 0x2                 |

| 15 bits              | 4 <sup>3</sup> = 64                | 0x6                    | 2                                      | 0x1                 |

| 16 bits              | 4 <sup>4</sup> = 256               | 0x8                    | 4                                      | 0x0                 |

#### Table 41-3. Configuration Required for Oversampling and Decimation

#### 41.6.2.12 Automatic Sequences

The ADC has the ability to automatically sequence a series of conversions. This means that each time the ADC receives a start-of-conversion request, it can perform multiple conversions automatically. All of the 32 positive inputs can be included in a sequence by writing to corresponding bits in the Sequence Control register (SEQCTRL). The order of the conversion in a sequence is the lower positive MUX selection to upper positive MUX (AIN0, AIN1, AIN2 ...). In differential mode, the negative inputs selected by MUXNEG field, will be used for the entire sequence.

When a sequence starts, the Sequence Busy status bit in Sequence Status register (SEQSTATUS.SEQBUSY) will be set. When the sequence is complete, the Sequence Busy status bit will be cleared.

Each time a conversion is completed, the Sequence State bit in Sequence Status register (SEQSTATUS.SEQSTATE) will store the input number from which the conversion is done. The result will be stored in the RESULT register, and the Result Ready Interrupt Flag (INTFLAG.RESRDY) is set.

If additional inputs must be scanned, the ADC will automatically start a new conversion on the next input present in the sequence list.

Note that if SEQCTRL register has no bits set to '1', the conversion is done with the selected MUXPOS input.

#### 41.6.2.13 Window Monitor

The window monitor feature allows the conversion result in the RESULT register to be compared to predefined threshold values. The window mode is selected by setting the Window Monitor Mode bits in the Control C register (CTRLC.WINMODE). Threshold values must be written in the Window Monitor Lower Threshold register (WINLT) and Window Monitor Upper Threshold register (WINUT).

If differential input is selected, the WINLT and WINUT are evaluated as signed values. Otherwise they are evaluated as unsigned values. The significant WINLT and WINUT bits are given by the precision selected in the Conversion Result Resolution bit group in the Control C register (CTRLC.RESSEL). This means that for example in 8-bit mode, only the eight lower bits will be considered. In addition, in differential mode, the eighth bit will be considered as the sign bit, even if the ninth bit is zero.

The INTFLAG.WINMON interrupt flag will be set if the conversion result matches the window monitor condition.

#### 41.6.2.14 Offset and Gain Correction

Inherent gain and offset errors affect the absolute accuracy of the ADC.

The offset error is defined as the deviation of the actual ADC transfer function from an ideal straight line at zero input voltage. The offset error cancellation is handled by the Offset Correction register

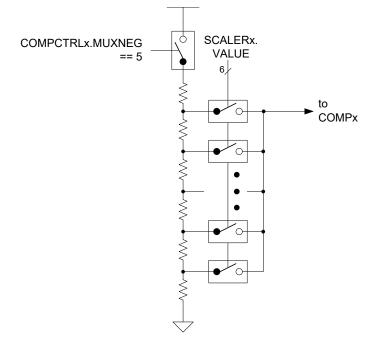

#### Figure 42-5. VDD Scaler

#### 42.6.6 Input Hysteresis

Application software can selectively enable/disable hysteresis for the comparison. Applying hysteresis will help prevent constant toggling of the output, which can be caused by noise when the input signals are close to each other.

Hysteresis is enabled for each comparator individually by the Hysteresis Enable bit in the Comparator x Control register (COMPCTRLx.HYSTEN). Furthermore, when enabled, the level of hysteresis is programmable through the Hysteresis Level bits also in the Comparator x Control register (COMPCTRLx.HYST). Hysteresis is available only in continuous mode (COMPCTRLx.SINGLE=0).

#### 42.6.7 Propagation Delay vs. Power Consumption

It is possible to trade off comparison speed for power efficiency to get the shortest possible propagation delay or the lowest power consumption. The speed setting is configured for each comparator individually by the Speed bit group in the Comparator x Control register (COMPCTRLx.SPEED). The Speed bits select the amount of bias current provided to the comparator, and as such will also affect the start-up time.

#### 42.6.8 Filtering

The output of the comparators can be filtered digitally to reduce noise. The filtering is determined by the Filter Length bits in the Comparator Control x register (COMPCTRLx.FLEN), and is independent for each comparator. Filtering is selectable from none, 3-bit majority (N=3) or 5-bit majority (N=5) functions. Any change in the comparator output is considered valid only if N/2+1 out of the last N samples agree. The filter sampling rate is the GCLK\_AC frequency.

Note that filtering creates an additional delay of N-1 sampling cycles from when a comparison is started until the comparator output is validated. For continuous mode, the first valid output will occur when the required number of filter samples is taken. Subsequent outputs will be generated every cycle based on the current sample plus the previous N-1 samples, as shown in Figure 42-6. For single-shot mode, the comparison completes after the Nth filter sample, as shown in Figure 42-7.

© 2018 Microchip Technology Inc.

# SAM L10/L11 Family

## **Electrical Characteristics**

| Mode | Conditions | Regulator Mode | Vcc  | Та   | Тур.  | Max.   | Units |

|------|------------|----------------|------|------|-------|--------|-------|

| OFF  |            |                | 1.8V | 25°C | 34.6  | 54.4   | nA    |

|      |            |                |      | 85°C | 595.7 | 1197.3 |       |

|      |            |                | 3.3V | 25°C | 61.2  | 89.1   |       |

|      |            |                |      | 85°C | 796.1 | 1622.8 |       |

## 46.8 Wake-Up Time

Conditions:

- VDDIO/VDDANA = 3.3V

- LDO Regulation mode

- CPU clock = OSC16M @ 4 MHz

- One Wait-state

- Cache enabled

- Flash Fast Wake-up enabled (NVMCTRL.CTRLB.FWUP = 1)

- Flash in WAKEUPINSTANT mode (NVMCTRL.CTRLB.SLEEPPRM = 1)

Measurement Method:

For Idle and Standby, the CPU sets an I/O by writing PORT->IOBUS without jumping in an interrupt handler (Cortex M23 register PRIMASK = 1). The wake-up time is measured between the edge of the wake-up input signal and the edge of the GPIO pin.

For Off mode, the exit of the mode is done through the reset pin, the time is measured between the falling edge of the RESETN signal (with the minimum reset pulse length), and the set of the I/O which is done by the first executed instructions after Reset.

| Sleep Mode | Condition                                                                            | Тур                      | Unit |    |  |

|------------|--------------------------------------------------------------------------------------|--------------------------|------|----|--|

| Idle       | PL2 or PL0                                                                           | or PL0                   |      |    |  |

| Standby    | PL0                                                                                  | PDSW domain in retention | 5.3  |    |  |

|            |                                                                                      | PDSW domain in active    | 2.6  |    |  |

|            | PL2                                                                                  | PDSW domain in retention | 76   |    |  |

|            | Voltage scaling at default values:<br>SUPC >VREG.VSVSTEP=0<br>SUPC > VREG.VSPER=0    | PDSW domain in active    | 75   |    |  |

|            | PL2                                                                                  | PDSW domain in retention | 16   |    |  |

|            | Voltage scaling at fastest setting:<br>SUPC > VREG.VSVSTEP=15<br>SUPC > VREG.VSPER=0 | PDSW domain in active    | 15   |    |  |

| OFF        | L10 with BOOTOPT=0                                                                   |                          | 3.2  | ms |  |