#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d14a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PAC - Peripheral Access Controller**

- Bit 8 WDT Peripheral WDT Write Protection Status

- Bit 7 GCLK Peripheral GCLK Write Protection Status

- Bit 6 SUPC Peripheral SUPC Write Protection Status

- Bit 5 OSC32KCTRL Peripheral OSC32KCTRL Write Protection Status

- Bit 4 OSCCTRL Peripheral OSCCTRL Write Protection Status

- Bit 3 RSTC Peripheral RSTC Write Protection Status

- Bit 2 MCLK Peripheral MCLK Write Protection Status

- Bit 1 PM Peripheral PM Write Protection Status

- Bit 0 PAC Peripheral PAC Write Protection Status

# DSU - Device Service Unit

|        | Name:<br>Offset:<br>Reset:<br>Property: | MEMTYPE<br>0x1FCC<br>0x0000000x<br>- |    |    |    |    |    |       |

|--------|-----------------------------------------|--------------------------------------|----|----|----|----|----|-------|

| Bit    | 31                                      | 30                                   | 29 | 28 | 27 | 26 | 25 | 24    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

|        |                                         |                                      |    |    |    |    |    |       |

| Bit    | 23                                      | 22                                   | 21 | 20 | 19 | 18 | 17 | 16    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| D.4    | 45                                      |                                      | 10 | 10 | 44 | 10 | 0  | 0     |

| Bit    | 15                                      | 14                                   | 13 | 12 | 11 | 10 | 9  | 8     |

| A      |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| Bit    | 7                                       | 6                                    | 5  | 4  | 3  | 2  | 1  | 0     |

|        |                                         |                                      |    |    |    |    |    | SMEMP |

| Access |                                         |                                      |    |    |    |    |    | R     |

| Reset  |                                         |                                      |    |    |    |    |    | x     |

|        |                                         |                                      |    |    |    |    |    |       |

#### 16.12.16 CoreSight ROM Table Memory Type

#### Bit 0 - SMEMP System Memory Present

This bit indicates whether system memory is present on the bus that connects to the ROM table.

This bit is set at power-up if the device is not protected, indicating that the system memory is accessible from a debug adapter.

This bit is cleared at power-up if the device is protected, indicating that the system memory is not accessible from a debug adapter.

# **GCLK - Generic Clock Controller**

| Value     | Name      | Description                      |

|-----------|-----------|----------------------------------|

| 0x00      | XOSC      | XOSC oscillator output           |

| 0x01      | GCLK_IN   | Generator input pad (GCLK_IO)    |

| 0x02      | GCLK_GEN1 | Generic clock generator 1 output |

| 0x03      | OSCULP32K | OSCULP32K oscillator output      |

| 0x04      | XOSC32K   | XOSC32K oscillator output        |

| 0x05      | OSC16M    | OSC16M oscillator output         |

| 0x06      | DFLLULP   | DFLLULP ultra low power output   |

| 0x07      | FDPLL96M  | FDPLL96M output                  |

| 0x08-0x1F | Reserved  | Reserved for future use          |

#### Table 18-4. Generator Clock Source Selection

A Power Reset will reset all GENCTRLn registers. the Reset values of the GENCTRLn registers are shown in table below.

#### Table 18-5. GENCTRLn Reset Value after a Power Reset

| GCLK Generator | Reset Value after a Power Reset |

|----------------|---------------------------------|

| 0              | 0x0000105                       |

| others         | 0x0000000                       |

A User Reset will reset the associated GENCTRL register unless the Generator is the source of a locked Peripheral Channel (PCHCTRLm.WRTLOCK=1). The reset values of the GENCTRL register are as shown in the table below.

### Table 18-6. GENCTRLn Reset Value after a User Reset

| GCLK Generator | Reset Value after a User Reset                                                                       |

|----------------|------------------------------------------------------------------------------------------------------|

| 0              | 0x0000105                                                                                            |

| others         | No change if the generator is used by a Peripheral Channel m with PCHCTRLm.WRTLOCK=1 else 0x00000000 |

Related Links 18.8.4 PCHCTRLm

© 2018 Microchip Technology Inc.

### **19.7 Register Summary**

| Offset   | Name      | Bit Pos. |         |          |                |           |          |          |          |          |

|----------|-----------|----------|---------|----------|----------------|-----------|----------|----------|----------|----------|

| 0x00     | CTRLA     | 7:0      |         |          |                |           |          | CKSEL    |          |          |

| 0x01     | INTENCLR  | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x02     | INTENSET  | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x03     | INTFLAG   | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x04     | Reserved  |          |         |          |                |           |          |          |          |          |

| 0x05     | CPUDIV    | 7:0      |         |          |                | CPUD      | IV[7:0]  | 1        |          |          |

| 0x06     |           |          |         |          |                |           |          |          |          |          |

| <br>0x0F | Reserved  |          |         |          |                |           |          |          |          |          |

|          |           | 7:0      | NVMCTRL | PAC      | Reserved       | DSU       | DMAC     | APBC     | APBB     | APBA     |

| 0x10     | AHBMASK   | 15:8     |         |          |                | TRAM      | Reserved | Reserved | Reserved | Reserved |

| 0.00     | ANDWASK   | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          |           | 7:0      | GCLK    | SUPC     | OSC32KCTR<br>L | OSCCTRL   | RSTC     | MCLK     | PM       | PAC      |

| 0x14     | APBAMASK  | 15:8     |         | Reserved | AC             | PORT      | FREQM    | EIC      | RTC      | WDT      |

|          |           | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          |           | 7:0      |         |          |                | HMATRIXHS |          | NVMCTRL  | DSU      | IDAU     |

| 0x18     | APBBMASK  | 15:8     |         |          |                |           |          |          |          |          |

| 0,10     | AI DEMAOR | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          |           | 7:0      | ADC     | TC2      | TC1            | TC0       | SERCOM2  | SERCOM1  | SERCOM0  | EVSYS    |

| 0x1C     | APBCMASK  | 15:8     |         |          |                | OPAMP     | CCL      | TRNG     | PTC      | DAC      |

|          |           | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

### 19.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers can be write-protected optionally by the Peripheral Access Controller (PAC). This is denoted by the property "PAC Write-Protection" in each individual register description. Refer to the 19.5.8 Register Access Protection for details.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

The DMAC is configured to operate in standby sleep mode by using its respective RUNSTDBY bit. A DMAC channel is configured to set the DMA destination. The Run in Standby bit of this DMAC channel is written to '1' to allow it running in Standby Sleep mode.

*Entering Standby mode*: The Power Manager peripheral sets PDSW to retention state. The VDDCORE is supplied by the low-power regulator.

*Dynamic SleepWalking*: based on RTC conditions, an RTC output signal (DMA request for timestamp) triggers DMAC to put timestamp value at configured DMA destination.

This event is detected by the Power Manager which sets the PDSW power domain to active state and starts the main voltage regulator.

This DMA transfer request is detected by the PM, which sets PDSW (containing the DMAC) to active state. The DMAC requests the CLK\_DMAC\_AHB clock and transfer the timestamp value to the memory. When the DMA beat transfer is completed, the CLK\_DMAC\_AHB clock is stopped again.

The low-power regulator starts again and the PDSW power domain is set back to retention state by the PM. Note that during this dynamic SleepWalking period, the CPU is still sleeping.

*Exiting Standby mode*: during SleepWalking with Dynamic Power Gating sequence, if conditions are met, the DMAC generates an interrupt to wake up the device.

#### Related Links

27. RTC – Real-Time Counter

33. EVSYS - Event System

#### 22.6.7 DMA Operation

Not applicable.

#### 22.6.8 Interrupts

The peripheral has the following interrupt sources:

Performance Level Ready (PLRDY)

This interrupt is a synchronous wake-up source. See Table 22-1 for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the peripheral is reset.

An interrupt flag is cleared by writing a '1' to the corresponding bit in the INTFLAG register. Each peripheral can have one interrupt request line per interrupt source or one common interrupt request line for all the interrupt sources. Refer to the Nested Vector Interrupt Controller (NVIC) for details. If the peripheral has one common interrupt request line for all the interrupt sources, the user must read the INTFLAG register to determine which interrupt condition is present.

#### 22.6.9 Events

Not applicable.

# SAM L10/L11 Family OSC32KCTRL – 32KHz Oscillators Controller

#### Name: OSCULP32K Offset: 0x1C Reset: 0x0000XX06 Property: **PAC Write-Protection** Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset 15 Bit 14 13 12 11 10 9 8 WRTLOCK CALIB[4:0] R/W R/W R/W R/W R/W R/W Access 0 Reset х х х х х Bit 7 6 5 4 3 2 0 1 ULP32KSW R/W Access 0 Reset

#### 24.8.9 32KHz Ultra Low-Power Internal Oscillator (OSCULP32K) Control

#### Bit 15 – WRTLOCK Write Lock

This bit locks the OSCULP32K register for future writes to fix the OSCULP32K configuration.

| Val | lue | Description                                |

|-----|-----|--------------------------------------------|

| 0   |     | The OSCULP32K configuration is not locked. |

| 1   |     | The OSCULP32K configuration is locked.     |

#### Bits 12:8 - CALIB[4:0] Oscillator Calibration

These bits control the oscillator calibration.

These bits are loaded from Flash Calibration at startup.

#### Bit 5 – ULP32KSW OSCULP32K Clock Switch Enable

| Value | е | Description                                                      |

|-------|---|------------------------------------------------------------------|

| 0     |   | OSCULP32K is not switched and provided by the ULP32K oscillator. |

| 1     |   | OSCULP32K is switched to be provided by the XOSC32K oscillator.  |

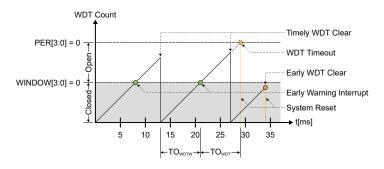

disabled again by writing a '1' to the Early Warning Interrupt bit in the Interrupt Enable Clear (INTENCLR.EW) register.

If the Early Warning interrupt is enabled in Window mode, the interrupt is generated at the start of the open window period, i.e. after TO<sub>WDTW</sub>. The Window mode operation is illustrated in figure Window-Mode Operation.

#### Figure 26-3. Window-Mode Operation

#### 26.6.3 DMA Operation

Not applicable.

#### 26.6.4 Interrupts

The WDT has the following interrupt source:

- Early Warning (EW): Indicates that the counter is approaching the time-out condition.

- This interrupt is an asynchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the WDT is reset. See the 26.8.6 INTFLAG register description for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

22. PM – Power Manager22.6.3.3 Sleep Mode Controller

#### 26.6.5 Events

Not applicable.

#### Normal Transfer

The event input is used to trigger a beat or burst transfer on peripherals.

The event is acknowledged as soon as the event is received. When received, both the Channel Pending status bit in the Channel Status register (CHSTATUS.PEND) and the corresponding Channel n bit in the Pending Channels register (28.8.13 PENDCH.PENDCHn) are set. If the event is received while the channel is pending, the event trigger is lost.

The figure below shows an example where beat transfers are enabled by internal events.

| Figure 28-11. | Beat Event | <b>Trigger Action</b> |

|---------------|------------|-----------------------|

|---------------|------------|-----------------------|

| CHENn              |                                                                           | \        |

|--------------------|---------------------------------------------------------------------------|----------|

| Peripheral Trigger | Trigger Lost                                                              |          |

| Event              |                                                                           |          |

| PENDCHn            |                                                                           |          |

| BUSYCHn            |                                                                           | <u> </u> |

| Data Transfer      | Block Transfer     Block Transfer       BEAT     BEAT       BEAT     BEAT |          |

#### **Conditional Transfer on Strobe**

The event input is used to trigger a transfer on peripherals with pending transfer requests. This event action is intended to be used with peripheral triggers, e.g. for timed communication protocols or periodic transfers between peripherals: only when the peripheral trigger coincides with the occurrence of a (possibly cyclic) event the transfer is issued.

The event is acknowledged as soon as the event is received. The peripheral trigger request is stored internally when the previous trigger action is completed (i.e. the channel is not pending) and when an active event is received. If the peripheral trigger is active, the DMA will wait for an event before the peripheral trigger is internally registered. When both event and peripheral trigger are active, both CHSTATUS.PEND and 28.8.13 PENDCH.PENDCHn are set. A software trigger will now trigger a transfer.

The figure below shows an example where the peripheral beat transfer is started by a conditional strobe event action.

#### 28.8.19 Channel Control B

Name:CHCTRLBOffset:0x44 [ID-00001ece]Reset:0x0000000Property:PAC Write-Protection, Enable-Protected

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Bit    | 31    | 30      | 29    | 28   | 27                   | 26           | 25  | 24     |

|--------|-------|---------|-------|------|----------------------|--------------|-----|--------|

|        |       |         |       |      |                      |              | CME | 0[1:0] |

| Access |       |         |       |      |                      |              | R/W | R/W    |

| Reset  |       |         |       |      |                      |              | 0   | 0      |

|        |       |         |       |      |                      |              |     |        |

| Bit    | 23    | 22      | 21    | 20   | 19                   | 18           | 17  | 16     |

|        | TRIGA | CT[1:0] |       |      |                      |              |     |        |

| Access | R/W   | R/W     |       |      |                      |              |     |        |

| Reset  | 0     | 0       |       |      |                      |              |     |        |

|        |       |         |       |      |                      |              |     |        |

| Bit    | 15    | 14      | 13    | 12   | 11                   | 10           | 9   | 8      |

|        |       |         |       |      |                      | TRIGSRC[4:0] |     |        |

| Access |       |         |       | R/W  | R/W                  | R/W          | R/W | R/W    |

| Reset  |       |         |       | 0    | 0                    | 0            | 0   | 0      |

|        |       |         |       |      |                      |              |     |        |

| Bit    | 7     | 6       | 5     | 4    | 3                    | 2            | 1   | 0      |

|        |       | LVL     | [1:0] | EVOE | EVOE EVIE EVACT[2:0] |              |     |        |

| Access |       | R/W     | R/W   | R/W  | R/W                  | R/W          | R/W | R/W    |

| Reset  |       | 0       | 0     | 0    | 0                    | 0            | 0   | 0      |

#### Bits 25:24 - CMD[1:0] Software Command

These bits define the software commands. Refer to 28.6.3.2 Channel Suspend and 28.6.3.3 Channel Resume and Next Suspend Skip.

These bits are not enable-protected.

| CMD[1:0] | Name    | Description               |

|----------|---------|---------------------------|

| 0x0      | NOACT   | No action                 |

| 0x1      | SUSPEND | Channel suspend operation |

| 0x2      | RESUME  | Channel resume operation  |

| 0x3      | -       | Reserved                  |

#### Bits 23:22 - TRIGACT[1:0] Trigger Action

These bits define the trigger action used for a transfer.

| TRIGACT[1:0] | Name  | Description                                  |

|--------------|-------|----------------------------------------------|

| 0x0          | BLOCK | One trigger required for each block transfer |

| 0x1          | -     | Reserved                                     |

system frequencies, a programmable number of wait states can be used to optimize performance. When changing the AHB bus frequency, the user must ensure that the NVM Controller is configured with the proper number of wait states. Refer to the Electrical Characteristics for the exact number of wait states to be used for a particular frequency range.

#### 30.5.3 Interrupts

The NVM Controller interrupt request line is connected to the interrupt controller. Using the NVMCTRL interrupt requires the interrupt controller to be programmed first.

#### 30.5.4 Events

The NVMCTRL can take the following actions on an input event:

- Write zeroes in one Data FLASH row: Refer to 30.6.7 Tamper Erase for details.

- Write a page in the FLASH or in the Data FLASH: Refer to 30.6.6 Event Automatic Write for details.

The NVMCTRL uses only asynchronous events, so the asynchronous Event System channel path must be configured. By default, the NVMCTRL will detect a rising edge on the incoming event. If the NVMCTRL action must be performed on the falling edge of the incoming event, the event line must be inverted first. This is done by setting the corresponding Event Invert Enable bit in Event Control register (NVMCTRL.AUTOWINV=1).

#### 30.5.5 Debug Operation

When an external debugger forces the CPU into debug mode, the peripheral continues normal operation except that FLASH reads are not cached so that the cache state is not altered by debug tools.

#### 30.5.6 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Status register (STATUS)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

When TrustZone is supported (**SAM L11** only), all register reads are allowed. Non-secure writes to APB registers are limited as follows. Illegal writes will be ignored.

- Some commands written to CTRLA such as Write/Erase and Lock/Unlock are only permitted to non-secure application and data space.

- Writes to all other registers except CTRLC and INTFLAG are not allowed.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 30.5.7 SAM L11 TrustZone Specific Register Access Protection

The NVMCTRL is a split-secure APB module, all registers are available in the secure alias and only a subset of registers is available in the non-secure alias with limited access.

When NONSEC.WRITE is read zero, all APB write accesses to the non-secure APB alias and all nonsecure AHB write accesses to the Page Buffer are discarded. The latter returns a hardfault. Any attempt to change the configuration via the non-secure alias is silently ignored.

#### • No synchronization

When executing an operation that requires synchronization, the corresponding status bit in the Synchronization Busy register (SYNCBUSY.xxx) will be set immediately, and cleared when synchronization is complete.

If an operation that requires synchronization is executed while SYNCBUSY.xxx is one, the operation is discarded and an error is generated. The following bits need synchronization when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

#### 31.8.7 Data Scramble Control

| Name:     | DSCC                                  |

|-----------|---------------------------------------|

| Offset:   | 0x00C                                 |

| Reset:    | 0x0000000                             |

| Property: | PAC Write-Protected, Enable-Protected |

| W<br>0       |  |  |  |  |  |  |  |

|--------------|--|--|--|--|--|--|--|

|              |  |  |  |  |  |  |  |

| 0            |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

| 16           |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

| W            |  |  |  |  |  |  |  |

| 0            |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

| 8            |  |  |  |  |  |  |  |

| DSCKEY[15:8] |  |  |  |  |  |  |  |

| W            |  |  |  |  |  |  |  |

| 0            |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

| 0            |  |  |  |  |  |  |  |

|              |  |  |  |  |  |  |  |

| W            |  |  |  |  |  |  |  |

| 0            |  |  |  |  |  |  |  |

| -            |  |  |  |  |  |  |  |

#### Bit 31 – DSCEN Data Scramble Enable

| Value | Description                |

|-------|----------------------------|

| 0     | TrustRAM is not scrambled. |

| 1     | TrustRAM is scrambled.     |

#### Bits 29:0 – DSCKEY[29:0] Data Scramble Key

The key value used for data scrambling. Any value written to this field is XOR'ed with the previous data. Writing '1' to CTRLA.SWRST will reset this field to 0. These bits will always return zero when read.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 34.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 34.5.10 Analog Connections

Not applicable.

#### 34.6 Functional Description

#### 34.6.1 Principle of Operation

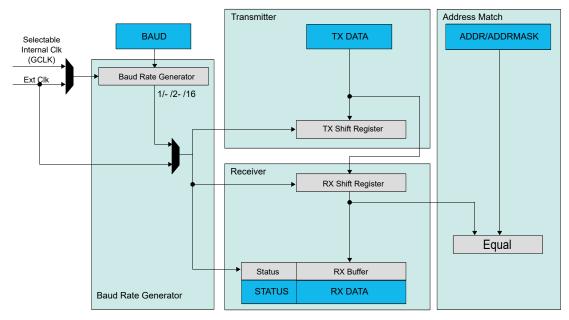

The basic structure of the SERCOM serial engine is shown in Figure 34-2. Labels in capital letters are synchronous to the system clock and accessible by the CPU; labels in lowercase letters can be configured to run on the GCLK\_SERCOMx\_CORE clock or an external clock.

#### Figure 34-2. SERCOM Serial Engine

The transmitter consists of a single write buffer and a shift register.

# SAM L10/L11 Family

SERCOM USART - SERCOM Synchronous and Asyn...

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

#### Bit 0 – SWRST Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

|   | Value | Description                        |

|---|-------|------------------------------------|

| [ | 0     | SWRST synchronization is not busy. |

|   | 1     | SWRST synchronization is busy.     |

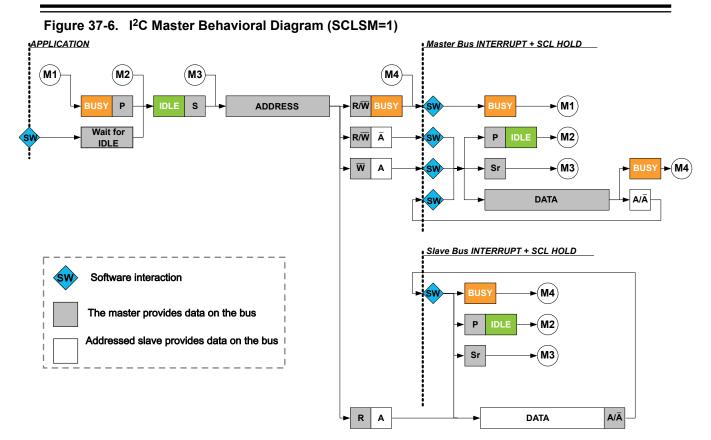

# SAM L10/L11 Family SERCOM I2C – SERCOM Inter-Integrated Circ...

#### 37.6.2.4.1 Master Clock Generation

The SERCOM peripheral supports several I<sup>2</sup>C bidirectional modes:

- Standard mode (*Sm*) up to 100 kHz

- Fast mode (*Fm*) up to 400 kHz

- Fast mode Plus (*Fm*+) up to 1 MHz

- High-speed mode (Hs) up to 3.4 MHz

The Master clock configuration for *Sm*, *Fm*, and *Fm*+ are described in Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus). For *Hs*, refer to Master Clock Generation (High-Speed Mode).

#### Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus)

In I<sup>2</sup>C *Sm, Fm*, and *Fm*+ mode, the Master clock (SCL) frequency is determined as described in this section:

The low (T<sub>LOW</sub>) and high (T<sub>HIGH</sub>) times are determined by the Baud Rate register (BAUD), while the rise (T<sub>RISE</sub>) and fall (T<sub>FALL</sub>) times are determined by the bus topology. Because of the wired-AND logic of the bus, T<sub>FALL</sub> will be considered as part of T<sub>LOW</sub>. Likewise, T<sub>RISE</sub> will be in a state between T<sub>LOW</sub> and T<sub>HIGH</sub> until a high state has been detected.

#### 38.7.1.6 Interrupt Enable Set

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

| [      |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

**Bit 4 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will set the corresponding Match or Capture Channel x Interrupt Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### Bit 0 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Valu | ue | Description                         |

|------|----|-------------------------------------|

| 0    |    | The Overflow interrupt is disabled. |

| 1    |    | The Overflow interrupt is enabled.  |

#### 38.7.3.4 Event Control

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x06                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15 | 14 | 13    | 12    | 11 | 10  | 9          | 8     |

|--------|----|----|-------|-------|----|-----|------------|-------|

|        |    |    | MCEOx | MCEOx |    |     |            | OVFEO |

| Access |    |    | R/W   | R/W   |    |     |            | R/W   |

| Reset  |    |    | 0     | 0     |    |     |            | 0     |

|        |    |    |       |       |    |     |            |       |

| Bit    | 7  | 6  | 5     | 4     | 3  | 2   | 1          | 0     |

|        |    |    | TCEI  | TCINV |    |     | EVACT[2:0] |       |

| Access |    |    | R/W   | R/W   |    | R/W | R/W        | R/W   |

| Reset  |    |    | 0     | 0     |    | 0   | 0          | 0     |

**Bits 13,12 – MCEOx** Match or Capture Channel x Event Output Enable [x = 1..0] These bits enable the generation of an event for every match or capture on channel x.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Match/Capture event on channel x is disabled and will not be generated.              |

| 1     | Match/Capture event on channel x is enabled and will be generated for every compare/ |

|       | capture.                                                                             |

#### Bit 8 - OVFEO Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

#### Bit 5 - TCEI TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

#### Bit 4 – TCINV TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |  |  |  |

|-------|-------------------------------------|--|--|--|

| 0     | Input event source is not inverted. |  |  |  |

| 1     | Input event source is inverted.     |  |  |  |

#### Bits 2:0 – EVACT[2:0] Event Action

These bits define the event action the TC will perform on an event.

# SAM L10/L11 Family

# ADC – Analog-to-Digital Converter

| Value | Description                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------|

| 0     | The ADC run in single conversion mode.                                                                       |

| 1     | The ADC is in free running mode and a new conversion will be initiated when a previous conversion completes. |

#### Bit 1 – LEFTADJ Left-Adjusted Result

| Value                                                                                 | Description                                                                                   |  |  |  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 0 The ADC conversion result is right-adjusted in the RESULT register.                 |                                                                                               |  |  |  |  |

| 1 The ADC conversion result is left-adjusted in the RESULT register. The high byte of |                                                                                               |  |  |  |  |

|                                                                                       | bit result will be present in the upper part of the result register. Writing this bit to zero |  |  |  |  |

|                                                                                       | (default) will right-adjust the value in the RESULT register.                                 |  |  |  |  |

#### Bit 0 – DIFFMODE Differential Mode

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The ADC is running in singled-ended mode.                                                 |

| 1     | The ADC is running in differential mode. In this mode, the voltage difference between the |

|       | MUXPOS and MUXNEG inputs will be converted by the ADC.                                    |

The AC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the AC will be reset to their initial state, and the AC will be disabled. Refer to *CTRLA* for details.

#### 42.6.2.3 Comparator Configuration

Each individual comparator must be configured by its respective Comparator Control register (COMPCTRLx) before that comparator is enabled. These settings cannot be changed while the comparator is enabled.

- Select the desired measurement mode with COMPCTRLx.SINGLE. See Starting a Comparison for more details.

- Select the desired hysteresis with COMPCTRLx.HYSTEN and COMPCTRLx.HYST. See Input Hysteresis for more details.

- Select the comparator speed versus power with COMPCTRLx.SPEED. See Propagation Delay vs. Power Consumption for more details.

- Select the interrupt source with COMPCTRLx.INTSEL.

- Select the positive and negative input sources with the COMPCTRLx.MUXPOS and COMPCTRLx.MUXNEG bits. See Selecting Comparator Inputs for more details.

- Select the filtering option with COMPCTRLx.FLEN.

- Select standby operation with Run in Standby bit (COMPCTRLx.RUNSTDBY).

The individual comparators are enabled by writing a '1' to the Enable bit in the Comparator x Control registers (COMPCTRLx.ENABLE). The individual comparators are disabled by writing a '0' to COMPCTRLx.ENABLE. Writing a '0' to CTRLA.ENABLE will also disable all the comparators, but will not clear their COMPCTRLx.ENABLE bits.

#### 42.6.2.4 Starting a Comparison

Each comparator channel can be in one of two different measurement modes, determined by the Single bit in the Comparator x Control register (COMPCTRLx.SINGLE):

- Continuous measurement

- Single-shot

After being enabled, a start-up delay is required before the result of the comparison is ready. This start-up time is measured automatically to account for environmental changes, such as temperature or voltage supply level, and is specified in the *Electrical Characteristics* chapters. During the start-up time, the COMP output is not available.

The comparator can be configured to generate interrupts when the output toggles, when the output changes from '0' to '1' (rising edge), when the output changes from '1' to '0' (falling edge) or at the end of the comparison. An end-of-comparison interrupt can be used with the Single-Shot mode to chain further events in the system, regardless of the state of the comparator outputs. The Interrupt mode is set by the Interrupt Selection bit group in the Comparator Control register (COMPCTRLx.INTSEL). Events are generated using the comparator output state, regardless of whether the interrupt is enabled or not.

#### 42.6.2.4.1 Continuous Measurement

Continuous measurement is selected by writing COMPCTRLx.SINGLE to zero. In continuous mode, the comparator is continuously enabled and performing comparisons. This ensures that the result of the latest comparison is always available in the Current State bit in the Status A register (STATUSA.STATEx).

After the start-up time has passed, a comparison is done and STATUSA is updated. The Comparator x Ready bit in the Status B register (STATUSB.READYx) is set, and the appropriate peripheral events and

# SAM L10/L11 Family

# **Electrical Characteristics**

| Symbol | Parameters | Drift<br>Calibration | PTC<br>scan rate<br>(msec) | Oversamples | Та | Тур. | Max. | Units |

|--------|------------|----------------------|----------------------------|-------------|----|------|------|-------|

|        |            |                      | 100                        | 4           |    | 1.7  | 43.2 |       |

|        |            |                      |                            | 16          |    | 2.4  | 43.9 |       |

|        |            |                      | 200                        | 4           |    | 1.4  | 42.8 |       |

|        |            |                      |                            | 16          |    | 1.8  | 43.2 |       |

|        |            |                      | 10                         | 4           |    | 8.3  | 51.7 |       |

|        |            | Enabled              |                            | 16          |    | 14.2 | 60.5 |       |

|        |            |                      | 50                         | 4           |    | 3.0  | 44.8 |       |

|        |            |                      |                            | 16          |    | 4.8  | 47.0 |       |

|        |            | Enabled              | 100                        | 4           |    | 2.3  | 44.5 |       |

|        |            |                      |                            | 16          |    | 2.8  | 45.4 |       |

|        |            |                      | 200                        | 4           |    | 1.9  | 43.9 |       |

|        |            |                      |                            | 16          |    | 2.4  | 44.2 |       |

#### Note:

1. These are based on characterization.

### 46.12 NVM Characteristics

### Table 46-39. NVM Max Speed Characteristics <sup>(1)</sup>

|                           | Conditions                | CPU Fmax (MHz) |     |     |  |

|---------------------------|---------------------------|----------------|-----|-----|--|

|                           |                           | ows            | 1WS | 2WS |  |

| PL0                       | V <sub>DDIO</sub> >1.62 V | 6              | 8   | 8   |  |

| (-40/85°C)<br>(-40/125°C) | V <sub>DDIO</sub> >2.7 V  | 7.5            | 8   | 8   |  |

| PL2                       | V <sub>DDIO</sub> >1.62 V | 14             | 28  | 32  |  |

| (-40/85°C)<br>(-40/125°C) | V <sub>DDIO</sub> >2.7 V  | 14             | 32  | 32  |  |

### Table 46-40. NVM Timing Characteristics <sup>(1)</sup>

| Symbol           | Timings    | Мах | Units |

|------------------|------------|-----|-------|

| t <sub>FPP</sub> | Page Write | 2.5 | ms    |

| t <sub>FRE</sub> | Row erase  | 6   |       |

Note: