#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d14a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 10. Memories

# **10.1 Embedded Memories**

The 32-bit physical memory address space is mapped as follows:

# Table 10-1. Memory Sizes

| Memory     | Base Address | Size [KB]                                      |                                                |                       |                       |  |  |  |

|------------|--------------|------------------------------------------------|------------------------------------------------|-----------------------|-----------------------|--|--|--|

|            |              | SAM L11x16 <u>(1)</u><br>SAM L10x16 <u>(1)</u> | SAM L11x15 <u>(1)</u><br>SAM L10x15 <u>(1)</u> | SAM L11x14 <u>(1)</u> | SAM L10x14 <u>(1)</u> |  |  |  |

| Flash      | 0x0000000    | 64                                             | 32                                             | 16                    | 16                    |  |  |  |

| Data Flash | 0x00400000   | 2                                              | 2                                              | 2                     | 2                     |  |  |  |

| SRAM       | 0x20000000   | 16                                             | 8                                              | 8                     | 4                     |  |  |  |

| Boot ROM   | 0x02000000   | 8                                              | 8                                              | 8                     | 8                     |  |  |  |

**Note:** 1. x = E or D.

# 10.1.1 Flash

SAM L10/L11 devices embed 16 KB, 32 KB or 64 KB of internal Flash mapped at address 0x0000 0000.

The Flash has a 512-byte (64 lines of 8 bytes) direct-mapped cache which is disabled by default after power up.

The Flash is organized into rows, where each row contains four pages. The Flash has a row-erase and a page-write granularity.

### Table 10-2. Flash Memory Parameters

| Device                      | Memory Size [KB] | Number of Rows | Row size [Bytes] | Number of Pages | Page size [Bytes] |

|-----------------------------|------------------|----------------|------------------|-----------------|-------------------|

| SAM L11x16 / SAM L10x16 (1) | 64               | 256            | 256              | 1024            | 64                |

| SAM L11x15 / SAM L10x15 (1) | 32               | 128            | 256              | 512             | 64                |

| SAM L11x14 / SAM L10x14 (1) | 16               | 64             | 256              | 256             | 64                |

# Note:

```

1. x = E or D.

```

The Flash is divided in different regions. Each region has a dedicated lock bit preventing from writing and erasing pages on it. Refer to the NVM Memory Organization figures in the *NVMCTRL* chapter to get the different regions definition.

**Note:** The regions size is configured by the Boot ROM at device startup by reading the NVM Boot Configuration Row (BOCOR). Please refer to the 14. Boot ROM chapter for more information.

# Table 10-3. Flash Lock Regions Parameters

| Device                       | SAM L10                        | SAM L11                                                                                              |

|------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|

| Number of FLASH Lock Regions | 2                              | 4                                                                                                    |

| Regions Name                 | Flash Boot / Flash Application | Flash Boot Secure / Flash Boot Non-Secure<br>Flash Application Secure / Flash Application Non-Secure |

# 16.12.14 CoreSight ROM Table Entry 1

| Name:     | ENTRY1               |

|-----------|----------------------|

| Offset:   | 0x1004               |

| Reset:    | 0xXXXXX00X           |

| Property: | PAC Write-Protection |

|           |                      |

| Bit    | 31            | 30   | 29      | 28   | 27       | 26 | 25  | 24    |

|--------|---------------|------|---------|------|----------|----|-----|-------|

|        | ADDOFF[19:12] |      |         |      |          |    |     |       |

| Access | R             | R    | R       | R    | R        | R  | R   | R     |

| Reset  | x             | х    | x       | x    | х        | x  | x   | x     |

|        |               |      |         |      |          |    |     |       |

| Bit    | 23            | 22   | 21      | 20   | 19       | 18 | 17  | 16    |

|        |               |      |         | ADDO | FF[11:4] |    |     |       |

| Access | R             | R    | R       | R    | R        | R  | R   | R     |

| Reset  | x             | х    | x       | х    | х        | х  | х   | x     |

|        |               |      |         |      |          |    |     |       |

| Bit    | 15            | 14   | 13      | 12   | 11       | 10 | 9   | 8     |

|        |               | ADDO | FF[3:0] |      |          |    |     |       |

| Access | R             | R    | R       | R    |          |    |     |       |

| Reset  | x             | x    | x       | x    |          |    |     |       |

|        |               |      |         |      |          |    |     |       |

| Bit    | 7             | 6    | 5       | 4    | 3        | 2  | 1   | 0     |

|        |               |      |         |      |          |    | FMT | EPRES |

| Access |               |      |         |      |          |    | R   | R     |

| Reset  |               |      |         |      |          |    | 1   | x     |

### Bits 31:12 - ADDOFF[19:0] Address Offset

The base address of the component, relative to the base address of this ROM table.

### Bit 1 – FMT Format

Always read as '1', indicating a 32-bit ROM table.

## Bit 0 – EPRES Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

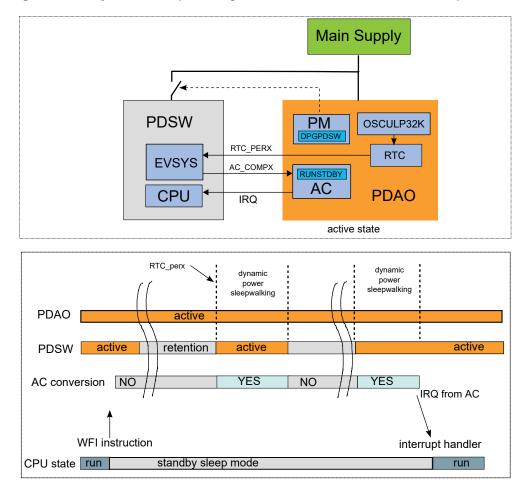

Dynamic SleepWalking based on event is illustrated in the following example:

# Figure 22-8. Dynamic SleepWalking based on Event: AC Periodic Comparison

The Analog Comparator (AC) peripheral is used in single shot mode to monitor voltage levels on input pins. A comparator interrupt, based on the AC peripheral configuration, is generated to wake up the device. In the GCLK module, the AC generic clock (GCLK\_AC) source is routed a 32.768kHz oscillator (for low power applications, OSC32KULP is recommended). RTC and EVSYS modules are configured to generate periodic events to the AC. To make the comparator continue to run in standby sleep mode, the RUNSTDBY bit is written to '1'. To enable the dynamic SleepWalking for PDSW power domain, STDBYCFG.PDSW must be written to '1'.

*Entering standby mode*: The Power Manager sets the PDSW power domain in retention state. The AC comparators, COMPx, are OFF. The GCLK\_AC clock is stopped. The VDDCORE is supplied by the low power regulator.

*Dynamic SleepWalking*: The RTC event (RTC\_PERX) is routed by the Event System to the Analog Comparator to trigger a single-shot measurement. This event is detected by the Power Manager, which sets the PDSW power domain to active state and starts the main voltage regulator.

After enabling the AC comparator and starting the GCLK\_AC, the single-shot measurement can be performed during Sleep mode (sleepwalking task), refer to 42.6.14.2 Single-Shot Measurement during Sleep for details. At the end of the conversion, if conditions to generate an interrupt are not met, the GCLK\_AC clock is stopped again, as well as the AC comparator.

© 2018 Microchip Technology Inc.

# 22.7 Register Summary

| Offset | Name     | Bit Pos. |        |         |         |         |             |         |

|--------|----------|----------|--------|---------|---------|---------|-------------|---------|

| 0x01   | SLEEPCFG | 7:0      |        |         |         | S       | LEEPMODE[2: | 0]      |

| 0x02   | PLCFG    | 7:0      | PLDIS  |         |         |         | PLSE        | L[1:0]  |

| 0x03   | PWCFG    | 7:0      |        |         |         |         | RAMPS       | WC[1:0] |

| 0x04   | INTENCLR | 7:0      |        |         |         |         |             | PLRDY   |

| 0x05   | INTENSET | 7:0      |        |         |         |         |             | PLRDY   |

| 0x06   | INTFLAG  | 7:0      |        |         |         |         |             | PLRDY   |

| 0x07   | Reserved |          |        |         |         |         |             |         |

| 0x08   | STDBYCFG | 7:0      | VREGSM | OD[1:0] | DPGPDSW |         |             | PDCFG   |

| 0,00   | STUBTURG | 15:8     |        |         | BBIASTR | BBIASHS |             |         |

# 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 22.5.7 Register Access Protection.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

# 23.8.13 DFLLULP Target Ratio

| Name:     | DFLLULPRATIO                           |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| R<br>0 |

|--------|

|        |

| 0      |

|        |

|        |

| 16     |

|        |

| R      |

| 0      |

|        |

| 8      |

|        |

| R/W    |

| 0      |

|        |

| 0      |

|        |

| R/W    |

| 0      |

|        |

# Bits 10:0 – RATIO[10:0] Target Tuner Ratio

Writing a value to this field sets the target ratio between the DFLLULP output clock and the reference clock. The DFLLULPDLY.DELAY value will be updated in such a way that the target ratio and the actual ratio are as close as possible.

The hysteresis functionality can be used in both Continuous and Sampling Mode.

### 25.6.3.8 Sleep Mode Operation

### 25.6.3.8.1 Standby Mode

The BOD33 can be used in standby mode if the BOD is enabled and the corresponding Run in Standby bit is written to '1' (BOD33.RUNSTDBY).

The BOD33 can be configured to work in either Continuous or Sampling Mode by writing a '1' to the Configuration in Standby Sleep Mode bit (BOD33.STDBYCFG).

# 25.6.4 Interrupts

The SUPC has the following interrupt sources, which are either synchronous or asynchronous wake-up sources:

- VDDCORE Voltage Ready (VCORERDY), asynchronous

- Voltage Regulator Ready (VREGRDY) asynchronous

- BOD33 Ready (BOD33RDY), synchronous

- BOD33 Detection (BOD33DET), asynchronous

- BOD33 Synchronization Ready (B33SRDY), synchronous

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the SUPC is reset. See the INTFLAG register for details on how to clear interrupt flags. The SUPC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

# **Related Links**

22.6.3.3 Sleep Mode Controller

# 25.6.5 Events

The SUPC can gemerate the following output event:

- BOD12 Detection (BOD12DET): Generated when the VDDCORE crosses below the brown-out threshold level.

- BOD33 Detection (BOD33DET): Generated when the VDD crosses below the brown-out threshold level.

Writing a one to an Event Output bit in the Event Control Register (EVCTRL.xxEO) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the Event System chapter for details on configuring the event system.

# 25.6.6 Synchronization

The prescaler counters that are used to trigger brown-out detections operate asynchronously from the peripheral bus. As a consequence, the BOD33 Enable bit (BOD33.ENABLE) need synchronization when written.

# 27. RTC – Real-Time Counter

# 27.1 Overview

The Real-Time Counter (RTC) is a 32-bit counter with a 10-bit programmable prescaler that typically runs continuously to keep track of time. The RTC can wake up the device from sleep modes using the alarm/ compare wake up, periodic wake up, or overflow wake up mechanisms, or from the wake inputs.

The RTC can generate periodic peripheral events from outputs of the prescaler, as well as alarm/compare interrupts and peripheral events, which can trigger at any counter value. Additionally, the timer can trigger an overflow interrupt and peripheral event, and can be reset on the occurrence of an alarm/compare match. This allows periodic interrupts and peripheral events at very long and accurate intervals.

The 10-bit programmable prescaler can scale down the clock source. By this, a wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the minimum counter tick interval is  $30.5\mu$ s, and time-out periods can range up to 36 hours. For a counter tick interval of 1s, the maximum time-out period is more than 136 years.

# 27.2 Features

- 32-bit counter with 10-bit prescaler

- Multiple clock sources

- 32-bit or 16-bit counter mode

- One 32-bit or two 16-bit compare values

- Clock/Calendar mode

- Time in seconds, minutes, and hours (12/24)

- Date in day of month, month, and year

- Leap year correction

- Digital prescaler correction/tuning for increased accuracy

- Overflow, alarm/compare match and prescaler interrupts and events

- Optional clear on alarm/compare match

- 2 general purpose registers

- Tamper Detection

- Timestamp on event or up to 5 inputs with debouncing

- Active layer protection

# 27.10.1 Control A in COUNT16 mode (CTRLA.MODE=1)

| Name:     | CTRLA                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x00                                                       |

| Reset:    | 0x0000                                                     |

| Property: | PAC Write-Protection, Enable-Protected, Write-Synchronized |

| Bit    | 15        | 14     | 13 | 12 | 11  | 10     | 9        | 8     |

|--------|-----------|--------|----|----|-----|--------|----------|-------|

|        | COUNTSYNC | GPTRST |    |    |     | PRESCA | LER[3:0] |       |

| Access | R/W       | R/W    |    |    | R/W | R/W    | R/W      | R/W   |

| Reset  | 0         | 0      |    |    | 0   | 0      | 0        | 0     |

|        |           |        |    |    |     |        |          |       |

| Bit    | 7         | 6      | 5  | 4  | 3   | 2      | 1        | 0     |

|        |           |        |    |    | MOD | E[1:0] | ENABLE   | SWRST |

| Access |           |        |    |    | R/W | R/W    | R/W      | R/W   |

| Reset  |           |        |    |    | 0   | 0      | 0        | 0     |

# Bit 15 – COUNTSYNC COUNT Read Synchronization Enable

The COUNT register requires synchronization when reading. Disabling the synchronization will prevent reading valid values from the COUNT register.

This bit is not enable-protected.

| Value | Description                            |

|-------|----------------------------------------|

| 0     | COUNT read synchronization is disabled |

| 1     | COUNT read synchronization is enabled  |

# Bit 14 – GPTRST GP Registers Reset On Tamper Enable

Only GP registers enabled by the CTRLB.GPnEN bits are affected. This bit can be written only when the peripheral is disabled.

This bit is not synchronized.

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | GPn registers will not reset when a tamper condition occurs. |

| 1     | GPn registers will reset when a tamper condition occurs.     |

# Bits 11:8 - PRESCALER[3:0] Prescaler

These bits define the prescaling factor for the RTC clock source (GCLK\_RTC) to generate the counter clock (CLK\_RTC\_CNT). Periodic events and interrupts are not available when the prescaler is off. These bits are not synchronized.

| Value | Name  | Description               |

|-------|-------|---------------------------|

| 0x0   | OFF   | CLK_RTC_CNT = GCLK_RTC/1  |

| 0x1   | DIV1  | CLK_RTC_CNT = GCLK_RTC/1  |

| 0x2   | DIV2  | CLK_RTC_CNT = GCLK_RTC/2  |

| 0x3   | DIV4  | CLK_RTC_CNT = GCLK_RTC/4  |

| 0x4   | DIV8  | CLK_RTC_CNT = GCLK_RTC/8  |

| 0x5   | DIV16 | CLK_RTC_CNT = GCLK_RTC/16 |

| 0x6   | DIV32 | CLK_RTC_CNT = GCLK_RTC/32 |

| 0x7   | DIV64 | CLK_RTC_CNT = GCLK_RTC/64 |

# RTC – Real-Time Counter

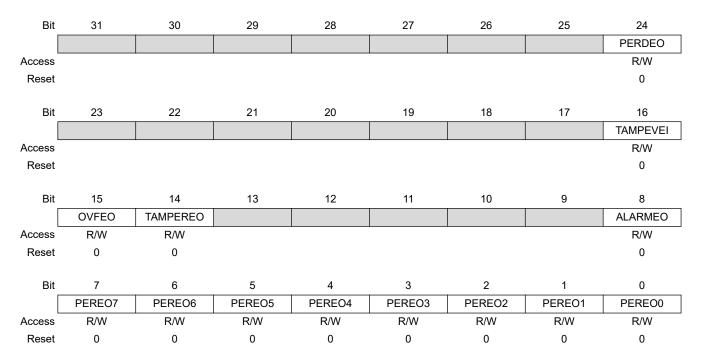

# 27.12.3 Event Control in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x04                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

# Bit 24 – PERDEO Periodic Interval Daily Event Output Enable

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | Periodic Daily event is disabled and will not be generated.                        |

| 1     | Periodic Daily event is enabled and will be generated.                             |

|       | The event occurs at the last second of each day depending on the CTRLA.CLKREP bit: |

|       | <ul> <li>If CLKREP = 0, the event will occur at 23:59:59</li> </ul>                |

|       | • If CLKREP = 1, the event will occur at 11:59:59, PM = 1                          |

# Bit 16 – TAMPEVEI Tamper Event Input Enable

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Tamper event input is disabled, and incoming events will be ignored.                 |

| 1     | Tamper event input is enabled, and all incoming events will capture the CLOCK value. |

### Bit 15 – OVFEO Overflow Event Output Enable

| V | alue | Description                                                         |

|---|------|---------------------------------------------------------------------|

| 0 |      | Overflow event is disabled and will not be generated.               |

| 1 |      | Overflow event is enabled and will be generated for every overflow. |

# Bit 4 – EVOE Channel Event Output Enable

This bit indicates if the Channel event generation is enabled. The event will be generated for every condition defined in the descriptor Event Output Selection (BTCTRL.EVOSEL).

This bit is available only for the four least significant DMA channels. Refer to table: *User Multiplexer Selection* and *Event Generator Selection* of the Event System for details.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | Channel event generation is disabled. |

| 1     | Channel event generation is enabled.  |

# Bit 3 – EVIE Channel Event Input Enable

This bit is available only for the four least significant DMA channels. Refer to table: *User Multiplexer Selection* and *Event Generator Selection* of the Event System for details.

| Value | Description                                                      |

|-------|------------------------------------------------------------------|

| 0     | Channel event action will not be executed on any incoming event. |

| 1     | Channel event action will be executed on any incoming event.     |

# Bits 2:0 – EVACT[2:0] Event Input Action

These bits define the event input action, as shown below. The action is executed only if the corresponding EVIE bit in the CHCTRLB register of the channel is set.

These bits are available only for the four least significant DMA channels. Refer to table: *User Multiplexer Selection* and *Event Generator Selection* of the Event System for details.

| EVACT[2:0] | Name    | Description                                                |

|------------|---------|------------------------------------------------------------|

| 0x0        | NOACT   | No action                                                  |

| 0x1        | TRIG    | Normal Transfer and Conditional Transfer on Strobe trigger |

| 0x2        | CTRIG   | Conditional transfer trigger                               |

| 0x3        | CBLOCK  | Conditional block transfer                                 |

| 0x4        | SUSPEND | Channel suspend operation                                  |

| 0x5        | RESUME  | Channel resume operation                                   |

| 0x6        | SSKIP   | Skip next block suspend action                             |

| 0x7        | -       | Reserved                                                   |

# Related Links

33.7.8 CHANNEL

### 28.8.21 Channel Interrupt Enable Set

Name:CHINTENSETOffset:0x4DReset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Channel Interrupt Enable Clear (CHINTENCLR) register. This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0    |

|--------|---|---|---|---|---|------|-------|------|

|        |   |   |   |   |   | SUSP | TCMPL | TERR |

| Access |   |   |   |   |   | R/W  | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0    | 0     | 0    |

Bit 2 – SUSP Channel Suspend Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Suspend Interrupt Enable bit, which enables the Channel Suspend interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Channel Suspend interrupt is disabled. |

| 1     | The Channel Suspend interrupt is enabled.  |

Bit 1 – TCMPL Channel Transfer Complete Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Complete Interrupt Enable bit, which enables the Channel Transfer Complete interrupt.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The Channel Transfer Complete interrupt is disabled. |

| 1     | The Channel Transfer Complete interrupt is enabled.  |

Bit 0 – TERR Channel Transfer Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Error Interrupt Enable bit, which enables the Channel Transfer Error interrupt.

|   | /alue | Description                                       |

|---|-------|---------------------------------------------------|

| ( | )     | The Channel Transfer Error interrupt is disabled. |

| - | L     | The Channel Transfer Error interrupt is enabled.  |

# 29.7 Register Summary

# Important:

•

For SAM L11, the EIC register map is automatically duplicated in a Secure and Non-Secure alias:

- The Non-Secure alias is at the peripheral base address

- The Secure alias is located at the peripheral base address + 0x200

Refer to Mix-Secure Peripherals for more information on register access rights

| Offset   | Name        | Bit Pos. |         |            |           |           |               |       |

|----------|-------------|----------|---------|------------|-----------|-----------|---------------|-------|

| 0x00     | CTRLA       | 7:0      |         |            | CKSEL     |           | ENABLE        | SWRST |

| 0x01     | NMICTRL     | 7:0      |         |            | NMIASYNCH | NMIFILTEN | NMISENSE[2:0] |       |

| 000      | NMIFLAG     | 7:0      |         |            |           |           |               | NMI   |

| 0x02     |             | 15:8     |         |            |           |           |               |       |

|          |             | 7:0      |         |            |           |           | ENABLE        | SWRST |

| 0.04     | 01410011014 | 15:8     |         |            |           |           |               |       |

| 0x04     | SYNCBUSY    | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    |         |            |           |           |               |       |

|          |             | 7:0      |         |            | EXTINT    | EO[7:0]   |               |       |

|          |             | 15:8     |         |            |           |           |               |       |

| 0x08     | EVCTRL      | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    |         |            |           |           |               |       |

|          | INTENCLR    | 7:0      |         |            | EXTIN     | IT[7:0]   |               |       |

|          |             | 15:8     |         |            |           |           |               |       |

| 0x0C     |             | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    | NSCHK   |            |           |           |               |       |

|          | INTENSET    | 7:0      |         |            | EXTIN     | IT[7:0]   |               |       |

|          |             | 15:8     |         |            |           |           |               |       |

| 0x10     |             | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    | NSCHK   |            |           |           |               |       |

|          |             | 7:0      |         |            | EXTIN     | IT[7:0]   |               |       |

|          |             | 15:8     |         |            |           |           |               |       |

| 0x14     | INTFLAG     | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    | NSCHK   |            |           |           |               |       |

|          |             | 7:0      |         |            | ASYN      | CH[7:0]   |               |       |

|          |             | 15:8     |         |            |           |           |               |       |

| 0x18     | ASYNCH      | 23:16    |         |            |           |           |               |       |

|          |             | 31:24    |         |            |           |           |               |       |

|          |             | 7:0      | FILTENx | SENSEx[2:0 | 1         | FILTENx   | SENSEx[2:0]   |       |

|          |             | 15:8     | FILTENx | SENSEx[2:0 |           | FILTENx   | SENSEx[2:0]   |       |

| 0x1C     | CONFIG      | 23:16    | FILTENx | SENSEx[2:0 |           | FILTENx   | SENSEx[2:0]   |       |

|          |             | 31:24    | FILTENX | SENSEx[2:0 |           | FILTENx   | SENSEx[2:0]   |       |

| 0x20     |             |          |         |            |           |           |               |       |

| <br>0x2F | Reserved    |          |         |            |           |           |               |       |

### 29.8.2 Non-Maskable Interrupt Control

| Name:     | NMICTRL                          |

|-----------|----------------------------------|

| Offset:   | 0x01                             |

| Reset:    | 0x00                             |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the NMI interrupt is set as Non-Secure in the NONSEC register (NONSEC.NMI bit).

| Bit    | 7 | 6 | 5 | 4         | 3         | 2         | 1             | 0         |

|--------|---|---|---|-----------|-----------|-----------|---------------|-----------|

|        |   |   |   | NMIASYNCH | NMIFILTEN |           | NMISENSE[2:0] |           |

| Access |   |   |   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW     | RW/RW*/RW |

| Reset  |   |   |   | 0         | 0         | 0         | 0             | 0         |

**Bit 4 – NMIASYNCH** Non-Maskable Interrupt Asynchronous Edge Detection Mode The NMI edge detection can be operated synchronously or asynchronously to the EIC clock.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The NMI edge detection is synchronously operated.  |

| 1     | The NMI edge detection is asynchronously operated. |

**Bit 3 – NMIFILTEN** Non-Maskable Interrupt Filter Enable

| Value | Description             |

|-------|-------------------------|

| 0     | NMI filter is disabled. |

| 1     | NMI filter is enabled.  |

# Bits 2:0 – NMISENSE[2:0] Non-Maskable Interrupt Sense Configuration

These bits define on which edge or level the NMI triggers.

| Value | Name | Description            |

|-------|------|------------------------|

| 0x0   | NONE | No detection           |

| 0x1   | RISE | Rising-edge detection  |

| 0x2   | FALL | Falling-edge detection |

| 0x3   | BOTH | Both-edge detection    |

| 0x4   | HIGH | High-level detection   |

| 0x5   | LOW  | Low-level detection    |

| 0x6 - | -    | Reserved               |

| 0x7   |      |                        |

Writing '1' to a bit will clear the corresponding bit in the OUT register. Pins configured as outputs via the Data Direction register (DIR) will be set to low output drive level. Pins configured as inputs via DIR and with pull enabled via the Pull Enable bit in the Pin Configuration register (PINCFG.PULLEN) will set the input pull direction to an internal pull-down.

| Value | Description                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration.                                |

| 1     | The corresponding I/O pin output is driven low, or the input is connected to an internal pull-<br>down. |

Important: Only EVSYS channel 0 to 3 can be configured as synchronous or resynchronized.

# **Related Links**

19.6.2.6 Peripheral Clock Masking18. GCLK - Generic Clock Controller

### 33.4.4 DMA

Not applicable.

## 33.4.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the EVSYS interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

## 33.4.6 Events

Not applicable.

### 33.4.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging.

### 33.4.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except for the following:

- Channel Pending Interrupt (INTPEND)

- Channel n Interrupt Flag Status and Clear (CHINTFLAGn)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

Write-protection does not apply for accesses through an external debugger.

### 33.4.9 SAM L11 TrustZone Specific Register Access Protection

When the EVSYS is not PAC secured, non-secure and secure code can both access all functionalities. When the EVSYS is PAC secured, all registers are by default available in the secure alias only.

A PAC secured EVSYS can open up individual event channels and event users for non-secure access. This is done using the NONSECCHAN and NONSECUSER registers. When a channel or event user has been configured as non-secure, it can be handled from non-secure code using the EVSYS module non-secure alias. Since only Secured code has the rights to modify the NONSECCHAN and NONSECUSER registers, an interrupt-based mechanism has been added to let Non Secured code know when these registers have been changed by Secured code. A single flag called NSCHK in the INTFLAG register will rise should changes, conditioned by the NSCHKCHAN and NSCHKUSER registers, occur in the NONSECCHAN and NONSECUSER registers.

Note: Refer to the Mix-Secure Peripherals section in the SAM L11 Security Features chapter.

### 33.4.10 Analog Connections

Not applicable.

# 42.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access |   |   |   |   |   |   | R/W    | W     |

| Reset  |   |   |   |   |   |   | 0      | 0     |

## Bit 1 – ENABLE Enable

Due to synchronization, there is delay from updating the register until the peripheral is enabled/disabled. The value written to CTRL.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the peripheral is enabled/disabled.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The AC is disabled.                                                                       |

| 1     | The AC is enabled. Each comparator must also be enabled individually by the Enable bit in |

|       | the Comparator Control register (COMPCTRLn.ENABLE).                                       |

## Bit 0 – SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the AC to their initial state, and the AC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# 43.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|----------|---|---|---|---|--------|-------|

|        |   | RUNSTDBY |   |   |   |   | ENABLE | SWRST |

| Access |   | R/W      |   |   |   |   | R/W    | R/W   |

| Reset  |   | 0        |   |   |   |   | 0      | 0     |

## Bit 6 - RUNSTDBY Run in Standby

This bit is not synchronized

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | The DAC output buffer is disabled in standby sleep mode.    |

| 1     | The DAC output buffer can be enabled in standby sleep mode. |

## Bit 1 – ENABLE Enable DAC Controller

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the DAC to their initial state, and the DAC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# 43.8.6 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x06Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | EMPTY | UNDERRUN |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

### Bit 1 – EMPTY Data Buffer Empty

This flag is cleared by writing a '1' to it or by writing new data to DATABUF.

This flag is set when data is transferred from DATABUF to DATA, and the DAC is ready to receive new data in DATABUF, and will generate an interrupt request if INTENCLR/SET.EMPTY is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Empty interrupt flag.

#### Bit 0 – UNDERRUN Underrun

This flag is cleared by writing a '1' to it.

This flag is set when a start conversion event occurs when DATABUF is empty, and will generate an interrupt request if INTENCLR/SET.UNDERRUN is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Underrun interrupt flag.

# 50.5 Unused or Unconnected Pins

For unused pins the default state of the pins will give the lowest current leakage. Thus there is no need to do any configuration of the unused pins in order to lower the power consumption.

# 50.6 Clocks and Crystal Oscillators

The SAM L10/L11 can be run from internal or external clock sources, or a mix of internal and external sources. An example of usage can be to use the internal 16MHz oscillator as source for the system clock and an external 32.768kHz watch crystal as clock source for the Real-Time counter (RTC).

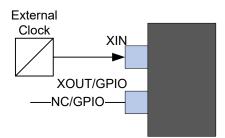

# 50.6.1 External Clock Source

## Figure 50-6. External Clock Source Schematic

# Table 50-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    | NC/GPIO                            |

# 50.6.2 Crystal Oscillator

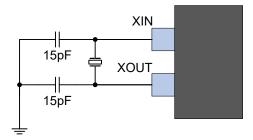

# Figure 50-7. Crystal Oscillator Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause too high load to operate the crystal, and cause crosstalk to other parts of the system.

Table 50-5.

Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 32MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |

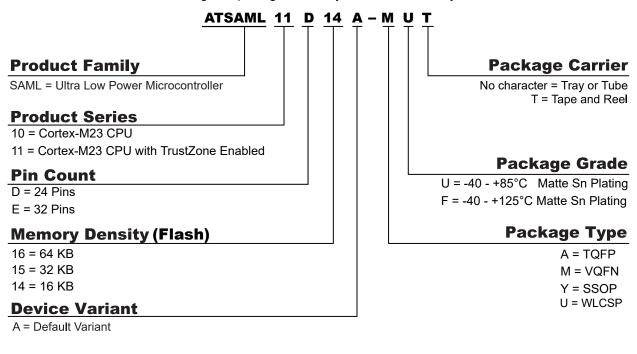

# **Product Identification System**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

# Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR

© 2018 Microchip Technology Inc.