# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 24-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d14a-yut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- HMAC is described in FIPS PUB 198-1.

- The hash used for HMAC is SHA256.

- The output of the HMAC-SHA256 is truncated to obtain an HMAC-SHA256-128 as explained in RFC4868.

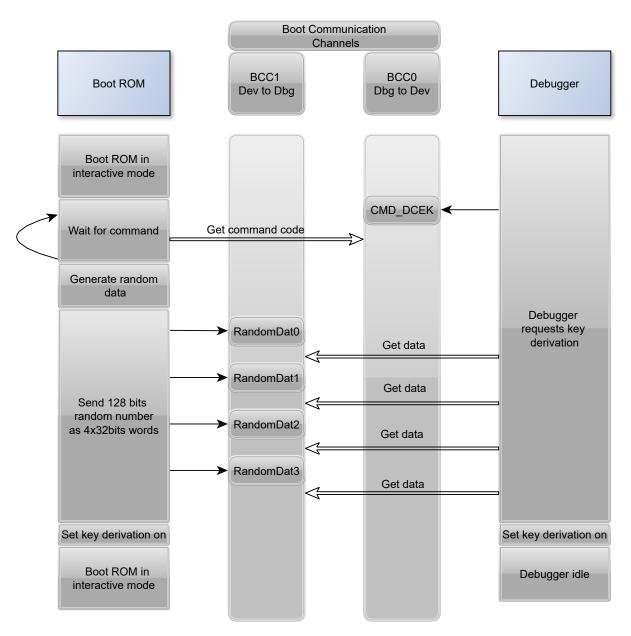

#### 14.4.5.7.1 CMD\_DCEK (SAM L11 only)

#### Figure 14-14. CMD\_DCEK Flow diagram

#### 14.4.5.8 NVM Rows Content Checks (CMD\_RAUX)

The Boot ROM provides a way to check the content of the NVM rows.

When device is secured (DAL0), the fuse configuration can still be read by the debugger using the Read Auxiliary command (CMD\_RAUX).

• 0x0: debugger can only access the DSU external address space making it possible to communicate with the Boot ROM after reset.

A typical programming procedure when DAL=0x2 is as follows:

- 1. At power up, RESET is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating state.

- 2. The Power Manager (PM) starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- 3. The debugger maintains a low level on SWCLK. RESET is released, resulting in a debugger Cold-Plugging procedure.

- 4. The debugger generates a clock signal on the SWCLK pin, the Debug Access Port (DAP) receives a clock.

- 5. The CPU executes the Boot ROM.

- 6. It is recommended to issue a Chip-Erase (supported by the Boot ROM) to ensure that the Flash is fully erased prior to programming.

- 7. If the operation issued above was accepted and has completed successfully then DAL equals 0x2 thus programming is available through the AHB-AP.

- 8. After the operation is completed, the chip can be restarted either by asserting RESET, toggling power, or sending a command to the Boot ROM to jump to the NVM code. Make sure that the SWCLK pin is high when releasing RESET to prevent entering again the cold-plugging procedure with the Boot ROM stalling the CPU.

#### **Related Links**

30. NVMCTRL - Nonvolatile Memory Controller

# 16.8 Security Enforcement

Security enforcement aims at protecting intellectual property, which includes:

- Restricts access to internal memories from external tools depending on the debugger access level.

- Restricts access to a portion of the DSU address space from non-secure AHB masters depending on the debugger access level.

The DAL setting can be locked or reverted using Boot ROM commands depending on the Boot ROM user configuration. When DAL is equal to 0x0, read/write accesses using the AHB-AP are limited to the DSU external address range and DSU commands are restricted. When issuing a Boot ROM Chip-Erase, sensitive information is erased from volatile memory and Flash. Refer to 14. Boot ROM more information about the Boot ROM features.

The DSU implements a security filter that monitors the AHB transactions generated by the ARM AHB-AP inside the DAP. If DAL=0x0, then AHB-AP read/write accesses outside the DSU external address range are discarded, causing an error response that sets the ARM AHB-AP sticky error bits (refer to the "ARM Debug Interface v5 Architecture Specification", which is available for download at http://www.arm.com).

For security reasons, DSU features have limitations when used from a debug adapter. To differentiate external accesses from internal ones, the first 0x100 bytes of the DSU register map have been replicated at offset 0x100:

- The first 0x100 bytes form the internal address range

- The next 0x1F00 bytes form the external address range

# **DSU - Device Service Unit**

#### Name: PID1 Offset: 0x1FE4 0x00000FC Reset: **Property:** \_ Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 15 14 13 12 9 8 11 10 Access Reset 7 6 5 3 2 Bit 4 1 0 JEPIDCL[3:0] PARTNBH[3:0] R R R R R R R R Access Reset 1 1 1 1 1 1 0 0

#### 16.12.19 Peripheral Identification 1

**Bits 7:4 – JEPIDCL[3:0]** Low part of the JEP-106 Identity Code These bits will always return 0xF when read (JEP-106 identity code is 0x1F).

#### Bits 3:0 – PARTNBH[3:0] Part Number High

These bits will always return 0xC when read, indicating that this device implements a DSU module instance.

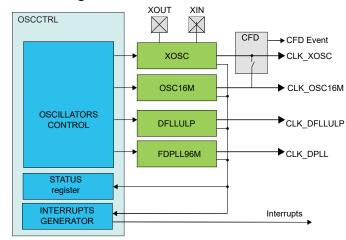

# 23.3 Block Diagram

Figure 23-1. OSCCTRL Block Diagram

# 23.4 Signal Description

| Signal | Description                                                       | Туре          |

|--------|-------------------------------------------------------------------|---------------|

| XIN    | Multipurpose Crystal Oscillator or external clock generator input | Analog input  |

| XOUT   | Multipurpose Crystal Oscillator output                            | Analog output |

The I/O lines are automatically selected when XOSC is enabled.

# 23.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 23.5.1 I/O Lines

I/O lines are configured by OSCCTRL when XOSC is enabled, and need no user configuration.

#### 23.5.2 Power Management

The OSCCTRL can continue to operate in any sleep mode where the selected source clock is running. The OSCCTRL interrupts can be used to wake up the device from sleep modes. The events can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

22. PM - Power Manager

#### 23.5.3 Clocks

The OSCCTRL gathers controls for all device oscillators and provides clock sources to the Generic Clock Controller (GCLK). The available clock sources are XOSC, OSC16M, DFLLULP and FDPLL96M.

The OSCCTRL bus clock (CLK\_OSCCTRL\_APB) can be enabled and disabled in the Main Clock module (MCLK).

# 27.12.9 Frequency Correction

| Name:     | FREQCORR                                 |

|-----------|------------------------------------------|

| Offset:   | 0x14                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7    | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|--------|------|-----|-----|-----|------------|-----|-----|-----|

|        | SIGN |     |     |     | VALUE[6:0] |     |     |     |

| Access | R/W  | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |

| Reset  | 0    | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

Bit 7 – SIGN Correction Sign

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The correction value is positive, i.e., frequency will be decreased. |

| 1     | The correction value is negative, i.e., frequency will be increased. |

#### Bits 6:0 - VALUE[6:0] Correction Value

These bits define the amount of correction applied to the RTC prescaler.

| Value   | Description                                                |

|---------|------------------------------------------------------------|

| 0       | Correction is disabled and the RTC frequency is unchanged. |

| 1 - 127 | The RTC frequency is adjusted according to the value.      |

The tamper full erase routine operates at the highest priority. If a remanence routine executing when a tamper full erase occurs, the remanence routine is immediately terminated. If the CPU attempts to write a new scramble key at the same time the tamper key erase routine is active, the CPU data is ignored, but no bus error will occur. If a CPU security routine access is requested during a tamper full erase, the CPU transaction will be ignored and treated as a bus error similar to accessing the module during a software reset.

**Important:** In STANDBY low power mode, it is mandatory to enable the dynamic power gating feature (STDBYCFG.DPGPDSW) to ensure TrustRAM erasing when the power domain PDSW is in a retention state.

#### 31.6.3 Interrupts

The TRAM has the following interrupt sources:

- Data Remanence Prevention (DRP): Indicates that the data remanence prevention routine has ended.

- Data Read Error (ERR): Indicates when there is a RAM readout error.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TRAM is reset. See 22.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### 31.6.4 Sleep Mode Operation

The TRAM continues to operate during sleep. When it receives events from the Event System, it will request its own clock in order to perform the requested operation.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering an interrupt. In this case, the CPU will continue executing from the instruction following the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *EVSYS – Event System* for more information.

#### 31.6.5 Synchronization

Due to the asynchronicity between event sources and CLK\_TRAM\_APB some registers must be synchronized when accessed. A register can require:

Synchronization when written

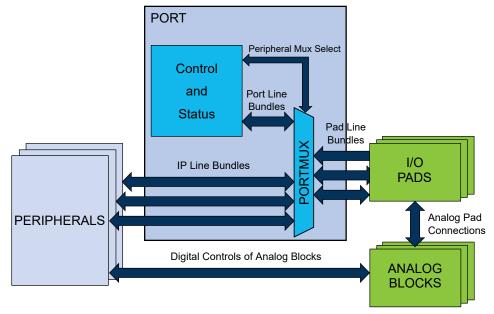

# 32.3 Block Diagram

Figure 32-1. PORT Block Diagram

# 32.4 Signal Description Table 32-1. Signal description for PORT

| Signal name Type |             | Description                          |  |  |  |  |

|------------------|-------------|--------------------------------------|--|--|--|--|

| Рху              | Digital I/O | General-purpose I/O pin y in group x |  |  |  |  |

Refer to the *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

# 32.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly as following.

#### 32.5.1 I/O Lines

The I/O lines of the PORT are mapped to pins of the physical device. The following naming scheme is used:

Each line bundle with up to 32 lines is assigned an identifier 'xy', with letter x=A, B, C... and two-digit number y=00, 01, ...31. Examples: A24, C03.

PORT pins are labeled 'Pxy' accordingly, for example PA24, PC03. This identifies each pin in the device uniquely.

Each pin may be controlled by one or more peripheral multiplexer settings, which allow the pad to be routed internally to a dedicated peripheral function. When the setting is enabled, the selected peripheral has control over the output state of the pad, as well as the ability to read the current physical pad state. Refer to *I/O Multiplexing and Considerations* for details.

© 2018 Microchip Technology Inc.

Writing '1' to a bit will clear the corresponding bit in the OUT register. Pins configured as outputs via the Data Direction register (DIR) will be set to low output drive level. Pins configured as inputs via DIR and with pull enabled via the Pull Enable bit in the Pin Configuration register (PINCFG.PULLEN) will set the input pull direction to an internal pull-down.

| Value | Description                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration.                                |

| 1     | The corresponding I/O pin output is driven low, or the input is connected to an internal pull-<br>down. |

#### Bit 17 – INEN Input Enable

This bit determines the new value written to PINCFGy.INEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 16 – PMUXEN Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bits 15:0 – PINMASK[15:0] Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

#### These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

# SAM L10/L11 Family

SERCOM USART - SERCOM Synchronous and Asyn...

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | NACK is transmitted when a parity error is received.     |

| 1     | NACK is not transmitted when a parity error is received. |

#### Bits 2:0 - GTIME[2:0] Guard Time

These bits define the guard time when using RS485 mode (CTRLA.FORM=0x0 or CTRLA.FORM=0x1, and CTRLA.TXPO=0x3) or ISO7816 mode (CTRLA.FORM=0x7).

For RS485 mode, the guard time is programmable from 0-7 bit times and defines the time that the transmit enable pin (TE) remains high after the last stop bit is transmitted and there is no remaining data to be transmitted.

For ISO7816 T=0 mode, the guard time is programmable from 2-9 bit times and defines the guard time between each transmitted byte.

# 37.8.9 Data

|        | Name:<br>Offset:<br>Reset:<br>Property: | DATA<br>0x28<br>0x0000<br>Read/Write |     |           |     |     |     |     |

|--------|-----------------------------------------|--------------------------------------|-----|-----------|-----|-----|-----|-----|

| Bit    | 15                                      | 14                                   | 13  | 12        | 11  | 10  | 9   | 8   |

| Access |                                         |                                      |     |           |     |     |     |     |

| Reset  |                                         |                                      |     |           |     |     |     |     |

| Bit    | 7                                       | 6                                    | 5   | 4<br>DATA | 3   | 2   | 1   | 0   |

| Access | R/W                                     | R/W                                  | R/W | R/W       | R/W | R/W | R/W | R/W |

| Reset  |                                         | 0                                    | 0   | 0         | 0   | 0   | 0   | 0   |

#### Bits 7:0 - DATA[7:0] Data

The slave data register I/O location (DATA.DATA) provides access to the master transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is held low by the slave (STATUS.CLKHOLD is set). An exception occurs when reading the last data byte after the stop condition has been received.

Accessing DATA.DATA auto-triggers I<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

### 38.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 38.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

#### **Related Links**

32. PORT - I/O Pin Controller

#### 38.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

22. PM – Power Manager

#### 38.5.3 Clocks

The TC bus clocks (CLK\_TCx\_APB) can be enabled and disabled in the Main Clock Module. The default state of CLK\_TCx\_APB can be found in the *Peripheral Clock Masking*.

The generic clocks (GCLK\_TCx) are asynchronous to the user interface clock (CLK\_TCx\_APB). Due to this asynchronicity, accessing certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

**Note:** Two instances of the TC may share a peripheral clock channel. In this case, they cannot be set to different clock frequencies. Refer to the peripheral clock channel mapping of the Generic Clock Controller (GCLK.PCHTRLm) to identify shared peripheral clocks.

#### **Related Links**

18.8.4 PCHCTRLm 19.6.2.6 Peripheral Clock Masking

#### 38.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

28. DMAC - Direct Memory Access Controller

#### 38.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### 38.5.6 Events

The events of this peripheral are connected to the Event System.

#### **Related Links**

This bit has no effect when input capture operation is enabled.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The CCBUFx and PERBUF buffer registers value are copied into CCx and PER registers on  |

|       | hardware update condition.                                                             |

| 1     | The CCBUFx and PERBUF buffer registers value are not copied into CCx and PER registers |

|       | on hardware update condition.                                                          |

#### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

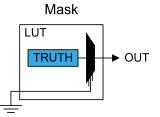

#### Figure 40-3. Masked Input Selection

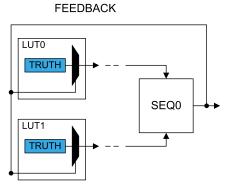

## Internal Feedback Inputs (FEEDBACK)

When selected (LUTCTRLx.INSELy=FEEDBACK), the Sequential (SEQ) output is used as input for the corresponding LUT.

The output from an internal sequential sub-module can be used as input source for the LUT, see figure below for an example for LUT0 and LUT1. The sequential selection for each LUT follows the formula:

IN[2N][i] = SEQ[N]

IN[2N+1][i] = SEQ[N]

With *N* representing the sequencer number and i=0,1,2 representing the LUT input index.

For details, refer to 40.6.2.7 Sequential Logic.

#### Figure 40-4. Feedback Input Selection

#### Linked LUT (LINK)

When selected (LUTCTRLx.INSELy=LINK), the subsequent LUT output is used as the LUT input (e.g., LUT2 is the input for LUT1), as shown in this figure:

Example: For ROOM\_TEMP\_VAL\_INT=0x19=25 and ROOM\_TEMP\_VAL\_DEC=2, the measured temperature at room insertion is 25.2°C.

- HOT\_TEMP\_VAL\_INT and HOT\_TEMP\_VAL\_DEC contain the measured temperature at hot insertion, *temp*<sub>H</sub>, in °C. The integer and decimal value are also separated.

- For each temperature, the corresponding sensor value at the ADC in 12-bit, ADC<sub>R</sub> and ADC<sub>H</sub>:

- ROOM\_ADC\_VAL contains the 12-bit ADC value, ADC<sub>R</sub>, corresponding to *temp*<sub>R</sub>. Its conversion to Volt is denoted V<sub>ADCR</sub>.

- HOT\_ADC\_VAL contains the 12-bit ADC value, ADC<sub>H</sub>, corresponding to *temp*<sub>H</sub>. Its conversion to Volt is denoted V<sub>ADCH</sub>.

- Actual reference voltages at each calibration temperature in Volt,  $INT1V_R$  and  $INT1V_H$ , respectively:

- ROOM\_INT1V\_VAL is the 2's complement of the internal 1V reference value at  $temp_R$ : INT1V<sub>R</sub>.

- HOT\_INT1V\_VAL is the 2's complement of the internal 1V reference value at *temp*<sub>H</sub>: INT1V<sub>H</sub>.

- Both ROOM\_INT1V\_VAL and HOT\_INT1V\_VAL values are centered around 1V with a 0.001V step. In other words, the range of values [0,127] corresponds to [1V, 0.873V] and the range of values [-1, -127] corresponds to [1.001V, 1.127V]. INT1V == 1 (VAL/1000) is valid for both ranges.

# Calculating the Temperature by Linear Interpolation

Using the data pairs ( $temp_R$ ,  $V_{ADCR}$ ) and ( $temp_H$ ,  $V_{ADCH}$ ) for a linear interpolation, we have the following equation:

$$\left(\frac{V_{ADC} - V_{ADCR}}{temp - temp_R}\right) = \left(\frac{V_{ADCH} - V_{ADCR}}{temp_H - temp_R}\right)$$

The voltages  $V_x$  are acquired as 12-bit ADC values  $ADC_x$ , with respect to an internal reference voltage INT1V<sub>x</sub>:

# [Equation 1]

$$V_{ADCx} = ADC_x \cdot \frac{\text{INT1V}_x}{2^{12} - 1}$$

For the measured value of the temperature sensor,  $ADC_m$ , the reference voltage is assumed to be perfect, i.e.,  $INT1V_m = INT1V_c = 1V$ . These substitutions yield a coarse value of the measured temperature  $temp_C$ :

# [Equation 2]

$$temp_{C} = temp_{R} + \left[ \frac{\left\{ \left( ADC_{m} \cdot \frac{INT1V_{C}}{(2^{12} - 1)} \right) - \left( ADC_{R} \cdot \frac{INT1V_{R}}{(2^{12} - 1)} \right) \right\} \cdot (temp_{H} - temp_{R})}{\left( ADC_{H} \cdot \frac{INT1V_{H}}{(2^{12} - 1)} \right) - \left( ADC_{R} \cdot \frac{INT1V_{R}}{(2^{12} - 1)} \right)} \right]$$

Or, after eliminating the 12-bit scaling factor  $(2^{12}-1)$ :

# [Equation 3]

$$temp_{C} = temp_{R} + \left[\frac{\{ADC_{m} \cdot \text{INT1V}_{c} - (ADC_{R} \cdot \text{INT1V}_{R})\} \cdot (temp_{H} - temp_{R})}{\{(ADC_{H} \cdot \text{INT1V}_{H}) - (ADC_{R} \cdot \text{INT1V}_{R})\}}\right]$$

#### 41.8.18 Debug Control

Name:DBGCTRLOffset:0x1CReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

This bit should be written only while a conversion is not ongoing.

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | The ADC is halted when the CPU is halted by an external debugger.                  |

| 1     | The ADC continues normal operation when the CPU is halted by an external debugger. |

# 42. AC – Analog Comparators

# 42.1 Overview

The Analog Comparator (AC) supports two individual comparators. Each comparator (COMP) compares the voltage levels on two inputs, and provides a digital output based on this comparison. Each comparator may be configured to generate interrupt requests and/or peripheral events upon several different combinations of input change.

Hysteresis and propagation delay can be adjusted to achieve the optimal operation for each application.

The input selection includes four shared analog port pins and several internal signals. Each comparator output state can also be output on a pin for use by external devices.

The comparators are grouped in pairs on each port. The AC peripheral implements one pair of comparators . These are called Comparator 0 (COMP0) and Comparator 1 (COMP1) They have identical behaviors, but separate control registers. The pair can be set in window mode to compare a signal to a voltage range instead of a single voltage level.

# 42.2 Features

- Two individual comparators

- Selectable propagation delay versus current consumption

- Selectable hysteresis: 4-level On, or Off

- Analog comparator outputs available on pins

- Asynchronous or synchronous

- Flexible input selection:

- Four pins selectable for positive or negative inputs

- Ground (for zero crossing)

- Bandgap reference voltage

- 64-level programmable VDD scaler per comparator

- DAC

- OPAMP2

- Interrupt generation on:

- Rising or falling edge

- Toggle

- End of comparison

- Window function interrupt generation on:

- Signal above window

- Signal inside window

- Signal below window

- Signal outside window

- Event generation on:

- Comparator output

- Window function inside/outside window

# 44.6 Functional Description

#### 44.6.1 Principle of Operation

Each OPAMP has one positive and one negative input. Each input may be chosen from either a selection of analog input pins, or internal inputs such as the DAC, the resistor ladder, and the ground and output of another OPAMP.

Each OPAMP can be configured with built-in feedback to support various functions with programmable or unity gain.

I/O pins are externally accessible so that the operational amplifier can be configured with external feedback.

All OPAMPs can be cascaded to support circuits such as differential amplifiers.

#### 44.6.2 Basic Operation

Each operational amplifier can be configured in different modes, selected by the OPAMP Control x register (OPAMPCTRLx):

- Standalone operational amplifier

- Operational amplifier with built-in feedback

After being enabled, a start-up delay is added before the output of the operational amplifier is available. This start-up time is measured internally to account for environmental changes such as temperature or voltage supply level.

When the OPAMP is ready, the respective Ready x bit in the Status register is set (STATUS.READYx=1).

If the supply voltage is below 2.5V, the start-up time is also dependent on the voltage doubler. If the supply voltage is always above 2.5V, the voltage doubler can be disabled by setting the Low-Power Mux bit in the Control A Register (CTRLA.LPMUX).

#### 44.6.2.1 Initialization

The OPAMP must be configured with the desired properties and inputs before it is enabled.

The asynchronous clocks CLK\_ULP32K must be configured in the OSC32KCTRL module before enabling individual OPAMPs. See OSC32KCTRL – 32KHz Oscillators Controller for further details.

#### **Related Links**

24. OSC32KCTRL - 32KHz Oscillators Controller

#### 44.6.2.2 Enabling, Disabling, and Resetting

The OPAMP is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The OPAMP is disabled by writing a '0' to CTRLA.ENABLE.

Each OPAMP sub-module is enabled by writing a '1' to the Enable bit in the OPAMP Control x register (OPAMPCTRLx.ENABLE). Each OPAMP sub-module is disabled by writing a '0' to OPAMPCTRLx.ENABLE.

The OPAMP module is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the OPAMP will be reset to their initial state, and the OPAMP will be disabled. Refer to 44.8.1 CTRLA for details.

#### 44.6.3 DMA Operation

Not applicable.

# Master Mode

$f_{SCKmax} = 1/2^*(t_{MIS} + t_{valid})$ , where  $t_{valid}$  is the slave time response to output data after detecting an SCK edge. For a non-volatile memory with  $t_{valid} = 12$  ns Max,  $f_{SPCKMax} = 3.7$  MHz @ VDDIO > 2.7V

#### Slave Mode

$f_{SCKmax} = 1/2^*(t_{SOV} + t_{su})$ , where  $t_{su}$  is the setup time from the master before sampling data. With a perfect master ( $t_{su}$ =0),  $f_{SPCKMax}$  = 6 MHz @ VDDIO > 2.7V

# 46.14.3 SERCOM in SPI Mode in PL2

# Table 46-58. SPI Timing Characteristics and Requirements <sup>(1)</sup>

| Symbol | Parameter                                                    | Conditions        |              | Min.                                   | Тур.      | Max. | Units |

|--------|--------------------------------------------------------------|-------------------|--------------|----------------------------------------|-----------|------|-------|

| tSCK   | SCK period<br>when tSOV=0                                    | Master            | Reception    | 2*(tMIS<br>+tSLAVE_OUT) <sup>(3)</sup> | -         | -    | ns    |

|        | on the slave<br>side                                         | Master            | Transmission | 2*(tMOV<br>+tSLAVE_IN) <sup>(4)</sup>  | -         | -    |       |

| tSCKW  | SCK high/low<br>width                                        | Master            |              | -                                      | 0,5*tSCK  | -    |       |

| tSCKR  | SCK rise<br>time <sup>(2)</sup>                              | Master            |              | -                                      | 0,25*tSCK | -    |       |

| tSCKF  | SCK fall<br>time <sup>(2)</sup>                              | Master            |              | -                                      | 0,25*tSCK | -    |       |

| tMIS   | MISO setup to                                                | Master, VDD       | )>2,70V      | 42.5                                   | -         | -    |       |

|        | SCK                                                          |                   | )>1,62V      | 52.5                                   | -         | -    |       |

| tMIH   | MISO hold<br>after SCK                                       | Master, VDD>2,70V |              | 0                                      | -         | -    |       |

|        |                                                              | Master, VDD>1,62V |              | 0                                      | -         | -    |       |

| tMOV   | MOSI output                                                  | Master, VDD>2,70V |              | -                                      | -         | 17.1 |       |

|        | valid after<br>SCK                                           | Master, VDD       | 0>1,62V      | -                                      | -         | 21.2 |       |

| tMOH   | MOSI hold                                                    | Master, VDD>2,70V |              | 6.3                                    | -         | -    |       |

|        | after SCK                                                    | Master, VDD>1,62V |              | 6.3                                    | -         | -    |       |

| tSSCK  | Slave SCK<br>Period when<br>tMIS =0 on<br>the master<br>side | Slave             | Reception    | 2*(tSIS<br>+tMASTER_OUT)<br>(5)        | -         | -    |       |

|        |                                                              | Slave             | Transmission | 2*(tSOV<br>+tMASTER_IN) <sup>(6)</sup> | -         | -    |       |

| tSSCKW | SCK high/low width                                           | Slave             |              | -                                      | 0,5*tSCK  | -    | ns    |

| tSSCKR | SCK rise<br>time <sup>(2)</sup>                              | Slave             |              | -                                      | 0,25*tSCK | -    |       |

| tSSCKF | SCK fall<br>time <sup>(2)</sup>                              | Slave             |              | -                                      | 0,25*tSCK | -    |       |

#### Table 47-25. Power Consumption<sup>(1)</sup>

| Symbol          | Parameter           | Conditions                       | ТА         | Min. | Тур. | Max. | Units |

|-----------------|---------------------|----------------------------------|------------|------|------|------|-------|

| I <sub>DD</sub> | Current Consumption | Fout = 48 MHz (PL0) - VDD = 3.3V | Max. 125°C | -    | 339  | 618  | μA    |

|                 |                     | Fout = 96 MHz (PL2) - VDD = 3.3V | Typ. 25°C  | -    | 678  | 1005 |       |

**Note:** These characteristics are only applicable in LDO regulator mode.

# 47.6 Timing Characteristics

#### 47.6.1 SERCOM in SPI Mode in PL0

#### Table 47-26. SPI Timing Characteristics and Requirements <sup>(1)</sup>

| Symbol | Parameter                                                | Conditi           | ions         | Min.                                   | Тур.      | Max. | Units |  |

|--------|----------------------------------------------------------|-------------------|--------------|----------------------------------------|-----------|------|-------|--|

| tSCK   | SCK period<br>when tSOV=0 on<br>the slave side           | Master            | Reception    | 2*(tMIS<br>+tSLAVE_OUT) <sup>(3)</sup> | -         | -    | ns    |  |

|        |                                                          | Master            | Transmission | 2*(tMOV<br>+tSLAVE_IN) <sup>(4)</sup>  | -         | -    |       |  |

| tSCKW  | SCK high/low<br>width                                    | Master            |              | -                                      | 0,5*tSCK  | -    |       |  |

| tSCKR  | SCK rise time <sup>(2)</sup>                             | Master            |              | -                                      | 0,25*tSCK | -    |       |  |

| tSCKF  | SCK fall time <sup>(2)</sup>                             | Master            |              | -                                      | 0,25*tSCK | -    |       |  |

| tMIS   | MISO setup to                                            | Master, VDD>2,70V |              | 86                                     | -         | -    |       |  |

|        | SCK                                                      | Master,           | VDD>1,62V    | 95                                     | -         | -    |       |  |

| tMIH   | MISO hold after<br>SCK                                   | Master, VDD>2,70V |              | 0                                      | -         | -    |       |  |

|        |                                                          | Master,           | VDD>1,62V    | 0                                      | -         | -    |       |  |

| tMOV   | MOSI output                                              | Master,           | VDD>2,70V    | -                                      | -         | 33.3 | ns    |  |

|        | valid after SCK                                          | Master,           | VDD>1,62V    | -                                      | -         | 49.6 |       |  |

| tMOH   | MOSI hold after<br>SCK                                   | Master,           | VDD>2,70V    | 9.7                                    | -         | -    |       |  |

| tMOH   | MOSI hold after<br>SCK                                   | Master,           | VDD>1,62V    | 9.7                                    | -         | -    |       |  |

| tSSCK  | Slave SCK<br>Period when<br>tMIS=0 on the<br>master side | Slave             | Reception    | 2*(tSIS<br>+tMASTER_OUT)<br>(5)        | -         | -    |       |  |

|        |                                                          | Slave             | Transmission | 2*(tSOV<br>+tMASTER_IN) <sup>(6)</sup> | -         | -    |       |  |

| tSSCKW | SCK high/low<br>width                                    | Slave             |              | -                                      | 0,5*tSCK  | -    |       |  |