Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d15a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 46.1.                                                                                                                                                                | Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 46.2.                                                                                                                                                                | Thermal Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1125     |

| 46.3.                                                                                                                                                                | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 46.4.                                                                                                                                                                | General Operating Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 46.5.                                                                                                                                                                | Supply Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1127     |

| 46.6.                                                                                                                                                                | Maximum Clock Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1127     |

| 46.7.                                                                                                                                                                | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1129     |

| 46.8.                                                                                                                                                                | Wake-Up Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 46.9.                                                                                                                                                                | I/O Pin Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1134     |

| 46.10                                                                                                                                                                | ). Injection Current                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1135     |

| 46.1                                                                                                                                                                 | . Analog Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1136     |

| 46.12                                                                                                                                                                | 2. NVM Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1152     |

| 46.13                                                                                                                                                                | 3. Oscillators Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1153     |

| 46.14                                                                                                                                                                | I. Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 47. 125                                                                                                                                                              | C Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1166     |

| 47 1                                                                                                                                                                 | Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1166     |

|                                                                                                                                                                      | General Operating Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|                                                                                                                                                                      | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|                                                                                                                                                                      | Analog Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|                                                                                                                                                                      | Oscillators Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                                                                                                                                                                      | Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 48. AC                                                                                                                                                               | and DC Characteristics Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1192     |

|                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 85°C                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|                                                                                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 85°C<br>Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                         |          |

| 48.2.                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1194     |

| 48.2.<br>49. Pac                                                                                                                                                     | Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 48.2.<br><b>49. Pac</b><br>49.1.                                                                                                                                     | Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                                                                                             | 1194<br> |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.                                                                                                                                   | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information                                                                                                                                                                                                                                                                                                                                                        | 1194<br> |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.                                                                                                                          | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings                                                                                                                                                                                                                                                                                                                                    |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch                                                                                                               | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile.                                                                                                                                                                                                                                                                                                              |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction                                                                                                                                                                                                                                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.                                                                                             | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile                                                                                                                                                                                                                                                                                                               |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.                                                                                    | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply                                                                                                                                                                                                                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.                                                                           | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections                                                                                                                                                                                                                  |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.                                                                  | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit.                                                                                                                                                                                       |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.                                                         | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins                                                                                                                                                          |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.                                                | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings.<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators                                                                                                                       |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.                                       | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports                                                                                         |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con                            | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.                   | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation                         |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.<br>51.2.          | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation<br>Memory Size and Type |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.<br>51.2.<br>51.2. | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation                         |          |

| 52. Acronyms and Abbreviations1218             |  |  |  |  |  |  |

|------------------------------------------------|--|--|--|--|--|--|

| 53. Datasheet Revision History                 |  |  |  |  |  |  |

| The Microchip Web Site 1222                    |  |  |  |  |  |  |

| Customer Change Notification Service1222       |  |  |  |  |  |  |

| Customer Support 1222                          |  |  |  |  |  |  |

| Product Identification System1223              |  |  |  |  |  |  |

| Vicrochip Devices Code Protection Feature1223  |  |  |  |  |  |  |

| Legal Notice1223                               |  |  |  |  |  |  |

| Trademarks 1224                                |  |  |  |  |  |  |

| Quality Management System Certified by DNV1224 |  |  |  |  |  |  |

| Worldwide Sales and Service1226                |  |  |  |  |  |  |

#### 14.4.2.1.3 CRC Computation and Programming

The CRCs needs to be recalculated and updated in their respective NVM row as soon as a data from any of the checked regions is changed.

**Important:** USERCRC and BOCORCRC CRCs programming must be done by any programming tool supporting the SAM L11 devices.

The algorithm is a CRC-32 module embedded in the DSU peripheral and that uses for both CRC calculation with the following parameters:

- Width = 32 bits

- Polynomial = 0x04C11DB7 (Poly)

- Initial Value = 0xFFFFFFFF (Init)

- Input Data is reflected (RefIn)

- Output Data is reflected (RefOut)

- No XOR is performed on the output CRC (XorOut)

Example: the DSU CRC of 0x31, 0x32, 0x33, 0x34, 0x35, 0x36, 0x37, 0x38, 0x39 is 0x340BC6D9

#### 14.4.2.2 Memories and Peripherals Configurations Initialization

For SAM L11 devices, memories and peripherals security attributions are done by reading the different fuses values from the NVM User (UROW) and Boot Configuration (BOCOR) rows.

The Boot ROM is responsible for setting these attributions on the different concerned memory and peripheral controllers:

- Set memory security attribution according to AS, ANSC, DS, RS, BS, BSNC and BOOTPROT fuses

- Set peripherals security attribution according to NONSECA, NONSECB and NONSECC fuses

**Important:** The Boot ROM does not perform any consistency checks on the configured memory attributions (e.g setting BS>BOOTPROT will not trigger any errors during Boot ROM execution).

#### 14.4.2.3 Secure Boot

Depending on the BOOTOPT fuse value (from BOCOR NVM row), the following secure boot integrity checks will be performed on:

- The Flash BS memory area which is composed by:

- The Flash Secure BOOT memory region

- The Flash Non-Secure Callable BOOT memory region

- And the NVM Boot Configuration row (BOCOR)

#### Table 14-4. Secure Boot Options

| вооторт | Verified Areas         | Verification Method |

|---------|------------------------|---------------------|

| 0       | None                   | -                   |

| 1       | Flash BS Memory Region | SHA-256             |

|         | +                      |                     |

|         | NVM BOCOR row          |                     |

#### 14.4.5.1 Enter Interactive Mode (CMD\_INIT)

This command allows launching the Boot Interactive command mode of the Boot ROM.

To reach interactive mode, the debugger will trigger a "cold plugging" sequence as described in DSU chapter.

**Important:** Debugger must not clear DSU.STATUSA.BREXT bit before clearing DSU.STATUSA.CRSTEXT bit.

When CRSTEXT is cleared, CPU starts Boot ROM Interactive mode execution. After a small delay (5ms advised), the debugger must check if the Boot ROM has not flagged any errors by checking the BCC1D bit in DSU.STATUSB register.

If no error is reported, the debugger writes the CMD\_INIT command to DSU.BCC0 register to request Boot ROM Interactive mode entry. When command is successful, Boot ROM will place the "SIG\_COMM" status in DSU.BCC1 register.

#### **Related Links**

19.6.2.6 Peripheral Clock Masking

#### 19.6.2.2 Enabling, Disabling, and Resetting

The MCLK module is always enabled and cannot be reset.

#### 19.6.2.3 Selecting the Main Clock Source

Refer to the Generic Clock Controller description for details on how to configure the clock source of the GCLK\_MAIN clock.

Refer to the Oscillators Controller (OSCCTRL) description for details on how to configure the clock source of the CLK\_DFLLULP clock.

#### **Related Links**

18. GCLK - Generic Clock Controller

#### 19.6.2.4 Selecting the Synchronous Clock Division Ratio

The main clock CLK\_MAIN feeds an 8-bit prescaler, which can be used to generate the synchronous clocks. By default, the synchronous clocks run on the undivided main clock. The user can select a prescaler division for the CPU clock domain by writing the Division (DIV) bits in the CPU Clock Division register CPUDIV, resulting in a CPU clock domain frequency determined by this equation:

$$f_{CPU} = \frac{f_{main}}{CPUDIV}$$

If the application attempts to write forbidden values in CPUDIV register, registers are written but these bad values are not used and a violation is reported to the PAC module.

Division bits (DIV) can be written without halting or disabling peripheral modules. Writing DIV bits allows a new clock setting to be written to all synchronous clocks belonging to the corresponding clock domain at the same time.

#### Name: SYNCBUSY Offset: 0x0C 0x0000000 Reset: Property: \_ Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset 15 12 Bit 14 13 11 10 9 8 Access Reset 7 6 5 3 0 Bit 4 2 1 ENABLE SWRST R R Access Reset 0 0

#### 20.8.8 Synchronization Busy

#### Bit 1 - ENABLE Enable

This bit is cleared when the synchronization of CTRLA.ENABLE is complete.

This bit is set when the synchronization of CTRLA.ENABLE is started.

#### Bit 0 – SWRST Synchronization Busy

This bit is cleared when the synchronization of CTRLA.SWRST is complete.

This bit is set when the synchronization of CTRLA.SWRST is started.

#### RTC – Real-Time Counter

| Offset           | Name      | Bit Pos. |            |              |       |         |          |         |         |         |  |

|------------------|-----------|----------|------------|--------------|-------|---------|----------|---------|---------|---------|--|

|                  |           | 15:8     |            | ,            |       | GP      | [15:8]   |         |         |         |  |

|                  |           | 23:16    |            |              |       | GP[     | 23:16]   |         |         |         |  |

|                  |           | 31:24    |            |              |       | GP[     | 31:24]   |         |         |         |  |

| 0x48<br><br>0x5F | Reserved  |          |            |              |       |         |          |         |         |         |  |

|                  |           | 7:0      | IN3A0      | CT[1:0]      | IN2AC | CT[1:0] | IN1AC    | CT[1:0] | IN0AC   | CT[1:0] |  |

| 0x60             | TAMPCTRL  | 15:8     |            |              |       |         |          |         |         |         |  |

| 0,00             | TAMPETRE  | 23:16    |            |              |       |         | TAMLVL3  | TAMLVL2 | TAMLVL1 | TAMLVL0 |  |

|                  |           | 31:24    |            |              |       |         | DEBNC3   | DEBNC2  | DEBNC1  | DEBNC0  |  |

|                  |           | 7:0      | COUNT[7:0] |              |       |         |          |         |         |         |  |

| 0x64             | TIMESTAMP | 15:8     |            | COUNT[15:8]  |       |         |          |         |         |         |  |

| 0,001            |           | 23:16    |            | COUNT[23:16] |       |         |          |         |         |         |  |

|                  |           | 31:24    |            |              |       | COUN    | T[31:24] |         |         |         |  |

|                  |           | 7:0      |            |              |       |         | TAMPID3  | TAMPID2 | TAMPID1 | TAMPID0 |  |

| 0x68             | TAMPID    | 15:8     |            |              |       |         |          |         |         |         |  |

| 0,000            |           | 23:16    |            |              |       |         |          |         |         |         |  |

|                  |           | 31:24    | TAMPEVT    |              |       |         |          |         |         |         |  |

|                  |           | 7:0      |            |              |       |         | ALSI3    | ALSI2   | ALSI1   | ALSI0   |  |

| 0x6C             | TAMPCTRLB | 15:8     |            |              |       |         |          |         |         |         |  |

|                  |           | 23:16    |            |              |       |         |          |         |         |         |  |

|                  |           | 31:24    |            |              |       |         |          |         |         |         |  |

#### 27.8 Register Description - Mode 0 - 32-Bit Counter

This Register Description section is valid if the RTC is in COUNT32 mode (CTRLA.MODE=0).

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 27.10.17 Tamper Control B

| Name:     | TAMPCTRLB                              |

|-----------|----------------------------------------|

| Offset:   | 0x6C                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31 | 30 | 29 | 28 | 27    | 26    | 25    | 24    |

|--------|----|----|----|----|-------|-------|-------|-------|

|        |    |    |    |    |       |       |       |       |

| Access |    |    |    |    |       |       |       |       |

| Reset  |    |    |    |    |       |       |       |       |

|        |    |    |    |    |       |       |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19    | 18    | 17    | 16    |

|        |    |    |    |    |       |       |       |       |

| Access |    |    |    |    |       |       |       |       |

| Reset  |    |    |    |    |       |       |       |       |

|        |    |    |    |    |       |       |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11    | 10    | 9     | 8     |

|        |    |    |    |    |       |       |       |       |

| Access |    |    |    |    |       |       |       |       |

| Reset  |    |    |    |    |       |       |       |       |

|        |    |    |    |    |       |       |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3     | 2     | 1     | 0     |

|        |    |    |    |    | ALSI3 | ALSI2 | ALSI1 | ALSI0 |

| Access |    |    |    |    | R/W   | R/W   | R/W   | R/W   |

| Reset  |    |    |    |    | 0     | 0     | 0     | 0     |

#### Bits 0, 1, 2, 3 - ALSI Active Layer Internal Select n

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | Active layer Protection is monitoring the RTC signal using INn and OUTn tamper pins |

| 1     | Active layer Protection is monitoring the RTC signal on the TrustRAM shield         |

#### 28.10.1 Block Transfer Control

| Name:     | BTCTRL |

|-----------|--------|

| Offset:   | 0x00   |

| Property: | -      |

The BTCTRL register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 15                           | 14 | 13     | 12     | 11       | 10    | 9       | 8     |

|--------|------------------------------|----|--------|--------|----------|-------|---------|-------|

|        | STEPSIZE[2:0] STEPSEL DSTINC |    | SRCINC | BEATS  | IZE[1:0] |       |         |       |

| Access |                              |    |        |        |          |       |         |       |

| Reset  |                              |    |        |        |          |       |         |       |

|        |                              |    |        |        |          |       |         |       |

| Bit    | 7                            | 6  | 5      | 4      | 3        | 2     | 1       | 0     |

|        |                              |    |        | BLOCKA | ACT[1:0] | EVOSI | EL[1:0] | VALID |

| Access |                              | •  |        |        |          |       |         | ••    |

Reset

#### Bits 15:13 – STEPSIZE[2:0] Address Increment Step Size

These bits select the address increment step size. The setting apply to source or destination address, depending on STEPSEL setting.

| Value | Name | Description                                  |

|-------|------|----------------------------------------------|

| 0x0   | X1   | Next ADDR = ADDR + (Beat size in byte) * 1   |

| 0x1   | X2   | Next ADDR = ADDR + (Beat size in byte) * 2   |

| 0x2   | X4   | Next ADDR = ADDR + (Beat size in byte) * 4   |

| 0x3   | X8   | Next ADDR = ADDR + (Beat size in byte) * 8   |

| 0x4   | X16  | Next ADDR = ADDR + (Beat size in byte) * 16  |

| 0x5   | X32  | Next ADDR = ADDR + (Beat size in byte) * 32  |

| 0x6   | X64  | Next ADDR = ADDR + (Beat size in byte) * 64  |

| 0x7   | X128 | Next ADDR = ADDR + (Beat size in byte) * 128 |

#### Bit 12 – STEPSEL Step Selection

This bit selects if source or destination addresses are using the step size settings.

| Value | Name | Description                                         |

|-------|------|-----------------------------------------------------|

| 0x0   | DST  | Step size settings apply to the destination address |

| 0x1   | SRC  | Step size settings apply to the source address      |

#### Bit 11 – DSTINC Destination Address Increment Enable

Writing a '0' to this bit will disable the destination address incrementation. The address will be kept fixed during the data transfer.

Writing a '1' to this bit will enable the destination address incrementation. By default, the destination address is incremented by 1. If the STEPSEL bit is cleared, flexible step-size settings are available in the STEPSIZE register.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Destination Address Increment is disabled. |

| 1     | The Destination Address Increment is enabled.  |

#### 29.6.10 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in control register (CTRLA.SWRST)

- Enable bit in control register (CTRLA.ENABLE)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

### SAM L10/L11 Family TRAM - TrustRAM

| Offset | Name       | Bit Pos. |            |  |      |                |  |  |  |

|--------|------------|----------|------------|--|------|----------------|--|--|--|

|        | 01FC RAM63 | 7:0      |            |  | DATA | <b>A</b> [7:0] |  |  |  |

| 0.0150 |            | 15:8     | DATA[15:8] |  |      |                |  |  |  |

| UXUIFC |            | 23:16    |            |  | DATA | [23:16]        |  |  |  |

|        |            | 31:24    |            |  | DATA | [31:24]        |  |  |  |

#### 31.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Refer to PAC - Peripheral Access Controller and 39.6.6 Synchronization for details.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

TRAM - TrustRAM

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 33.7.3 Priority Control

| Name:     | PRICTRL                      |

|-----------|------------------------------|

| Offset:   | 0x08                         |

| Reset:    | 0x00                         |

| Property: | PAC Write-Protection, Secure |

|           |                              |

| Bit    | 7        | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|--------|----------|---|---|---|---|---|---------|---------|

|        | RREN     |   |   |   |   |   | PRI     | [1:0]   |

| Access | RW/RW/RW |   |   |   |   |   | RW/-/RW | RW/-/RW |

| Reset  | 0        |   |   |   |   |   | 0       | 0       |

#### Bit 7 – RREN Round-Robin Scheduling Enable

For details on scheduling schemes, refer to Interrupt Status and Interrupts Arbitration

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Static scheduling scheme for channels with level priority      |

| 1     | Round-robin scheduling scheme for channels with level priority |

#### Bits 1:0 - PRI[1:0] Channel Priority Number

When round-robin arbitration is enabled (PRICTRL.RREN=1) for priority level, this register holds the channel number of the last EVSYS channel being granted access as the active channel with priority level. The value of this bit group is updated each time the INTPEND or any of CHINTFLAG registers are written.

When static arbitration is enabled (PRICTRL.RREN=0) for priority level, and the value of this bit group is nonzero, it will not affect the static priority scheme.

This bit group is not reset when round-robin scheduling gets disabled (PRICTRL.RREN written to zero).

#### 36.8.9 Address

| Name:     | ADDR                                   |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31  | 30  | 29  | 28    | 27       | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|----------|-----|-----|-----|

|        |     |     |     |       |          |     |     |     |

| Access |     |     |     |       |          |     |     |     |

| Reset  |     |     |     |       |          |     |     |     |

|        |     |     |     |       |          |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19       | 18  | 17  | 16  |

|        |     |     |     | ADDRM | ASK[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

|        |     |     |     |       |          |     |     |     |

| Access |     |     |     |       |          |     |     |     |

| Reset  |     |     |     |       |          |     |     |     |

|        |     |     |     |       |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

|        |     |     |     | ADD   | R[7:0]   |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

#### Bits 23:16 – ADDRMASK[7:0] Address Mask

These bits hold the address mask when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

#### Bits 7:0 – ADDR[7:0] Address

These bits hold the address when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

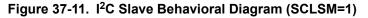

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit is sent as shown in Slave Behavioral Diagram (SCLSM=1). This strategy can be used when it is not necessary to check DATA before acknowledging. For master reads, an address and data interrupt will be issued simultaneously after the address acknowledge. However, for master writes, the first data interrupt will be seen after the first data byte has been received by the slave and the acknowledge bit has been sent to the master.

**Note:** For I<sup>2</sup>C High-speed mode (*Hs*), SCLSM=1 is required.

#### 37.6.2.5.1 Receiving Address Packets (SCLSM=0)

When CTRLA.SCLSM=0, the I2C slave stretches the SCL line according to Figure 37-10. When the I<sup>2</sup>C slave is properly configured, it will wait for a start condition.

When a start condition is detected, the successive address packet will be received and checked by the address match logic. If the received address is not a match, the packet will be rejected, and the I<sup>2</sup>C slave will wait for a new start condition. If the received address is a match, the Address Match bit in the Interrupt Flag register (INTFLAG.AMATCH) will be set.

SCL will be stretched until the I<sup>2</sup>C slave clears INTFLAG.AMATCH. As the I<sup>2</sup>C slave holds the clock by forcing SCL low, the software has unlimited time to respond.

The direction of a transaction is determined by reading the Read / Write Direction bit in the Status register (STATUS.DIR). This bit will be updated only when a valid address packet is received.

If the Transmit Collision bit in the Status register (STATUS.COLL) is set, this indicates that the last packet addressed to the I<sup>2</sup>C slave had a packet collision. A collision causes the SDA and SCL lines to be released without any notification to software. Therefore, the next AMATCH interrupt is the first indication of the previous packet's collision. Collisions are intended to follow the SMBus Address Resolution Protocol (ARP).

After the address packet has been received from the I<sup>2</sup>C master, one of two cases will arise based on transfer direction.

© 2018 Microchip Technology Inc.

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to *Peripherals Security Attribution* for more information.

### **OPAMP – Operational Amplifier Controller**

| Value | OPAMPx  | Name      | Description                 |

|-------|---------|-----------|-----------------------------|

| 0x0   | x=0,1,2 | OAxPOS    | OPAMPx Positive Input       |

| 0x1   | x=0,1,2 | OAxTAP    | OPAMPx Resistor Ladder Taps |

| 0x2   | x=0,1,2 | REFERENCE | REFERENCE[DAC/REFBUF]       |

| 0x3   | x=0,1,2 | GND       | Ground                      |

| 0x4   | x=0     | Reserved  |                             |

|       | x=1     | OA0OUT    | OPAMP0 output               |

|       | x=2     | OA1OUT    | OPAMP1 output               |

| 0x5   | x=0,1   | Reserved  |                             |

|       | x=2     | OA0POS    | OPAMP0 Positive Input       |

| 0x6   | x=0,1   | Reserved  |                             |

|       | x=2     | OA1POS    | OPAMP1 Positive Input       |

| 0x7   | x=0,1   | Reserved  |                             |

|       | x=2     | OA0TAP    | OPAMP0 Resistor Ladder Taps |

| 0x8   | x=0,1   | Reserved  |                             |

|       | x=2     | RES3TAP   |                             |

#### Bits 15:13 – POTMUX[2:0] Potentiometer selection

Resistor selection bits control a numeric potentiometer with eight fixed values.

| Value | R1  | R2  |

|-------|-----|-----|

| 0x0   | 14R | 2R  |

| 0x1   | 12R | 4R  |

| 0x2   | 8R  | 8R  |

| 0x3   | 6R  | 10R |

| 0x4   | 4R  | 12R |

| 0x5   | 3R  | 13R |

| 0x6   | 2R  | 14R |

| 0x7   | R   | 15R |

#### Bits 12:10 – RES1MUX[2:0] Resistor 1 Mux

These bits select the connection of R1 resistor of the potentiometer.

| Value | OPAMPx  | Name   | Description           |

|-------|---------|--------|-----------------------|

| 0x0   | x=0,1,2 | OAxPOS | OPAMPx Positive Input |

| 0x1   | x=0,1,2 | OAxNEG | OPAMPx Negative Input |

#### Bit 1 – RES1EN Resistor 1 Enable

RES1EN = 1 is required in order to provide DAC/REFBUF to POSMUX, NEGMUX and RES1MUX.

| Value | Description                   |

|-------|-------------------------------|

| 0     | R1 disconnected from RES1MUX. |

| 1     | R1 connected to RES1MUX.      |

#### Bit 0 – RES2OUT Resistor ladder To Output

RES2OUT switch can only be closed if all OPAMPs are enabled.

| Value | Description    |

|-------|----------------|

| 0     | Swith open.    |

| 1     | Switch closed. |

**Electrical Characteristics**

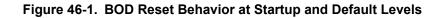

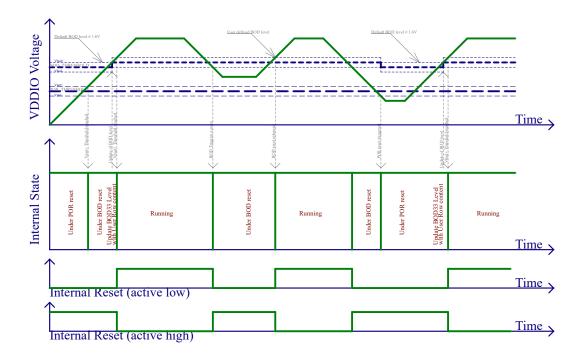

#### 46.11.3 Brown-Out Detectors (BOD) Characteristics Table 46-20. BOD33 Characteristics (BOD33.VREFSEL = 0)

| Symbol                            | Parameters                                                | Conditions                   | Min. | Тур. | Max. | Unit |

|-----------------------------------|-----------------------------------------------------------|------------------------------|------|------|------|------|

| V <sub>BOD+</sub> <sup>(2)</sup>  | BOD33 high<br>threshold level                             | BOD33.LEVEL = 6              | 1.66 | 1.68 | 1.70 | V    |

|                                   |                                                           | BOD33.LEVEL = 7              | 1.70 | 1.72 | 1.74 |      |

|                                   |                                                           | BOD33.LEVEL = 39             | 2.79 | 2.84 | 2.89 |      |

|                                   |                                                           | BOD33.LEVEL = 48             | 3.12 | 3.18 | 3.20 |      |

| V <sub>BOD-</sub> /               | BOD33 low<br>threshold level                              | BOD33.LEVEL = 6              | 1.61 | 1.64 | 1.65 | V    |

| V <sub>BOD</sub> <sup>(2)</sup>   |                                                           | BOD33.LEVEL = 7              | 1.65 | 1.67 | 1.68 |      |

|                                   |                                                           | BOD33.LEVEL = 39             | 2.74 | 2.78 | 2.80 |      |

|                                   |                                                           | BOD33.LEVEL = 48             | 3.04 | 3.09 | 3.11 |      |

| -                                 | Step size                                                 | -                            | -    | 34   | -    | mV   |

| V <sub>HYS</sub>                  | Hysteresis<br>(V <sub>BOD+</sub> -<br>V <sub>BOD-</sub> ) | BOD33.LEVEL = 0x0<br>to 0x3F | 40   | -    | 180  | mV   |

| T <sub>START</sub> <sup>(1)</sup> | Startup time                                              | time from enable to RDY      | -    | 3.2  | -    | μs   |

#### **Electrical Characteristics**

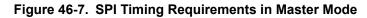

#### **Maximum SPI Frequency**

Master Mode

$f_{SCKmax} = 1/2^*(t_{MIS} + t_{valid})$ , where  $t_{valid}$  is the slave time response to output data after detecting an SCK edge. For a non-volatile memory with  $t_{valid} = 12$ ns Max,  $f_{SPCKMax} = 9.8$  MHz @ VDDIO > 2.7V

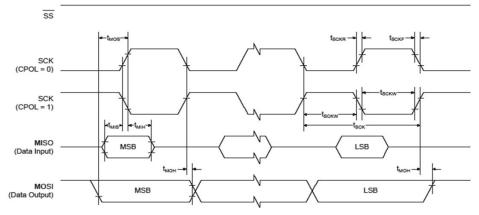

Slave Mode

$f_{SCKmax} = 1/2^*(t_{SOV} + t_{su})$ , where  $t_{su}$  is the setup time from the master before sampling data. With a perfect master ( $t_{su}$ =0),  $f_{SPCKMax}$  = 16.3MHz @ VDDIO > 2.7V