#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d15a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 11.4.  | SRAM Quality of Service              | 52   |

|-----|--------|--------------------------------------|------|

| 12. | Perip  | pherals Configuration Summary        | .54  |

| 13. | SAM    | L11 Security Features                | .57  |

|     | 13.1.  | Features                             | . 57 |

|     | 13.2.  | ARM TrustZone Technology for ARMv8-M | 58   |

|     | 13.3.  | Crypto Acceleration                  | 69   |

|     | 13.4.  | True Random Number Generator (TRNG)  | 72   |

|     | 13.5.  | Secure Boot                          | 72   |

|     | 13.6.  | Secure Pin Multiplexing on SERCOM    | 72   |

|     | 13.7.  | Data Flash                           | 72   |

|     | 13.8.  | TrustRAM (TRAM)                      | 72   |

| 14. | Boot   | ROM                                  | .73  |

|     | 14.1.  | Features                             | . 73 |

|     | 14.2.  | Block Diagram                        | 74   |

|     |        | Product Dependencies                 |      |

|     |        | Functional Description               |      |

| 4 - |        |                                      |      |

| 15. |        | - Peripheral Access Controller       |      |

|     |        | Overview                             |      |

|     |        | Features                             |      |

|     |        | Block Diagram                        |      |

|     |        | Product Dependencies                 |      |

|     |        | Functional Description               |      |

|     |        | Register Summary                     |      |

|     | 15.7.  | Register Description                 | 103  |

| 16. | DSU    | - Device Service Unit 1              | 27   |

|     | 16.1.  | Overview                             | 127  |

|     | 16.2.  | Features                             | 127  |

|     | 16.3.  | Block Diagram                        | 128  |

|     | 16.4.  | Signal Description                   | 128  |

|     | 16.5.  | Product Dependencies                 | 128  |

|     | 16.6.  | Debug Operation                      | 130  |

|     | 16.7.  | Programming                          | 131  |

|     | 16.8.  | Security Enforcement                 | 132  |

|     | 16.9.  | Device Identification                | 134  |

|     | 16.10  | . Functional Description             | 135  |

|     | 16.11. | Register Summary                     | 141  |

|     | 16.12  | Register Description                 | 143  |

| 17. | Cloc   | k System1                            | 172  |

|     | 17.1.  | Clock Distribution                   | 172  |

|     | 17.2.  | Synchronous and Asynchronous Clocks  | 173  |

|     | 17.3.  | Register Synchronization             | 174  |

|     | 17.4.  | Enabling a Peripheral                | 177  |

# Table 4-7. Secure Pin Multiplexing on SERCOM Pins

| Pin Name | Secure Pin Multiplexing Pad Name |

|----------|----------------------------------|

| PA16     | SERCOM1/PAD[0]                   |

| PA17     | SERCOM1/PAD[1]                   |

| PA18     | SERCOM1/PAD[2]                   |

| PA19     | SERCOM1/PAD[3]                   |

# 4.5 General Purpose I/O (GPIO) Clusters

# Table 4-8. GPIO Clusters

| Package | Cluster | GPIO                                                                                 | Supply Pins Connected to the Cluster |

|---------|---------|--------------------------------------------------------------------------------------|--------------------------------------|

| 32-pin  | 1       | PA00 PA01 PA02 PA03 PA04 PA05 PA06 PA07                                              | V <sub>DDANA</sub> /GNDANA           |

|         | 2       | PA08 PA09 PA10 PA11 PA14 PA15 PA16 PA17 PA18 PA19 PA22 PA23 PA24 PA25 PA27 PA30 PA31 | V <sub>DDIO</sub> /GND               |

| 24-pin  | 1       | PA00 PA01 PA02 PA03 PA04 PA05                                                        | V <sub>DDANA</sub> /GND              |

|         | 2       | PA08 PA14 PA15 PA16 PA17 PA18 PA19 PA22 PA23 PA30 PA31                               | V <sub>DDIO</sub> /GND               |

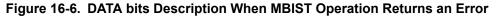

In this mode, the MBIST algorithm is paused when an error is detected. In such a situation, only STATUSA.FAIL is asserted. The state machine waits for user to clear STATUSA.FAIL by writing a '1' in STATUSA.FAIL to resume. Prior to resuming, user can read the DATA and ADDR registers to locate the fault.

#### 4. Locating Faults

If the test stops with STATUSA.FAIL set, one or more bits failed the test. The test stops at the first detected error. The position of the failing bit can be found by reading the following registers:

- ADDR: Address of the word containing the failing bit

- DATA: contains data to identify which bit failed, and during which phase of the test it failed.

The DATA register will in this case contains the following bit groups:

• bit\_index: contains the bit number of the failing bit

• phase: indicates which phase of the test failed and the cause of the error, as listed in the following table.

#### Table 16-5. MBIST Operation Phases

| Phase | Test actions                                    |

|-------|-------------------------------------------------|

| 0     | Write all bits to zero. This phase cannot fail. |

| 1     | Read '0', write '1', increment address          |

| 2     | Read '1', write '0'                             |

| 3     | Read '0', write '1', decrement address          |

| 4     | Read '1', write '0', decrement address          |

| 5     | Read '0', write '1'                             |

| 6     | Read '1', write '0', decrement address          |

| 7     | Read all zeros. bit_index is not used           |

#### 18.6.3.3 Selecting the Clock Source for a Peripheral

When changing a peripheral clock source by writing to PCHCTRLm.GEN, the peripheral clock must be disabled before re-enabling it with the new clock source setting. This prevents glitches during the transition:

- 1. Disable the Peripheral Channel by writing PCHCTRLm.CHEN=0

- 2. Assert that PCHCTRLm.CHEN reads '0'

- 3. Change the source of the Peripheral Channel by writing PCHCTRLm.GEN

- 4. Re-enable the Peripheral Channel by writing PCHCTRLm.CHEN=1

### Related Links 18.8.4 PCHCTRLm

#### 18.6.3.4 Configuration Lock

The peripheral clock configuration can be locked for further write accesses by setting the Write Lock bit in the Peripheral Channel Control register PCHCTRLm.WRTLOCK=1). All writing to the PCHCTRLm register will be ignored. It can only be unlocked by a Power Reset.

The Generator source of a locked Peripheral Channel will be locked, too: The corresponding GENCTRLn register is locked, and can be unlocked only by a Power Reset.

There is one exception concerning the Generator 0. As it is used as GCLK\_MAIN, it cannot be locked. It is reset by any Reset and will start up in a known configuration. The software reset (CTRLA.SWRST) can not unlock the registers.

In case of an external Reset, the Generator source will be disabled. Even if the WRTLOCK bit is written to '1' the peripheral channels are disabled (PCHCTRLm.CHEN set to '0') until the Generator source is enabled again. Then, the PCHCTRLm.CHEN are set to '1' again.

### **Related Links**

18.8.1 CTRLA

#### 18.6.4 Additional Features

#### 18.6.4.1 Peripheral Clock Enable after Reset

The Generic Clock Controller must be able to provide a generic clock to some specific peripherals after a Reset. That means that the configuration of the Generators and Peripheral Channels after Reset is device-dependent.

Refer to GENCTRLn.SRC for details on GENCTRLn reset.

Refer to PCHCTRLm.SRC for details on PCHCTRLm reset.

#### 18.6.5 Sleep Mode Operation

#### 18.6.5.1 SleepWalking

The GCLK module supports the SleepWalking feature.

If the system is in a sleep mode where the Generic Clocks are stopped, a peripheral that needs its clock in order to execute a process must request it from the Generic Clock Controller.

The Generic Clock Controller receives this request, determines which Generic Clock Generator is involved and which clock source needs to be awakened. It then wakes up the respective clock source, enables the Generator and Peripheral Channel stages successively, and delivers the clock to the peripheral.

© 2018 Microchip Technology Inc.

#### 19.8.2 Interrupt Enable Clear

Name:INTENCLROffset:0x01Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | CKRDY |

| Access |   |   |   |   |   |   |   | R/W   |

| Reset  |   |   |   |   |   |   |   | 0     |

**Bit 0 – CKRDY** Clock Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Clock Ready Interrupt Enable bit and the corresponding interrupt request.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Clock Ready interrupt is enabled and will generate an interrupt request when the Clock |

|       | Ready Interrupt Flag is set.                                                               |

| 1     | The Clock Ready interrupt is disabled.                                                     |

# SAM L10/L11 Family

# **FREQM – Frequency Meter**

FREQM is reset. See 20.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the 20.8.6 INTFLAG register to determine which interrupt condition is present.

This interrupt is a synchronous wake-up source.

Note that interrupts must be globally enabled for interrupt requests to be generated.

#### 20.6.5 Events

Not applicable.

#### 20.6.6 Sleep Mode Operation

The FREQM will continue to operate in idle sleep mode where the selected source clock is running. The FREQM's interrupts can be used to wake up the device from idle sleep mode.

For lowest chip power consumption in sleep modes, FREQM should be disabled before entering a sleep mode.

#### **Related Links**

22. PM – Power Manager

#### 20.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits and registers are write-synchronized:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

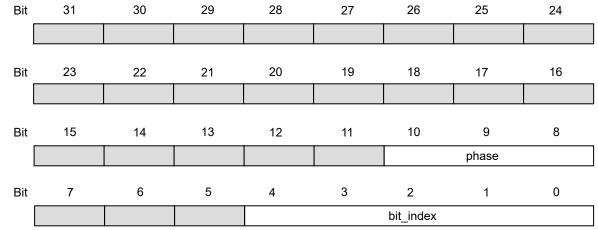

Dynamic SleepWalking based on event is illustrated in the following example:

#### Figure 22-8. Dynamic SleepWalking based on Event: AC Periodic Comparison

The Analog Comparator (AC) peripheral is used in single shot mode to monitor voltage levels on input pins. A comparator interrupt, based on the AC peripheral configuration, is generated to wake up the device. In the GCLK module, the AC generic clock (GCLK\_AC) source is routed a 32.768kHz oscillator (for low power applications, OSC32KULP is recommended). RTC and EVSYS modules are configured to generate periodic events to the AC. To make the comparator continue to run in standby sleep mode, the RUNSTDBY bit is written to '1'. To enable the dynamic SleepWalking for PDSW power domain, STDBYCFG.PDSW must be written to '1'.

*Entering standby mode*: The Power Manager sets the PDSW power domain in retention state. The AC comparators, COMPx, are OFF. The GCLK\_AC clock is stopped. The VDDCORE is supplied by the low power regulator.

*Dynamic SleepWalking*: The RTC event (RTC\_PERX) is routed by the Event System to the Analog Comparator to trigger a single-shot measurement. This event is detected by the Power Manager, which sets the PDSW power domain to active state and starts the main voltage regulator.

After enabling the AC comparator and starting the GCLK\_AC, the single-shot measurement can be performed during Sleep mode (sleepwalking task), refer to 42.6.14.2 Single-Shot Measurement during Sleep for details. At the end of the conversion, if conditions to generate an interrupt are not met, the GCLK\_AC clock is stopped again, as well as the AC comparator.

© 2018 Microchip Technology Inc.

# 26. WDT – Watchdog Timer

# 26.1 Overview

The Watchdog Timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is configured to a predefined time-out period, and is constantly running when enabled. If the WDT is not cleared within the time-out period, it will issue a system reset. An early-warning interrupt is available to indicate an upcoming watchdog time-out condition.

The window mode makes it possible to define a time slot (or window) inside the total time-out period during which the WDT must be cleared. If the WDT is cleared outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes the WDT to be cleared frequently.

When enabled, the WDT will run in active mode and all sleep modes. It is asynchronous and runs from a CPU-independent clock source. The WDT will continue operation and issue a system reset or interrupt even if the main clocks fail.

# 26.2 Features

- Issues a system reset if the Watchdog Timer is not cleared before its time-out period

- Early Warning interrupt generation

- Asynchronous operation from dedicated oscillator

- Two types of operation

- Normal

- Window mode

- Selectable time-out periods

- From 8 cycles to 16,384 cycles in Normal mode

- From 16 cycles to 32,768 cycles in Window mode

- Always-On capability

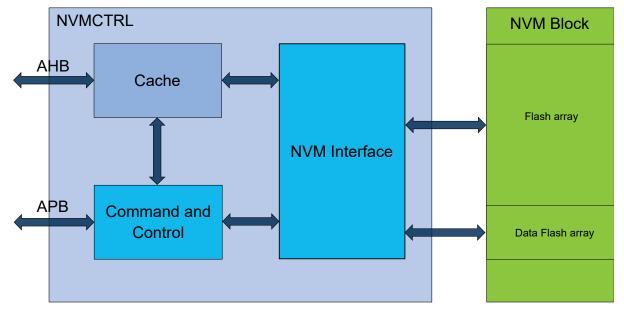

### 30.3 Block Diagram

Figure 30-1. Block Diagram

# 30.4 Signal Description

Not applicable.

# 30.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described in the following sections.

#### 30.5.1 Power Management

The NVMCTRL will continue to operate in any sleep mode where the selected source clock is running. The NVMCTRL interrupts can be used to wake up the device from sleep modes.

The Power Manager will automatically put the NVM block into a low-power state when entering sleep mode. This is based on the Control B register (CTRLB) SLEEPPRM bit setting. Refer to the 30.8.2 CTRLB.SLEEPPRM register description for more details. The NVM block goes into low-power mode automatically when the device enters STANDBY mode regardless of SLEEPPRM. The NVM Page Buffer is lost when the NVM goes into low power mode therefore a write command must be issued prior entering the NVM low power mode. NVMCTRL SLEEPPRM can be disabled to avoid such loss when the CPU goes into sleep except if the device goes into STANDBY mode for which there is no way to retain the Page Buffer.

#### **Related Links**

22. PM – Power Manager

### 30.5.2 Clocks

Two synchronous clocks are used by the NVMCTRL. One is provided by the AHB bus (CLK\_NVMCTRL\_AHB) and the other is provided by the APB bus (CLK\_NVMCTRL\_APB). For higher

#### 30.8.3 Control C

| Name:     | CTRLC                                  |

|-----------|----------------------------------------|

| Offset:   | 0x08                                   |

| Reset:    | 0x01                                   |

| Property: | PAC Write-Protection, Write-Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0         |

|--------|---|---|---|---|---|---|---|-----------|

|        |   |   |   |   |   |   |   | MANW      |

| Access |   |   |   |   |   |   |   | RW/RW*/RW |

| Reset  |   |   |   |   |   |   |   | 1         |

#### Bit 0 – MANW Manual Write

| Value | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 0     | Writing to the last word in the page buffer will initiate a write operation to the page addressed |

|       | by the last write operation. This includes writes to FLASH, Data FLASH and AUX FLASH.             |

| 1     | Write commands must be issued through the CTRLA.CMD register.                                     |

# 33. EVSYS – Event System

### 33.1 Overview

The Event System (EVSYS) allows autonomous, low-latency and configurable communication between peripherals.

Several peripherals can be configured to generate and/or respond to signals known as events. The exact condition to generate an event, or the action taken upon receiving an event, is specific to each peripheral. Peripherals that respond to events are called event users. Peripherals that generate events are called event generators. A peripheral can have one or more event generators and can have one or more event users. Channels and event users can be defined as secured or non-secured, where secured channels or event users can only be handled by secure code.

Communication is made without CPU intervention and without consuming system resources such as bus or RAM bandwidth. This reduces the load on the CPU and other system resources, compared to a traditional interrupt-based system.

# 33.2 Features

- 8 configurable event channels:

- All channels can be connected to any event generator

- All channels provide a pure asynchronous path

- 4 channels (CHANNEL0 to CHANNEL3) provide a resynchronized or synchronous path using their dedicated generic clock (GCLK\_EVSYS\_CHANNEL\_n)

- 49 event generators.

- 23 event users.

- Configurable edge detector.

- Peripherals can be event generators, event users, or both.

- SleepWalking and interrupt for operation in sleep modes.

- Software event generation.

- Each event user can choose which channel to respond to.

- Optional Static or Round-Robin interrupt priority arbitration.

- Each channel and each event user can be configured as secured or non-secured (SAM L11).

#### 33.7.3 Priority Control

| Name:     | PRICTRL                      |

|-----------|------------------------------|

| Offset:   | 0x08                         |

| Reset:    | 0x00                         |

| Property: | PAC Write-Protection, Secure |

|           |                              |

| Bit    | 7        | 6 | 5 | 4 | 3 | 2 | 1        | 0       |

|--------|----------|---|---|---|---|---|----------|---------|

|        | RREN     |   |   |   |   |   | PRI[1:0] |         |

| Access | RW/RW/RW |   |   |   |   |   | RW/-/RW  | RW/-/RW |

| Reset  | 0        |   |   |   |   |   | 0        | 0       |

#### Bit 7 – RREN Round-Robin Scheduling Enable

For details on scheduling schemes, refer to Interrupt Status and Interrupts Arbitration

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Static scheduling scheme for channels with level priority      |

| 1     | Round-robin scheduling scheme for channels with level priority |

#### Bits 1:0 - PRI[1:0] Channel Priority Number

When round-robin arbitration is enabled (PRICTRL.RREN=1) for priority level, this register holds the channel number of the last EVSYS channel being granted access as the active channel with priority level. The value of this bit group is updated each time the INTPEND or any of CHINTFLAG registers are written.

When static arbitration is enabled (PRICTRL.RREN=0) for priority level, and the value of this bit group is nonzero, it will not affect the static priority scheme.

This bit group is not reset when round-robin scheduling gets disabled (PRICTRL.RREN written to zero).

#### 33.7.8 Channel n Control

| Name:     | CHANNEL                          |

|-----------|----------------------------------|

| Offset:   | 0x20 + n*0x08 [n=07]             |

| Reset:    | 0x00008000                       |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding channel (CHANNELx) is set as Non-Secured in the NONSECCHAN register.

This register allows the user to configure channel n. To write to this register, do a single, 32-bit write of all the configuration data.

| Bit    | 31        | 30        | 29         | 28        | 27          | 26        | 25        | 24        |

|--------|-----------|-----------|------------|-----------|-------------|-----------|-----------|-----------|

|        |           |           |            |           |             |           |           |           |

| Access |           |           |            |           |             |           |           |           |

| Reset  |           |           |            |           |             |           |           |           |

|        |           |           |            |           |             |           |           |           |

| Bit    | 23        | 22        | 21         | 20        | 19          | 18        | 17        | 16        |

|        |           |           |            |           |             |           |           |           |

| Access |           |           |            |           |             |           |           |           |

| Reset  |           |           |            |           |             |           |           |           |

|        |           |           |            |           |             |           |           |           |

| Bit    | 15        | 14        | 13         | 12        | 11          | 10        | 9         | 8         |

|        | ONDEMAND  | RUNSTDBY  |            |           | EDGSEL[1:0] |           | PATH[1:0] |           |

| Access | RW/RW*/RW | RW/RW*/RW |            |           | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 1         | 0         |            |           | 0           | 0         | 0         | 0         |

|        |           |           |            |           |             |           |           |           |

| Bit    | 7         | 6         | 5          | 4         | 3           | 2         | 1         | 0         |

|        |           |           | EVGEN[5:0] |           |             |           |           |           |

| Access |           |           | RW/RW*/RW  | RW/RW*/RW | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  |           |           | 0          | 0         | 0           | 0         | 0         | 0         |

#### Bit 15 – ONDEMAND Generic Clock On Demand

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock |

|       | source is enabled.                                                                       |

| 1     | Generic clock is requested on demand while an event is handled                           |

#### Bit 14 – RUNSTDBY Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                      |

| 1     | The channel is not stopped in standby sleep mode and depends on the |

|       | CHANNEL.ONDEMAND bit.                                               |

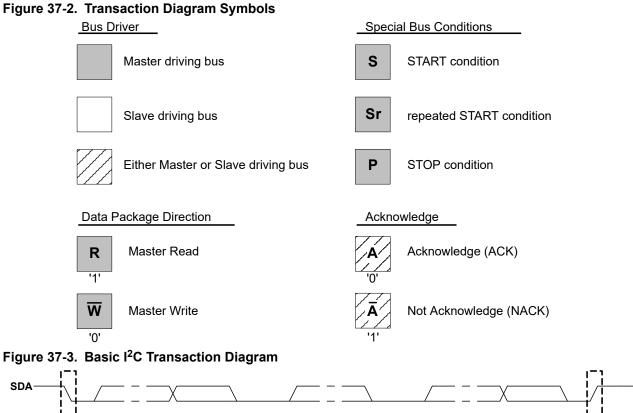

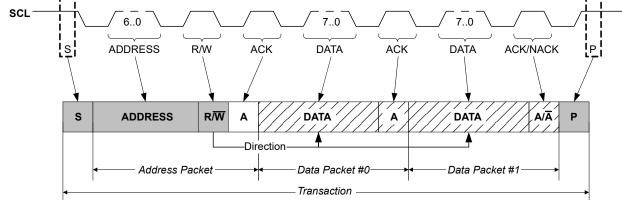

# SAM L10/L11 Family SERCOM I2C – SERCOM Inter-Integrated Circ...

### 37.6.2 Basic Operation

#### 37.6.2.1 Initialization

The following registers are enable-protected, meaning they can be written only when the I<sup>2</sup>C interface is disabled (CTRLA.ENABLE is '0'):

- Control A register (CTRLA), except Enable (CTRLA.ENABLE) and Software Reset (CTRLA.SWRST) bits

- Control B register (CTRLB), except Acknowledge Action (CTRLB.ACKACT) and Command (CTRLB.CMD) bits

- Baud register (BAUD)

- Address register (ADDR) in slave operation.

When the  $l^2C$  is enabled or is being enabled (CTRLA.ENABLE=1), writing to these registers will be discarded. If the  $l^2C$  is being disabled, writing to these registers will be completed after the disabling.

When a data packet is received or sent, INTFLAG.DRDY will be set. After receiving data, the I<sup>2</sup>C slave will send an acknowledge according to CTRLB.ACKACT.

#### Case 1: Data received

INTFLAG.DRDY is set, and SCL is held low, pending for SW interaction.

#### Case 2: Data sent

When a byte transmission is successfully completed, the INTFLAG.DRDY interrupt flag is set. If NACK is received, indicated by STATUS.RXNACK=1, the I<sup>2</sup>C slave must expect a stop or a repeated start to be received. The I<sup>2</sup>C slave must release the data line to allow the I<sup>2</sup>C master to generate a stop or repeated start. Upon detecting a stop condition, the Stop Received bit in the Interrupt Flag register (INTFLAG.PREC) will be set and the I<sup>2</sup>C slave will return to IDLE state.

#### 37.6.2.5.4 High-Speed Mode

When the I<sup>2</sup>C slave is configured in High-speed mode (*Hs*, CTRLA.SPEED=0x2) and CTRLA.SCLSM=1, switching between Full-speed and High-speed modes is automatic. When the slave recognizes a START followed by a master code transmission and a NACK, it automatically switches to High-speed mode and sets the High-speed status bit (STATUS.HS). The slave will then remain in High-speed mode until a STOP is received.

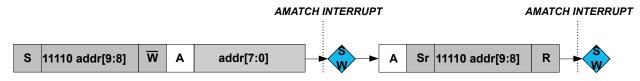

#### 37.6.2.5.5 10-Bit Addressing

When 10-bit addressing is enabled (ADDR.TENBITEN=1), the two address bytes following a START will be checked against the 10-bit slave address recognition. The first byte of the address will always be acknowledged, and the second byte will raise the address interrupt flag, see 10-bit Addressing.

If the transaction is a write, then the 10-bit address will be followed by *N* data bytes.

If the operation is a read, the 10-bit address will be followed by a repeated START and reception of '11110 ADDR[9:8] 1', and the second address interrupt will be received with the DIR bit set. The slave matches on the second address as it it was addressed by the previous 10-bit address.

#### Figure 37-12. 10-bit Addressing

#### 37.6.2.5.6 PMBus Group Command

When the PMBus Group Command bit in the CTRLB register is set (CTRLB.GCMD=1) and 7-bit addressing is used, INTFLAG.PREC will be set if the slave has been addressed since the last STOP condition. When CTRLB.GCMD=0, a STOP condition without address match will not be set INTFLAG.PREC.

The group command protocol is used to send commands to more than one device. The commands are sent in one continuous transmission with a single STOP condition at the end. When the STOP condition is detected by the slaves addressed during the group command, they all begin executing the command they received.

PMBus Group Command Example shows an example where this slave, bearing ADDRESS 1, is addressed after a repeated START condition. There can be multiple slaves addressed before and after this slave. Eventually, at the end of the group command, a single STOP is generated by the master. At this point a STOP interrupt is asserted.

# SAM L10/L11 Family TC – Timer/Counter

# 38.6.4 DMA Operation

The TC can generate the following DMA requests:

- Overflow (OVF): the request is set when an update condition (overflow, underflow or re-trigger) is detected, the request is cleared by hardware on DMA acknowledge.

- Match or Capture Channel x (MCx): for a compare channel, the request is set on each compare match detection, the request is cleared by hardware on DMA acknowledge. For a capture channel, the request is set when valid data is present in the CCx register, and cleared when CCx register is read.

#### 38.6.5 Interrupts

The TC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Match or Capture Channel x (MCx)

- Capture Overflow Error (ERR)

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the TC is reset. See INTFLAG for details on how to clear interrupt flags.

The TC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### 38.6.6 Events

The TC can generate the following output events:

- Overflow/Underflow (OVF)

- Match or Capture Channel x (MCx)

#### 41.6.2 Basic Operation

#### 41.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the ADC is disabled (CTRLA.ENABLE=0):

- Control B register (CTRLB)

- Reference Control register (REFCTRL)

- Event Control register (EVCTRL)

- Calibration register (CALIB)

Enable-protection is denoted by the "Enable-Protected" property in the register description.

#### 41.6.2.2 Enabling, Disabling and Resetting

The ADC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The ADC is disabled by writing CTRLA.ENABLE=0.

The ADC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the ADC, except DBGCTRL, will be reset to their initial state, and the ADC will be disabled. Refer to 41.8.1 CTRLA for details.

#### 41.6.2.3 Operation

In the most basic configuration, the ADC samples values from the configured internal or external sources (INPUTCTRL register). The rate of the conversion depends on the combination of the GCLK\_ADC frequency and the clock prescaler.

To convert analog values to digital values, the ADC needs to be initialized first, as described in the Initialization section. Data conversion can be started either manually by setting the Start bit in the Software Trigger register (SWTRIG.START=1), or automatically by configuring an automatic trigger to initiate the conversions. A free-running mode can be used to continuously convert an input channel. When using free-running mode the first conversion must be started, while subsequent conversions will start automatically at the end of previous conversions.

The result of the conversion is stored in the Result register (RESULT) overwriting the result from the previous conversion.

To avoid data loss if more than one channel is enabled, the conversion result must be read as soon as it is available (INTFLAG.RESRDY). Failing to do so will result in an overrun error condition, indicated by the OVERRUN bit in the Interrupt Flag Status and Clear register (INTFLAG.OVERRUN).

To enable one of the available interrupts sources, the corresponding bit in the Interrupt Enable Set register (INTENSET) must be written to '1'.

#### 41.6.2.4 Prescaler Selection

The ADC is clocked by GCLK\_ADC. There is also a prescaler in the ADC to enable conversion at lower clock rates. Refer to CTRLB for details on prescaler settings. Refer to 41.6.2.8 Conversion Timing and Sampling Rate for details on timing and sampling rate.

# AC – Analog Comparators

#### 42.8.13 Synchronization Busy

|        | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x20<br>0x00000000<br>Read-Only |    |           |           |         |        |       |

|--------|-----------------------------------------|---------------------------------------------|----|-----------|-----------|---------|--------|-------|

| Bit    | 31                                      | 30                                          | 29 | 28        | 27        | 26      | 25     | 24    |

|        |                                         |                                             |    |           |           |         |        |       |

| Access |                                         | ,                                           |    |           |           |         |        |       |

| Reset  |                                         |                                             |    |           |           |         |        |       |

|        |                                         |                                             |    |           |           |         |        |       |

| Bit    | 23                                      | 22                                          | 21 | 20        | 19        | 18      | 17     | 16    |

|        |                                         |                                             |    |           |           |         |        |       |

| Access |                                         |                                             |    |           |           |         |        |       |

| Reset  |                                         |                                             |    |           |           |         |        |       |

|        |                                         |                                             |    |           |           |         |        |       |

| Bit    | 15                                      | 14                                          | 13 | 12        | 11        | 10      | 9      | 8     |

|        |                                         |                                             |    |           |           |         |        |       |

| Access |                                         |                                             |    |           |           |         |        |       |

| Reset  |                                         |                                             |    |           |           |         |        |       |

|        |                                         |                                             |    |           |           |         |        |       |

| Bit    | 7                                       | 6                                           | 5  | 4         | 3         | 2       | 1      | 0     |

|        |                                         |                                             |    | COMPCTRLx | COMPCTRLx | WINCTRL | ENABLE | SWRST |

| Access |                                         |                                             |    | R         | R         | R       | R      | R     |

| Reset  |                                         |                                             |    | 0         | 0         | 0       | 0      | 0     |

#### Bits 4,3 – COMPCTRLx COMPCTRLx Synchronization Busy

This bit is cleared when the synchronization of the COMPCTRLx register between the clock domains is complete.

This bit is set when the synchronization of the COMPCTRLx register between clock domains is started.

#### Bit 2 – WINCTRL WINCTRL Synchronization Busy

This bit is cleared when the synchronization of the WINCTRL register between the clock domains is complete.

This bit is set when the synchronization of the WINCTRL register between clock domains is started.

#### **Bit 1 – ENABLE** Enable Synchronization Busy

This bit is cleared when the synchronization of the CTRLA.ENABLE bit between the clock domains is complete.

This bit is set when the synchronization of the CTRLA.ENABLE bit between clock domains is started.

#### Bit 0 – SWRST Software Reset Synchronization Busy

This bit is cleared when the synchronization of the CTRLA.SWRST bit between the clock domains is complete.

This bit is set when the synchronization of the CTRLA.SWRST bit between clock domains is started.

© 2018 Microchip Technology Inc.

# 53. Datasheet Revision History

**Note:** The datasheet revision is independent of the die revision (Revision bit in the Device Identification register of the Device Service Unit, DSU.DID.REVISION) and the device variant (last letter of the ordering number).

# 53.1 Rev A - 09/2017

This is the initial released version of the document.

# 53.2 Rev B - 6/2018

Added new documentation for Electrical Characteristics -125°C.

analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.