#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d15a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

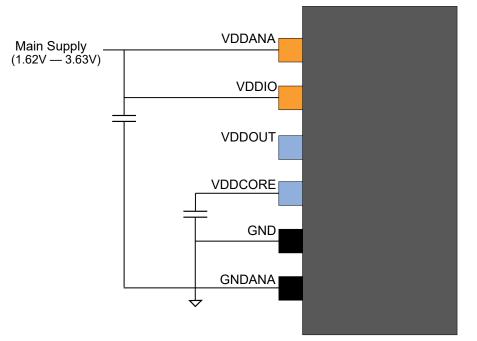

Figure 6-2. Power Supply Connections for Linear (LDO) Mode Only

Note: Refer to "Schematic Checklist" chapter for additional information.

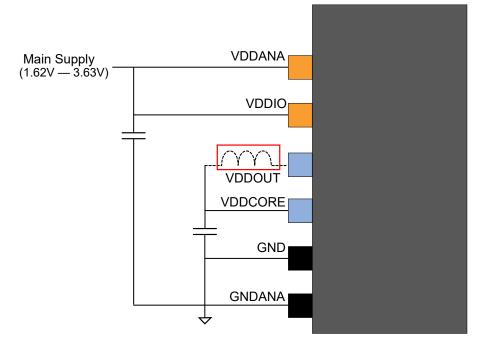

Figure 6-3. Power Supply Connections for Switching (BUCK) / Linear (LDO) Modes

**Note:** Refer to "Schematic Checklist" chapter for additional information.

#### Table 10-19. SAM L11 BOCOR Mapping

| Offset    | Bit<br>Pos. |          | Name       |       |       |  |  |

|-----------|-------------|----------|------------|-------|-------|--|--|

| 0x00      | 7:0         |          | Reserved   |       |       |  |  |

| 0x01      | 15:8        |          | BS         |       |       |  |  |

| 0x02      | 23:16       | Reserved | BNSC       |       |       |  |  |

| 0x03      | 31:24       |          | BOOTOPT    |       |       |  |  |

| 0x04      | 39:32       |          | BOOTPROT   |       |       |  |  |

| 0x05      | 47:40       |          | Reserved   |       |       |  |  |

| 0x06      | 55:48       |          | Reserved   | BCREN | BCWEN |  |  |

| 0x07      | 63:56       |          | Reserved   |       |       |  |  |

| 0x08-0x0B | 95:64       |          | BOCORCRC   |       |       |  |  |

| 0x0C-0x0F | 127:96      |          | ROMVERSION |       |       |  |  |

| 0x10-0x1F | 255:128     |          | CEKEY0     |       |       |  |  |

| 0x20-0x2F | 383:256     |          | CEKEY1     |       |       |  |  |

| 0x30-0x3F | 511:384     |          | CEKEY2     |       |       |  |  |

| 0x40-0x4F | 639:512     |          | CRCKEY     |       |       |  |  |

| 0x50-0x6F | 895:640     |          | BOOTKEY    |       |       |  |  |

| 0x70-0xDF | 1791:896    |          | Reserved   |       |       |  |  |

| 0xE0-0xFF | 2047:1792   |          | BOCORHASH  |       |       |  |  |

#### 10.3 Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following addresses of the NVM Rows memory space:

- Word 0: 0x0080A00C

- Word 1: 0x0080A040

- Word 2: 0x0080A044

- Word 3: 0x0080A048

Note: The uniqueness of the serial number is only guaranteed when considering all 128 bits.

### 16.12.8 Debug Communication Channel 1

| Name:     | DCC1       |

|-----------|------------|

| Offset:   | 0x0014     |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31  | 30          | 29  | 28   | 27             | 26  | 25  | 24  |

|--------|-----|-------------|-----|------|----------------|-----|-----|-----|

|        |     | DATA[31:24] |     |      |                |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0              | 0   | 0   | 0   |

|        |     |             |     |      |                |     |     |     |

| Bit    | 23  | 22          | 21  | 20   | 19             | 18  | 17  | 16  |

|        |     |             |     | DATA | [23:16]        |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0              | 0   | 0   | 0   |

|        |     |             |     |      |                |     |     |     |

| Bit    | 15  | 14          | 13  | 12   | 11             | 10  | 9   | 8   |

|        |     | DATA[15:8]  |     |      |                |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0              | 0   | 0   | 0   |

|        |     |             |     |      |                |     |     |     |

| Bit    | 7   | 6           | 5   | 4    | 3              | 2   | 1   | 0   |

|        |     |             |     | DATA | <b>\</b> [7:0] |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W            | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0              | 0   | 0   | 0   |

Bits 31:0 – DATA[31:0] Data Data register.

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the OSCCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSCCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

**Note:** The interrupts must be globally enabled for interrupt requests to be generated.

#### 23.6.10 Events

The CFD can generate the following output event:

Clock Failure (CLKFAIL): Generated when the Clock Failure status bit is set in the Status register (STATUS.CLKFAIL). The CFD event is not generated when the Clock Switch bit (STATUS.CLKSW) in the Status register is set.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.CFDEO) enables the CFD output event. Writing a '0' to this bit disables the CFD output event. Refer to the *Event System* chapter for details on configuring the event system.

The DFLLULP can take the following actions on an input event:

• Unlock the DFLLULP close loop tuner and start over a frequency tuning, depending on the settings of the DFLLULP registers, until the tuner achieves a new lock.

Writing a '1' to the Event Input Enable bit in the Event Control register (EVCTRL.TUNEEI) enables the corresponding action on input event. Writing a '0' to this bit disables the corresponding action on input event. Refer to the *Event System* chapter for details on configuring the event system.

#### 23.6.11 Synchronization

#### DFLLULP

Due to the asynchronicity between the main clock domain (CLK\_OSCCTRL\_APB) and the internal clock domain, some registers are synchronized when written. When a write-synchronized register is written, the corresponding bit in the Synchronization Busy register (DFLLULPSYNCBUSY) is set immediately. When the write-synchronization is complete, this bit is cleared. Reading a write-synchronized register while the synchronization is ongoing will return the value written, and not the current value in the peripheral clock domain. To read the current value in the peripheral clock domain after writing a register, the user must wait for the corresponding DFLLULPSYNCBUSY bit to be cleared before reading the value.

If a register is written while the corresponding bit in DFLLULPSYNCBUSY is one, the write is discarded and an error is generated.

The following bits and registers are write-synchronized:

• Delay Value register (DFLLULPDLY)

Write-synchronization is denoted by the Write-Synchronized property in the register description.

#### 24.5.9 Analog Connections

The external 32.768kHz crystal must be connected between the XIN32 and XOUT32 pins, along with any required load capacitors. For details on recommended oscillator characteristics and capacitor load, refer to the related links.

#### 24.6 Functional Description

#### 24.6.1 Principle of Operation

XOSC32K and OSCULP32K are configured via OSC32KCTRL control registers. Through this interface, the sub-peripherals are enabled, disabled, or have their calibration values updated.

The STATUS register gathers different status signals coming from the sub-peripherals of OSC32KCTRL. The status signals can be used to generate system interrupts, and in some cases wake up the system from standby mode, provided the corresponding interrupt is enabled.

#### 24.6.2 32KHz External Crystal Oscillator (XOSC32K) Operation

The XOSC32K can operate in two different modes:

- External clock, with an external clock signal connected to XIN32

- Crystal oscillator, with an external 32.768kHz crystal connected between XIN32 and XOUT32

At reset, the XOSC32K is disabled, and the XIN32/XOUT32 pins can either be used as General Purpose I/O (GPIO) pins or by other peripherals in the system.

When XOSC32K is enabled, the operating mode determines the GPIO usage. When in crystal oscillator mode, the XIN32 and XOUT32 pins are controlled by the OSC32KCTRL, and GPIO functions are overridden on both pins. When in external clock mode, the only XIN32 pin will be overridden and controlled by the OSC32KCTRL, while the XOUT32 pin can still be used as a GPIO pin.

The XOSC32K is enabled by writing a '1' to the Enable bit in the 32KHz External Crystal Oscillator Control register (XOSC32K.ENABLE=1). The XOSC32K is disabled by writing a '0' to the Enable bit in the 32KHz External Crystal Oscillator Control register (XOSC32K.ENABLE=0).

To enable the XOSC32K as a crystal oscillator, the XTALEN bit in the 32KHz External Crystal Oscillator Control register must be set (XOSC32K.XTALEN=1). If XOSC32K.XTALEN is '0', the external clock input will be enabled.

The XOSC32K 32.768kHz output is enabled by setting the 32KHz Output Enable bit in the 32KHz External Crystal Oscillator Control register (XOSC32K.EN32K=1). The XOSC32K also has a 1.024kHz clock output, which can only be used by the RTC. This clock output is enabled by setting the 1KHz Output Enable bit in the 32KHz External Crystal Oscillator Control register (XOSC32K.EN1K=1).

It is also possible to lock the XOSC32K configuration by setting the Write Lock bit in the 32KHz External Crystal Oscillator Control register (XOSC32K.WRTLOCK=1). If set, the XOSC32K configuration is locked until a Power-On Reset (POR) is detected.

The XOSC32K will behave differently in different sleep modes based on the settings of XOSC32K.RUNSTDBY, XOSC32K.ONDEMAND, and XOSC32K.ENABLE. If XOSC32KCTRL.ENABLE=0, the XOSC32K will be always stopped. For XOS32KCTRL.ENABLE=1, this table is valid:

#### 27.12.9 Frequency Correction

| Name:     | FREQCORR                                 |

|-----------|------------------------------------------|

| Offset:   | 0x14                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7    | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|--------|------|-----|-----|-----|------------|-----|-----|-----|

|        | SIGN |     |     |     | VALUE[6:0] |     |     |     |

| Access | R/W  | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |

| Reset  | 0    | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

Bit 7 – SIGN Correction Sign

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The correction value is positive, i.e., frequency will be decreased. |

| 1     | The correction value is negative, i.e., frequency will be increased. |

#### Bits 6:0 - VALUE[6:0] Correction Value

These bits define the amount of correction applied to the RTC prescaler.

| Value   | Description                                                |

|---------|------------------------------------------------------------|

| 0       | Correction is disabled and the RTC frequency is unchanged. |

| 1 - 127 | The RTC frequency is adjusted according to the value.      |

are not accessible. When defined non-secure callable sections have the same attributes as the secure sections, therefore the NVMCTRL considers them as secure regions. The system may also have a secure callable boot and application regions. These regions have the same attributes as the secure sections, so there is no special treatment needed in NVMCTRL.

Any illegal access will result in a bus error. The BOOT and Application non-secure callable regions are shown for reference but have no effect on the NVMCTRL. These regions are included in secure regions therefore the NVMCTRL considers them as secure regions.

| Memory Region                           | Secure Access | Non-Secure Access | Limitations                  |

|-----------------------------------------|---------------|-------------------|------------------------------|

| FLASH Boot secure                       | R+W           | -                 |                              |

| FLASH Boot non-secure                   | R+W           | R+W               |                              |

| FLASH Application secure                | R+W           | -                 |                              |

| FLASH Application non-<br>secure        | R+W           | R+W               |                              |

| Data FLASH secure                       | R+W           | -                 |                              |

| Data FLASH non-secure                   | R+W           | R+W               |                              |

| AUX FLASH Calibration<br>Row            | R+W           | R                 |                              |

| AUX FLASH User Row<br>(UROW)            | R+W           | R                 |                              |

| AUX FLASH Boot<br>Configuration (BOCOR) | R+W           | -                 | No read if BCREN is cleared. |

Table 30-2.

Memory Regions AHB Access Limitations

The Boot Configuration row (BOCOR) contains information that is read by the boot ROM and written to IDAU and NVMCTRL registers. The BOCOR is read/writable if SCFGB.BCREN/BCWEN are set, respectively.

Important: SCFGB.BCREN/BCWEN are copied from BOCOR by the boot ROM.

#### Table 30-3. Memory Regions Modify operations Limitations (WP, EP commands)

| Memory Region            | Secure<br>Access | Non-<br>Secure<br>Access | Limitations        |

|--------------------------|------------------|--------------------------|--------------------|

| FLASH Boot secure        | Y                | N                        | No if SULCK.BS=0   |

| FLASH Boot non-secure    | Y                | Y                        | No if NSULCK.BNS=0 |

| FLASH Application secure | Y                | N                        | No if SULCK.AS=0   |

## SAM L10/L11 Family

### SERCOM SPI – SERCOM Serial Peripheral Interface

| AMODE[1:0] | Name    | Description                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------|

| 0x0        | MASK    | ADDRMASK is used as a mask to the ADDR register                                                               |

| 0x1        | 2_ADDRS | The slave responds to the two unique addresses in ADDR and ADDRMASK                                           |

| 0x2        | RANGE   | The slave responds to the range of addresses between and including ADDR and ADDRMASK. ADDR is the upper limit |

| 0x3        | -       | Reserved                                                                                                      |

#### Bit 13 – MSSEN Master Slave Select Enable

This bit enables hardware slave select  $(\overline{SS})$  control.

| Value | Description                      |

|-------|----------------------------------|

| 0     | Hardware SS control is disabled. |

| 1     | Hardware SS control is enabled.  |

#### Bit 9 – SSDE Slave Select Low Detect Enable

This bit enables wake up when the slave select  $(\overline{SS})$  pin transitions from high to low.

| Value | Description                  |

|-------|------------------------------|

| 0     | SS low detector is disabled. |

| 1     | SS low detector is enabled.  |

#### Bit 6 – PLOADEN Slave Data Preload Enable

Setting this bit will enable preloading of the slave shift register when there is no transfer in progress. If the SS line is high when DATA is written, it will be transferred immediately to the shift register.

#### Bits 2:0 – CHSIZE[2:0] Character Size

| CHSIZE[2:0] | Name | Description |

|-------------|------|-------------|

| 0x0         | 8BIT | 8 bits      |

| 0x1         | 9BIT | 9 bits      |

| 0x2-0x7     | -    | Reserved    |

Enable-protection is denoted by the "Enable-Protection" property in the register description.

Before the I<sup>2</sup>C is enabled it must be configured as outlined by the following steps:

- 1. Select I<sup>2</sup>C Master or Slave mode by writing 0x4 (Slave mode) or 0x5 (Master mode) to the Operating Mode bits in the CTRLA register (CTRLA.MODE).

- 2. If desired, select the SDA Hold Time value in the CTRLA register (CTRLA.SDAHOLD).

- 3. If desired, enable smart operation by setting the Smart Mode Enable bit in the CTRLB register (CTRLB.SMEN).

- 4. If desired, enable SCL low time-out by setting the SCL Low Time-Out bit in the Control A register (CTRLA.LOWTOUT).

- 5. In Master mode:

- 5.1. Select the inactive bus time-out in the Inactive Time-Out bit group in the CTRLA register (CTRLA.INACTOUT).

- 5.2. Write the Baud Rate register (BAUD) to generate the desired baud rate.

In Slave mode:

- 5.1. Configure the address match configuration by writing the Address Mode value in the CTRLB register (CTRLB.AMODE).

- 5.2. Set the Address and Address Mask value in the Address register (ADDR.ADDR and ADDR.ADDRMASK) according to the address configuration.

#### 37.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

#### 37.6.2.3 I<sup>2</sup>C Bus State Logic

The bus state logic includes several logic blocks that continuously monitor the activity on the I<sup>2</sup>C bus lines in all sleep modes with running GCLK\_SERCOM\_x clocks. The start and stop detectors and the bit counter are all essential in the process of determining the current bus state. The bus state is determined according to Bus State Diagram. Software can get the current bus state by reading the Master Bus State bits in the Status register (STATUS.BUSSTATE). The value of STATUS.BUSSTATE in the figure is shown in binary.

## SAM L10/L11 Family SERCOM I2C – SERCOM Inter-Integrated Circ...

#### 37.8.7 Synchronization Busy

| Name:<br>Offset:<br>Reset:<br>Property: |    | SYNCBUSY<br>0x1C<br>0x00000000<br>- |    |    |    |    |        |       |

|-----------------------------------------|----|-------------------------------------|----|----|----|----|--------|-------|

| Bit                                     | 31 | 30                                  | 29 | 28 | 27 | 26 | 25     | 24    |

|                                         |    |                                     |    |    |    |    |        |       |

| Access                                  |    |                                     |    |    |    |    |        |       |

| Reset                                   |    |                                     |    |    |    |    |        |       |

|                                         |    |                                     |    |    |    |    |        |       |

| Bit                                     | 23 | 22                                  | 21 | 20 | 19 | 18 | 17     | 16    |

|                                         |    |                                     |    |    |    |    |        |       |

| Access                                  |    |                                     |    |    |    |    |        |       |

| Reset                                   |    |                                     |    |    |    |    |        |       |

|                                         |    |                                     |    |    |    |    |        |       |

| Bit                                     | 15 | 14                                  | 13 | 12 | 11 | 10 | 9      | 8     |

|                                         |    |                                     |    |    |    |    |        |       |

| Access                                  |    |                                     |    |    |    |    |        |       |

| Reset                                   |    |                                     |    |    |    |    |        |       |

| Bit                                     | 7  | 6                                   | 5  | 4  | 3  | 2  | 1      | 0     |

| BIL                                     | 1  | 0                                   | 5  | 4  | 3  | 2  | ENABLE | SWRST |

| A                                       |    |                                     |    |    |    |    |        |       |

| Access                                  |    |                                     |    |    |    |    | R      | R     |

| Reset                                   |    |                                     |    |    |    |    | 0      | 0     |

#### Bit 1 – ENABLE SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

#### Bit 0 – SWRST Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

#### Bits 21:20 - SDAHOLD[1:0] SDA Hold Time

These bits define the SDA hold time with respect to the negative edge of SCL.

These bits are not synchronized.

| Value | Name  | Description         |

|-------|-------|---------------------|

| 0x0   | DIS   | Disabled            |

| 0x1   | 75NS  | 50-100ns hold time  |

| 0x2   | 450NS | 300-600ns hold time |

| 0x3   | 600NS | 400-800ns hold time |

#### Bit 16 – PINOUT Pin Usage

This bit set the pin usage to either two- or four-wire operation:

This bit is not synchronized.

| Value | Description                |

|-------|----------------------------|

| 0     | 4-wire operation disabled. |

| 1     | 4-wire operation enabled.  |

#### Bit 7 – RUNSTDBY Run in Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

| Value | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 0     | GCLK_SERCOMx_CORE is disabled and the I <sup>2</sup> C master will not operate in standby sleep |

|       | mode.                                                                                           |

| 1     | GCLK_SERCOMx_CORE is enabled in all sleep modes.                                                |

#### Bits 4:2 - MODE[2:0] Operating Mode

These bits must be written to 0x5 to select the  $I^2C$  master serial communication interface of the SERCOM.

These bits are not synchronized.

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Synchronization Enable Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled.                    |

#### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

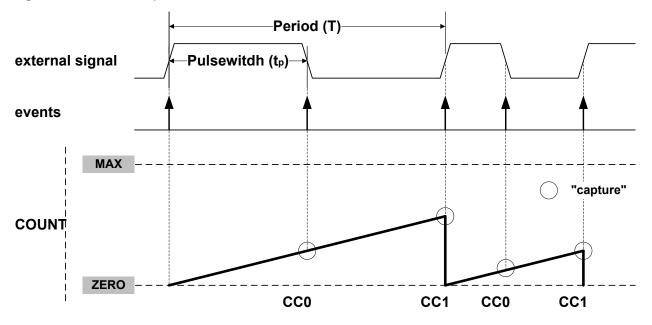

$$f = \frac{1}{T}$$

dutyCycle =  $\frac{t_p}{T}$

Figure 38-13. PWP Capture

Selecting PWP in the Event Action bit group in the Event Control register (EVCTRL.EVACT) enables the TC to perform one capture action on the rising edge and the other one on the falling edge. The period T will be captured into CC1 and the pulse width  $t_p$  in CC0. EVCTRL.EVACT=PPW (period and pulse-width) offers identical functionality, but will capture T into CC0 and  $t_p$  into CC1.

The TC Event Input Invert Enable bit in the Event Control register (EVCTRL.TCINV) is used to select whether the wraparound should occur on the rising edge or the falling edge. If EVCTRL.TCINV=1, the wraparound will happen on the falling edge. In case pin capture is enabled, this can also be achieved by modifying the value of the DRVCTRL.INVENx bit.

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

**Note:** The corresponding capture is working only if the channel is enabled in capture mode (CTRLA.CAPTENx=1). If not, the capture action is ignored and the channel is enabled in compare mode of operation. Consequently, both channels must be enabled in order to fully characterize the input.

#### 38.6.2.8.3 Pulse-Width Capture Action

The TC performs the input capture on the falling edge of the input signal. When the edge is detected, the counter value is cleared and the TC stops counting. When a rising edge is detected on the input signal, the counter restarts the counting operation. To enable the operation on opposite edges, the input signal to capture must be inverted (refer to DRVCTRL.INVEN or EVCTRL.TCEINV).

#### 38.7.1.16 Period Buffer Value, 8-bit Mode

Name:PERBUFOffset:0x2FReset:0xFFProperty:Write-Synchronized

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

|        |     |     |     | PERB | JF[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 1   |

#### Bits 7:0 – PERBUF[7:0] Period Buffer Value

These bits hold the value of the period buffer register. The value is copied to PER register on UPDATE condition.

#### 39.8.1 Control A

| Name:     | CTRLA                |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0 |

|--------|---|----------|---|---|---|---|--------|---|

|        |   | RUNSTDBY |   |   |   |   | ENABLE |   |

| Access |   | R/W      |   |   |   |   | R/W    |   |

| Reset  |   | 0        |   |   |   |   | 0      |   |

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the ADC behaves during standby sleep mode:

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The TRNG is halted during standby sleep mode.  |

| 1     | The TRNG is not stopped in standby sleep mode. |

#### Bit 1 – ENABLE Enable

| Value | Description           |

|-------|-----------------------|

| 0     | The TRNG is disabled. |

| 1     | The TRNG is enabled.  |

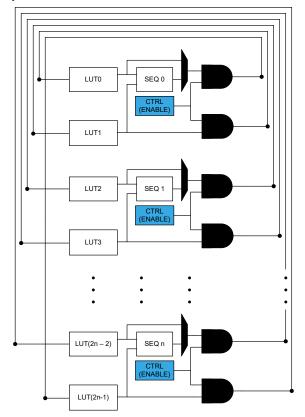

#### Figure 40-5. Linked LUT Input Selection

#### Internal Events Inputs Selection (EVENT)

Asynchronous events from the Event System can be used as input selection, as shown in Figure 40-6. For each LUT, one event input line is available and can be selected on each LUT input. Before enabling the event selection by writing LUTCTRLx.INSELy=EVENT, the Event System must be configured first.

By default CCL includes an edge detector. When the event is received, an internal strobe is generated when a rising edge is detected. The pulse duration is one GCLK\_CCL clock cycle. Writing the LUTCTRLx.INSELy=ASYNCEVENT will disable the edge detector. In this case, it is possible to combine an asynchronous event input with any other input source. This is typically useful with event levels inputs (external IO pin events, as example). The following steps ensure proper operation:

- 1. Enable the GCLK\_CCL clock.

- 2. Configure the Event System to route the event asynchronously.

- 3. Select the event input type (LUTCTRLx.INSEL).

- 4. If a strobe must be generated on the event input falling edge, write a '1' to the Inverted Event Input Enable bit in LUT Control register (LUTCTRLx.INVEI).

- 5. Enable the event input by writing the Event Input Enable bit in LUT Control register (LUTCTRLx.LUTEI) to '1'.

## SAM L10/L11 Family

## **Electrical Characteristics**

| Mode | Conditions | Regulator | PL                    | CPU Clock  | Vcc  | Та   | Тур. | Мах | Units |

|------|------------|-----------|-----------------------|------------|------|------|------|-----|-------|

|      |            |           |                       | DFLLULP at | 1.8V |      | 14.3 | 19  |       |

|      |            |           |                       | 32MHz      | 3.3V |      | 14.4 | 19  |       |

|      |            | BUCK      | PL0                   |            | 1.8V |      | 11.1 | 21  |       |

|      |            |           |                       | 8MHz       | 3.3V | 8.3  | 16   |     |       |

|      |            |           |                       | OSC 8MHz   | 1.8V |      | 15.5 | 24  |       |

|      |            |           | 3.3V<br>OSC 4MHz 1.8V |            | 3.3V |      | 15.2 | 21  |       |

|      |            |           |                       |            | 21.3 | 39   |      |     |       |

|      |            |           |                       | 3.3V       |      | 21.6 | 35   |     |       |

|      |            |           | PL2                   |            | 1.8V |      | 14.9 | 19  |       |

|      |            |           |                       | 32MHz      | 3.3V |      | 9.1  | 12  |       |

|      |            |           |                       | DFLLULP at | 1.8V |      | 10.6 | 14  |       |

|      |            |           | 32MHz 3               | 3.3V       |      | 6.7  | 9    |     |       |

#### Table 46-9. Standby and Off Mode Current Consumption

| Mode    | Conditions                                             | Regulator Mode                                                   | Vcc  | Та   | Тур. | Max. | Units |

|---------|--------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|-------|

| STANDBY |                                                        | LPVREG with LPEFF Disable                                        | 1.8V | 25°C | 1.3  | 3.5  | μA    |

|         | PDSW domain in active state                            |                                                                  |      | 85°C | 18.4 | 66.0 |       |

|         |                                                        | LPVREG with LPEFF Enable                                         | 3.3V | 25°C | 1.1  | 3.0  |       |

|         |                                                        |                                                                  |      | 85°C | 14.2 | 41.8 |       |

|         |                                                        | BUCK in standby with                                             | 1.8V | 25°C | 1.2  | 2.9  |       |

|         |                                                        | MAINVREG in PL0 mode<br>(VREG.RUNSTDBY=1 and<br>VREG.STDBYPL0=1) |      | 85°C | 14.6 | 42.9 |       |

|         |                                                        |                                                                  | 3.3V | 25°C | 1.1  | 2.2  |       |

|         |                                                        |                                                                  |      | 85°C | 9.6  | 28.6 |       |

|         | All 16 kB RAM retained,<br>PDSW domain in<br>retention | LPVREG with LPEFF Disable                                        | 1.8V | 25°C | 0.6  | 1.1  |       |

|         |                                                        |                                                                  |      | 85°C | 5.1  | 14.9 |       |

|         |                                                        | LPVREG with LPEFF Enable                                         | 3.3V | 25°C | 0.5  | 1.0  |       |

|         |                                                        |                                                                  |      | 85°C | 4.3  | 12.1 |       |

|         |                                                        | BUCK in standby with                                             | 1.8V | 25°C | 0.8  | 1.1  |       |

|         |                                                        | MAINVREG in PL0 mode<br>(VREG.RUNSTDBY=1 and                     |      | 85°C | 4.3  | 11.9 |       |

|         |                                                        | VREG.STDBYPL0=1)                                                 | 3.3V | 25°C | 0.8  | 1.5  |       |

|         |                                                        |                                                                  |      | 85°C | 3.4  | 8.5  |       |

# SAM L10/L11 Family

## **Electrical Characteristics**

#### 46.11.7 DETREF Characteristics

Table 46-31. Reference Voltage Characteristics

| Symbol      | Parameter                   | Conditions                                    | Min.  | Тур.          | Max.  | Units |

|-------------|-----------------------------|-----------------------------------------------|-------|---------------|-------|-------|

| ADC/DAC Ref | ADC/DAC internal reference  | nom. 1.0V, V <sub>CC</sub> =3.0V, T= 25°C     | 0.976 | 1.0           | 1.022 | V     |

|             |                             | nom. 1.1V, $V_{CC}$ =3.0V, T= 25°C            | 1.077 | 1.1           | 1.127 |       |

|             |                             | nom. 1.2V, V <sub>CC</sub> =3.0V, T= 25°C     | 1.174 | 1.2           | 1.234 |       |

|             |                             | nom. 1.25V, V <sub>CC</sub> =3.0V, T=<br>25°C | 1.221 | 1.25          | 1.287 |       |

|             |                             | nom. 2.0V, V <sub>CC</sub> =3.0V, T= 25°C     | 1.945 | 2.0           | 2.030 |       |

|             |                             | nom. 2.2V, V <sub>CC</sub> =3.0V, T= 25°C     | 2.143 | 2.2           | 2.242 |       |

|             |                             | nom. 2.4V, V <sub>CC</sub> =3.0V, T= 25°C     | 2.335 | 2.4           | 2.457 |       |

|             |                             | nom. 2.5V, V <sub>CC</sub> =3.0V, T= 25°C     | 2.428 | 2.5           | 2.563 |       |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                       | -     | -0.01/+0.015  | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                       | -     | -0.01/+0.005  | -     |       |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                       | -     | +/-0.35       | -     | %/V   |

| AC Ref      | AC Ref Accuracy             | V <sub>CC</sub> =3.0V, T=25°C                 | 1.086 | 1.1           | 1.128 | V     |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                       | -     | +/-0.01       | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                       | -     | -0.005/+0.001 | -     | %/°C  |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                       | -     | -0.35/+0.35   | -     | %/V   |

#### 46.11.8 OPAMP Characteristics Table 46-32. Operating Conditions

| Symbol                | Parameters               | Conditions                    | Min. | Тур. | Max.     | Unit |

|-----------------------|--------------------------|-------------------------------|------|------|----------|------|

| VCC                   | Power Supply             | All power modes               | 1.6  | 3    | 3.63     | V    |

| Vin                   | Input voltage range      |                               | 0    | -    | Vcc      | V    |

| Vout                  | Output voltage range     |                               | 0.15 | -    | Vcc-0.15 | V    |

| Cload                 | Maximum capacitance load |                               | -    | -    | 50       | pF   |

| Rload (1)             | Minimum resistive load   | Output Range[0.15V;Vcc-0.15V] | 3.5  | -    | -        | kΩ   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | 0.5  | -    | -        |      |

| I <sub>load</sub> (1) | DC output current load   | Output Range[0.15V;Vcc-0.15V] | -    | -    | 1        | mA   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | -    | -    | 6.9      |      |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

#### Note:

1. These values are based on simulation. They are not covered by production test limits or characterization.

| Symbol | Parameter                        | Conditions                                        |                                                  | Measurements |          |          | l lait |

|--------|----------------------------------|---------------------------------------------------|--------------------------------------------------|--------------|----------|----------|--------|

| Symbol | S                                | Conditions                                        |                                                  | Min          | Тур      | Max      | Unit   |

| ENOB   | Effective<br>Number of<br>bits   | Fadc =<br>1Msps                                   | Vref=2.0V<br>Vddana=3.<br>0V                     | 9.1          | 10.2     | 10.8     | bits   |

|        |                                  |                                                   | Vref=1.0V<br>Vddana=1.<br>6V to 3.6V             | 9.0          | 10.1     | 10.6     |        |

|        |                                  |                                                   | Vref=Vdda<br>na=1.6V to<br>3.6V                  | 8.9          | 9.9      | 11.0     |        |

|        |                                  |                                                   | Bandgap<br>Reference,<br>Vddana=1.<br>6V to 3.6V | 9.0          | 9.8      | 10.6     |        |

| TUE    | Total<br>Unadjusted<br>Error     | without<br>offset and<br>gain<br>compensati<br>on | Vref=Vdda<br>na=1.6V to<br>3.6V                  | -            | 7        | 32       | LSB    |

| INL    | Integral<br>Non<br>Linearity     | without<br>offset and<br>gain<br>compensati<br>on | Vref=Vdda<br>na=1.6V to<br>3.6V                  | -            | +/-1.9   | +/-4.8   |        |

| DNL    | Differential<br>Non<br>Linearity | without<br>offset and<br>gain<br>compensati<br>on | Vref=Vdda<br>na=1.6V to<br>3.6V                  | -            | +0.94/-1 | +1.85/-1 |        |

| Gain   | Gain Error                       | without<br>gain<br>compensati                     | Vref=1V<br>Vddana=1.<br>6V to 3.6V               | -            | +/-0.38  | +/-1.9   | %      |

|        | on                               | Vref=3V<br>Vddana=1.<br>6V to 3.6V                | -                                                | +/-0.14      | +/-0.9   |          |        |

|        |                                  |                                                   | Bandgap<br>Reference                             | -            | +/-0.64  | +/-5.4   |        |

### Table 47-8. Differential Mode (1)

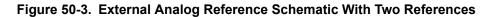

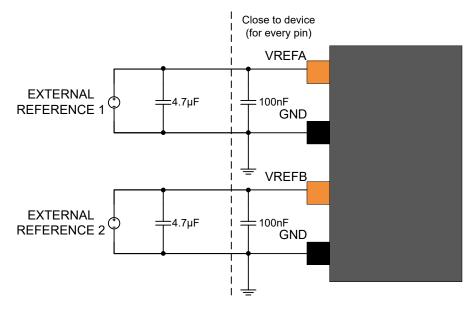

#### Figure 50-4. External Analog Reference Schematic With One Reference

#### Table 50-2. External Analog Reference Connections

| Signal Name | Recommended Pin Connection                                                                                                                                           | Description                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| VREFx       | 1.0V to $(V_{DDANA} - 0.6V)$ for ADC<br>1.0V to $(V_{DDANA} - 0.15V)$ for DAC<br>Decoupling/filtering capacitors<br>100nF <sup>(1)(2)</sup> and 4.7µF <sup>(1)</sup> | External reference VREFx for the analog port |

| GND         |                                                                                                                                                                      | Ground                                       |

1. These values are only given as a typical example.

2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

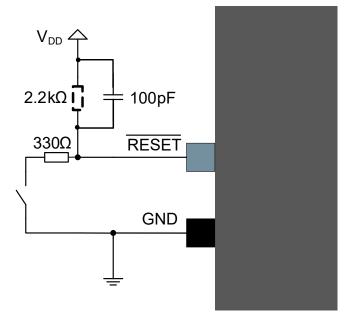

#### 50.4 External Reset Circuit

The external Reset circuit is connected to the RESET pin when the external Reset function is used. The circuit is not necessary when the RESET pin is not driven LOW externally by the application circuitry.

The reset switch can also be removed, if a manual reset is not desired. The RESET pin itself has an internal pull-up resistor, hence it is optional to add any external pull-up resistor.

#### Figure 50-5. External Reset Circuit Schematic

A pull-up resistor makes sure that the reset does not go low and unintentionally causing a device reset. An additional resistor has been added in series with the switch to safely discharge the filtering capacitor, i.e. preventing a current surge when shorting the filtering capacitor which again can cause a noise spike that can have a negative effect on the system.

|  | Table 50-3. | Reset | Circuit | Connections |

|--|-------------|-------|---------|-------------|

|--|-------------|-------|---------|-------------|

| Signal Name | Recommended Pin Connection                                                           | Description |

|-------------|--------------------------------------------------------------------------------------|-------------|

| RESET       | Reset low level threshold voltage $V_{DDIO}$ = 1.62V - 2.0V: Below 0.33 * $V_{DDIO}$ | Reset pin   |

|             | V <sub>DDIO</sub> = 2.7V - 3.63V: Below 0.36 * V <sub>DDIO</sub>                     |             |

|             | Decoupling/filter capacitor 100pF <sup>(1)</sup>                                     |             |

|             | Pull-up resistor 2.2k $\Omega^{(1,2)}$                                               |             |

|             | Resistor in series with the switch $330\Omega^{(1)}$                                 |             |

1. These values are only given as a typical example.

2. The SAM L10/L11 features an internal pull-up resistor on the RESET pin, hence an external pull-up is optional.