#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d15a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 27.2.                                                                                                                 | Features                                                                                                                                                                                                                                   | 386                                                                              |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 27.3.                                                                                                                 | Block Diagram                                                                                                                                                                                                                              | 387                                                                              |

| 27.4.                                                                                                                 | Signal Description                                                                                                                                                                                                                         | 388                                                                              |

| 27.5.                                                                                                                 | Product Dependencies                                                                                                                                                                                                                       | 388                                                                              |

| 27.6.                                                                                                                 | Functional Description                                                                                                                                                                                                                     | 390                                                                              |

| 27.7.                                                                                                                 | Register Summary - Mode 0 - 32-Bit Counter                                                                                                                                                                                                 | 402                                                                              |

| 27.8.                                                                                                                 | Register Description - Mode 0 - 32-Bit Counter                                                                                                                                                                                             | 403                                                                              |

| 27.9.                                                                                                                 | Register Summary - Mode 1 - 16-Bit Counter                                                                                                                                                                                                 | 426                                                                              |

| 27.10                                                                                                                 | . Register Description - Mode 1 - 16-Bit Counter                                                                                                                                                                                           | 427                                                                              |

| 27.11                                                                                                                 | . Register Summary - Mode 2 - Clock/Calendar                                                                                                                                                                                               | 450                                                                              |

| 27.12                                                                                                                 | . Register Description - Mode 2 - Clock/Calendar                                                                                                                                                                                           | 451                                                                              |

| 28. DMA                                                                                                               | C – Direct Memory Access Controller                                                                                                                                                                                                        | . 476                                                                            |

|                                                                                                                       | Overview                                                                                                                                                                                                                                   |                                                                                  |

|                                                                                                                       | Features                                                                                                                                                                                                                                   |                                                                                  |

|                                                                                                                       | Block Diagram                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                       | Signal Description                                                                                                                                                                                                                         |                                                                                  |

|                                                                                                                       | Product Dependencies                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                                       | Functional Description                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                                       | Register Summary                                                                                                                                                                                                                           |                                                                                  |

|                                                                                                                       | Register Description                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                                       | Register Summary - SRAM                                                                                                                                                                                                                    |                                                                                  |

|                                                                                                                       | . Register Description - SRAM                                                                                                                                                                                                              |                                                                                  |

| 20.10                                                                                                                 |                                                                                                                                                                                                                                            | 002                                                                              |

| 29. EIC                                                                                                               | – External Interrupt Controller                                                                                                                                                                                                            | . 540                                                                            |

| 29.1.                                                                                                                 | Overview                                                                                                                                                                                                                                   | 540                                                                              |

| 29.2.                                                                                                                 | Features                                                                                                                                                                                                                                   | 540                                                                              |

| 29.3.                                                                                                                 | Block Diagram                                                                                                                                                                                                                              | 540                                                                              |

| 29.4.                                                                                                                 | Signal Description                                                                                                                                                                                                                         | 541                                                                              |

| 29.5.                                                                                                                 | Product Dependencies                                                                                                                                                                                                                       | 541                                                                              |

| 29.6.                                                                                                                 | Functional Description                                                                                                                                                                                                                     | 543                                                                              |

| 29.7                                                                                                                  |                                                                                                                                                                                                                                            |                                                                                  |

| 20.7.                                                                                                                 | Register Summary                                                                                                                                                                                                                           | 550                                                                              |

|                                                                                                                       | Register Summary<br>Register Description                                                                                                                                                                                                   |                                                                                  |

| 29.8.                                                                                                                 | Register Description                                                                                                                                                                                                                       | 551                                                                              |

| 29.8.<br>30. NVM                                                                                                      | Register Description                                                                                                                                                                                                                       | 551<br><b>572</b>                                                                |

| 29.8.<br>30. NVM<br>30.1.                                                                                             | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview                                                                                                                                                                  | 551<br><b>572</b><br>572                                                         |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.                                                                                    | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features                                                                                                                                                      | 551<br><b>572</b><br>572<br>572                                                  |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.                                                                           | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram                                                                                                                                     | 551<br><b>572</b><br>572<br>572<br>573                                           |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.                                                                  | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description                                                                                                               | 551<br>572<br>572<br>572<br>573<br>573                                           |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.                                                         | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features.<br>Block Diagram<br>Signal Description<br>Product Dependencies.                                                                                     | 551<br>572<br>572<br>573<br>573<br>573                                           |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.                                                | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description                                                             | 551<br>572<br>572<br>573<br>573<br>573<br>573                                    |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.<br>30.7.                                       | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary                                         | 551<br>572<br>572<br>573<br>573<br>573<br>575<br>586                             |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.<br>30.7.<br>30.8.                              | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description                 | 551<br>572<br>572<br>573<br>573<br>573<br>573<br>575<br>586<br>587               |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.<br>30.7.<br>30.8.<br>31. TRA                   | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>M - TrustRAM | 551<br>572<br>572<br>573<br>573<br>573<br>573<br>575<br>586<br>587<br>614        |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.<br>30.7.<br>30.8.<br>31. TRA<br>31.1.          | Register Description   ICTRL – Nonvolatile Memory Controller   Overview                                                                                                                                                                    | 551<br>572<br>572<br>573<br>573<br>573<br>573<br>586<br>587<br>614<br>614        |

| 29.8.<br>30. NVM<br>30.1.<br>30.2.<br>30.3.<br>30.4.<br>30.5.<br>30.6.<br>30.7.<br>30.8.<br>31. TRA<br>31.1.<br>31.2. | Register Description<br>ICTRL – Nonvolatile Memory Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>M - TrustRAM | 551<br>572<br>572<br>573<br>573<br>573<br>573<br>587<br>587<br>614<br>614<br>614 |

## **Processor and Architecture**

## Table 11-3. Interrupt Line Mapping

| Module                                   | Source               | NVIC line |

|------------------------------------------|----------------------|-----------|

| EIC NMI – External Interrupt Controller  | NMI                  | NMI       |

| PM – Power Manager                       | PLRDY                | 0         |

| /ICLK - Main Clock                       | CKRDY                |           |

| DSCCTRL - Oscillators Controller         | XOSCRDY              |           |

|                                          | XOSCFAIL             |           |

|                                          | OSC16MRDY            |           |

|                                          | DFLLULPRDY           |           |

|                                          | DFLLULPLOCK          |           |

|                                          | DFLLULPNOLOCK        |           |

|                                          | DPLLLCKR             |           |

|                                          | DPLLLCKF             |           |

|                                          | DPLLLTO              |           |

|                                          | DPLLLDRTO            |           |

| SC32KCTRL - 32KHz Oscillators Controller | XOSC32KRDY           |           |

|                                          | CLKFAIL              |           |

| UPC - Supply Controller                  | BOD33RDY             |           |

|                                          | BOD33DET             |           |

|                                          | B33SRDY              |           |

|                                          | VREGRDY              |           |

|                                          | VCORERDY             |           |

|                                          | ULPVREFRDY           |           |

| VDT – Watchdog Timer                     | EW                   | 1         |

| RTC – Real Time Counter                  | СМР0                 | 2         |

|                                          | CMP1                 |           |

|                                          | OVF                  |           |

|                                          | PER0                 |           |

|                                          | PER1                 |           |

|                                          | PER2                 |           |

|                                          | PER3                 |           |

|                                          | PER4                 |           |

|                                          | PER5                 |           |

|                                          | PER6                 |           |

|                                          | PER7                 |           |

|                                          | TAMPER               |           |

| EIC – External Interrupt Controller      | EXTINT 0             | 3         |

|                                          | EXTINT 1             | 4         |

|                                          | EXTINT 2             | 5         |

|                                          | EXTINT 3             | 6         |

|                                          | EXTINT 47            | 7         |

|                                          | NSCHK <sup>(1)</sup> |           |

| REQM - Frequency Meter                   | DONE                 | 8         |

| IVMCTRL – Non-Volatile Memory Controller | DONE                 | 9         |

|                                          | PROGE                |           |

• Non-Secure Callable (NSC): NSC is a special type of Secure memory location. It allows software to transition from Non-Secure to Secure state.

The Cortex-M23 provides two ways for managing the security configurations of the device.

The first solution consists in using the Cortex-M23 SAU (Security Attribution Unit), which is a Memory Protection Unit (MPU) like hardware embedded in the core. The role of the SAU is to manage all the Secure and Non-Secure transactions coming from the core. However, using the SAU implies that the security configuration must be propagated somewhere else in the MCU architecture for security awareness.

The second approach, which is the one used for SAM L11 devices, is articulated around a centralized Implementation Defined Attribution Unit (IDAU), which is a hardware unit external to the core.

For SAM L11 devices, the IDAU is coupled to the Cortex-M23 and manages all the security configurations related to the core. In addition, the IDAU propagates all the security configurations to the memory controllers. The IDAU, Flash, Data Flash and SRAM embedded memories can be split in sub-regions, which are reserved either for the Secure or for the Non-Secure application. Therefore, the SAU is not required and is absent from SAM L10/L11 devices.

The peripherals security attribution is managed by the Peripherals Access Controller (PAC). The PAC and each peripheral can be allocated either to the Secure or to the Non-Secure application, with the exception of the PAC, NVMCTRL, and DSU.

#### Note:

- 1. The PAC and NVMCTRL peripherals are always secured.

- 2. The DSU peripheral is always non-secured.

Both IDAU and PAC security configurations are stored in NVM fuses, which are read after each reset during Boot ROM execution and are loaded after Boot ROM verifications into their respective registers.

The peripherals security attribution (using PAC) is locked before exiting the Boot ROM execution sequence, that is, it is not possible to change a peripheral's configuration (Secure or Non-Secure) during application execution. However, the security attribution of each peripheral, excluding the PAC, NVMCTRL, and DSU, can be modified using the NONSECx NVM fused from the User Row (UROW) during application execution, hence it can be considered after any reset.

### 13.2.2 Memories Security Attribution

The IDAU is used to indicate the processor if a particular memory region is Secure (S), Non-secure Callable (NSC), or Non-secure (NS). It can also mark a memory region to be exempted from security checking.

| Attribute           | Description                                                                             |

|---------------------|-----------------------------------------------------------------------------------------|

| Non-Secure          | Memory can be accessed in Secure or Non-Secure state.                                   |

| Secure              | Memory can only be accessed in Secure state. It cannot be called from Non-Secure state. |

| Non-Secure callable | Memory can only be accessed in Secure state, but can be called from Non-Secure state.   |

| Exempt              | No attribution check will be done, and the operation will take place on the bus         |

#### Table 13-1. IDAU Memory Attribution Definition

**Note:** Refer to "SAM L11 Security Attribution" chapter for the detailed SAM L11 memories and peripherals security attribution description.

## **PAC - Peripheral Access Controller**

### 15.7.14 Peripheral Non-Secure Status - Bridge C

| Name:     | NONSECC                                              |

|-----------|------------------------------------------------------|

| Offset:   | 0x5C                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | Write-Secure                                         |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

#### Reading NONSEC register returns peripheral Security Attribution status:

|                 | Value |       | Des  | cription                   |       |         |         |         |       |  |

|-----------------|-------|-------|------|----------------------------|-------|---------|---------|---------|-------|--|

|                 | 0 F   |       |      | Peripheral is secured.     |       |         |         |         |       |  |

|                 | 1     |       | Peri | Peripheral is non-secured. |       |         |         |         |       |  |

| Bit             | 31    | 30    |      | 29                         | 28    | 27      | 26      | 25      | 24    |  |

| Access          |       |       |      |                            |       |         |         |         |       |  |

| Reset           |       |       |      |                            |       |         |         |         |       |  |

| Bit             | 23    | 22    |      | 21                         | 20    | 19      | 18      | 17      | 16    |  |

| A               |       |       |      |                            |       |         |         |         |       |  |

| Access<br>Reset |       |       |      |                            |       |         |         |         |       |  |

| Bit             | 15    | 14    |      | 13                         | 12    | 11      | 10      | 9       | 8     |  |

|                 |       |       |      | TRAM                       | OPAMP | CCL     | TRNG    | PTC     | DAC   |  |

| Access          |       |       |      | R/R/R                      | R/R/R | R/R/R   | R/R/R   | R/R/R   | R/R/R |  |

| Reset           |       |       |      | х                          | х     | х       | х       | х       | x     |  |

| Bit             | 7     | 6     |      | 5                          | 4     | 3       | 2       | 1       | 0     |  |

|                 | ADC   | TC2   |      | TC1                        | TC0   | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS |  |

| Access          | R/R/R | R/R/F | 2    | R/R/R                      | R/R/R | R/R/R   | R/R/R   | R/R/R   | R/R/R |  |

| Reset           | x     | х     |      | x                          | x     | x       | x       | x       | x     |  |

#### Bit 13 – TRAM Peripheral TRAM Non-Secure

- Bit 12 OPAMP Peripheral OPAMP Non-Secure

- Bit 11 CCL Peripheral CCL Non-Secure

- Bit 10 TRNG Peripheral TRNG Non-Secure

- Bit 9 PTC Peripheral PTC Non-Secure

## 25. SUPC – Supply Controller

## 25.1 Overview

The Supply Controller (SUPC) manages the voltage reference and power supply of the device.

The SUPC controls the voltage regulators for the core (VDDCORE) domain. It sets the voltage regulators according to the sleep modes, or the user configuration. In active mode, the voltage regulators can be selected on the fly between LDO (low-dropout) type regulator or Buck converter.

The SUPC embeds two Brown-Out Detectors. BOD33 monitors the voltage applied to the device (VDD) and BOD12 monitors the internal voltage to the core (VDDCORE). The BOD can monitor the supply voltage continuously (continuous mode) or periodically (sampling mode).

The SUPC generates also a selectable reference voltage and a voltage dependent on the temperature which can be used by analog modules like the ADC or DAC.

## 25.2 Features

- Voltage Regulator System

- Main voltage regulator: LDO or Buck Converter in active mode (MAINVREG)

- Low-Power voltage regulator in Standby mode (LPVREG)

- Adjustable VDDCORE to the Sleep mode or the performance level

- Controlled VDDCORE voltage slope when changing VDDCORE

- Voltage Reference System

- Reference voltage for ADC and DAC

- Temperature sensor

- 3.3V Brown-Out Detector (BOD33)

- Programmable threshold

- Threshold value loaded from NVM User Row at startup

- Triggers resets or interrupts or event. Action loaded from NVM User Row

- Operating modes:

- Continuous mode

- Sampled mode for low power applications with programmable sample frequency

- Hysteresis value from Flash User Calibration

- 1.2V Brown-Out Detector (BOD12)

- Internal non-configurable Brown-Out Detector

#### 27.12.2 Control B in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x2                                    |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15    | 14     | 13        | 12     | 11 | 10  | 9         | 8     |

|--------|-------|--------|-----------|--------|----|-----|-----------|-------|

| ĺ      | SEPTO |        | ACTF[2:0] |        |    |     | DEBF[2:0] |       |

| Access | R/W   | R/W    | R/W       | R/W    |    | R/W | R/W       | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    | 0   | 0         | 0     |

|        |       |        |           |        |    |     |           |       |

| Bit    | 7     | 6      | 5         | 4      | 3  | 2   | 1         | 0     |

|        | DMAEN | RTCOUT | DEBASYNC  | DEBMAJ |    |     |           | GP0EN |

| Access | R/W   | R/W    | R/W       | R/W    |    |     |           | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    |     |           | 0     |

#### Bit 15 – SEPTO Separate Tamper Outputs

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | IN[n] is compared tp OUT[0] (backward-compatible). |

| 1     | IN[n] is compared tp OUT[n].                       |

#### Bits 14:12 – ACTF[2:0] Active Layer Frequency

These bits define the prescaling factor for the RTC clock output (OUT) used during active layer protection in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_OUT = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_OUT = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_OUT = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_OUT = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_OUT = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_OUT = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_OUT = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_OUT = CLK_RTC / 256 |

### Bits 10:8 – DEBF[2:0] Debounce Frequency

These bits define the prescaling factor for the input debouncers in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_DEB = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_DEB = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_DEB = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_DEB = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_DEB = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_DEB = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_DEB = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_DEB = CLK_RTC / 256 |

TRAM - TrustRAM

| Offset | Name      | Bit Pos. |             |

|--------|-----------|----------|-------------|

|        |           | 7:0      | DATA[7:0]   |

| 0x01A0 | RAM40     | 15:8     | DATA[15:8]  |

| UXUTAU |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01A4 | RAM41     | 15:8     | DATA[15:8]  |

| 010174 | rxAivi4 i | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01A8 | RAM42     | 15:8     | DATA[15:8]  |

| UXUTAO | RAIVI42   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01AC | RAM43     | 15:8     | DATA[15:8]  |

| UXUTAC | KAIVI43   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01B0 | RAM44     | 15:8     | DATA[15:8]  |

| 00100  | rtAivi44  | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01B4 | RAM45     | 15:8     | DATA[15:8]  |

| 0.0104 | TVAIN43   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01B8 | RAM46     | 15:8     | DATA[15:8]  |

| 0.0100 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01BC | RAM47     | 15:8     | DATA[15:8]  |

| 0,0100 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C0 | RAM48     | 15:8     | DATA[15:8]  |

| 0,0100 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C4 | RAM49     | 15:8     | DATA[15:8]  |

|        |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C8 | RAM50     | 15:8     | DATA[15:8]  |

| 0.0100 | 10 1000   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

| 0x01CC | RAM51     | 7:0      | DATA[7:0]   |

| 0,0100 |           | 15:8     | DATA[15:8]  |

### 33.7.12 Channel n Status

| Name:     | CHSTATUSn            |

|-----------|----------------------|

| Offset:   | 0x27 + n*0x08 [n=07] |

| Reset:    | 0x01                 |

| Property: | Mix-Secure           |

**Important:** For **SAM L11 Non-Secure** accesses, read accesses (R\*) are allowed only if the security attribution for the corresponding channel (CHANNELx) is set as Non-Secured in the NONSECCHAN register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|--------|---|---|---|---|---|---|--------|--------|

| ſ      |   |   |   |   |   |   | BUSYCH | RDYUSR |

| Access |   |   |   | • | • | • | R/R*/R | R/R*/R |

| Reset  |   |   |   |   |   |   | 0      | 0      |

#### Bit 1 – BUSYCH Busy Channel

This bit is cleared when channel is idle.

This bit is set if an event on channel has not been handled by all event users connected to channel.

When the event channel path is asynchronous, this bit is always read '0'.

#### Bit 0 – RDYUSR Ready User

This bit is cleared when at least one of the event users connected to the channel is not ready.

This bit is set when all event users connected to channel are ready to handle incoming events on the channel.

When the event channel path is asynchronous, this bit is always read zero.

#### 35.6.2.6 Data Reception

The receiver accepts data when a valid start bit is detected. Each bit following the start bit will be sampled according to the baud rate or XCK clock, and shifted into the receive shift register until the first stop bit of a frame is received. The second stop bit will be ignored by the receiver.

When the first stop bit is received and a complete serial frame is present in the receive shift register, the contents of the shift register will be moved into the two-level or four-level receive buffer. Then, the Receive Complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set, and the optional interrupt will be generated.

The received data can be read from the DATA register when the Receive Complete interrupt flag is set.

#### 35.6.2.6.1 Disabling the Receiver

Writing '0' to the Receiver Enable bit in the CTRLB register (CTRLB.RXEN) will disable the receiver, flush the two-level or four-level receive buffer, and data from ongoing receptions will be lost.

#### 35.6.2.6.2 Error Bits

The USART receiver has three error bits in the Status (STATUS) register: Frame Error (FERR), Buffer Overflow (BUFOVF), and Parity Error (PERR). Once an error happens, the corresponding error bit will be set until it is cleared by writing '1' to it. These bits are also cleared automatically when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the Immediate Buffer Overflow Notification bit in the Control A register (CTRLA.IBON):

When CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA, until the receiver complete interrupt flag (INTFLAG.RXC) is cleared.

When CTRLA.IBON=0, the buffer overflow condition is attending data through the receive FIFO. After the received data is read, STATUS.BUFOVF will be set along with INTFLAG.RXC.

#### 35.6.2.6.3 Asynchronous Data Reception

The USART includes a clock recovery and data recovery unit for handling asynchronous data reception.

The clock recovery logic can synchronize the incoming asynchronous serial frames at the RxD pin to the internally generated baud-rate clock.

The data recovery logic samples and applies a low-pass filter to each incoming bit, thereby improving the noise immunity of the receiver.

#### 35.6.2.6.4 Asynchronous Operational Range

The operational range of the asynchronous reception depends on the accuracy of the internal baud-rate clock, the rate of the incoming frames, and the frame size (in number of bits). In addition, the operational range of the receiver is depending on the difference between the received bit rate and the internally generated baud rate. If the baud rate of an external transmitter is too high or too low compared to the internally generated baud rate, the receiver will not be able to synchronize the frames to the start bit.

There are two possible sources for a mismatch in baud rate: First, the reference clock will always have some minor instability. Second, the baud-rate generator cannot always do an exact division of the reference clock frequency to get the baud rate desired. In this case, the BAUD register value should be set to give the lowest possible error. Refer to *Clock Generation – Baud-Rate Generator* for details.

Recommended maximum receiver baud-rate errors for various character sizes are shown in the table below.

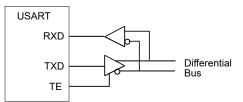

#### Figure 35-13. RS485 Bus Connection

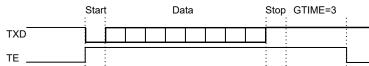

The TE pin will remain high for the complete frame including stop bit(s). If a Guard Time is programmed in the Control C register (CTRLC.GTIME), the line will remain driven after the last character completion. The following figure shows a transfer with one stop bit and CTRLC.GTIME=3.

#### Figure 35-14. Example of TE Drive with Guard Time

The Transmit Complete interrupt flag (INTFLAG.TXC) will be raised after the guard time is complete and TE goes low.

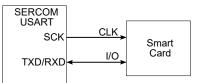

#### 35.6.3.6 ISO 7816 for Smart Card Interfacing

The SERCOM USART features an ISO/IEC 7816-compatible operating mode. This mode permits interfacing with smart cards and Security Access Modules (SAM) communicating through an ISO 7816 link. Both T=0 and T=1 protocols defined by the ISO 7816 specification are supported.

ISO 7816 is available with the following configuration:

- ISO 7816 format (CTRLA.FORM = 0x07)

- Inverse transmission and reception (CTRLA.RXINV=1 and CTRLA.TXINV=1)

- Single bidirectional data line (CTRLA.TXPO and CTRLA.RXPO configured to use the same data pin)

- Even parity (CTRLB.PMODE=0)

- 8-bit character size (CTRLB.CHSIZE=0)

- T=0 (CTRLA.CMODE=1) or T=1 (CTRLA.CMODE=0)

ISO 7816 is a half duplex communication on a single bidirectional line. The USART connects to a smart card as shown below. The output is only driven when the USART is transmitting. The USART is considered as the master of the communication as it generates the clock.

#### Figure 35-15. Connection of a Smart Card to the SERCOM USART

ISO 7816 characters are specified as 8 bits with even parity. The USART must be configured accordingly.

The USART cannot operate concurrently in both receiver and transmitter modes as the communication is unidirectional. It has to be configured according to the required mode by enabling or disabling either the receiver or the transmitter as desired. Enabling both the receiver and the transmitter at the same time in ISO 7816 mode may lead to unpredictable results.

The ISO 7816 specification defines an inverse transmission format. Data bits of the character must be transmitted on the I/O line at their negative value (CTRLA.RXINV=1 and CTRLA.TXINV=1).

#### 35.6.5 Sleep Mode Operation

The behavior in sleep mode is depending on the clock source and the Run In Standby bit in the Control A register (CTRLA.RUNSTDBY):

- Internal clocking, CTRLA.RUNSTDBY=1: GCLK\_SERCOMx\_CORE can be enabled in all sleep modes. Any interrupt can wake up the device.

- External clocking, CTRLA.RUNSTDBY=1: The Receive Complete interrupt(s) can wake up the device.

- Internal clocking, CTRLA.RUNSTDBY=0: Internal clock will be disabled, after any ongoing transfer was completed. The Receive Complete interrupt(s) can wake up the device.

- External clocking, CTRLA.RUNSTDBY=0: External clock will be disconnected, after any ongoing transfer was completed. All reception will be dropped.

#### 35.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Receiver Enable bit in the CTRLB register (CTRLB.RXEN)

- Transmitter Enable bit in the Control B register (CTRLB.TXEN)

**Note:** CTRLB.RXEN is write-synchronized somewhat differently. See also <u>35.8.2</u> CTRLB for details.

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

## 35.7 Register Summary

| Offset | Name       | Bit Pos. |          |            |              |        |           |        |             |           |

|--------|------------|----------|----------|------------|--------------|--------|-----------|--------|-------------|-----------|

|        |            | 7:0      | RUNSTDBY |            |              |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0.400  | 0x00 CTRLA |          |          | SAMPR[2:0] |              |        |           | RXINV  | TXINV       | IBON      |

| 0x00   | UXUU CIRLA | 23:16    | SAMF     | PA[1:0]    | RXPC         | D[1:0] |           |        | TXPC        | D[1:0]    |

|        |            | 31:24    |          | DORD       | CPOL         | CMODE  |           | FOR    | M[3:0]      |           |

|        |            | 7:0      |          | SBMODE     |              |        |           |        | CHSIZE[2:0] |           |

| 0x04   | CTRLB      | 15:8     |          |            | PMODE        |        |           | ENC    | SFDE        | COLDEN    |

| 0x04   | CIRLB      | 23:16    |          |            |              |        |           |        | RXEN        | TXEN      |

|        |            | 31:24    |          |            |              |        |           |        |             |           |

|        |            | 7:0      |          |            |              |        |           |        | GTIME[2:0]  |           |

| 0.409  | CTRLC      | 15:8     |          |            |              |        |           |        |             |           |

| 0x08   | CIRLC      | 23:16    |          |            | MAXITER[2:0] |        |           |        | DSNACK      | INACK     |

|        |            | 31:24    |          |            |              |        |           |        |             |           |

| 000    | DALID      | 7:0      |          | 1          | 11           | BAU    | D[7:0]    |        | 1           |           |

| 0x0C   | BAUD       | 15:8     |          |            |              | BAUI   | D[15:8]   |        |             |           |

| 0x0E   | RXPL       | 7:0      |          |            |              | RXP    | L[7:0]    |        |             |           |

| 0x0F   |            |          |          |            |              |        |           |        |             |           |

|        | Reserved   |          |          |            |              |        |           |        |             |           |

| 0x13   |            |          |          |            |              |        |           |        |             |           |

| 0x14   | INTENCLR   | 7:0      | ERROR    |            | RXBRK        | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x15   | Reserved   |          |          |            |              |        |           |        |             |           |

| 0x16   | INTENSET   | 7:0      | ERROR    |            | RXBRK        | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x17   | Reserved   |          |          |            |              |        |           |        |             |           |

| 0x18   | INTFLAG    | 7:0      | ERROR    |            | RXBRK        | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x19   | Reserved   |          |          |            |              |        |           |        |             |           |

| 0.41.0 | STATUS     | 7:0      | ITER     | TXE        | COLL         | ISF    | CTS       | BUFOVF | FERR        | PERR      |

| 0x1A   | STATUS     | 15:8     |          |            |              |        |           |        |             |           |

|        |            | 7:0      |          |            |              |        | RXERRCNT  | CTRLB  | ENABLE      | SWRST     |

| 0×10   | SYNCBUSY   | 15:8     |          |            |              |        |           |        |             |           |

| 0x1C   | STINCBUST  | 23:16    |          |            |              |        |           |        |             |           |

|        |            | 31:24    |          |            |              |        |           |        |             |           |

| 0x20   | RXERRCNT   | 7:0      |          |            |              | RXERR  | CNT[7:0]  |        |             |           |

| 0x21   |            |          |          |            |              |        |           |        |             |           |

|        | Reserved   |          |          |            |              |        |           |        |             |           |

| 0x27   |            |          |          |            |              |        |           |        |             |           |

| 0x29   | DATA       | 7:0      |          |            |              | DAT    | A[7:0]    |        |             |           |

| 0x28   | DAIA       | 15:8     |          |            |              |        |           |        |             | DATA[8:8] |

| 0x2A   |            |          |          |            |              |        |           |        |             |           |

|        | Reserved   |          |          |            |              |        |           |        |             |           |

| 0x2F   |            |          |          |            |              |        |           |        |             |           |

| 0x30   | DBGCTRL    | 7:0      |          |            |              |        |           |        |             | DBGSTOP   |

## SERCOM SPI – SERCOM Serial Peripheral Interface

| DOPO | DO     | SCK    | Slave SS | Master SS            |

|------|--------|--------|----------|----------------------|

| 0x0  | PAD[0] | PAD[1] | PAD[2]   | System configuration |

| 0x1  | PAD[2] | PAD[3] | PAD[1]   | System configuration |

| 0x2  | PAD[3] | PAD[1] | PAD[2]   | System configuration |

| 0x3  | PAD[0] | PAD[3] | PAD[1]   | System configuration |

#### Bit 8 – IBON Immediate Buffer Overflow Notification

This bit controls when the buffer overflow status bit (STATUS.BUFOVF) is set when a buffer overflow occurs.

This bit is not synchronized.

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | STATUS.BUFOVF is set when it occurs in the data stream. |

| 1     | STATUS.BUFOVF is set immediately upon buffer overflow.  |

#### Bit 7 – RUNSTDBY Run In Standby

This bit defines the functionality in standby sleep mode.

These bits are not synchronized.

| RUNSTDBY | Slave                                                                  | Master                                                                                                       |

|----------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 0x0      | Disabled. All reception is dropped, including the ongoing transaction. | Generic clock is disabled when ongoing<br>transaction is finished. All interrupts can wake<br>up the device. |

| 0x1      | Ongoing transaction continues, wake on Receive Complete interrupt.     | Generic clock is enabled while in sleep modes.<br>All interrupts can wake up the device.                     |

#### Bits 4:2 - MODE[2:0] Operating Mode

These bits must be written to 0x2 or 0x3 to select the SPI serial communication interface of the SERCOM.

0x2: SPI slave operation

0x3: SPI master operation

These bits are not synchronized.

#### Bit 1 - ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Synchronization Enable Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

## 37.6.2.4 I<sup>2</sup>C Master Operation

The I<sup>2</sup>C master is byte-oriented and interrupt based. The number of interrupts generated is kept at a minimum by automatic handling of most incidents. The software driver complexity and code size are reduced by auto-triggering of operations, and a special smart mode, which can be enabled by the Smart Mode Enable bit in the Control A register (CTRLA.SMEN).

The I<sup>2</sup>C master has two interrupt strategies.

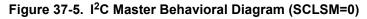

When SCL Stretch Mode (CTRLA.SCLSM) is '0', SCL is stretched before or after the acknowledge bit . In this mode the I<sup>2</sup>C master operates according to Master Behavioral Diagram (SCLSM=0). The circles labelled "Mn" (M1, M2..) indicate the nodes the bus logic can jump to, based on software or hardware interaction.

This diagram is used as reference for the description of the I<sup>2</sup>C master operation throughout the document.

APPLICATION Master Bus INTERRUPT + SCL HOLD (M1 M2 M3 (M4 s ADDRESS R/W (M1 Р Wait for R/W Ā Р IDLE M2 IDLE  $\overline{W}$ Sr М3 Α M4 DATA A/Ā Slave Bus INTERRUPT + SCL HOLD Ā M4 Software interaction The master provides data on the bus A/Ā Р IDLE М2 Addressed slave provides data on the bus A/Ā Sr **M**3 A/Ā DATA R Α

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit, as in Master Behavioral Diagram (SCLSM=1). This strategy can be used when it is not necessary to check DATA before acknowledging.

Note: I<sup>2</sup>C High-speed (*Hs*) mode requires CTRLA.SCLSM=1.

15. PAC - Peripheral Access Controller

## 41.7 Register Summary

| Offset | Name       | Bit Pos. |          |          |             |          |          |              |                |          |

|--------|------------|----------|----------|----------|-------------|----------|----------|--------------|----------------|----------|

| 0x00   | CTRLA      | 7:0      | ONDEMAND | RUNSTDBY |             |          |          |              | ENABLE         | SWRST    |

| 0x01   | CTRLB      | 7:0      |          |          |             |          |          | F            | RESCALER[2:    | 0]       |

| 0x02   | REFCTRL    | 7:0      | REFCOMP  |          |             |          |          | REFS         | EL[3:0]        |          |

| 0x03   | EVCTRL     | 7:0      |          |          | WINMONEO    | RESRDYEO | STARTINV | FLUSHINV     | STARTEI        | FLUSHEI  |

| 0x04   | INTENCLR   | 7:0      |          |          |             |          |          | WINMON       | OVERRUN        | RESRDY   |

| 0x05   | INTENSET   | 7:0      |          |          |             |          |          | WINMON       | OVERRUN        | RESRDY   |

| 0x06   | INTFLAG    | 7:0      |          |          |             |          |          | WINMON       | OVERRUN        | RESRDY   |

| 0x07   | SEQSTATUS  | 7:0      | SEQBUSY  |          |             |          |          | SEQSTATE[4:0 | )]             |          |

| 000    |            | 7:0      |          |          |             |          |          | MUXPOS[4:0]  |                |          |

| 0x08   | INPUTCTRL  | 15:8     |          |          |             |          |          | MUXNEG[4:0]  |                |          |

|        |            | 7:0      |          |          | RESS        | EL[1:0]  | CORREN   | FREERUN      | LEFTADJ        | DIFFMODE |

| 0x0A   | CTRLC      | 15:8     |          |          |             |          |          |              | WINMODE[2:0]   |          |

| 0x0C   | AVGCTRL    | 7:0      |          |          | ADJRES[2:0] |          |          | SAMPLE       | NUM[3:0]       |          |

| 0x0D   | SAMPCTRL   | 7:0      | OFFCOMP  |          |             |          | SAMPL    | _EN[5:0]     |                |          |

| 0.05   |            | 7:0      |          |          |             | WINL     | T[7:0]   |              |                |          |

| 0x0E   | WINLT      | 15:8     |          |          |             | WINLT    | [15:8]   |              |                |          |

|        |            | 7:0      |          |          |             | WINU     | T[7:0]   |              |                |          |

| 0x10   | WINUT      | 15:8     |          |          |             | WINU     | T[15:8]  |              |                |          |

|        |            | 7:0      |          |          |             | GAINCO   | DRR[7:0] |              |                |          |

| 0x12   | GAINCORR   | 15:8     |          |          |             |          |          | GAINCO       | DRR[11:8]      |          |

|        |            | 7:0      |          |          |             | OFFSETC  | ORR[7:0] |              |                |          |

| 0x14   | OFFSETCORR | 15:8     |          |          |             |          |          | OFFSETC      | ORR[11:8]      |          |

| 0x16   |            |          |          |          |             |          |          |              |                |          |

|        | Reserved   |          |          |          |             |          |          |              |                |          |

| 0x17   |            |          |          |          |             |          |          |              |                |          |

| 0x18   | SWTRIG     | 7:0      |          |          |             |          |          |              | START          | FLUSH    |

| 0x19   |            |          |          |          |             |          |          |              |                |          |

|        | Reserved   |          |          |          |             |          |          |              |                |          |

| 0x1B   |            |          |          |          |             |          |          |              |                |          |

| 0x1C   | DBGCTRL    | 7:0      |          |          |             |          |          |              |                | DBGRUN   |

| 0x1D   |            |          |          |          |             |          |          |              |                |          |

|        | Reserved   |          |          |          |             |          |          |              |                |          |

| 0x1F   |            |          |          |          |             |          |          |              |                |          |

|        |            | 7:0      | WINUT    | WINLT    | SAMPCTRL    | AVGCTRL  | CTRLC    | INPUTCTRL    | ENABLE         | SWRST    |

| 0x20   | SYNCBUSY   | 15:8     |          |          |             |          |          | SWTRIG       | OFFSETCOR<br>R | GAINCORR |

| 0x22   |            |          |          |          |             |          |          |              |                |          |

|        | Reserved   |          |          |          |             |          |          |              |                |          |

| 0x23   |            |          |          |          |             |          |          |              |                |          |

| 0.24   | RESULT     | 7:0      |          |          |             | RESU     | LT[7:0]  |              |                |          |

| 0x24   | RESULI     | 15:8     |          |          |             | RESUL    | .T[15:8] |              |                |          |

| 0x26   |            |          |          |          |             |          |          |              |                |          |

|        | Reserved   |          |          |          |             |          |          |              |                |          |

| 0x27   |            |          |          |          |             |          |          |              |                |          |

#### 41.8.3 Reference Control

| Name:     | REFCTRL                                |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 7       | 6 | 5 | 4 | 3   | 2     | 1       | 0   |

|--------|---------|---|---|---|-----|-------|---------|-----|

|        | REFCOMP |   |   |   |     | REFSE | EL[3:0] |     |

| Access | R/W     |   |   |   | R/W | R/W   | R/W     | R/W |

| Reset  | 0       |   |   |   | 0   | 0     | 0       | 0   |

#### Bit 7 – REFCOMP Reference Buffer Offset Compensation Enable

The gain error can be reduced by enabling the reference buffer offset compensation. This will increase the start-up time of the reference.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Reference buffer offset compensation is disabled. |

| 1     | Reference buffer offset compensation is enabled.  |

### Bits 3:0 - REFSEL[3:0] Reference Selection

These bits select the reference for the ADC.

| Value | Name    | Description                                                                                      |

|-------|---------|--------------------------------------------------------------------------------------------------|

| 0x0   | INTREF  | Internal variable reference voltage, refer to the SUPC.VREF register for voltage reference value |

| x01   | INTVCC0 | 1/1.6 VDDANA                                                                                     |

| 0x2   | INTVCC1 | 1/2 VDDANA (only for VDDANA > 2.0V)                                                              |

| 0x3   | VREFA   | External reference                                                                               |

| 0x4   | VREFB   | External reference                                                                               |

| 0x5   | INTVCC2 | VDDANA                                                                                           |

| 0x6 - |         | Reserved                                                                                         |

| 0xF   |         |                                                                                                  |

#### 42.8.11 Scaler n

| Name:     | SCALER               |

|-----------|----------------------|

| Offset:   | 0x0C + n*0x01 [n=01] |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5          | 4   | 3   | 2   | 1   | 0   |

|--------|---|---|------------|-----|-----|-----|-----|-----|

|        |   |   | VALUE[5:0] |     |     |     |     |     |

| Access |   |   | R/W        | R/W | R/W | R/W | R/W | R/W |

| Reset  |   |   | 0          | 0   | 0   | 0   | 0   | 0   |

#### Bits 5:0 - VALUE[5:0] Scaler Value

These bits define the scaling factor for channel n of the  $V_{DD}$  voltage scaler. The output voltage,  $V_{SCALE}$ , is:

$V_{\text{SCALE}} = \frac{V_{\text{DD}} \cdot (\text{VALUE}+1)}{64}$

**OPAMP – Operational Amplifier Controller**

| OPAMPCTRL0.POTMUX | OPAMPCTRL2.POTMUX | GAIN     |

|-------------------|-------------------|----------|

| 0x7               | Reserved          | Reserved |

| 0x6               | 0x0               | 1/7      |

| 0x5               | Reserved          | Reserved |

| 0x4               | 0x1               | 1/3      |

| 0x3               | Reserved          | Reserved |

| 0x2               | 0x2               | 1        |

| 0x1               | 0x4               | 3        |

| 0x0               | 0x6               | 7        |

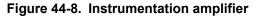

#### Table 44-10. Instrumentation Amplifier Gain Selection

**Note:** Either the DAC or GND must be the reference, selected by the OPAMPCTRL0.RES1MUX bits. Refer to the OPAMP Control 'x' register (44.8.3 OPAMPCTRL) for details.

#### 44.6.10.8 High Gain Instrumentation Amplifier

In this mode, OPAMP0 and OPAMP1 are configured as non inverting amplifiers [Stage 1]. OPAMP2 is configured as difference amplifier[Stage 2]. Total gain of the instrumentation amplifier is product of gains of stage 1 and stage 2. The OPAMPCTRLx and RESCTRL registers can be configured as follows:

## **Electrical Characteristics**

| Mode | Conditions | Regulator Mode | Vcc  | Та   | Тур.  | Max.   | Units |

|------|------------|----------------|------|------|-------|--------|-------|

| OFF  |            |                | 1.8V | 25°C | 34.6  | 54.4   | nA    |

|      |            |                |      | 85°C | 595.7 | 1197.3 |       |

|      |            |                | 3.3V | 25°C | 61.2  | 89.1   |       |

|      |            |                |      | 85°C | 796.1 | 1622.8 |       |

## 46.8 Wake-Up Time

Conditions:

- VDDIO/VDDANA = 3.3V

- LDO Regulation mode

- CPU clock = OSC16M @ 4 MHz

- One Wait-state

- Cache enabled

- Flash Fast Wake-up enabled (NVMCTRL.CTRLB.FWUP = 1)

- Flash in WAKEUPINSTANT mode (NVMCTRL.CTRLB.SLEEPPRM = 1)

Measurement Method:

For Idle and Standby, the CPU sets an I/O by writing PORT->IOBUS without jumping in an interrupt handler (Cortex M23 register PRIMASK = 1). The wake-up time is measured between the edge of the wake-up input signal and the edge of the GPIO pin.

For Off mode, the exit of the mode is done through the reset pin, the time is measured between the falling edge of the RESETN signal (with the minimum reset pulse length), and the set of the I/O which is done by the first executed instructions after Reset.

| Sleep Mode | Condition                                                                            |                          |     | Unit |

|------------|--------------------------------------------------------------------------------------|--------------------------|-----|------|

| Idle       | PL2 or PL0                                                                           | _2 or PL0                |     |      |

| Standby    | PL0                                                                                  | PDSW domain in retention |     |      |

|            |                                                                                      | PDSW domain in active    | 2.6 |      |

|            | ·                                                                                    | PDSW domain in retention | 76  |      |

|            | Voltage scaling at default values:<br>SUPC >VREG.VSVSTEP=0<br>SUPC > VREG.VSPER=0    | PDSW domain in active    | 75  |      |

|            | PL2                                                                                  | PDSW domain in retention | 16  |      |

|            | Voltage scaling at fastest setting:<br>SUPC > VREG.VSVSTEP=15<br>SUPC > VREG.VSPER=0 | PDSW domain in active    | 15  |      |

| OFF        | L10 with BOOTOPT=0                                                                   |                          | 3.2 | ms   |