#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d16a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 15.7.1 Write Control

|        | Name:<br>Offset:<br>Reset:<br>Property: | WRCTRL<br>0x00<br>0x00000000<br>- |          |          |          |          |          |          |

|--------|-----------------------------------------|-----------------------------------|----------|----------|----------|----------|----------|----------|

| Bit    | 31                                      | 30                                | 29       | 28       | 27       | 26       | 25       | 24       |

|        |                                         |                                   |          |          |          |          |          |          |

| Access |                                         |                                   |          |          |          |          |          |          |

| Reset  |                                         |                                   |          |          |          |          |          |          |

|        |                                         |                                   |          |          |          |          |          |          |

| Bit    | 23                                      | 22                                | 21       | 20       | 19       | 18       | 17       | 16       |

|        |                                         |                                   |          | KEY      | [7:0]    |          |          |          |

| Access | RW/RW/RW                                | RW/RW/RW                          | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW |

| Reset  | 0                                       | 0                                 | 0        | 0        | 0        | 0        | 0        | 0        |

|        |                                         |                                   |          |          |          |          |          |          |

| Bit    | 15                                      | 14                                | 13       | 12       | 11       | 10       | 9        | 8        |

|        |                                         |                                   |          | PERIE    | D[15:8]  |          |          |          |

| Access | RW/RW/RW                                | RW/RW/RW                          | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW |

| Reset  | 0                                       | 0                                 | 0        | 0        | 0        | 0        | 0        | 0        |

|        |                                         |                                   |          |          |          |          |          |          |

| Bit    | 7                                       | 6                                 | 5        | 4        | 3        | 2        | 1        | 0        |

|        |                                         |                                   |          | PERI     | D[7:0]   |          |          |          |

| Access | RW/RW/RW                                | RW/RW/RW                          | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW |

| Reset  | 0                                       | 0                                 | 0        | 0        | 0        | 0        | 0        | 0        |

#### **Bits 23:16 – KEY[7:0]** Peripheral Access Control Key These bits define the peripheral access control key:

| Value | Name  | Description                                                             |

|-------|-------|-------------------------------------------------------------------------|

| 0x0   | OFF   | No action                                                               |

| 0x1   | CLEAR | Clear the peripheral write control                                      |

| 0x2   | SET   | Set the peripheral write control                                        |

| 0x3   | LOCK  | Set and lock the peripheral write control until the next hardware reset |

#### Bits 15:0 – PERID[15:0] Peripheral Identifier

The PERID represents the peripheral whose control is changed using the WRCTRL.KEY. The Peripheral Identifier is calculated by the following formula:

$PERID = 32^*$  BridgeNumber + N

Where BridgeNumber represents the Peripheral Bridge Number (0 for Peripheral Bridge A, 1 for Peripheral Bridge B, etc.). N represents the peripheral index from the respective Peripheral Bridge Number, which can be retrieved in the *Peripherals Configuration Summary* table:

# 17.6 Power Consumption vs. Speed

When targeting for either a low-power or a fast acting system, some considerations have to be taken into account due to the nature of the asynchronous clocking of the peripherals:

If clocking a peripheral with a very low clock, the active power consumption of the peripheral will be lower. At the same time the synchronization to the synchronous (CPU) clock domain is dependent on the peripheral clock speed, and will take longer with a slower peripheral clock. This will cause worse response times and longer synchronization delays.

# 17.7 Clocks after Reset

On any Reset the synchronous clocks start to their initial state:

- OSC16M is enabled and configured to run at 4MHz

- Generic Clock Generator 0 uses OSC16M as source and generates GCLK\_MAIN and CLK\_MAIN

- CPU and BUS clocks are undivided

On a Power-on Reset, the 32KHz clock sources are reset and the GCLK module starts to its initial state:

- All Generic Clock Generators are disabled except Generator 0

- All Peripheral Channels in GCLK are disabled.

On a User Reset the GCLK module starts to its initial state, except for:

• Generic Clocks that are write-locked, i.e., the according WRTLOCK is set to 1 prior to Reset

#### 22. PM - Power Manager

#### 19.5.3 Clocks

The MCLK bus clock (CLK\_MCLK\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_MCLK\_APB can be found in the Peripheral Clock Masking section. If this clock is disabled, it can only be re-enabled by a reset.

The Generic Clock GCLK\_MAIN or the DFLLULP Clock CLK\_DFLLULP is required to generate the Main Clocks. GCLK\_MAIN is configured in the Generic Clock Controller, and can be re-configured by the user if needed. CLK\_DFLLULP is configured in the Oscillators Controller (OSCCTRL).

#### **Related Links**

18. GCLK - Generic Clock Controller19.6.2.6 Peripheral Clock Masking

#### 19.5.3.1 Main Clock

The main clock CLK\_MAIN is the common source for the synchronous clocks. This is fed into the common 8-bit prescaler that is used to generate synchronous clocks to the CPU, AHBx, and APBx modules.

#### 19.5.3.2 CPU Clock

The CPU clock (CLK\_CPU) is routed to the CPU. Halting the CPU clock inhibits the CPU from executing instructions.

#### 19.5.3.3 APBx and AHBx Clock

The APBx clocks (CLK\_APBx) and the AHBx clocks (CLK\_AHBx) are the root clock source used by modules requiring a clock on the APBx and the AHBx bus. These clocks are always synchronous to the CPU clock, and can run even when the CPU clock is turned off in sleep mode. A clock gater is inserted after the common APB clock to gate any APBx clock of a module on APBx bus, as well as the AHBx clock.

#### 19.5.3.4 Clock Domains

The device has these synchronous clock domains:

• CPU synchronous clock domain (CPU Clock Domain). Frequency is f<sub>CPU</sub>.

See also the related links for the clock domain partitioning.

#### **Related Links**

19.6.2.6 Peripheral Clock Masking

#### 19.5.4 DMA

Not applicable.

#### 19.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the MCLK interrupt requires the Interrupt Controller to be configured first.

#### 19.5.6 Events

Not applicable.

#### 25.6.3.4 1.2V Brown-Out Detector (BOD12)

The BOD12 is calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration must not be changed to assure the correct behavior of the BOD12. The BOD12 generates a reset when 1.2V crosses below the preset brown-out level. The BOD12 is always disabled in Standby Sleep mode.

#### 25.6.3.5 Continuous Mode

Continuous mode is the default mode for BOD33.

The BOD33 is continuously monitoring the VDD supply voltage if it is enabled (BOD33.ENABLE=1) and if the BOD33 Configuration bit in the BOD33 register is cleared (BOD33.ACTCFG=0 for active mode, BOD33.STDBYCFG=0 for standby mode).

#### 25.6.3.6 Sampling Mode

The Sampling Mode is a low-power mode where the BOD33 is being repeatedly enabled on a sampling clock's ticks. The BOD33 will monitor the supply voltage for a short period of time and then go to a low-power disabled state until the next sampling clock tick.

Sampling mode is enabled in Active mode for BOD33 by writing the ACTCFG bit (BOD33.ACTCFG=1). Sampling mode is enabled in Standby mode by writing to the STDBYCFG bit (BOD33.STBYCFG=1). The frequency of the clock ticks (F<sub>clksampling</sub>) is controlled by the Prescaler Select bit groups in the BOD33 register (BOD33.PSEL).

$$F_{clksampling} = \frac{F_{clkprescaler}}{2^{(PSEL+1)}}$$

The prescaler signal ( $F_{clkprescaler}$ ) is a 1KHz clock, output by the 32KHz Ultra Low Power Oscillator OSCULP32K.

As the sampling clock is different from the APB clock domain, synchronization among the clocks is necessary. See also 25.6.6 Synchronization.

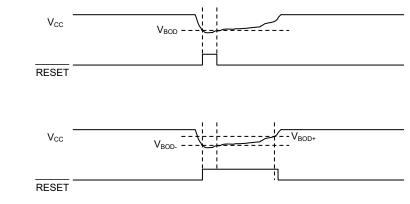

#### 25.6.3.7 Hysteresis

A hysteresis on the trigger threshold of a BOD will reduce the sensitivity to ripples on the monitored voltage: instead of switching  $\overrightarrow{\text{RESET}}$  at each crossing of V<sub>BOD</sub>, the thresholds for switching  $\overrightarrow{\text{RESET}}$  on and off are separated (V<sub>BOD</sub>, and V<sub>BOD</sub>, respectively).

#### Figure 25-2. BOD Hysteresis Principle

Hysteresis OFF:

Hysteresis ON:

Enabling the BOD33 hysteresis by writing the Hysteresis bit in the BOD33 register (BOD33.HYST) to '1' will add hysteresis to the BOD33 threshold level.

#### 27.12.10 Clock Value in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | CLOCK                                                       |

|-----------|-------------------------------------------------------------|

| Offset:   | 0x18                                                        |

| Reset:    | 0x0000000                                                   |

| Property: | PAC Write-Protection, Write-Synchronized, Read-Synchronized |

| Bit    | 31   | 30      | 29     | 28     | 27          | 26      | 25  | 24        |

|--------|------|---------|--------|--------|-------------|---------|-----|-----------|

|        |      |         | YEAF   | ٦[5:0] |             |         | MON | TH[3:2]   |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0       | 0   | 0         |

|        |      |         |        |        |             |         |     |           |

| Bit    | 23   | 22      | 21     | 20     | 19          | 18      | 17  | 16        |

|        | MON  | TH[1:0] |        |        | DAY[4:0]    |         |     | HOUR[4:4] |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0       | 0   | 0         |

|        |      |         |        |        |             |         |     |           |

| Bit    | 15   | 14      | 13     | 12     | 11          | 10      | 9   | 8         |

|        |      | HOU     | R[3:0] |        | MINUTE[5:2] |         |     |           |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0       | 0   | 0         |

|        |      |         |        |        |             |         |     |           |

| Bit    | 7    | 6       | 5      | 4      | 3           | 2       | 1   | 0         |

|        | MINU | TE[1:0] |        |        | SECO        | ND[5:0] |     |           |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0       | 0   | 0         |

#### Bits 31:26 - YEAR[5:0] Year

The year offset with respect to the reference year (defined in software).

The year is considered a leap year if YEAR[1:0] is zero.

#### Bits 25:22 - MONTH[3:0] Month

1 – January

2 – February

...

12 - December

#### Bits 21:17 - DAY[4:0] Day

Day starts at 1 and ends at 28, 29, 30, or 31, depending on the month and year.

#### Bits 16:12 - HOUR[4:0] Hour

When CTRLA.CLKREP=0, the Hour bit group is in 24-hour format, with values 0-23. When CTRLA.CLKREP=1, HOUR[3:0] has values 1-12, and HOUR[4] represents AM (0) or PM (1).

# **Bits 11:6 – MINUTE[5:0]** Minute 0 – 59

© 2018 Microchip Technology Inc.

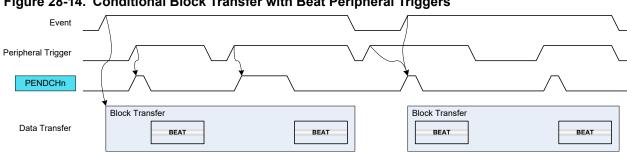

### Figure 28-14. Conditional Block Transfer with Beat Peripheral Triggers

### **Channel Suspend**

The event input is used to suspend an ongoing channel operation. The event is acknowledged when the current AHB access is completed. For further details on Channel Suspend, refer to 28.6.3.2 Channel Suspend.

#### **Channel Resume**

The event input is used to resume a suspended channel operation. The event is acknowledged as soon as the event is received and the Channel Suspend Interrupt Flag (CHINTFLAG.SUSP) is cleared. For further details refer to 28.6.3.2 Channel Suspend.

#### Skip Next Block Suspend

This event can be used to skip the next block suspend action. If the channel is suspended before the event rises, the channel operation is resumed and the event is acknowledged. If the event rises before a suspend block action is detected, the event is kept until the next block suspend detection. When the block transfer is completed, the channel continues the operation (not suspended) and the event is acknowledged.

#### 28.6.3.5 Event Output Selection

Event output selection is available only for the four least significant DMA channels. The pulse width of an event output from a channel is one AHB clock cycle.

The output of channel events is enabled by writing a '1' to the Channel Event Output Enable bit in the Control B register (CHCTRLB.EVOE). The event output cause is selected by writing to the Event Output Selection bits in the Block Transfer Control register (BTCTRL.EVOSEL). It is possible to generate events after each block transfer (BTCTRL.EVOSEL=0x1) or beat transfer (BTCTRL.EVOSEL=0x3). To enable an event being generated when a transaction is complete, the block event selection must be set in the last transfer descriptor only.

The figure Figure 28-15 shows an example where the event output generation is enabled in the first block transfer, and disabled in the second block.

(ASYNCH.ASYNCH[x]). The EIC edge detection is operated synchronously when the Asynchronous Control Mode bit (ASYNCH.ASYNCH[x]) is '0' (default value). It is operated asynchronously when ASYNCH.ASYNCH[x] is written to '1'.

In *Synchronous Edge Detection Mode*, the external interrupt (EXTINT) or the non-maskable interrupt (NMI) pins are sampled using the EIC clock as defined by the Clock Selection bit in the Control A register (CTRLA.CKSEL). The External Interrupt flag (INTFLAG.EXTINT[x]) or Non-Maskable Interrupt flag (NMIFLAG.NMI) is set when the last sampled state of the pin differs from the previously sampled state. In this mode, the EIC clock is required.

The Synchronous Edge Detection Mode can be used in Idle and Standby sleep modes.

In *Asynchronous Edge Detection Mode*, the external interrupt (EXTINT) pins or the non-maskable interrupt (NMI) pins set the External Interrupt flag or Non-Maskable Interrupt flag (INTFLAG.EXTINT[x] or NMIFLAG) directly. In this mode, the EIC clock is not requested.

The asynchronous edge detection mode can be used in Idle and Standby sleep modes.

#### 29.6.4.3 Interrupt Pin Debouncing

The external interrupt pin (EXTINT) edge detection can use a debouncer to improve input noise immunity. When selected, the debouncer can work in the synchronous mode or the asynchronous mode, depending on the configuration of the ASYNCH.ASYNCH[x] bit for the pin. The debouncer uses the EIC clock as defined by the bit CTRLA.CKSEL to clock the debouncing circuitry. The debouncing time frame is set with the debouncer prescaler DPRESCALER.DPRESCALERn, which provides the *low frequency clock* tick that is used to reject higher frequency signals.

The debouncing mode for pin EXTINT x can be selected only if the Sense bits in the Configuration y register (CONFIGy.SENSEx) are set to RISE, FALL or BOTH. If the debouncing mode for pin EXTINT x is selected, the filter mode for that pin (CONFIGy.FILTENx) can not be selected.

The debouncer manages an internal "valid pin state" that depends on the external interrupt (EXTINT) pin transitions, the debouncing mode and the debouncer prescaler frequency. The valid pin state reflects the pin value after debouncing. The external interrupt pin (EXTINT) is sampled continously on EIC clock. The sampled value is evaluated on each *low frequency clock* tick to detect a transitional edge when the sampled value is different of the current valid pin state. The sampled value is evaluated on each EIC clock when DPRESCALER.TICKON=0 or on each *low frequency clock* tick when DPRESCALER.TICKON=1, to detect a bounce when the sampled value is equal to the current valid pin state. Transitional edge detection increments the transition counter of the EXTINT pin, while bounce detection resets the transition counter. The transition counter must exceed the transition count threshold as defined by the DPRESCALER.STATESn bitfield. In the synchronous mode the threshold is 4 when DPRESCALER.STATESn=0 or 8 when DPRESCALER.STATESn=1. In the asynchronous mode the threshold is 4.

The valid pin state for the pins can be accessed by reading the register PINSTATE for both synchronous or asynchronous debouncing mode.

**Synchronous edge detection** In this mode the external interrupt (EXTINT) pin is sampled continously on EIC clock.

- 1. A pin edge transition will be validated when the sampled value is consistently different of the current valid pin state for 4 (or 8 depending on bit DPRESCALER.STATESn) consecutive ticks of the low frequency clock.

- 2. Any pin sample, at the *low frequency clock* tick rate, with a value opposite to the current valid pin state will increment the transition counter.

# SAM L10/L11 Family

TRAM - TrustRAM

| Offset | Name     | Bit Pos. |             |

|--------|----------|----------|-------------|

|        |          | 7:0      | DATA[7:0]   |

| 0x0144 | DAMAZ    | 15:8     | DATA[15:8]  |

| 0x0144 | RAM17    | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0148 | RAM18    | 15:8     | DATA[15:8]  |

| 0x0146 | NAIVITO  | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x014C | RAM19    | 15:8     | DATA[15:8]  |

| 0x014C | RAIN19   | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0150 | RAM20    | 15:8     | DATA[15:8]  |

| 0x0150 | RAIVIZU  | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0154 | RAM21    | 15:8     | DATA[15:8]  |

| 0x0154 | RAIVIZ I | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0158 | RAM22    | 15:8     | DATA[15:8]  |

| 0.0130 | RAM22    | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x015C | RAM23    | 15:8     | DATA[15:8]  |

| 0.0130 | TAWI23   | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0160 | RAM24    | 15:8     | DATA[15:8]  |

| 0,0100 |          | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0164 | RAM25    | 15:8     | DATA[15:8]  |

| 0,0101 | 10 10 20 | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x0168 | RAM26    | 15:8     | DATA[15:8]  |

| 0.0100 |          | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

|        |          | 7:0      | DATA[7:0]   |

| 0x016C | RAM27    | 15:8     | DATA[15:8]  |

| 0.0100 | 10.0021  | 23:16    | DATA[23:16] |

|        |          | 31:24    | DATA[31:24] |

| 0x0170 | RAM28    | 7:0      | DATA[7:0]   |

| 0.0170 |          | 15:8     | DATA[15:8]  |

#### 32.8.12 Event Input Control

| Name:     | EVCTRL                       |

|-----------|------------------------------|

| Offset:   | 0x2C                         |

| Reset:    | 0x0000000                    |

| Property: | PAC Write-Protection, Secure |

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to four input event pins for each PORT group. Each byte of this register addresses one Event input pin.

| Bit    | 31      | 30      | 29      | 28      | 27      | 26        | 25      | 24      |

|--------|---------|---------|---------|---------|---------|-----------|---------|---------|

|        | PORTEIx | EVAC    | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |         |         |         |         |           |         |         |

| Bit    | 23      | 22      | 21      | 20      | 19      | 18        | 17      | 16      |

|        | PORTEIX | EVAC    | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |         |         |         |         |           |         |         |

| Bit    | 15      | 14      | 13      | 12      | 11      | 10        | 9       | 8       |

|        | PORTEIX | EVAC    | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |         |         |         |         |           |         |         |

| Bit    | 7       | 6       | 5       | 4       | 3       | 2         | 1       | 0       |

|        | PORTEIX | EVAC    | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |         |         |         |         |           |         |         |

Bits 31,23,15,7 – PORTEIx PORT Event Input Enable x [x = 3..0]

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The event action x (EVACTx) will not be triggered on any incoming event. |

| 1     | The event action x (EVACTx) will be triggered on any incoming event.     |

# Bits 30:29, 22:21,14:13,6:5 – EVACTx PORT Event Action x [x = 3..0]

These bits define the event action the PORT will perform on event input x. See also Table 32-4.

Bits 28:24,20:16,12:8,4:0 – PIDx PORT Event Pin Identifier x [x = 3..0]

These bits define the I/O pin on which the event action will be performed, according to Table 32-5.

#### 32.8.19 Security Attribution Check

| Name:     | NSCHK                |

|-----------|----------------------|

| Offset:   | 0x70                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

This register allows the user to select one or more pins to check their security attribution as non-secured.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31       | 30       | 29       | 28       | 27       | 26       | 25       | 24       |

|--------|----------|----------|----------|----------|----------|----------|----------|----------|

|        |          |          |          | NSCH     | ([31:24] |          |          |          |

| Access | RW/RW/RW |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

|        |          |          |          |          |          |          |          |          |

| Bit    | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|        |          |          |          | NSCH     | ([23:16] |          |          |          |

| Access | RW/RW/RW |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

|        |          |          |          |          |          |          |          |          |

| Bit    | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        |

|        |          |          |          | NSCH     | K[15:8]  |          |          |          |

| Access | RW/RW/RW |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

|        |          |          |          |          |          |          |          |          |

| Bit    | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|        |          |          |          | NSCH     | IK[7:0]  |          |          |          |

| Access | RW/RW/RW |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

#### Bits 31:0 – NSCHK[31:0] Port Security Attribution Check

These bits select the individual pins for security attribution check. If any pin selected in NSCHK has the corresponding bit in NONSEC set to the opposite value, then the NSCHK interrupt flag will be set.

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | 0-to-1 transition will be detected on corresponding NONSEC bit. |

| 1     | 1-to-0 transition will be detected on corresponding NONSEC bit. |

#### 33.7.8 Channel n Control

| Name:     | CHANNEL                          |

|-----------|----------------------------------|

| Offset:   | 0x20 + n*0x08 [n=07]             |

| Reset:    | 0x00008000                       |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding channel (CHANNELx) is set as Non-Secured in the NONSECCHAN register.

This register allows the user to configure channel n. To write to this register, do a single, 32-bit write of all the configuration data.

| Bit    | 31        | 30        | 29        | 28          | 27        | 26        | 25        | 24        |  |

|--------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|--|

|        |           |           |           |             |           |           |           |           |  |

| Access |           |           |           |             |           |           |           |           |  |

| Reset  |           |           |           |             |           |           |           |           |  |

|        |           |           |           |             |           |           |           |           |  |

| Bit    | 23        | 22        | 21        | 20          | 19        | 18        | 17        | 16        |  |

|        |           |           |           |             |           |           |           |           |  |

| Access |           |           |           |             |           |           |           |           |  |

| Reset  |           |           |           |             |           |           |           |           |  |

|        |           |           |           |             |           |           |           |           |  |

| Bit    | 15        | 14        | 13        | 12          | 11        | 10        | 9         | 8         |  |

|        | ONDEMAND  | RUNSTDBY  |           | EDGSEL[1:0] |           | PATH      | H[1:0]    |           |  |

| Access | RW/RW*/RW | RW/RW*/RW |           |             | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |

| Reset  | 1         | 0         |           |             | 0         | 0         | 0         | 0         |  |

|        |           |           |           |             |           |           |           |           |  |

| Bit    | 7         | 6         | 5         | 4           | 3         | 2         | 1         | 0         |  |

|        |           |           |           | EVGEN[5:0]  |           |           |           |           |  |

| Access |           |           | RW/RW*/RW | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |

| Reset  |           |           | 0         | 0           | 0         | 0         | 0         | 0         |  |

#### Bit 15 – ONDEMAND Generic Clock On Demand

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock |

|       | source is enabled.                                                                       |

| 1     | Generic clock is requested on demand while an event is handled                           |

#### Bit 14 – RUNSTDBY Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                      |

| 1     | The channel is not stopped in standby sleep mode and depends on the |

|       | CHANNEL.ONDEMAND bit.                                               |

# 35.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

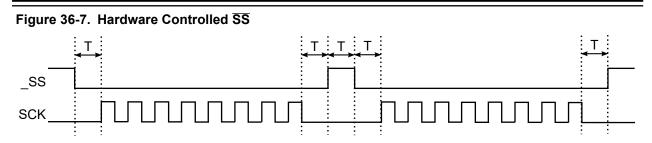

T = 1 to 2 baud cycles

When CTRLB.MSSEN=0, the  $\overline{SS}$  pin(s) is/are controlled by user software and normal GPIO.

#### 36.6.3.6 Slave Select Low Detection

In slave mode, the SPI can wake the CPU when the slave select  $(\overline{SS})$  goes low. When the Slave Select Low Detect is enabled (CTRLB.SSDE=1), a high-to-low transition will set the Slave Select Low interrupt flag (INTFLAG.SSL) and the device will wake up if applicable.

#### 36.6.4 DMA, Interrupts, and Events

#### Table 36-4. Module Request for SERCOM SPI

| Condition                 | Request                                       |           |       |  |  |  |  |  |

|---------------------------|-----------------------------------------------|-----------|-------|--|--|--|--|--|

|                           | DMA                                           | Interrupt | Event |  |  |  |  |  |

| Data Register Empty (DRE) | Yes<br>(request cleared when data is written) | Yes       | NA    |  |  |  |  |  |

| Receive Complete (RXC)    | Yes<br>(request cleared when data is read)    | Yes       |       |  |  |  |  |  |

| Transmit Complete (TXC)   | NA                                            | Yes       | •     |  |  |  |  |  |

| Slave Select low (SSL)    | NA                                            | Yes       |       |  |  |  |  |  |

| Error (ERROR)             | NA                                            | Yes       |       |  |  |  |  |  |

#### 36.6.4.1 DMA Operation

The SPI generates the following DMA requests:

- Data received (RX): The request is set when data is available in the receive FIFO. The request is cleared when DATA is read.

- Data transmit (TX): The request is set when the transmit buffer (TX DATA) is empty. The request is cleared when DATA is written.

#### 36.6.4.2 Interrupts

The SPI has the following interrupt sources. These are asynchronous interrupts, and can wake up the device from any sleep mode:

- Data Register Empty (DRE)

- Receive Complete (RXC)

- Transmit Complete (TXC)

- Slave Select Low (SSL)

- Error (ERROR)

#### 38.7.3.3 Control B Set

Name:CTRLBSETOffset:0x05Reset:0x00Property:PAC Write-Protection, Read-synchronized, Write-Synchronized

This register allows the user to set bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Clear register (CTRLBCLR).

| Bit    | 7   | 6        | 5   | 4 | 3 | 2       | 1    | 0   |

|--------|-----|----------|-----|---|---|---------|------|-----|

|        |     | CMD[2:0] |     |   |   | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W |   |   | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   |   |   | 0       | 0    | 0   |

#### Bits 7:5 – CMD[2:0] Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a value different from 0x0 to these bits will issue a command for execution.

| Value | Name      | Description                               |

|-------|-----------|-------------------------------------------|

| 0x0   | NONE      | No action                                 |

| 0x1   | RETRIGGER | Force a start, restart or retrigger       |

| 0x2   | STOP      | Force a stop                              |

| 0x3   | UPDATE    | Force update of double buffered registers |

| 0x4   | READSYNC  | Force a read synchronization of COUNT     |

#### Bit 2 - ONESHOT One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will enable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

#### Bit 1 – LUPD Lock Update

This bit controls the update operation of the TC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the LUPD bit.

Equations 3 is a coarse value, because we assumed that  $INT1V_c=1V$ . To achieve a more accurate result, we replace  $INT1V_c$  with an interpolated value  $INT1V_m$ . We use the two data pairs (*temp*<sub>R</sub>,  $INT1V_R$ ) and (*temp*<sub>H</sub>,  $INT1V_H$ ) and yield:

$$(\frac{\text{INT1V}_m - \text{INT1V}_R}{temp_m - temp_R}) = (\frac{\text{INT1V}_H - \text{INT1VV}_R}{temp_H - temp_R})$$

Using the coarse temperature value  $temp_c$ , we can infer a more precise INT1V<sub>m</sub> value during the ADC conversion as:

#### [Equation 4]

$$INT1V_m = INT1V_R + \left(\frac{(INT1V_H - INT1V_R) \cdot (temp_C - temp_R)}{(temp_H - temp_R)}\right)$$

Back to Equation 3, we replace the simple  $INT1V_c=1V$  by the more precise  $INT1V_m$  of Equation 4, and find a more accurate temperature value *temp*<sub>f</sub>:

#### [Equation 5]

$$temp_{f} = temp_{R} + \left[\frac{\{ADC_{m} \cdot \text{INT1V}_{m} - (ADC_{R} \cdot \text{INT1V}_{R})\} \cdot (temp_{H} - temp_{R})}{\{(ADC_{H} \cdot \text{INT1V}_{H}) - (ADC_{R} \cdot \text{INT1V}_{R})\}}\right]$$

#### 41.6.4 DMA Operation

The ADC generates the following DMA request:

• Result Conversion Ready (RESRDY): the request is set when a conversion result is available and cleared when the RESULT register is read. When the averaging operation is enabled, the DMA request is set when the averaging is completed and result is available.

#### 41.6.5 Interrupts

The ADC has the following interrupt sources:

- Result Conversion Ready: RESRDY

- Window Monitor: WINMON

- Overrun: OVERRUN

These interrupts, except the OVERRUN interrupt, are asynchronous wake-up sources. See *Sleep Mode Controller* for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the ADC is reset. See INTFLAG register for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

22.6.3.3 Sleep Mode Controller

#### 41.8.16 Offset Correction

| Name:     | OFFSETCORR                               |

|-----------|------------------------------------------|

| Offset:   | 0x14                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15  | 14  | 13  | 12     | 11        | 10      | 9         | 8   |

|--------|-----|-----|-----|--------|-----------|---------|-----------|-----|

|        |     |     |     |        |           | OFFSETC | ORR[11:8] |     |

| Access |     |     |     |        | R/W       | R/W     | R/W       | R/W |

| Reset  |     |     |     |        | 0         | 0       | 0         | 0   |

|        |     |     |     |        |           |         |           |     |

| Bit    | 7   | 6   | 5   | 4      | 3         | 2       | 1         | 0   |

|        |     |     |     | OFFSET | CORR[7:0] |         |           |     |

| Access | R/W | R/W | R/W | R/W    | R/W       | R/W     | R/W       | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0         | 0       | 0         | 0   |

Bits 11:0 - OFFSETCORR[11:0] Offset Correction Value

If CTRLC.CORREN=1, these bits define how the ADC conversion result is compensated for offset error before being written to the Result register. This OFFSETCORR value is in two's complement format.

# 43.7 Register Summary

| Offset           | Name     | Bit Pos. |        |          |        |       |          |         |         |          |

|------------------|----------|----------|--------|----------|--------|-------|----------|---------|---------|----------|

| 0x00             | CTRLA    | 7:0      | F      | RUNSTDBY |        |       |          |         | ENABLE  | SWRST    |

| 0x01             | CTRLB    | 7:0      | REFSEL | [1:0]    | DITHER |       | VPD      | LEFTADJ | IOEN    | EOEN     |

| 0x02             | EVCTRL   | 7:0      |        |          |        |       |          | INVEI   | EMPTYEO | STARTEI  |

| 0x03             | Reserved |          |        |          |        |       |          |         |         |          |

| 0x04             | INTENCLR | 7:0      |        |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x05             | INTENSET | 7:0      |        |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x06             | INTFLAG  | 7:0      |        |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x07             | STATUS   | 7:0      |        |          |        |       |          |         |         | READY    |

| 0x08             | DATA     | 7:0      |        |          |        | DAT   | A[7:0]   |         |         |          |

| 0x06             | DATA     | 15:8     |        |          |        | DATA  | [15:8]   |         |         |          |

| 0x0A<br><br>0x0B | Reserved |          |        |          |        |       |          |         |         |          |

| 0.00             | DATADUS  | 7:0      |        |          |        | DATAB | UF[7:0]  |         | 1       |          |

| 0x0C             | DATABUF  | 15:8     |        |          |        | DATAB | UF[15:8] |         |         |          |

| 0x0E<br><br>0x0F | Reserved |          |        |          |        |       |          |         |         |          |

|                  |          | 7:0      |        |          |        |       | DATABUF  | DATA    | ENABLE  | SWRST    |

| 0x10             | SYNCBUSY | 15:8     |        |          |        |       |          |         |         |          |

| 0.10             | 31100031 | 23:16    |        |          |        |       |          |         |         |          |

|                  |          | 31:24    |        |          |        |       |          |         |         |          |

| 0x14             |          |          |        |          |        |       |          |         |         |          |

| <br>0x17         | Reserved |          |        |          |        |       |          |         |         |          |

| 0x18             | DBGCTRL  | 7:0      |        |          |        |       |          |         |         | DBGRUN   |

## 43.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 43.5.8 Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to 43.6.7 Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

© 2018 Microchip Technology Inc.

# SAM L10/L11 Family

# **Electrical Characteristics**

| Symbol             | Parameter                | Conditions                                        | Min. | Тур. | Max   | Units |

|--------------------|--------------------------|---------------------------------------------------|------|------|-------|-------|

|                    |                          | F = 8MHz - CL=20 pF<br>XOSC,GAIN=2, Cshunt=5.5pF  | -    | 6.2K | 27.2K |       |

|                    |                          | F = 16MHz - CL=20 pF<br>XOSC,GAIN=3, Cshunt=4pF   |      |      |       | •     |

|                    |                          | F = 32MHz - CL=20 pF<br>XOSC,GAIN=4, Cshunt=3.9pF | -    | 6.0K | 21K   |       |

| CL <sup>(1)</sup>  | Crystal load capacitance |                                                   | 10   | -    | 20    | pF    |

| Pon <sup>(1)</sup> | Drive Level              | AMPGC=ON                                          | -    | -    | 100   | uW    |

#### Note:

- 1. These values are based on simulation. They are not covered by production test limits or characterization.

- 2. These are based on characterization.

#### Table 46-45. Power Consumption

| Symbol          | Parameter              | Conditions                                    |           | Та                             | Min. | Тур. | Max. | Units |

|-----------------|------------------------|-----------------------------------------------|-----------|--------------------------------|------|------|------|-------|

| I <sub>DD</sub> | Current<br>consumption | F=2MHz - CL=20pF<br>XOSC,GAIN=0,<br>VCC=3.3V  | AMPGC=OFF | Typ 25°C -<br>-<br>-<br>-<br>- | -    | 66   | 85   | μΑ    |

|                 |                        |                                               | AMPGC=ON  |                                | -    | 62   | 99   |       |

|                 |                        | F=4MHz - CL=20pF<br>XOSC,GAIN=1,<br>VCC=3.3V  | AMPGC=OFF |                                | -    | 107  | 140  |       |

|                 |                        |                                               | AMPGC=ON  |                                | -    | 70   | 101  |       |

|                 |                        | F=8MHz - CL=20pF<br>XOSC,GAIN=2,<br>VCC=3.3V  | AMPGC=OFF |                                | -    | 200  | 261  |       |

|                 |                        |                                               | AMPGC=ON  |                                | -    | 118  | 153  |       |

|                 |                        | F=16MHz - CL=20pF<br>XOSC,GAIN=3,<br>VCC=3.3V | AMPGC=OFF |                                | -    | 436  | 581  |       |

|                 |                        |                                               | AMPGC=ON  |                                | -    | 247  | 329  |       |

|                 |                        | F=32MHz - CL=20pF<br>XOSC,GAIN=4,<br>VCC=3.3V | AMPGC=OFF |                                | -    | 1303 | 1902 |       |

|                 |                        |                                               | AMPGC=ON  | -                              | 627  | 940  |      |       |

#### 46.13.2 External 32KHz Crystal Oscillator (XOSC32K) Characteristics

#### **Digital Clock Characteristics**

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN32 pin.

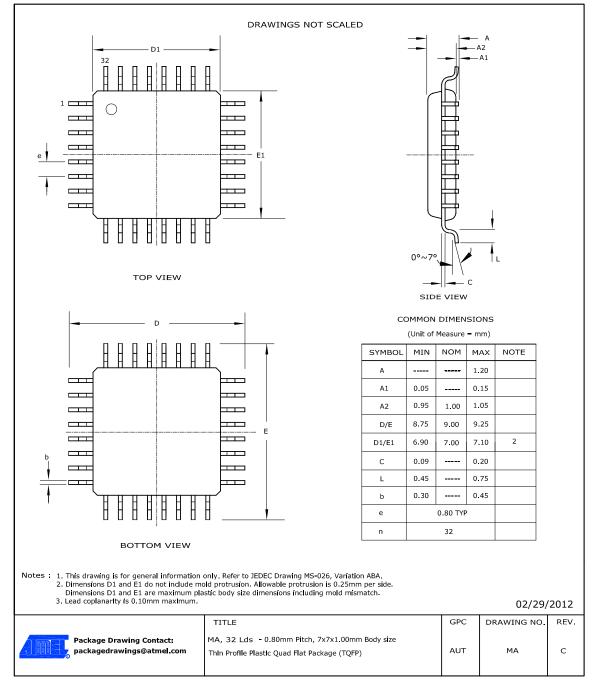

## 49.2 Package Drawings

#### 49.2.1 32-pin TQFP

100

mg

#### Table 49-2. Package Characteristics

MSL3

# **52.** Acronyms and Abbreviations

The below table contains acronyms and abbreviations used in this document.

#### Table 52-1. Acronyms and Abbreviations

| Abbreviation | Description                                         |  |  |  |  |

|--------------|-----------------------------------------------------|--|--|--|--|

| AC           | Analog Comparator                                   |  |  |  |  |

| ADC          | Analog-to-Digital Converter                         |  |  |  |  |

| ADDR         | Address                                             |  |  |  |  |

| AES          | Advanced Encryption Standard                        |  |  |  |  |

| АНВ          | Advanced High-performance Bus                       |  |  |  |  |

| AMBA         | Advanced Microcontroller Bus Architecture           |  |  |  |  |

| APB          | AMBA Advanced Peripheral Bus                        |  |  |  |  |

| AREF         | Analog Reference Voltage                            |  |  |  |  |

| BOD          | Brown-out Detector                                  |  |  |  |  |

| CAL          | Calibration                                         |  |  |  |  |

| CC           | Compare/Capture                                     |  |  |  |  |

| CCL          | Configurable Custom Logic                           |  |  |  |  |

| CLK          | Clock                                               |  |  |  |  |

| CRC          | Cyclic Redundancy Check                             |  |  |  |  |

| CTRL         | Control                                             |  |  |  |  |

| DAC          | Digital-to-Analog Converter                         |  |  |  |  |

| DAP          | Debug Access Port                                   |  |  |  |  |

| DFLL         | Digital Frequency Locked Loop                       |  |  |  |  |

| DPLL         | Digital Phase Locked Loop                           |  |  |  |  |

| DMAC         | DMA (Direct Memory Access) Controller               |  |  |  |  |

| DSU          | Device Service Unit                                 |  |  |  |  |

| EEPROM       | Electrically Erasable Programmable Read-Only Memory |  |  |  |  |

| EIC          | External Interrupt Controller                       |  |  |  |  |

| EVSYS        | Event System                                        |  |  |  |  |

| FDPLL        | Fractional Digital Phase Locked Loop, also DPLL     |  |  |  |  |

| FREQM        | Frequency Meter                                     |  |  |  |  |

| GCLK         | Generic Clock Controller                            |  |  |  |  |

| GND          | Ground                                              |  |  |  |  |

|              |                                                     |  |  |  |  |