#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·ХГ

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d16a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each peripheral can only be configured either in Secure or in Non-Secure mode.

The PAC NONSECx registers (Read Only) contain one bit per peripheral for that purpose, which is the image of the NONSECx fuses from the NVM User row (UROW).

During Boot ROM execution, the NONSECx fuses from the NVM User row are copied in the PAC peripheral NONSECx registers so that they can be read by the application.

All peripherals are marked as "exempt" in the memory map, meaning that all bus transactions are propagated. As a consequence, any illegal accesses are reported back to the PAC and trigger an interrupt if enabled.

The security configuration (Secure or Non-Secure) is propagated to each individual peripheral, thus it is the responsibility of the peripheral to grant or not the access with the following rules:

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0), a PAC error is triggered

**Important:** These rules do not apply to the specific peripherals called Mix-Secure peripherals.

**Note:** The Secure application will usually provide an API for the Non-Secure application using the Non-Secure Callable region (NSC) to allow the Non-Secure application to request specific resources.

Table 13-8. Peripheral PAC Security Attribution (Excluding Mix-Secure Peripherals)

| Mode       | Secure Master Access | Non-Secure Master Access             |

|------------|----------------------|--------------------------------------|

| Non-Secure | Read / Write         | Read / Write                         |

| Secure     | Read / Write         | Discarded (Write ignored / Read 0x0) |

|            |                      | PAC Error is generated               |

#### 13.2.5.1 SAM L11 Peripherals Configuration Example

Below is a typical configuration examples where all peripherals except the ADC, TC0, and Event System (EVSYS) are reserved to the Secure application:

- Secure/Non-Secure Peripherals PAC configuration:

- PAC.NONSECA=PAC.NONSECB=0x0000\_0000

- PAC.NONSECC=0x0000\_00091 (ADC, TC0 and EVSYS available for the Non-Secure application)

#### 13.2.6 SAM L11 Memory Space Security Attribution

This table provides the security attributions of the SAM L11 memory space:

#### 19.8.7 APBA Mask

| Name:     | APBAMASK             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x000007FFF          |

| Property: | PAC Write-Protection |

| Bit    | 31   | 30       | 29         | 28      | 27    | 26   | 25  | 24  |

|--------|------|----------|------------|---------|-------|------|-----|-----|

|        |      |          |            |         |       |      |     |     |

| Access |      |          |            |         |       |      |     |     |

| Reset  |      |          |            |         |       |      |     |     |

|        |      |          |            |         |       |      |     |     |

| Bit    | 23   | 22       | 21         | 20      | 19    | 18   | 17  | 16  |

|        |      |          |            |         |       |      |     |     |

| Access |      |          | I I        |         |       |      |     |     |

| Reset  |      |          |            |         |       |      |     |     |

|        |      |          |            |         |       |      |     |     |

| Bit    | 15   | 14       | 13         | 12      | 11    | 10   | 9   | 8   |

|        |      | Reserved | AC         | PORT    | FREQM | EIC  | RTC | WDT |

| Access |      | R/W      | R/W        | R/W     | R/W   | R/W  | R/W | R/W |

| Reset  |      | 1        | 1          | 1       | 1     | 1    | 1   | 1   |

|        |      |          |            |         |       |      |     |     |

| Bit    | 7    | 6        | 5          | 4       | 3     | 2    | 1   | 0   |

|        | GCLK | SUPC     | OSC32KCTRL | OSCCTRL | RSTC  | MCLK | PM  | PAC |

| Access | R/W  | R/W      | R/W        | R/W     | R/W   | R/W  | R/W | R/W |

| Reset  | 1    | 1        | 1          | 1       | 1     | 1    | 1   | 1   |

#### Bit 14 – Reserved For future use

Reserved bits are unused and reserved for future use. For compatibility with future devices, always write reserved bits to their reset value. If no reset value is given, write 0.

### Bit 13 – AC AC APBA Clock Enable

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The APBA clock for the AC is stopped. |

| 1     | The APBA clock for the AC is enabled. |

#### Bit 12 - PORT PORT APBA Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBA clock for the PORT is stopped. |

| 1     | The APBA clock for the PORT is enabled. |

#### Bit 11 – FREQM FREQM APBA Clock Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The APBA clock for the FREQM is stopped. |

| 1     | The APBA clock for the FREQM is enabled. |

## **FREQM – Frequency Meter**

FREQM is reset. See 20.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the 20.8.6 INTFLAG register to determine which interrupt condition is present.

This interrupt is a synchronous wake-up source.

Note that interrupts must be globally enabled for interrupt requests to be generated.

#### 20.6.5 Events

Not applicable.

#### 20.6.6 Sleep Mode Operation

The FREQM will continue to operate in idle sleep mode where the selected source clock is running. The FREQM's interrupts can be used to wake up the device from idle sleep mode.

For lowest chip power consumption in sleep modes, FREQM should be disabled before entering a sleep mode.

#### **Related Links**

22. PM – Power Manager

#### 20.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits and registers are write-synchronized:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

PM – Power Manager

| CPU Mode       | XOSC32K.<br>RUNSTDBY | XOSC32K.<br>ONDEMAND | Sleep Behavior of XOSC32K and CFD |

|----------------|----------------------|----------------------|-----------------------------------|

| Active or Idle | -                    | 0                    | Always run                        |

| Active or Idle | -                    | 1                    | Run if requested by peripheral    |

| Standby        | 1                    | 0                    | Always run                        |

| Standby        | 1                    | 1                    | Run if requested by peripheral    |

| Standby        | 0                    | -                    | Run if requested by peripheral    |

#### Table 24-1. XOSC32K Sleep Behavior

As a crystal oscillator usually requires a very long start-up time, the 32KHz External Crystal Oscillator will keep running across resets when XOSC32K.ONDEMAND=0, except for power-on reset (POR). After a reset or when waking up from a sleep mode where the XOSC32K was disabled, the XOSC32K will need a certain amount of time to stabilize on the correct frequency. This start-up time can be configured by changing the Oscillator Start-Up Time bit group (XOSC32K.STARTUP) in the 32KHz External Crystal Oscillator Control register. During the start-up time, the oscillator output is masked to ensure that no unstable clock propagates to the digital logic.

Once the external clock or crystal oscillator is stable and ready to be used as a clock source, the XOSC32K Ready bit in the Status register is set (STATUS.XOSC32KRDY=1). The transition of STATUS.XOSC32KRDY from '0' to '1' generates an interrupt if the XOSC32K Ready bit in the Interrupt Enable Set register is set (INTENSET.XOSC32KRDY=1).

The XOSC32K can be used as a source for Generic Clock Generators (GCLK) or for the Real-Time Counter (RTC). Before enabling the GCLK or the RTC module, the corresponding oscillator output must be enabled (XOSC32K.EN32K or XOSC32K.EN1K) in order to ensure proper operation. In the same way, the GCLK or RTC modules must be disabled before the clock selection is changed. For details on RTC clock configuration, refer also to 24.6.6 Real-Time Counter Clock Selection.

#### **Related Links**

18. GCLK - Generic Clock Controller

27. RTC – Real-Time Counter

## 24.6.3 Clock Failure Detection Operation

The Clock Failure Detector (CFD) allows the user to monitor the external clock or crystal oscillator signal provided by the external oscillator (XOSC32K). The CFD detects failing operation of the XOSC32K clock with reduced latency, and allows to switch to a safe clock source in case of clock failure. The user can also switch from the safe clock back to XOSC32K in case of recovery. The safe clock is derived from the OSCULP32K oscillator with a configurable prescaler. This allows to configure the safe clock in order to fulfill the operative conditions of the microcontroller.

In sleep modes, CFD operation is automatically disabled when the external oscillator is not requested to run by a peripheral. See the Sleep Behavior table above when this is the case.

The user interface registers allow to enable, disable, and configure the CFD. The Status register provides status flags on failure and clock switch conditions. The CFD can optionally trigger an interrupt or an event when a failure is detected.

## WDT – Watchdog Timer

| V | VEN | Interrupt Enable | Mode                                                   |

|---|-----|------------------|--------------------------------------------------------|

| 1 |     | 0                | Always-on and window mode                              |

| 1 |     | 1                | Always-on and window mode with Early Warning interrupt |

#### 26.6.8.2 Early Warning

The Early Warning interrupt notifies that the WDT is approaching its time-out condition. The Early Warning interrupt behaves differently in Normal mode and in Window mode.

*In Normal mode*, the Early Warning interrupt generation is defined by the Early Warning Offset in the Early Warning Control register (EWCTRL.EWOFFSET). The Early Warning Offset bits define the number of CLK\_WDT\_OSC clocks before the interrupt is generated, relative to the start of the watchdog time-out period.

The user must take caution when programming the Early Warning Offset bits. If these bits define an Early Warning interrupt generation time greater than the watchdog time-out period, the watchdog time-out system reset is generated prior to the Early Warning interrupt. Consequently, the Early Warning interrupt will never be generated.

*In window mode*, the Early Warning interrupt is generated at the start of the open window period. In a typical application where the system is in sleep mode, the Early Warning interrupt can be used to wake up and clear the Watchdog Timer, after which the system can perform other tasks or return to sleep mode.

If the WDT is operating in Normal mode with CONFIG.PER = 0x2 and EWCTRL.EWOFFSET = 0x1, the Early Warning interrupt is generated 16 CLK\_WDT\_OSC clock cycles after the start of the time-out period. The time-out system reset is generated 32 CLK\_WDT\_OSC clock cycles after the start of the watchdog timeout period.

## RTC – Real-Time Counter

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | Tamper event output is disabled and will not be generated.                   |

| 1     | Tamper event output is enabled and will be generated for every tamper input. |

#### Bit 8 – CMPEO0 Compare 0 Event Output Enable

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | Compare 0 event is disabled and will not be generated.                    |

| 1     | Compare 0 event is enabled and will be generated for every compare match. |

#### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PEREOn Periodic Interval n Event Output Enable [n = 7..0]

| Value | Description                                                      |

|-------|------------------------------------------------------------------|

| 0     | Periodic Interval n event is disabled and will not be generated. |

| 1     | Periodic Interval n event is enabled and will be generated.      |

RTC – Real-Time Counter

|        | Offset:<br>Reset: | SYNCBUSY<br>0x10<br>0x00000000<br>- |       |     |       |          |        |       |

|--------|-------------------|-------------------------------------|-------|-----|-------|----------|--------|-------|

| Bit    | 31                | 30                                  | 29    | 28  | 27    | 26       | 25     | 24    |

|        |                   |                                     |       |     |       |          |        |       |

| Access |                   |                                     |       |     |       |          |        |       |

| Reset  |                   |                                     |       |     |       |          |        |       |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    | 23                | 22                                  | 21    | 20  | 19    | 18       | 17     | 16    |

|        |                   |                                     |       |     |       |          |        | [1:0] |

| Access |                   |                                     |       |     |       |          | R      | R     |

| Reset  |                   |                                     |       |     |       |          | 0      | 0     |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    |                   | 14                                  | 13    | 12  | 11    | 10       | 9      | 8     |

|        | COUNTSYNC         |                                     |       |     |       |          |        |       |

| Access | R                 |                                     |       |     |       |          |        |       |

| Reset  | 0                 |                                     |       |     |       |          |        |       |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    | 7                 | 6                                   | 5     | 4   | 3     | 2        | 1      | 0     |

|        |                   | COMP1                               | COMP0 | PER | COUNT | FREQCORR | ENABLE | SWRST |

| Access |                   | R/W                                 | R/W   | R   | R     | R        | R      | R     |

| Reset  |                   | 0                                   | 0     | 0   | 0     | 0        | 0      | 0     |

#### 27.10.8 Synchronization Busy in COUNT16 mode (CTRLA.MODE=1)

Bits 17:16 - GPn[1:0] General Purpose n Synchronization Busy Status

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | Write synchronization for GPn register is complete. |

| 1     | Write synchronization for GPn register is ongoing.  |

Bit 15 – COUNTSYNC Count Read Sync Enable Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Write synchronization for CTRLA.COUNTSYNC bit is complete. |

| 1     | Write synchronization for CTRLA.COUNTSYNC bit is ongoing.  |

#### Bits 5, 6 – COMPn Compare n Synchronization Busy Status [n = 1..0]

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Write synchronization for COMPn register is complete. |

| 1     | Write synchronization for COMPn register is ongoing.  |

#### **Bit 4 – PER** Period Synchronization Busy Status

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | Write synchronization for PER register is complete. |

| 1     | Write synchronization for PER register is ongoing.  |

#### 29.5.4 DMA

Not applicable.

#### 29.5.5 Interrupts

There are several interrupt request lines, at least one for the external interrupts (EXTINT) and one for non-maskable interrupt (NMI).

The EXTINT interrupt request line is connected to the interrupt controller. Using the EIC interrupt requires the interrupt controller to be configured first.

The NMI interrupt request line is also connected to the interrupt controller, but does not require the interrupt to be configured.

#### 29.5.6 Events

The events are connected to the Event System. Using the events requires the Event System to be configured first.

#### **Related Links**

33. EVSYS - Event System

#### 29.5.7 Debug Operation

When the CPU is halted in debug mode, the EIC continues normal operation. If the EIC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 29.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Non-Maskable Interrupt Flag Status and Clear register (NMIFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

## 29.5.9 SAM L11 TrustZone Specific Register Access Protection

When the EIC is not PAC secured, non-secure and secure code can both access all functionalities. When the EIC is PAC secured, all registers are by default available in the secure alias only.

A PAC secured EIC can open up individual external interrupts for non-secure access. This is done using the NONSEC and the NONSECNMI registers. When an external interrupt has been set as non-secure, it can be handled from non-secure code, using the EIC module non-secure alias. Since only Secured code has the rights to modify the NONSEC register, an interrupt-based mechanism has been added to let Non Secured code know when these registers have been changed by Secured code. A single flag called NSCHK in the INTFLAG register will rise should changes, conditioned by the NSCHK register, occur in the NONSEC or NONSECNMI registers.

• EIC Security Attribution registers (NONSEC and NONSECNMI) can only be written in the secure alias, otherwise a PAC error results.

#### 32.8.8 Data Output Value Toggle

| Name:     | OUTTGL                           |

|-----------|----------------------------------|

| Offset:   | 0x1C                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

This register allows the user to toggle the drive level of one or more output I/O pins, without doing a readmodify-write operation. Changes in this register will also be reflected in the Data Output Value (OUT), Data Output Value Set (OUTSET) and Data Output Value Clear (OUTCLR) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31        | 30            | 29        | 28        | 27        | 26        | 25        | 24        |  |  |  |

|--------|-----------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|

| Dit [  |           |               |           |           |           |           |           |           |  |  |  |

|        |           | OUTTGL[31:24] |           |           |           |           |           |           |  |  |  |

| Access | RW/RW*/RW | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |

| Reset  | 0         | 0             | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |

|        |           |               |           |           |           |           |           |           |  |  |  |

| Bit    | 23        | 22            | 21        | 20        | 19        | 18        | 17        | 16        |  |  |  |

|        |           |               |           | OUTTG     | L[23:16]  |           |           |           |  |  |  |

| Access | RW/RW*/RW | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |

| Reset  | 0         | 0             | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |

|        |           |               |           |           |           |           |           |           |  |  |  |

| Bit    | 15        | 14            | 13        | 12        | 11        | 10        | 9         | 8         |  |  |  |

| [      |           |               |           | OUTTO     | GL[15:8]  |           | <u>.</u>  |           |  |  |  |

| Access | RW/RW*/RW | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |

| Reset  | 0         | 0             | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |

|        |           |               |           |           |           |           |           |           |  |  |  |

| Bit    | 7         | 6             | 5         | 4         | 3         | 2         | 1         | 0         |  |  |  |

| [      |           |               |           | OUTTO     | GL[7:0]   |           |           |           |  |  |  |

| Access | RW/RW*/RW | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |

| Reset  | 0         | 0             | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |

#### Bits 31:0 – OUTTGL[31:0] PORT Data Output Value Toggle

Writing '0' to a bit has no effect.

#### 32.8.12 Event Input Control

| Name:     | EVCTRL                       |

|-----------|------------------------------|

| Offset:   | 0x2C                         |

| Reset:    | 0x0000000                    |

| Property: | PAC Write-Protection, Secure |

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to four input event pins for each PORT group. Each byte of this register addresses one Event input pin.

| Bit    | 31      | 30          | 29      | 28        | 27        | 26        | 25      | 24      |  |

|--------|---------|-------------|---------|-----------|-----------|-----------|---------|---------|--|

|        | PORTEIx | EVACTx[1:0] |         |           | PIDx[4:0] |           |         |         |  |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW   | RW/-/RW   | RW/-/RW   | RW/-/RW | RW/-/RW |  |

| Reset  | 0       | 0           | 0       | 0         | 0         | 0         | 0       | 0       |  |

|        |         |             |         |           |           |           |         |         |  |

| Bit    | 23      | 22          | 21      | 20        | 19        | 18        | 17      | 16      |  |

|        | PORTEIX | EVAC        | Tx[1:0] |           |           | PIDx[4:0] |         |         |  |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW   | RW/-/RW   | RW/-/RW   | RW/-/RW | RW/-/RW |  |

| Reset  | 0       | 0           | 0       | 0         | 0         | 0         | 0       | 0       |  |

|        |         |             |         |           |           |           |         |         |  |

| Bit    | 15      | 14          | 13      | 12        | 11        | 10        | 9       | 8       |  |

|        | PORTEIX | EVAC        | Tx[1:0] | PIDx[4:0] |           |           |         |         |  |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW   | RW/-/RW   | RW/-/RW   | RW/-/RW | RW/-/RW |  |

| Reset  | 0       | 0           | 0       | 0         | 0         | 0         | 0       | 0       |  |

|        |         |             |         |           |           |           |         |         |  |

| Bit    | 7       | 6           | 5       | 4         | 3         | 2         | 1       | 0       |  |

|        | PORTEIX | EVACTx[1:0] |         |           |           | PIDx[4:0] |         |         |  |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW   | RW/-/RW   | RW/-/RW   | RW/-/RW | RW/-/RW |  |

| Reset  | 0       | 0           | 0       | 0         | 0         | 0         | 0       | 0       |  |

|        |         |             |         |           |           |           |         |         |  |

Bits 31,23,15,7 – PORTEIx PORT Event Input Enable x [x = 3..0]

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The event action x (EVACTx) will not be triggered on any incoming event. |

| 1     | The event action x (EVACTx) will be triggered on any incoming event.     |

## Bits 30:29, 22:21,14:13,6:5 – EVACTx PORT Event Action x [x = 3..0]

These bits define the event action the PORT will perform on event input x. See also Table 32-4.

Bits 28:24,20:16,12:8,4:0 – PIDx PORT Event Pin Identifier x [x = 3..0]

These bits define the I/O pin on which the event action will be performed, according to Table 32-5.

#### 32.8.14 Pin Configuration

| Name:     | PINCFG                           |

|-----------|----------------------------------|

| Offset:   | 0x40 + n*0x01 [n=031]            |

| Reset:    | 0x00                             |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to 32 Pin Configuration registers in each PORT group, one for each I/O line.

| Bit    | 7 | 6         | 5 | 4 | 3 | 2         | 1         | 0         |

|--------|---|-----------|---|---|---|-----------|-----------|-----------|

|        |   | DRVSTR    |   |   |   | PULLEN    | INEN      | PMUXEN    |

| Access |   | RW/RW*/RW |   |   |   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  |   | 0         |   |   |   | 0         | 0         | 0         |

#### **Bit 6 – DRVSTR** Output Driver Strength Selection

This bit controls the output driver strength of an I/O pin configured as an output.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Pin drive strength is set to normal drive strength.   |

| 1     | Pin drive strength is set to stronger drive strength. |

#### Bit 2 - PULLEN Pull Enable

This bit enables the internal pull-up or pull-down resistor of an I/O pin configured as an input.

| Value | Description                                                                                        |

|-------|----------------------------------------------------------------------------------------------------|

| 0     | Internal pull resistor is disabled, and the input is in a high-impedance configuration.            |

| 1     | Internal pull resistor is enabled, and the input is driven to a defined logic level in the absence |

|       | of external input.                                                                                 |

#### Bit 1 - INEN Input Enable

This bit controls the input buffer of an I/O pin configured as either an input or output.

Writing a zero to this bit disables the input buffer completely, preventing read-back of the physical pin state when the pin is configured as either an input or output.

#### 32.8.15 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x60                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24       |

|--------|----|----|----|----|----|----|----|----------|

|        |    |    |    |    |    |    |    |          |

| Access |    |    |    |    |    |    |    |          |

| Reset  |    |    |    |    |    |    |    |          |

|        |    |    |    |    |    |    |    |          |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16       |

|        |    |    |    |    |    |    |    |          |

| Access |    |    |    |    |    |    |    |          |

| Reset  |    |    |    |    |    |    |    |          |

| 5.4    | 45 |    | 10 | 10 |    | 10 | 0  | 0        |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8        |

|        |    |    |    |    |    |    |    |          |

| Access |    |    |    |    |    |    |    |          |

| Reset  |    |    |    |    |    |    |    |          |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0        |

| DIL    | /  | 0  | 5  | 4  | 3  | 2  | I  |          |

|        |    |    |    |    |    |    |    | NSCHK    |

| Access |    |    |    |    |    |    |    | RW/RW/RW |

| Reset  |    |    |    |    |    |    |    | 0        |

Bit 0 – NSCHK Non-Secure Check Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Non-Secure Check Interrupt Enable bit, which disables the Non-Secure Check interrupt.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The Non-Secure Check interrupt is disabled. |

| 1     | The Non-Secure Check interrupt is enabled.  |

# **Bit 0 – DRE** Data Register Empty Interrupt Enable Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

#### 37.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

22. PM - Power Manager

#### 37.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Main Clock Controller. Refer to *Peripheral Clock Masking* for details and default status of this clock.

Two generic clocks are used by SERCOM, GCLK\_SERCOMx\_CORE and GCLK\_SERCOM\_SLOW. The core clock (GCLK\_SERCOMx\_CORE) can clock the I<sup>2</sup>C when working as a master. The slow clock (GCLK\_SERCOM\_SLOW) is required only for certain functions, e.g. SMBus timing. These two clocks must be configured and enabled in the Generic Clock Controller (GCLK) before using the I<sup>2</sup>C.

These generic clocks are asynchronous to the bus clock (CLK\_SERCOMx\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to 37.6.6 Synchronization for further details.

#### **Related Links**

GCLK - Generic Clock Controller

19.6.2.6 Peripheral Clock Masking

PM – Power Manager

#### 37.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

28. DMAC - Direct Memory Access Controller

#### 37.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### 37.5.6 Events

Not applicable.

#### 37.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 37.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

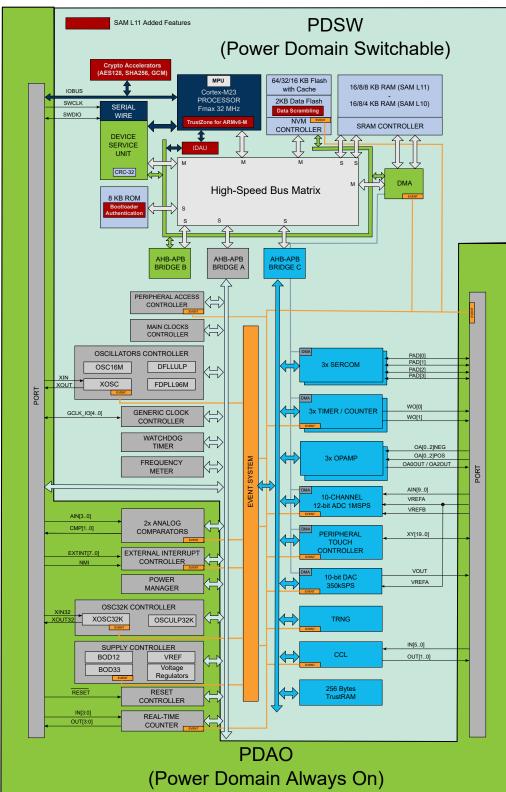

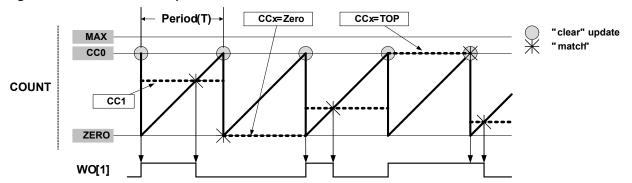

#### Figure 38-6. Match PWM Operation

The table below shows the update counter and overflow event/interrupt generation conditions in different operation modes.

| Name | Operation        | ТОР | Update    | Output Waveform        |           | OVFIF/Event |      |

|------|------------------|-----|-----------|------------------------|-----------|-------------|------|

|      |                  |     |           | On Match               | On Update | Up          | Down |

| NFRQ | Normal Frequency | PER | TOP/ ZERO | Toggle                 | Stable    | TOP         | ZERO |

| MFRQ | Match Frequency  | CC0 | TOP/ ZERO | Toggle                 | Stable    | TOP         | ZERO |

| NPWM | Single-slope PWM | PER | TOP/ ZERO | See description above. |           | TOP         | ZERO |

| MPWM | Single-slope PWM | CC0 | TOP/ ZERO | Toggle                 | Toggle    | TOP         | ZERO |

#### **Related Links**

32. PORT - I/O Pin Controller

#### 38.6.2.7 Double Buffering

The Compare Channels (CCx) registers, and the Period (PER) register in 8-bit mode are double buffered. Each buffer register has a buffer valid bit (CCBUFVx or PERBUFV) in the STATUS register, which indicates that the buffer register contains a new valid value that can be copied into the corresponding register. As long as the respective buffer valid status flag (PERBUFV or CCBUFVx) are set to '1', related syncbusy bits are set (SYNCBUSY.PER or SYNCBUSY.CCx), a write to the respective PER/PERBUF or CCx/CCBUFx registers will generate a PAC error, and access to the respective PER or CCx register is invalid.

When the buffer valid flag bit in the STATUS register is '1' and the Lock Update bit in the CTRLB register is set to '0', (writing CTRLBCLR.LUPD to '1'), double buffering is enabled: the data from buffer registers will be copied into the corresponding register under hardware UPDATE conditions, then the buffer valid flags bit in the STATUS register are automatically cleared by hardware.

**Note:** The software update command (CTRLBSET.CMD=0x3) is acting independently of the LUPD value.

A compare register is double buffered as in the following figure.

#### 38.7.3.13 Counter Value, 32-bit Mode

Name:COUNTOffset:0x14Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

**Note:** Prior to any read access, this register must be synchronized by user by writing the according TC Command value to the Control B Set register (CTRLBSET.CMD=READSYNC).

| Bit    | 31  | 30         | 29  | 28   | 27       | 26  | 25  | 24  |  |  |

|--------|-----|------------|-----|------|----------|-----|-----|-----|--|--|

|        |     |            |     | COUN | [31:24]  |     |     |     |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0        | 0   | 0   | 0   |  |  |

|        |     |            |     |      |          |     |     |     |  |  |

| Bit    | 23  | 22         | 21  | 20   | 19       | 18  | 17  | 16  |  |  |

|        |     |            |     | COUN | F[23:16] |     |     |     |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0        | 0   | 0   | 0   |  |  |

|        |     |            |     |      |          |     |     |     |  |  |

| Bit    | 15  | 14         | 13  | 12   | 11       | 10  | 9   | 8   |  |  |

|        |     |            |     | COUN | T[15:8]  |     |     |     |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0        | 0   | 0   | 0   |  |  |

|        |     |            |     |      |          |     |     |     |  |  |

| Bit    | 7   | 6          | 5   | 4    | 3        | 2   | 1   | 0   |  |  |

|        |     | COUNT[7:0] |     |      |          |     |     |     |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0        | 0   | 0   | 0   |  |  |

Bits 31:0 - COUNT[31:0] Counter Value

These bits contain the current counter value.

## **Electrical Characteristics**

#### 46.11.7 DETREF Characteristics

Table 46-31. Reference Voltage Characteristics

| Symbol      | Parameter                   | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min.  | Тур.          | Max.  | Units |

|-------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|-------|

| ADC/DAC Ref | ADC/DAC internal reference  | AC internal reference nom. $1.0V, V_{CC}=3.0V, T=25^{\circ}C$ 0.976 1.0<br>nom. $1.1V, V_{CC}=3.0V, T=25^{\circ}C$ 1.077 1.1<br>nom. $1.2V, V_{CC}=3.0V, T=25^{\circ}C$ 1.174 1.2<br>nom. $1.25V, V_{CC}=3.0V, T=$ 1.221 1.25<br>$1.0000, 1.25V, V_{CC}=3.0V, T=$ 1.221 1.25<br>nom. $2.0V, V_{CC}=3.0V, T=25^{\circ}C$ 1.945 2.0<br>nom. $2.2V, V_{CC}=3.0V, T=25^{\circ}C$ 2.143 2.2<br>nom. $2.4V, V_{CC}=3.0V, T=25^{\circ}C$ 2.143 2.2<br>nom. $2.5V, V_{CC}=3.0V, T=25^{\circ}C$ 2.143 2.5<br>additional drift over [-40, +25]^{\circ}C - 0.01/+0.005<br>drift over [+25, +85]^{\circ}C - 0.01/+0.005<br>drift over [-40, +25]^{\circ}C - 1.086 1.1<br>addition over [-40, +25]^{\circ}C - 1.086 1.1 | 1.0   | 1.022         | V     |       |

|             |                             | nom. 1.1V, V <sub>CC</sub> =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.077 | 1.1           | 1.127 |       |

|             |                             | nom. 1.2V, V <sub>CC</sub> =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.174 | 1.2           | 1.234 |       |

|             |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.221 | 1.25          | 1.287 |       |

|             |                             | nom. 2.0V, V <sub>CC</sub> =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.945 | 2.0           | 2.030 |       |

|             |                             | nom. 2.2V, V <sub>CC</sub> =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.143 | 2.2           | 2.242 |       |

|             |                             | nom. 2.4V, $V_{CC}$ =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.335 | 2.4           | 2.457 |       |

|             |                             | nom. 2.5V, V <sub>CC</sub> =3.0V, T= 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.428 | 2.5           | 2.563 |       |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | -0.01/+0.015  | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | -0.01/+0.005  | -     |       |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | +/-0.35       | -     | %/V   |

| AC Ref      | AC Ref Accuracy             | V <sub>CC</sub> =3.0V, T=25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.086 | 1.1           | 1.128 | V     |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | +/-0.01       | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | -0.005/+0.001 | -     | %/°C  |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | -0.35/+0.35   | -     | %/V   |

#### 46.11.8 OPAMP Characteristics Table 46-32. Operating Conditions

| Symbol                | Parameters               | Conditions                    | Min. | Тур. | Max.     | Unit |

|-----------------------|--------------------------|-------------------------------|------|------|----------|------|

| VCC                   | Power Supply             | All power modes               | 1.6  | 3    | 3.63     | V    |

| Vin                   | Input voltage range      |                               | 0    | -    | Vcc      | V    |

| Vout                  | Output voltage range     |                               | 0.15 | -    | Vcc-0.15 | V    |

| Cload                 | Maximum capacitance load |                               | -    | -    | 50       | pF   |

| Rload (1)             | Minimum resistive load   | Output Range[0.15V;Vcc-0.15V] | 3.5  | -    | -        | kΩ   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | 0.5  | -    | -        |      |

| I <sub>load</sub> (1) | DC output current load   | Output Range[0.15V;Vcc-0.15V] | -    | -    | 1        | mA   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | -    | -    | 6.9      |      |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

## **Electrical Characteristics**

| Symbol | Parameter                                 | Conditions                             |              | Min.                                          | Тур.      | Max.       | Units |

|--------|-------------------------------------------|----------------------------------------|--------------|-----------------------------------------------|-----------|------------|-------|

|        |                                           | Master, VDD                            | )>1,62V      | 0                                             | -         | -          |       |

| tMOV   | MOSI output                               | Master, VDD                            | )>2,70V      | -                                             | -         | 34.5       | ns    |

|        | valid after<br>SCK                        | Master, VDD                            | 0>1,62V      | -                                             | -         | 38.6       |       |

| tMOH   | MOSI hold                                 | Master, VDD>2,70V<br>Master, VDD>1,62V |              | 9.7                                           | -         | -          |       |

|        | after SCK                                 |                                        |              | 9.7                                           | -         | -          |       |

| tSSCK  | Slave SCK<br>Period when<br>tMIS=0 on the | Slave                                  | Reception    | 2*(tSIS<br>+tMASTER_OUT)                      | -         | -          |       |

|        | master side                               | Slave                                  | Transmission | 2*(tSOV<br>+tMASTER_IN) <sup>(6)</sup>        | -         | -          |       |

| tSSCKW | SCK high/low<br>width                     | Slave                                  |              | -                                             | 0,5*tSCK  | -          |       |

| tSSCKR | SCK rise<br>time <sup>(2)</sup>           | Slave                                  |              | -                                             | 0,25*tSCK | -          |       |

| tSSCKF | SCK fall<br>time <sup>(2)</sup>           | Slave                                  |              | -                                             | 0,25*tSCK | -          |       |

| tSIS   | MOSI setup to                             | Slave, VDD>                            | >2,70V       | 25.6                                          | -         | -          | ns    |

|        | SCK                                       | Slave, VDD>                            | >1,62V       | 26.2                                          | -         | -          |       |

| tSIH   | MOSI hold                                 | Slave, VDD>                            | >2,70V       | 13.2                                          | -         | -          |       |

|        | after SCK                                 | Slave, VDD>                            | >1,62V       | 13.9                                          | -         | -          |       |

| tSSS   | SS setup to<br>SCK                        | Slave                                  | PRELOADEN=1  | tSOSS+tEXT_MIS<br>+2*tAPBC <sup>(8) (9)</sup> | -         | -          |       |

|        |                                           |                                        | PRELOADEN=0  | tSOSS+tEXT_MIS                                | -         | -          |       |

| tSSH   | SS hold after<br>SCK                      | Slave                                  |              | 0.5*tSSCK                                     | -         | -          |       |

| tSOV   | MISO output                               | Slave, VDD>                            | >2,70V       | -                                             | -         | 69         |       |

|        | valid after<br>SCK                        | Slave, VDD>1,62V                       |              | -                                             | -         | 78.4       |       |

| tSOH   | MISO hold                                 | Slave, VDD>                            | >2,70V       | 20.2                                          | -         | -          |       |

|        | after SCK                                 | Slave, VDD>                            | >1,62V       | 20.2                                          | -         | -          |       |

| tSOSS  | MISO setup<br>after SS low                | Slave, VDD>                            | >2,70V       | -                                             | -         | 1*<br>tSCK |       |

|        |                                           | Slave, VDD>                            | >1,62V       | -                                             | -         | 1*<br>tSCK |       |

### 125°C Electrical Characteristics

| Symbol | Parameter                      | Conditi          | ions        | Min.                                          | Тур.      | Max.       | Units |

|--------|--------------------------------|------------------|-------------|-----------------------------------------------|-----------|------------|-------|

| tSSCKR | SCK rise time <sup>(2)</sup>   | Slave            |             | -                                             | 0,25*tSCK | -          |       |

| tSSCKF | SCK fall time <sup>(2)</sup>   | Slave            |             | -                                             | 0,25*tSCK | -          |       |

| tSIS   | MOSI setup to<br>SCK           | Slave, VDD>2,70V |             | 24.2                                          | -         | -          |       |

|        |                                | Slave, VDD>1,62V |             | 24.9                                          | -         | -          |       |

| tSIH   | MOSI hold after<br>SCK         | Slave, VDD>2,70V |             | 12.9                                          | -         | -          |       |

|        |                                | Slave, VDD>1,62V |             | 13.5                                          | -         | -          |       |

| tSSS   | SS setup to SCK                | Slave            | PRELOADEN=1 | tSOSS+tEXT_MIS<br>+2*tAPBC <sup>(8) (9)</sup> | -         | -          | ns    |

|        |                                |                  | PRELOADEN=0 | tSOSS+tEXT_MIS                                | -         | -          |       |

| tSSH   | SS hold after<br>SCK           | Slave            |             | 0.5*tSSCK                                     | -         | -          |       |

| tSOV   | MISO output<br>valid after SCK | Slave, VDD>2,70V |             | -                                             | -         | 66.9       |       |

|        |                                | Slave, VDD>1,62V |             | -                                             | -         | 76.6       |       |

| tSOH   | MISO hold after<br>SCK         | Slave, VDD>2,70V |             | 22.7                                          | -         | -          |       |

|        |                                | Slave, VDD>1,62V |             | 20.3                                          | -         | -          |       |

| tSOSS  | MISO setup after<br>SS low     | Slave, VDD>2,70V |             | -                                             | -         | 1*<br>tSCK |       |

|        |                                | Slave, VDD>1,62V |             | -                                             | -         | 1*<br>tSCK |       |

| tSOSH  | MISO hold after<br>SS high     | Slave, VDD>2,70V |             | 15                                            | -         | -          |       |

|        |                                | Slave, VDD>1,62V |             | 15                                            | -         | -          |       |

#### Note:

- 1. These values are based on simulation. These values are not covered by test limits in production.

- 2. See I/O Pin Characteristics.

- 3. Where tSLAVE\_OUT is the slave external device output response time, generally tEXT\_SOV +tLINE\_DELAY (See Note 7).

- 4. Where tSLAVE\_IN is the slave external device input constraint, generally tEXT\_SIS+tLINE\_DELAY (See Note 7).

- 5. Where tMASTER\_OUT is the master external device output response time, generally tEXT\_MOV +tLINE\_DELAY (See Note 7).

- 6. Where tMASTER\_IN is the master external device input constraint, generally tEXT\_MIS +tLINE\_DELAY (See Note 7).

- 7. tLINE\_DELAY is the transmission line time delay.

- 8. tEXT\_MIS is the input constraint for the master external device.

- 9. tAPBC is the APB period for SERCOM.