# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 24-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d16a-yf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Standby with Full SRAM Retention (0.5 µA) with 5.3 µs wake-up time

- Off mode (< 100 nA)

- Static and dynamic power gating architecture

- Sleepwalking peripherals

- Two performance levels

- Embedded Buck/LDO regulator with on-the-fly selection

- Security

- Up to four tamper pins for static and dynamic intrusion detections

- Data Flash

- Optimized for secrets storage

- Data Scrambling with user-defined key (optional)

- Rapid Tamper erase on scrambling key and on one user-defined row

- Silent access for side channel attack resistance

- TrustRAM

- Address and Data scrambling with user-defined key

- Chip-level tamper detection on physical RAM to resist microprobing attacks

- Rapid Tamper Erase on scrambling key and RAM data

- Silent access for side channel attack resistance

- Data remanence prevention

- Peripherals

- One True Random Generator (TRNG)

- AES-128, SHA-256, and GCM cryptography accelerators (optional)

- Secure pin multiplexing to isolate on dedicated I/O pins a secured communication with external devices from the non-secure application (optional)

- TrustZone for flexible hardware isolation of memories and peripherals (optional)

- Up to six regions for the Flash

- Up to two regions for the Data Flash

- Up to two regions for the SRAM

- Individual security attribution for each peripheral, I/O, external interrupt line, and Event System Channel

- Secure Boot with SHA-based authentication (optional)

- Up to three debug access levels

- Up to three Chip Erase commands to erase part of or the entire embedded memories

- Unique 128-bit serial number

#### Advanced Analog and Touch

- One 12-bit 1 Msps Analog-to-Digital Converter (ADC) with up to 10 channels

- Two Analog Comparators (AC) with window compare function

- One 10-bit 350 kSPS Digital-to-Analog Converter (DAC) with external and internal outputs

- Three Operational Amplifiers (OPAMP)

- One enhanced Peripheral Touch Controller (PTC):

- Up to 20 self-capacitance channels

- Up to 100 (10 x 10) mutual-capacitance channels

- Low-power, high-sensitivity, environmentally robust capacitive touch buttons, sliders, and wheels

# Pinouts

# Table 4-4. Serial Wire Debug Interface Pinout

| Signal | Supply | I/O pin |

|--------|--------|---------|

| SWCLK  | VDDIO  | PA30    |

| SWDIO  | VDDIO  | PA31    |

# 4.4 SERCOM Configurations

The following table lists the supported features for each SERCOM instance:

#### Table 4-5. SERCOM Features Summary

|                                        |                                                   | SERCOM Instance                                   |                                                                                                       |

|----------------------------------------|---------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Protocol                               | SERCOM0                                           | SERCOM1                                           | SERCOM2                                                                                               |

| SPI                                    | Yes                                               | Yes                                               | Yes                                                                                                   |

| I <sup>2</sup> C (1)                   | Yes<br>High-speed mode (≤ 3,4 Mbit/s)             | Yes<br>Fast plus Mode (≤ 1 Mbit/s)                | No                                                                                                    |

| USART                                  | Yes<br>including:<br>Hardware Handshaking<br>IrDA | Yes<br>including:<br>Hardware Handshaking<br>IrDA | Yes<br>including:<br>Hardware Handshaking<br>IrDA<br>RS-485<br>Auto-baud mode<br>LIN Slave<br>ISO7816 |

| USART/SPI Receive Buffer Size          | Two-level                                         | Four-level                                        | Two-level                                                                                             |

| Secure Pin Multiplexing (SAM L11 only) | No                                                | Yes                                               | No                                                                                                    |

#### Note:

1. I<sup>2</sup>C is not supported on all SERCOM pins. Refer to the SERCOM I<sup>2</sup>C Pins table for more details.

#### 4.4.1 SERCOM I2C Pins

The following table lists the SERCOM pins which support I<sup>2</sup>C:

#### Table 4-6. SERCOM I<sup>2</sup>C Pins

| Pin Name | SERCOM0 I <sup>2</sup> C Pad Name | SERCOM1 I <sup>2</sup> C Pad Name |

|----------|-----------------------------------|-----------------------------------|

| PA16     | SERCOM0/PAD[0]                    | SERCOM1/PAD[0]                    |

| PA17     | SERCOM0/PAD[1]                    | SERCOM1/PAD[1]                    |

| PA22     | SERCOM0/PAD[0]                    | N/A                               |

| PA23     | SERCOM0/PAD[1]                    | N/A                               |

#### 4.4.2 Secure Pin Multiplexing (on SERCOM) Pins

The Secure Pin Multiplexing feature can be used on dedicated SERCOM I/O pins to isolate a secure communication with external devices from the non-secure application.

Refer to 13.6 Secure Pin Multiplexing on SERCOM for more details.

The following table lists the SERCOM pins that support the Secure Pin Multiplexing feature:

# SAM L10/L11 Family

# **Processor and Architecture**

| Features                       | Cortex-M23 Configurable<br>Options                             | SAM L10 Implementation | SAM L11 Implementation |

|--------------------------------|----------------------------------------------------------------|------------------------|------------------------|

| Cross Trigger Interface (CTI)  | Present or absent                                              | Absent                 | Absent                 |

| Micro Trace Buffer (MTB)       | Present or absent                                              | Absent                 | Absent                 |

| Embedded Trace Macrocell (ETM) | Present or absent                                              | Absent                 | Absent                 |

| JTAGnSW debug protocol         | Selects between JTAG or Serial-<br>Wire interfaces for the DAP | Serial-Wire            | Serial-Wire            |

| Multi-drop for Serial Wire     | Present or absent                                              | Absent                 | Absent                 |

#### Note:

1. Refer to Table 11-3 for more information.

For more details, refer to the ARM Cortex-M23 Processor Technical Reference Manual (http://www.arm.com).

#### 11.1.2 Cortex-M23 Core Peripherals

The processor has the following core peripheral:

- System Timer (SysTick)

- The System Timer is a 24-bit timer clocked by the core frequency.

**Important:** On SAM L11 devices, there are two System timers, one for Secure state and one for Non-secure state.

- Nested Vectored Interrupt Controller (NVIC)

- The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

**Important:** On SAM L11 devices, there are two Vector tables: the Secure Vector table and the Non-Secure Vector table.

- System Control Block (SCB)

- The System Control Block (SCB) provides system implementation information and system control that includes configuration, control, and reporting of system exceptions

- Memory Protection Unit (MPU)

- The MPU improves system reliability by defining the memory attributes for different memory regions.

| 7 |

|---|

|   |

**Important:** On SAM L11 devices, there are two MPUs: one for the Secure state and one for the Non-secure state. Each MPU can define memory access permissions and attributes independently.

- Security Attribution Unit (SAU)

- The SAU improves system security by defining security attributes for different regions.

## 14.4.5.3 System Reset Request (CMD\_RESET)

This command allows resetting the system using a system reset request. Since the reset is executed immediately after receiving the command, no reply is sent to the debugger.

After reset, the CPU executes the Boot ROM code from the beginning

#### 14.4.5.4 Chip Erase (CMD\_CHIPERASE) - SAM L10 only

CMD\_CHIPERASE command erases the entire device except BOOT area, and reverts to Debug Access Level 2.

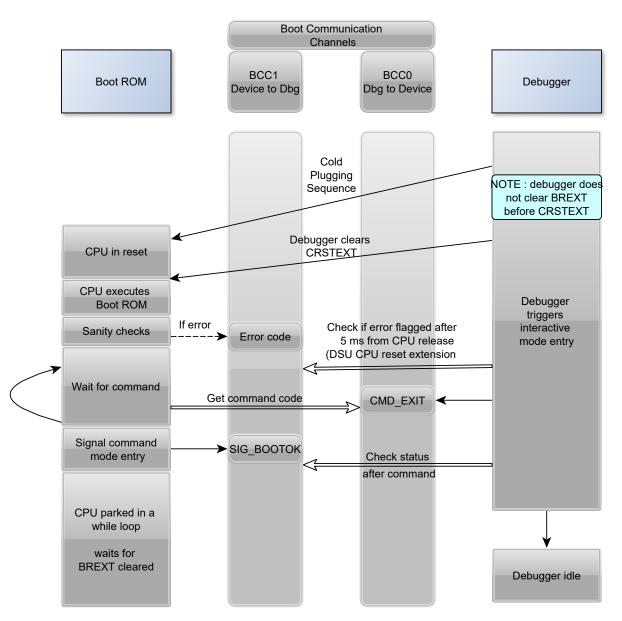

# 14.4.5.5.1 CMD\_CEx (SAM L11 only) Figure 14-11. CMD\_CEx Flow diagram

## 14.4.5.6 NVM Memory Regions Integrity Checks (CMD\_CRC)

The Boot ROM provides a way to check the integrity of the embedded non-volatile memories which may be of interest in case of a failure analysis.

This requires the user to place tables describing the memory area to be checked with their expected CRC values.

**Note:** During this integrity check process, the debugger sends the CRC table address to the device.

# SAM L10/L11 Family

# **PAC - Peripheral Access Controller**

#### Table 15-2. PERID Values

| Peripheral Bridge Name | BridgeNumber | PERID Values |

|------------------------|--------------|--------------|

| А                      | 0            | 0+N          |

| В                      | 1            | 32+N         |

| С                      | 2            | 64+N         |

# 16.12.6 Data

| Name:     | DATA                 |

|-----------|----------------------|

| Offset:   | 0x000C               |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

| 31                      | 30                                                | 29                                                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                  | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DATA[31:24]             |                                                   |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| R/W R/W R/W R/W R/W R/W |                                                   |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 0                       | 0                                                 | 0                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                         |                                                   |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 23                      | 22                                                | 21                                                                                                                                                                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                         |                                                   |                                                                                                                                                                                                                                       | DATA[                                                                                                                                                                                                                                                                                                                                               | 23:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| R/W                     | R/W                                               | R/W                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0                       | 0                                                 | 0                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                         |                                                   |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |