# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 24-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10d16a-yut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

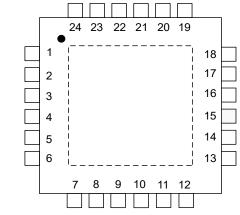

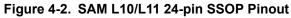

## 4. Pinouts

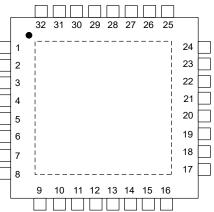

Figure 4-1. SAM L10/L11 24-pin VQFN Pinout

Figure 4-3. SAM L10/L11 32-pin VQFN and TQFP Pinout

#### Table 10-19. SAM L11 BOCOR Mapping

| Offset    | Bit<br>Pos. |          | Name                 |  |  |  |  |  |

|-----------|-------------|----------|----------------------|--|--|--|--|--|

| 0x00      | 7:0         |          | Reserved             |  |  |  |  |  |

| 0x01      | 15:8        |          | BS                   |  |  |  |  |  |

| 0x02      | 23:16       | Reserved | BNSC                 |  |  |  |  |  |

| 0x03      | 31:24       |          | BOOTOPT              |  |  |  |  |  |

| 0x04      | 39:32       |          | BOOTPROT             |  |  |  |  |  |

| 0x05      | 47:40       |          | Reserved             |  |  |  |  |  |

| 0x06      | 55:48       |          | Reserved BCREN BCWEN |  |  |  |  |  |

| 0x07      | 63:56       |          | Reserved             |  |  |  |  |  |

| 0x08-0x0B | 95:64       |          | BOCORCRC             |  |  |  |  |  |

| 0x0C-0x0F | 127:96      |          | ROMVERSION           |  |  |  |  |  |

| 0x10-0x1F | 255:128     |          | CEKEY0               |  |  |  |  |  |

| 0x20-0x2F | 383:256     |          | CEKEY1               |  |  |  |  |  |

| 0x30-0x3F | 511:384     |          | CEKEY2               |  |  |  |  |  |

| 0x40-0x4F | 639:512     |          | CRCKEY               |  |  |  |  |  |

| 0x50-0x6F | 895:640     |          | BOOTKEY              |  |  |  |  |  |

| 0x70-0xDF | 1791:896    |          | Reserved             |  |  |  |  |  |

| 0xE0-0xFF | 2047:1792   |          | BOCORHASH            |  |  |  |  |  |

#### 10.3 Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following addresses of the NVM Rows memory space:

- Word 0: 0x0080A00C

- Word 1: 0x0080A040

- Word 2: 0x0080A044

- Word 3: 0x0080A048

Note: The uniqueness of the serial number is only guaranteed when considering all 128 bits.

PAC - Peripheral Access Controller

Bits 1, 2, 3 – SERCOM Interrupt Flag for SERCOMn [n = 2..0]

Bit 0 – EVSYS Interrupt Flag for EVSYS

#### 16.12.14 CoreSight ROM Table Entry 1

| Name:     | ENTRY1               |

|-----------|----------------------|

| Offset:   | 0x1004               |

| Reset:    | 0xXXXXX00X           |

| Property: | PAC Write-Protection |

|           |                      |

| Bit    | 31 | 30   | 29      | 28    | 27       | 26 | 25  | 24    |

|--------|----|------|---------|-------|----------|----|-----|-------|

|        |    |      |         | ADDOF | F[19:12] |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | x  | х    | x       | x     | х        | x  | x   | x     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 23 | 22   | 21      | 20    | 19       | 18 | 17  | 16    |

|        |    |      |         | ADDO  | FF[11:4] |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | x  | х    | x       | x     | х        | х  | х   | x     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 15 | 14   | 13      | 12    | 11       | 10 | 9   | 8     |

|        |    | ADDO | FF[3:0] |       |          |    |     |       |

| Access | R  | R    | R       | R     |          |    |     |       |

| Reset  | x  | x    | x       | x     |          |    |     |       |

|        |    |      |         |       |          |    |     |       |

| Bit    | 7  | 6    | 5       | 4     | 3        | 2  | 1   | 0     |

|        |    |      |         |       |          |    | FMT | EPRES |

| Access |    |      |         |       |          |    | R   | R     |

| Reset  |    |      |         |       |          |    | 1   | x     |

#### Bits 31:12 - ADDOFF[19:0] Address Offset

The base address of the component, relative to the base address of this ROM table.

#### Bit 1 – FMT Format

Always read as '1', indicating a 32-bit ROM table.

#### Bit 0 – EPRES Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

| 20.8.2 | Control B                               |                            |          |   |   |   |   |       |

|--------|-----------------------------------------|----------------------------|----------|---|---|---|---|-------|

|        | Name:<br>Offset:<br>Reset:<br>Property: | CTRLB<br>0x01<br>0x00<br>– |          |   |   |   |   |       |

| Bi     | t 7                                     | 6                          | 5        | 4 | 3 | 2 | 1 | 0     |

|        |                                         |                            |          |   |   |   |   | START |

| Acces  | s                                       |                            | ·        |   |   |   |   | W     |

| Rese   | t                                       |                            |          |   |   |   |   | 0     |

|        | Bit 0 – STA                             | <b>RT</b> Start Meas       | surement |   |   |   |   |       |

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Writing a '0' has no effect.        |

| 1     | Writing a '1' starts a measurement. |

## 25. SUPC – Supply Controller

#### 25.1 Overview

The Supply Controller (SUPC) manages the voltage reference and power supply of the device.

The SUPC controls the voltage regulators for the core (VDDCORE) domain. It sets the voltage regulators according to the sleep modes, or the user configuration. In active mode, the voltage regulators can be selected on the fly between LDO (low-dropout) type regulator or Buck converter.

The SUPC embeds two Brown-Out Detectors. BOD33 monitors the voltage applied to the device (VDD) and BOD12 monitors the internal voltage to the core (VDDCORE). The BOD can monitor the supply voltage continuously (continuous mode) or periodically (sampling mode).

The SUPC generates also a selectable reference voltage and a voltage dependent on the temperature which can be used by analog modules like the ADC or DAC.

### 25.2 Features

- Voltage Regulator System

- Main voltage regulator: LDO or Buck Converter in active mode (MAINVREG)

- Low-Power voltage regulator in Standby mode (LPVREG)

- Adjustable VDDCORE to the Sleep mode or the performance level

- Controlled VDDCORE voltage slope when changing VDDCORE

- Voltage Reference System

- Reference voltage for ADC and DAC

- Temperature sensor

- 3.3V Brown-Out Detector (BOD33)

- Programmable threshold

- Threshold value loaded from NVM User Row at startup

- Triggers resets or interrupts or event. Action loaded from NVM User Row

- Operating modes:

- Continuous mode

- Sampled mode for low power applications with programmable sample frequency

- Hysteresis value from Flash User Calibration

- 1.2V Brown-Out Detector (BOD12)

- Internal non-configurable Brown-Out Detector

#### 25.8.8 Event Control

Name:EVCTRLOffset:0x2CReset:0x000000Property:Enable-Protected, PAC Write-Protection

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25         | 24 |

|--------|----|----|----|----|----|----|------------|----|

|        |    |    |    |    |    |    |            |    |

| Access |    |    |    |    |    |    |            |    |

| Reset  |    |    |    |    |    |    |            |    |

|        |    |    |    |    |    |    |            |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17         | 16 |

|        |    |    |    |    |    |    |            |    |

| Access |    |    | •  |    |    |    | • •        |    |

| Reset  |    |    |    |    |    |    |            |    |

|        |    |    |    |    |    |    |            |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9          | 8  |

|        |    |    |    |    |    |    |            |    |

| Access |    |    |    |    |    |    | •          |    |

| Reset  |    |    |    |    |    |    |            |    |

|        |    |    |    |    |    |    |            |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1          | 0  |

|        |    |    |    |    |    |    | BOD33DETEO |    |

| Access |    |    |    |    |    |    | R/W        |    |

| Reset  |    |    |    |    |    |    | 0          |    |

|        |    |    |    |    |    |    |            |    |

#### Bit 1 – BOD33DETEO BOD33 Detection Event Output Enable

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | BOD33 detection event output is disabled and event will not be generated |

| 1     | BOD33 detection event output is enabled and event will be generated      |

## 26. WDT – Watchdog Timer

#### 26.1 Overview

The Watchdog Timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is configured to a predefined time-out period, and is constantly running when enabled. If the WDT is not cleared within the time-out period, it will issue a system reset. An early-warning interrupt is available to indicate an upcoming watchdog time-out condition.

The window mode makes it possible to define a time slot (or window) inside the total time-out period during which the WDT must be cleared. If the WDT is cleared outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes the WDT to be cleared frequently.

When enabled, the WDT will run in active mode and all sleep modes. It is asynchronous and runs from a CPU-independent clock source. The WDT will continue operation and issue a system reset or interrupt even if the main clocks fail.

#### 26.2 Features

- Issues a system reset if the Watchdog Timer is not cleared before its time-out period

- Early Warning interrupt generation

- Asynchronous operation from dedicated oscillator

- Two types of operation

- Normal

- Window mode

- Selectable time-out periods

- From 8 cycles to 16,384 cycles in Normal mode

- From 16 cycles to 32,768 cycles in Window mode

- Always-On capability

#### 26.8.7 Synchronization Busy

|        | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x08<br>0x00000000<br>- |       |          |          |     |        |    |

|--------|-----------------------------------------|-------------------------------------|-------|----------|----------|-----|--------|----|

| Bit    | 31                                      | 30                                  | 29    | 28       | 27       | 26  | 25     | 24 |

|        |                                         |                                     |       |          |          |     |        |    |

| Access |                                         |                                     |       |          |          |     |        |    |

| Reset  |                                         |                                     |       |          |          |     |        |    |

| Bit    | 23                                      | 22                                  | 21    | 20       | 19       | 18  | 17     | 16 |

| DIL    | 23                                      | 22                                  | 21    | 20       | 19       | 10  | 17     | 10 |

| Access |                                         |                                     |       |          |          |     |        |    |

| Reset  |                                         |                                     |       |          |          |     |        |    |

| Reset  |                                         |                                     |       |          |          |     |        |    |

| Bit    | 15                                      | 14                                  | 13    | 12       | 11       | 10  | 9      | 8  |

|        |                                         |                                     |       |          |          |     |        |    |

| Access |                                         |                                     |       |          |          |     |        |    |

| Reset  |                                         |                                     |       |          |          |     |        |    |

|        |                                         |                                     |       |          |          |     |        |    |

| Bit    | 7                                       | 6                                   | 5     | 4        | 3        | 2   | 1      | 0  |

|        |                                         |                                     | CLEAR | ALWAYSON | RUNSTDBY | WEN | ENABLE |    |

| Access |                                         |                                     | R     | R        | R        | R   | R      |    |

| Reset  |                                         |                                     | 0     | 0        | 0        | 0   | 0      |    |

#### Bit 5 – CLEAR Clear Synchronization Busy

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Write synchronization of the CLEAR register is complete. |

| 1     | Write synchronization of the CLEAR register is ongoing.  |

#### Bit 4 – ALWAYSON Always-On Synchronization Busy

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | Write synchronization of the CTRLA.ALWAYSON bit is complete. |

| 1     | Write synchronization of the CTRLA.ALWAYSON bit is ongoing.  |

#### Bit 3 – RUNSTDBY Run-In-Standby Synchronization Busy

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | Write synchronization of the CTRLA.RUNSTDBY bit is complete. |

| 1     | Write synchronization of the CTRLA.RUNSTDBY bit is ongoing.  |

#### Bit 2 – WEN Window Enable Synchronization Busy

| Va | lue | Description                                             |

|----|-----|---------------------------------------------------------|

| 0  |     | Write synchronization of the CTRLA.WEN bit is complete. |

| 1  |     | Write synchronization of the CTRLA.WEN bit is ongoing.  |

#### 27.8.2 Control B in COUNT32 mode (CTRLA.MODE=0)

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15    | 14     | 13        | 12     | 11 | 10  | 9         | 8     |

|--------|-------|--------|-----------|--------|----|-----|-----------|-------|

|        | SEPTO |        | ACTF[2:0] |        |    |     | DEBF[2:0] |       |

| Access | R/W   | R/W    | R/W       | R/W    |    | R/W | R/W       | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    | 0   | 0         | 0     |

|        |       |        |           |        |    |     |           |       |

| Bit    | 7     | 6      | 5         | 4      | 3  | 2   | 1         | 0     |

|        | DMAEN | RTCOUT | DEBASYNC  | DEBMAJ |    |     |           | GP0EN |

| Access | R/W   | R/W    | R/W       | R/W    |    |     |           | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    |     |           | 0     |

#### Bit 15 – SEPTO Separate Tamper Outputs

| Value | Description                  |

|-------|------------------------------|

| 0     | IN[n] is compared to OUT[0]. |

| 1     | IN[n] is compared to OUT[n]. |

#### Bits 14:12 – ACTF[2:0] Active Layer Frequency

These bits define the prescaling factor for the RTC clock output (OUT) used during active layer protection in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_OUT = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_OUT = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_OUT = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_OUT = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_OUT = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_OUT = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_OUT = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_OUT = CLK_RTC / 256 |

#### Bits 10:8 - DEBF[2:0] Debounce Frequency

These bits define the prescaling factor for the input debouncers in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_DEB = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_DEB = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_DEB = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_DEB = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_DEB = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_DEB = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_DEB = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_DEB = CLK_RTC / 256 |

Bit 3 – CLOCK Clock Register Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Read/write synchronization for CLOCK register is complete. |

| 1     | Read/write synchronization for CLOCK register is ongoing.  |

**Bit 2 – FREQCORR** Frequency Correction Synchronization Busy Status

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Write synchronization for FREQCORR register is complete. |

| 1     | Write synchronization for FREQCORR register is ongoing.  |

## Bit 1 – ENABLE Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

#### Bit 0 – SWRST Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

#### • No synchronization

When executing an operation that requires synchronization, the corresponding status bit in the Synchronization Busy register (SYNCBUSY.xxx) will be set immediately, and cleared when synchronization is complete.

If an operation that requires synchronization is executed while SYNCBUSY.xxx is one, the operation is discarded and an error is generated. The following bits need synchronization when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

#### 31.8.7 Data Scramble Control

| Name:     | DSCC                                  |

|-----------|---------------------------------------|

| Offset:   | 0x00C                                 |

| Reset:    | 0x0000000                             |

| Property: | PAC Write-Protected, Enable-Protected |

| W<br>0 |

|--------|

|        |

| 0      |

|        |

|        |

| 16     |

|        |

| W      |

| 0      |

|        |

| 8      |

|        |

| W      |

| 0      |

|        |

| 0      |

|        |

| W      |

| 0      |

| -      |

#### Bit 31 – DSCEN Data Scramble Enable

| Value | Description                |

|-------|----------------------------|

| 0     | TrustRAM is not scrambled. |

| 1     | TrustRAM is scrambled.     |

#### Bits 29:0 – DSCKEY[29:0] Data Scramble Key

The key value used for data scrambling. Any value written to this field is XOR'ed with the previous data. Writing '1' to CTRLA.SWRST will reset this field to 0. These bits will always return zero when read.

- 7.2. Configure the Parity Mode bit in the CTRLB register (CTRLB.PMODE) for even or odd parity.

- 8. Configure the number of stop bits in the Stop Bit Mode bit in the CTRLB register (CTRLB.SBMODE).

- 9. When using an internal clock, write the Baud register (BAUD) to generate the desired baud rate.

- 10. Enable the transmitter and receiver by writing '1' to the Receiver Enable and Transmitter Enable bits in the CTRLB register (CTRLB.RXEN and CTRLB.TXEN).

#### 35.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

Refer to the CTRLA register description for details.

#### 35.6.2.3 Clock Generation and Selection

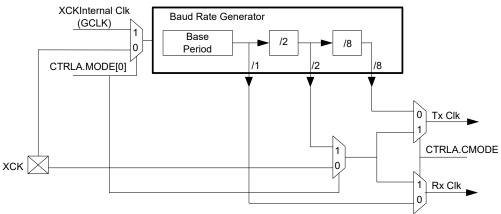

For both synchronous and asynchronous modes, the clock used for shifting and sampling data can be generated internally by the SERCOM baud-rate generator or supplied externally through the XCK line.

The synchronous mode is selected by writing a '1' to the Communication Mode bit in the Control A register (CTRLA.CMODE), the asynchronous mode is selected by writing a zero to CTRLA.CMODE.

The internal clock source is selected by writing 0x1 to the Operation Mode bit field in the Control A register (CTRLA.MODE), the external clock source is selected by writing 0x0 to CTRLA.MODE.

The SERCOM baud-rate generator is configured as in the figure below.

In asynchronous mode (CTRLA.CMODE=0), the 16-bit Baud register value is used.

In synchronous mode (CTRLA.CMODE=1), the eight LSBs of the Baud register are used. Refer to *Clock Generation – Baud-Rate Generator* for details on configuring the baud rate.

#### Figure 35-3. Clock Generation

#### **Related Links**

34.6.2.3 Clock Generation – Baud-Rate Generator 34.6.2.3.1 Asynchronous Arithmetic Mode BAUD Value Selection

#### 35.6.2.3.1 Synchronous Clock Operation

In synchronous mode, the CTRLA.MODE bit field determines whether the transmission clock line (XCK) serves either as input or output. The dependency between clock edges, data sampling, and data change

#### 35.8.10 Synchronization Busy

| Name:<br>Offset:<br>Reset:<br>Property: |    | SYNCBUSY<br>0x1C<br>0x00000000<br>- |    |    |          |       |        |       |

|-----------------------------------------|----|-------------------------------------|----|----|----------|-------|--------|-------|

| Bit                                     | 31 | 30                                  | 29 | 28 | 27       | 26    | 25     | 24    |

|                                         |    |                                     |    |    |          |       |        |       |

| Access                                  |    |                                     |    |    |          |       |        |       |

| Reset                                   |    |                                     |    |    |          |       |        |       |

| Bit                                     | 23 | 22                                  | 21 | 20 | 19       | 18    | 17     | 16    |

| DIL                                     | 23 | 22                                  | 21 | 20 | 19       | 10    | 17     | 10    |

| Access                                  |    |                                     |    |    |          |       |        |       |

| Reset                                   |    |                                     |    |    |          |       |        |       |

| Reset                                   |    |                                     |    |    |          |       |        |       |

| Bit                                     | 15 | 14                                  | 13 | 12 | 11       | 10    | 9      | 8     |

|                                         |    |                                     |    |    |          |       |        |       |

| Access                                  |    |                                     |    |    |          |       |        |       |

| Reset                                   |    |                                     |    |    |          |       |        |       |

|                                         |    |                                     |    |    |          |       |        |       |

| Bit                                     | 7  | 6                                   | 5  | 4  | 3        | 2     | 1      | 0     |

|                                         |    |                                     |    |    | RXERRCNT | CTRLB | ENABLE | SWRST |

| Access                                  |    |                                     |    |    | R        | R     | R      | R     |

| Reset                                   |    |                                     |    |    | 0        | 0     | 0      | 0     |

#### Bit 3 – RXERRCNT Receive Error Count Synchronization Busy

The RXERRCNT register is automatically synchronized to the APB domain upon error. When returning from sleep, this bit will be raised until the new value is available to be read.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | RXERRCNT synchronization is not busy. |

| 1     | RXERRCNT synchronization is busy.     |

#### Bit 2 – CTRLB CTRLB Synchronization Busy

Writing to the CTRLB register when the SERCOM is enabled requires synchronization. When writing to CTRLB the SYNCBUSY.CTRLB bit will be set until synchronization is complete. If CTRLB is written while SYNCBUSY.CTRLB is asserted, an APB error will be generated.

| Value | Description                        |

|-------|------------------------------------|

| 0     | CTRLB synchronization is not busy. |

| 1     | CTRLB synchronization is busy.     |

#### Bit 1 – ENABLE SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

#### 35.8.11 Receive Error Count

| Name:     | RXERRCNT          |

|-----------|-------------------|

| Offset:   | 0x20              |

| Reset:    | 0x00              |

| Property: | Read-Synchronized |

| Bit    | 7 | 6 | 5 | 4     | 3        | 2 | 1 | 0 |

|--------|---|---|---|-------|----------|---|---|---|

| ĺ      |   |   |   | RXERR | CNT[7:0] |   |   |   |

| Access | R | R | R | R     | R        | R | R | R |

| Reset  | 0 | 0 | 0 | 0     | 0        | 0 | 0 | 0 |

#### Bits 7:0 - RXERRCNT[7:0] Receive Error Count

This register records the total number of parity errors and NACK errors combined in ISO7816 mode (CTRLA.FORM=0x7).

This register is automatically cleared on read.

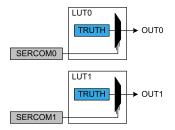

#### Figure 40-11. SERCOM Input Selection

#### **Related Links**

- 32. PORT I/O Pin Controller

- 18. GCLK Generic Clock Controller

- 42. AC Analog Comparators

- 38. TC Timer/Counter

- 34. SERCOM Serial Communication Interface

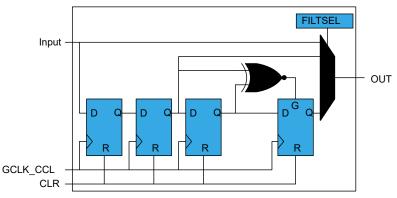

#### 40.6.2.5 Filter

By default, the LUT output is a combinatorial function of the LUT inputs. This may cause some short glitches when the inputs change value. These glitches can be removed by clocking through filters, if demanded by application needs.

The Filter Selection bits in LUT Control register (LUTCTRLx.FILTSEL) define the synchronizer or digital filter options. When a filter is enabled, the OUT output will be delayed by two to five GCLK cycles. One APB clock after the corresponding LUT is disabled, all internal filter logic is cleared. **Note:** Events used as LUT input will also be filtered, if the filter is enabled.

#### Figure 40-12. Filter

#### 40.6.2.6 Edge Detector

The edge detector can be used to generate a pulse when detecting a rising edge on its input. To detect a falling edge, the TRUTH table should be inverted.

The edge detector is enabled by writing '1' to the Edge Selection bit in LUT Control register (LUTCTRLx.EDGESEL). In order to avoid unpredictable behavior, either the filter or synchronizer must be enabled.

Edge detection is disabled by writing a '0' to LUTCTRLx.EDGESEL. After disabling a LUT, the corresponding internal Edge Detector logic is cleared one APB clock cycle later.

#### 43.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|----------|---|---|---|---|--------|-------|

|        |   | RUNSTDBY |   |   |   |   | ENABLE | SWRST |

| Access |   | R/W      |   |   |   |   | R/W    | R/W   |

| Reset  |   | 0        |   |   |   |   | 0      | 0     |

#### Bit 6 - RUNSTDBY Run in Standby

This bit is not synchronized

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | The DAC output buffer is disabled in standby sleep mode.    |

| 1     | The DAC output buffer can be enabled in standby sleep mode. |

#### Bit 1 – ENABLE Enable DAC Controller

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the DAC to their initial state, and the DAC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

## SAM L10/L11 Family

## 125°C Electrical Characteristics

### Table 47-9. Single Ended Mode <sup>(1)</sup>

| Qumbal | Parameter                        | Conditions                                        |                                                  | Measureme | Unit    |         |      |

|--------|----------------------------------|---------------------------------------------------|--------------------------------------------------|-----------|---------|---------|------|

| Symbol | S                                | Conditions                                        |                                                  | Min       | Тур     | Max     | Unit |

| ENOB   | Effective<br>Number of<br>bits   | Fadc =<br>1Msps                                   | Vref=2.0V<br>Vddana=3.<br>0V                     | 8.0       | 9.3     | 9.7     | bits |

|        |                                  |                                                   | Vref=1.0V<br>Vddana=1.<br>6V to 3.6V             | 7.9       | 8.2     | 9.4     |      |

|        |                                  |                                                   | Vref=Vdda<br>na=1.6V to<br>3.6V                  | 8.6       | 9.2     | 9.9     |      |

|        |                                  |                                                   | Bandgap<br>Reference,<br>Vddana=1.<br>6V to 3.6V | 7.8       | 8.4     | 8.9     |      |

| TUE    | Total<br>Unadjusted<br>Error     | without<br>offset and<br>gain<br>compensati<br>on | Vref=2.0V<br>Vddana=3.<br>0V                     | -         | 12      | 66      | LSB  |

| INL    | Integral<br>Non<br>Linearity     | without<br>offset and<br>gain<br>compensati<br>on | Vref=2.0V<br>Vddana=3.<br>0V                     | -         | +/-3.4  | +/-9.1  |      |

| DNL    | Differential<br>Non<br>Linearity | without<br>offset and<br>gain<br>compensati<br>on | Vref=2.0V<br>Vddana=3.<br>0V                     | -         | +0.9/-1 | +1.8/-1 |      |

| Gain   | Gain Error                       | without<br>gain<br>compensati<br>on               | Vref=1V<br>Vddana=1.<br>6V to 3.6V               | -         | +/-0.3  | +/-5.1  | %    |

|        |                                  |                                                   | Vref=3V<br>Vddana=1.<br>6V to 3.6V               | -         | +/-0.3  | +/-5.1  |      |

|        |                                  |                                                   | Bandgap<br>Reference                             | -         | +/-0.4  | +/-5.1  |      |

|        |                                  |                                                   | Vref=Vdda<br>na=1.6V to<br>3.6V                  | -         | +/-0.2  | +/-0.8  |      |

AC and DC Characteristics Graphs

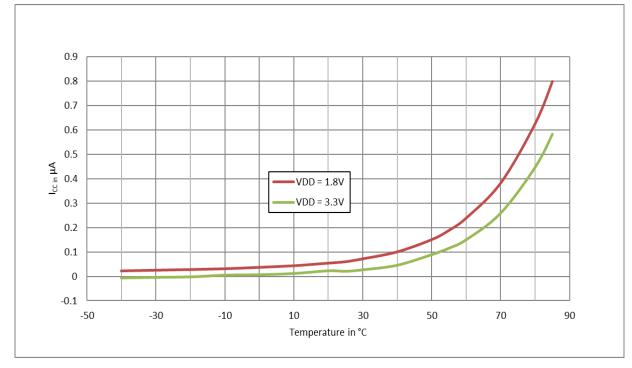

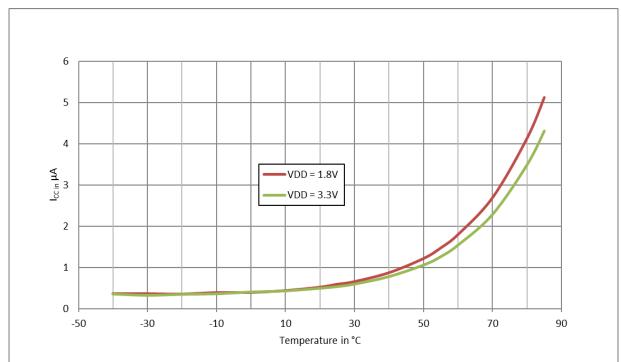

## Figure 48-2. Power Consumption over Temperature in Standby Sleep Mode with PDSW in Retention state

#### Power Consumption in Off Sleep Mode

Operating conditions:

• VDDIO = 3.3V or 1.8V

Figure 48-3. Power Consumption over Temperature in Off Sleep Mode