Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e14a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SAM L10/L11 Family

## **Processor and Architecture**

| Module                              | Source   | NVIC line |

|-------------------------------------|----------|-----------|

|                                     | MC 1     |           |

|                                     | OVF      |           |

| TC1 – Timer Counter 1               | ERR A    | 35        |

|                                     | MC 0     |           |

|                                     | MC 1     |           |

|                                     | OVF      |           |

| TC2 – Timer Counter 2               | ERR A    | 36        |

|                                     | MC 0     |           |

|                                     | MC 1     |           |

|                                     | OVF      |           |

| ADC – Analog-to-Digital Converter   | OVERRUN  | 37        |

|                                     | WINMON   |           |

|                                     | RESRDY   | 38        |

| AC – Analog Comparator              | COMP 0   | 39        |

|                                     | COMP 1   |           |

|                                     | WIN 0    |           |

| DAC – Digital-to-Analog Converter   | UNDERRUN | 40        |

|                                     | EMPTY    | 41        |

| PTC – Peripheral Touch Controller   | EOC      | 42        |

|                                     | WCOMP    |           |

| TRNG - True Random Number Generator | DATARDY  | 43        |

| TRAM - Trust RAM                    | DRP      | 44        |

|                                     | ERR      |           |

#### Note:

1. NSCHK interrupt sources will not generate any interrupts for SAM L10 devices.

## 11.3 High-Speed Bus System

#### 11.3.1 Features

The High-Speed Bus Matrix has the following features:

- 32-bit data bus

- Allows concurrent accesses from different masters to different slaves

- Operation at a one-to-one clock frequency with the bus masters

## 11.3.2 Configuration

There are two master-to-slave connections to optimize system bandwidth:

• Multi-Slave Masters which are connected through the AHB bus matrix

#### Table 11-4. AHB Multi-Slave Masters

AHB Multi-Slave Masters

Cortex-M23 Processor

DSU - Device Service Unit

DMAC - Direct Memory Access Controller / Data Access

# 16.11 Register Summary

| Offset             | Name     | Bit Pos. |                            |                            |          |         |                      |            |         |        |

|--------------------|----------|----------|----------------------------|----------------------------|----------|---------|----------------------|------------|---------|--------|

| 0x00               | CTRL     | 7:0      |                            |                            |          |         | MBIST                | CRC        |         | SWRST  |

| 0x01               | STATUSA  | 7:0      |                            |                            | BREXT    | PERR    | FAIL                 | BERR       | CRSTEXT | DONE   |

| 0x02               | STATUSB  | 7:0      | BCCDx                      | BCCDx                      | DCCDx    | DCCDx   | HPE                  | DBGPRES    | DAL     | [1:0]  |

| 0x03               | Reserved |          |                            |                            |          |         |                      |            |         |        |

|                    |          | 7:0      |                            |                            | ADD      | R[5:0]  | 1                    |            | AMOI    | D[1:0] |

| 004                |          | 15:8     |                            |                            |          | ADDF    | R[13:6]              |            | 1       |        |

| 0x04               | ADDR     | 23:16    |                            |                            |          | ADDR    | [21:14]              |            |         |        |

|                    |          | 31:24    |                            |                            |          | ADDR    | [29:22]              |            |         |        |

|                    |          | 7:0      |                            |                            | LENG     | TH[5:0] |                      |            |         |        |

|                    |          | 15:8     |                            |                            |          | LENGT   | <sup>-</sup> H[13:6] |            |         |        |

| 0x08               | LENGTH   | 23:16    |                            |                            |          | LENGT   | H[21:14]             |            |         |        |

|                    |          | 31:24    |                            |                            |          | LENGT   | H[29:22]             |            |         |        |

|                    |          | 7:0      |                            |                            |          |         | A[7:0]               |            |         |        |

|                    |          | 15:8     |                            |                            |          |         | [15:8]               |            |         |        |

| 0x0C               | DATA     | 23:16    |                            |                            |          | DATA    | [23:16]              |            |         |        |

|                    |          | 31:24    |                            |                            |          |         | [31:24]              |            |         |        |

|                    |          | 7:0      |                            |                            |          |         | A[7:0]               |            |         |        |

|                    |          | 15:8     |                            |                            |          |         | [15:8]               |            |         |        |

| 0x10               | DCC0     | 23:16    | DATA[23:16]                |                            |          |         |                      |            |         |        |

|                    |          | 31:24    |                            | DATA[23:16]<br>DATA[31:24] |          |         |                      |            |         |        |

|                    |          | 7:0      |                            | DATA[7:0]                  |          |         |                      |            |         |        |

|                    |          | 15:8     | DATA[15:8]                 |                            |          |         |                      |            |         |        |

| 0x14               | DCC1     | 23:16    | DATA[23:16]                |                            |          |         |                      |            |         |        |

|                    |          | 31:24    |                            | DATA[31:24]                |          |         |                      |            |         |        |

|                    |          | 7:0      |                            |                            |          |         | EL[7:0]              |            |         |        |

|                    |          | 15:8     |                            | DIE[3:0] REVISION[         |          |         |                      |            | ON[3·0] |        |

| 0x18               | DID      | 23:16    | FAMILY[0:0]                | DIL                        | [0.0]    |         | SERI                 | ES[5:0]    |         |        |

|                    |          | 31:24    |                            | PPOCES                     | SOR[3:0] |         | JEN                  |            | _Y[4:1] |        |

|                    |          | 7:0      |                            | FROCE                      | 501(5.0] |         |                      |            |         | 2[1:0] |

|                    |          | 15:8     |                            |                            |          |         | DCCDMA               | LEVEL[1:0] | LQOS    | 5[1.0] |

| 0x1C               | CFG      |          |                            |                            |          |         |                      |            |         |        |

|                    |          | 23:16    |                            |                            |          |         |                      |            |         |        |

|                    |          | 31:24    |                            |                            |          | DAT     | A[7:0]               |            |         |        |

|                    |          | 7:0      |                            |                            |          |         | A[7:0]               |            |         |        |

| 0x20               | BCC0     | 15:8     | DATA[15:8]                 |                            |          |         |                      |            |         |        |

|                    |          | 23:16    | DATA[23:16]<br>DATA[31:24] |                            |          |         |                      |            |         |        |

|                    |          | 31:24    |                            |                            |          |         |                      |            |         |        |

|                    |          | 7:0      |                            |                            |          |         | 4[7:0]               |            |         |        |

| 0x24               | BCC1     | 15:8     |                            |                            |          |         | [15:8]               |            |         |        |

|                    |          | 23:16    |                            |                            |          |         | [23:16]              |            |         |        |

|                    |          | 31:24    |                            |                            |          | DATA    | [31:24]              |            |         |        |

| 0x28<br><br>0x0FFF | Reserved |          |                            |                            |          |         |                      |            |         |        |

# SAM L10/L11 Family

# **GCLK - Generic Clock Controller**

| index(m) | Name                    | Description        |

|----------|-------------------------|--------------------|

| 9        | GCLK_EVSYS_CHANNEL_3    | EVSYS_CHANNEL_3    |

| 10       | GCLK_SERCOM[0,1,2]_SLOW | SERCOM[0,1,2]_SLOW |

| 11       | GCLK_SERCOM0_CORE       | SERCOM0_CORE       |

| 12       | GCLK_SERCOM1_CORE       | SERCOM1_CORE       |

| 13       | GCLK_SERCOM2_CORE       | SERCOM2_CORE       |

| 14       | GCLK_TC0, GCLK_TC1      | TC0,TC1            |

| 15       | GCLK_TC2                | TC2                |

| 16       | GCLK_ADC                | ADC                |

| 17       | GCLK_AC                 | AC                 |

| 18       | GCLK_DAC                | DAC                |

| 19       | GCLK_PTC                | PTC                |

| 20       | GCLK_CCL                | CCL                |

## 20.8.3 Configuration A

| Name:     | CFGA                                   |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-protected |

| Bit    | 15     | 14  | 13  | 12    | 11      | 10  | 9   | 8   |

|--------|--------|-----|-----|-------|---------|-----|-----|-----|

| ĺ      | DIVREF |     |     |       |         |     |     |     |

| Access | R/W    |     |     |       |         |     |     |     |

| Reset  | 0      |     |     |       |         |     |     |     |

| Bit    | 7      | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|        |        |     |     | REFNU | JM[7:0] |     |     |     |

| Access | R/W    | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0      | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

# Bit 15 – DIVREF Divide Reference Clock

Divides the reference clock by 8

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The reference clock is divided by 1. |

| 1     | The reference clock is divided by 8. |

## Bits 7:0 - REFNUM[7:0] Number of Reference Clock Cycles

Selects the duration of a measurement in number of CLK\_FREQM\_REF cycles. This must be a non-zero value, i.e. 0x01 (one cycle) to 0xFF (255 cycles).

## 25.5.5 Interrupts

The interrupt request lines are connected to the interrupt controller. Using the SUPC interrupts requires the interrupt controller to be configured first.

#### 25.5.6 Events

The events are connected to the Event System. Refer to the Event System section for details on how to configure the Event System.

#### 25.5.7 Debug Operation

When the CPU is halted in debug mode, the SUPC continues normal operation. If the SUPC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

If debugger cold-plugging is detected by the system, BOD33 and BOD12 resets will be masked. The BOD resets keep running under hot-plugging. This allows to correct a BOD33 user level too high for the available supply.

#### 25.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

Note: Not all registers with write-access can be write-protected.

PAC Write-Protection is not available for the following registers:

• Interrupt Flag Status and Clear register (INTFLAG)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

## Related Links

15. PAC - Peripheral Access Controller

## 25.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 25.5.10 Analog Connections

Not applicable.

## 25.6 Functional Description

## 25.6.1 Voltage Regulator System Operation

## 25.6.1.1 Enabling, Disabling, and Resetting

The LDO main voltage regulator is enabled after any Reset. The main voltage regulator (MAINVREG) can be disabled by writing the Enable bit in the VREG register (VREG.ENABLE) to zero. The main

#### 25.8.1 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|----|----|----|----|------------|----------|----------|----------|

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 23 | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 15 | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |    |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |    |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |    |    |    |    | 0          | 0        |          | 0        |

|        |    |    |    |    |            |          |          |          |

| Bit    | 7  | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |    |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access | -  |    |    |    |            | R/W      | R/W      | R/W      |

| Reset  |    |    |    |    |            | 0        | 0        | 0        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit will clear on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY).

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Low Power Ready interrupt is disabled.                                                                                     |

| 1     | The Low Power Ready interrupt is enabled and an interrupt request will be generated when the ULPVREFRDY Interrupt Flag is set. |

Bit 10 – VCORERDY VDDCORE Voltage Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the VDDCORE Ready Interrupt Enable bit, which disables the VDDCORE Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The VDDCORE Ready interrupt is disabled.                                                                                   |

| 1     | The VDDCORE Ready interrupt is enabled and an interrupt request will be generated when the VCORERDY Interrupt Flag is set. |

## 27.8.2 Control B in COUNT32 mode (CTRLA.MODE=0)

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15    | 14     | 13        | 12     | 11 | 10  | 9         | 8     |

|--------|-------|--------|-----------|--------|----|-----|-----------|-------|

|        | SEPTO |        | ACTF[2:0] |        |    |     | DEBF[2:0] |       |

| Access | R/W   | R/W    | R/W       | R/W    |    | R/W | R/W       | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    | 0   | 0         | 0     |

|        |       |        |           |        |    |     |           |       |

| Bit    | 7     | 6      | 5         | 4      | 3  | 2   | 1         | 0     |

|        | DMAEN | RTCOUT | DEBASYNC  | DEBMAJ |    |     |           | GP0EN |

| Access | R/W   | R/W    | R/W       | R/W    |    |     |           | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    |     |           | 0     |

## Bit 15 – SEPTO Separate Tamper Outputs

| Value | Description                  |

|-------|------------------------------|

| 0     | IN[n] is compared to OUT[0]. |

| 1     | IN[n] is compared to OUT[n]. |

## Bits 14:12 – ACTF[2:0] Active Layer Frequency

These bits define the prescaling factor for the RTC clock output (OUT) used during active layer protection in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_OUT = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_OUT = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_OUT = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_OUT = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_OUT = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_OUT = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_OUT = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_OUT = CLK_RTC / 256 |

## Bits 10:8 - DEBF[2:0] Debounce Frequency

These bits define the prescaling factor for the input debouncers in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_DEB = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_DEB = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_DEB = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_DEB = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_DEB = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_DEB = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_DEB = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_DEB = CLK_RTC / 256 |

## 27.10.14 Tamper Control

| Name:     | TAMPCTRL                               |

|-----------|----------------------------------------|

| Offset:   | 0x60                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31    | 30      | 29    | 28      | 27      | 26      | 25      | 24      |

|--------|-------|---------|-------|---------|---------|---------|---------|---------|

|        |       |         |       |         | DEBNC3  | DEBNC2  | DEBNC1  | DEBNC0  |

| Access |       |         | ·     | •       |         |         |         |         |

| Reset  |       |         |       |         | 0       | 0       | 0       | 0       |

|        |       |         |       |         |         |         |         |         |

| Bit    | 23    | 22      | 21    | 20      | 19      | 18      | 17      | 16      |

|        |       |         |       |         | TAMLVL3 | TAMLVL2 | TAMLVL1 | TAMLVL0 |

| Access |       | •       | •     | •       |         |         |         |         |

| Reset  |       |         |       |         | 0       | 0       | 0       | 0       |

|        |       |         |       |         |         |         |         |         |

| Bit    | 15    | 14      | 13    | 12      | 11      | 10      | 9       | 8       |

|        |       |         |       |         |         |         |         |         |

| Access |       | •       | •     |         |         |         |         |         |

| Reset  |       |         |       |         |         |         |         |         |

|        |       |         |       |         |         |         |         |         |

| Bit    | 7     | 6       | 5     | 4       | 3       | 2       | 1       | 0       |

|        | IN3A0 | CT[1:0] | IN2AC | CT[1:0] | IN1AC   | T[1:0]  | IN0AC   | T[1:0]  |

| Access |       |         |       |         |         |         |         |         |

| Reset  | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0       |

#### Bits 24, 25, 26, 27 - DEBNC Debounce Enable of Tamper Input INn

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Debouncing is disabled for Tamper input INn |

| 1     | Debouncing is enabled for Tamper input INn  |

#### Bits 16, 17, 18, 19 - TAMLVL Tamper Level Select of Tamper Input INn

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | A falling edge condition will be detected on Tamper input INn. |

| 1     | A rising edge condition will be detected on Tamper input INn.  |

## Bits 0:1, 2:3, 4:5, 6:7 - INACT Tamper Channel n Action

These bits determine the action taken by Tamper Channel n.

| Value | Name    | Description                                                          |

|-------|---------|----------------------------------------------------------------------|

| 0x0   | OFF     | Off (Disabled)                                                       |

| 0x1   | WAKE    | Wake and set Tamper flag                                             |

| 0x2   | CAPTURE | Capture timestamp and set Tamper flag                                |

| 0x3   | ACTL    | Compare RTC signal routed between INn and OUT pins . When a mismatch |

|       |         | occurs, capture timestamp and set Tamper flag                        |

# RTC – Real-Time Counter

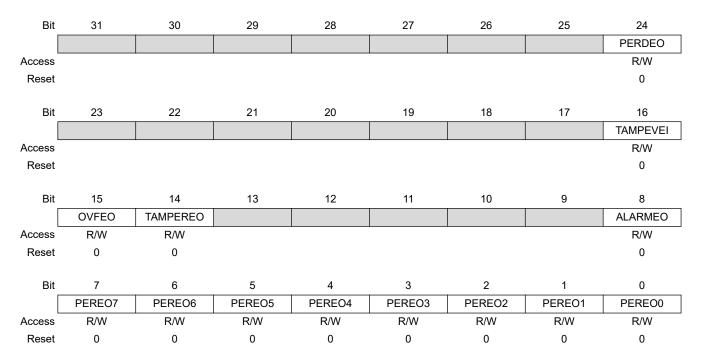

#### 27.12.3 Event Control in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x04                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

#### Bit 24 – PERDEO Periodic Interval Daily Event Output Enable

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | Periodic Daily event is disabled and will not be generated.                        |

| 1     | Periodic Daily event is enabled and will be generated.                             |

|       | The event occurs at the last second of each day depending on the CTRLA.CLKREP bit: |

|       | <ul> <li>If CLKREP = 0, the event will occur at 23:59:59</li> </ul>                |

|       | • If CLKREP = 1, the event will occur at 11:59:59, PM = 1                          |

#### Bit 16 – TAMPEVEI Tamper Event Input Enable

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Tamper event input is disabled, and incoming events will be ignored.                 |

| 1     | Tamper event input is enabled, and all incoming events will capture the CLOCK value. |

#### Bit 15 – OVFEO Overflow Event Output Enable

| V | alue | Description                                                         |

|---|------|---------------------------------------------------------------------|

| 0 |      | Overflow event is disabled and will not be generated.               |

| 1 |      | Overflow event is enabled and will be generated for every overflow. |

- Up to 8 channels

- Enable 8 independent transfers

- Automatic descriptor fetch for each channel

- Suspend/resume operation support for each channel

- Flexible arbitration scheme

- 4 configurable priority levels for each channel

- Fixed or round-robin priority scheme within each priority level

- From 1 to 256KB data transfer in a single block transfer

- Multiple addressing modes

- Static

- Configurable increment scheme

- Optional interrupt generation

- On block transfer complete

- On error detection

- On channel suspend

- 4 event inputs

- One event input for each of the 4 least significant DMA channels

- Can be selected to trigger normal transfers, periodic transfers or conditional transfers

- Can be selected to suspend or resume channel operation

- 4 event outputs

- One output event for each of the 4 least significant DMA channels

- Selectable generation on AHB, block, or transaction transfer complete

- Error management supported by write-back function

- Dedicated Write-Back memory section for each channel to store ongoing descriptor transfer

- CRC polynomial software selectable to

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE<sup>®</sup> 802.3)

are not accessible. When defined non-secure callable sections have the same attributes as the secure sections, therefore the NVMCTRL considers them as secure regions. The system may also have a secure callable boot and application regions. These regions have the same attributes as the secure sections, so there is no special treatment needed in NVMCTRL.

Any illegal access will result in a bus error. The BOOT and Application non-secure callable regions are shown for reference but have no effect on the NVMCTRL. These regions are included in secure regions therefore the NVMCTRL considers them as secure regions.

| Memory Region                           | Secure Access | Non-Secure Access | Limitations                  |

|-----------------------------------------|---------------|-------------------|------------------------------|

| FLASH Boot secure                       | R+W           | -                 |                              |

| FLASH Boot non-secure                   | R+W           | R+W               |                              |

| FLASH Application secure                | R+W           | -                 |                              |

| FLASH Application non-<br>secure        | R+W           | R+W               |                              |

| Data FLASH secure                       | R+W           | -                 |                              |

| Data FLASH non-secure                   | R+W           | R+W               |                              |

| AUX FLASH Calibration<br>Row            | R+W           | R                 |                              |

| AUX FLASH User Row<br>(UROW)            | R+W           | R                 |                              |

| AUX FLASH Boot<br>Configuration (BOCOR) | R+W           | -                 | No read if BCREN is cleared. |

Table 30-2.

Memory Regions AHB Access Limitations

The Boot Configuration row (BOCOR) contains information that is read by the boot ROM and written to IDAU and NVMCTRL registers. The BOCOR is read/writable if SCFGB.BCREN/BCWEN are set, respectively.

Important: SCFGB.BCREN/BCWEN are copied from BOCOR by the boot ROM.

## Table 30-3. Memory Regions Modify operations Limitations (WP, EP commands)

| Memory Region            | Secure<br>Access | Non-<br>Secure<br>Access | Limitations        |

|--------------------------|------------------|--------------------------|--------------------|

| FLASH Boot secure        | Y                | N                        | No if SULCK.BS=0   |

| FLASH Boot non-secure    | Y                | Y                        | No if NSULCK.BNS=0 |

| FLASH Application secure | Y                | N                        | No if SULCK.AS=0   |

#### 30.8.6 Interrupt Enable Set

| Name:     | INTENSET                               |

|-----------|----------------------------------------|

| Offset:   | 0x10                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Write-Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5         | 4         | 3         | 2         | 1         | 0         |  |

|--------|---|---|-----------|-----------|-----------|-----------|-----------|-----------|--|

|        |   |   | NSCHK     | KEYE      | NVME      | LOCKE     | PROGE     | DONE      |  |

| Access |   |   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |

| Reset  |   |   | 0         | 0         | 0         | 0         | 0         | 0         |  |

**Bit 5 – NSCHK** Non-secure Check Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit sets the NSCHK interrupt enable.

This bit will read as the current value of the NSCHK interrupt enable.

Bit 4 – KEYE Key Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit sets the KEYE interrupt enable.

This bit will read as the current value of the KEYE interrupt enable.

Bit 3 – NVME NVM internal Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit sets the NVME interrupt enable.

This bit will read as the current value of the NVME interrupt enable.

**Bit 2 – LOCKE** Lock Error Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit sets the LOCKE interrupt enable.

This bit will read as the current value of the LOCKE interrupt enable.

**Bit 1 – PROGE** Programming Error Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit sets the PROGE interrupt enable.

This bit will read as the current value of the PROGE interrupt enable.

#### 30.8.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG          |

|-----------|------------------|

| Offset:   | 0x14             |

| Reset:    | 0x00             |

| Property: | Write-Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

| Bit    | 7 | 6 | 5         | 4         | 3         | 2         | 1         | 0         |

|--------|---|---|-----------|-----------|-----------|-----------|-----------|-----------|

|        |   |   | NSCHK     | KEYE      | NVME      | LOCKE     | PROGE     | DONE      |

| Access |   |   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  |   |   | 0         | 0         | 0         | 0         | 0         | 0         |

## Bit 5 – NSCHK Non-Secure Check

This flag is set when the NONSEC register is changed and the new value differs from the NSCHK value.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | The NONSEC configuration has not changed since last clear.                          |

| 1     | At least one change has been made to the NONSEC configuration since the last clear. |

## Bit 4 – KEYE Key Error

This flag is set when a key write-protected register has been accessed in write with a bad key. A one indicates that at least one write access has been discarded.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | No key error occured since the last clear.           |

| 1     | At least one key error occured since the last clear. |

#### Bit 3 – NVME NVM internal Error

This flag is set on the occurrence of a NVM internal error.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | No NVM internal error has happened since this bit was last cleared.           |

| 1     | At least one NVM internal error has happened since this bit was last cleared. |

## Bit 2 – LOCKE Lock Error

This flag is set on the occurrence of a LOCKE error.

This bit can be cleared by writing a '1' to its bit location.

## 33.5 Functional Description

#### 33.5.1 Principle of Operation

The Event System consists of several channels which route the internal events from peripherals (generators) to other internal peripherals or I/O pins (users). Each event generator can be selected as source for multiple channels, but a channel cannot be set to use multiple event generators at the same time.

A channel path can be configured in asynchronous, synchronous or resynchronized mode of operation. The mode of operation must be selected based on the requirements of the application.

When using synchronous or resynchronized path, the Event System includes options to transfer events to users when rising, falling or both edges are detected on event generators.

For further details, refer to the Channel Path section of this chapter.

#### **Related Links**

33.5.2.6 Channel Path

#### 33.5.2 Basic Operation

#### 33.5.2.1 Initialization

Before enabling event routing within the system, the Event Users Multiplexer and Event Channels must be selected in the Event System (EVSYS), and the two peripherals that generate and use the event have to be configured. The recommended sequence is:

- 1. In the event generator peripheral, enable output of event by writing a '1' to the respective Event Output Enable bit ("EO") in the peripheral's Event Control register (e.g., TCC.EVCTRL.MCEO1, AC.EVCTRL.WINEO0, RTC.EVCTRL.OVFEO).

- 2. Configure the EVSYS:

- 2.1. Configure the Event User multiplexer by writing the respective EVSYS.USERm register, see also 33.5.2.3 User Multiplexer Setup.

- 2.2. Configure the Event Channel by writing the respective EVSYS.CHANNELn register, see also 33.5.2.4 Event System Channel.

- Configure the action to be executed by the event user peripheral by writing to the Event Action bits (EVACT) in the respective Event control register (e.g., TC.EVCTRL.EVACT, PDEC.EVCTRL.EVACT). Note: not all peripherals require this step.

- 4. In the event user peripheral, enable event input by writing a '1' to the respective Event Input Enable bit ("EI") in the peripheral's Event Control register (e.g., AC.EVCTRL.IVEI0, ADC.EVCTRL.STARTEI).

#### 33.5.2.2 Enabling, Disabling, and Resetting

The EVSYS is always enabled.

The EVSYS is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the EVSYS will be reset to their initial state and all ongoing events will be canceled.

Refer to CTRLA.SWRST register for details.

#### 33.5.2.3 User Multiplexer Setup

The user multiplexer defines the channel to be connected to which event user. Each user multiplexer is dedicated to one event user. A user multiplexer receives all event channels output and must be configured to select one of these channels, as shown in Block Diagram section. The channel is selected with the Channel bit group in the User register (USERm.CHANNEL).

#### 37.8.3 Interrupt Enable Clear

Name:INTENCLROffset:0x14Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7     | 6 | 5 | 4 | 3 | 2    | 1      | 0    |

|--------|-------|---|---|---|---|------|--------|------|

|        | ERROR |   |   |   |   | DRDY | AMATCH | PREC |

| Access | R/W   |   |   |   |   | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   |   |   | 0    | 0      | 0    |

## Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

## **Bit 2 – DRDY** Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Ready bit, which disables the Data Ready interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Data Ready interrupt is disabled. |

| 1     | The Data Ready interrupt is enabled.  |

## **Bit 1 – AMATCH** Address Match Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Address Match Interrupt Enable bit, which disables the Address Match interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Address Match interrupt is disabled. |

| 1     | The Address Match interrupt is enabled.  |

## Bit 0 – PREC Stop Received Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Stop Received Interrupt Enable bit, which disables the Stop Received interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

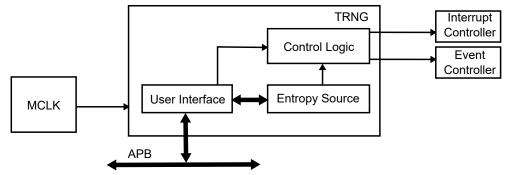

# 39. TRNG – True Random Number Generator

## 39.1 Overview

The True Random Number Generator (TRNG) generates unpredictable random numbers that are not generated by an algorithm. It passes the American NIST Special Publication 800-22 and Diehard Random Tests Suites.

The TRNG may be used as an entropy source for seeding an NIST approved DRNG (Deterministic RNG) as required by FIPS PUB 140-2 and 140-3.

## 39.2 Features

- Passed NIST Special Publication 800-22 Tests Suite

- Passed Diehard Random Tests Suite

- May be used as Entropy Source for seeding an NIST approved DRNG (Deterministic RNG) as required by FIPS PUB 140-2 and 140-3

- Provides a 32-bit random number every 84 clock cycles

## 39.3 Block Diagram

## Figure 39-1. TRNG Block Diagram.

## 39.4 Signal Description

Not applicable.

## **39.5 Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 39.5.1 I/O Lines

Not applicable.

## 39.5.2 Power Management

The functioning of TRNG depends on the sleep mode of device.

## 42.8.11 Scaler n

| Name:     | SCALER               |  |  |  |  |  |

|-----------|----------------------|--|--|--|--|--|

| Offset:   | 0x0C + n*0x01 [n=01] |  |  |  |  |  |

| Reset:    | 0x00                 |  |  |  |  |  |

| Property: | PAC Write-Protection |  |  |  |  |  |

| Bit    | 7 | 6 | 5          | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|---|---|------------|-----|-----|-----|-----|-----|--|--|

|        |   |   | VALUE[5:0] |     |     |     |     |     |  |  |

| Access |   |   | R/W        | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  |   |   | 0          | 0   | 0   | 0   | 0   | 0   |  |  |

## Bits 5:0 - VALUE[5:0] Scaler Value

These bits define the scaling factor for channel n of the  $V_{DD}$  voltage scaler. The output voltage,  $V_{SCALE}$ , is:

$V_{\text{SCALE}} = \frac{V_{\text{DD}} \cdot (\text{VALUE}+1)}{64}$

#### 32. PORT - I/O Pin Controller

#### 43.5.2 Power Management

The DAC will continue to operate in any Sleep mode where the selected source clock is running.

The DAC interrupts can be used to wake up the device from sleep modes.

Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

22. PM - Power Manager

#### 43.5.3 Clocks

The DAC bus clock (CLK\_DAC\_APB) can be enabled and disabled by the Main Clock module, and the default state of CLK\_DAC\_APB can be found in the *Peripheral Clock Masking* section.

A generic clock (GCLK\_DAC) is required to clock the DAC Controller. This clock must be configured and enabled in the Generic Clock Controller before using the DAC Controller. Refer to GCLK – Generic Clock Controller for details.

This generic clock is asynchronous to the bus clock (CLK\_DAC\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to 43.6.7 Synchronization for further details.

#### **Related Links**

18. GCLK - Generic Clock Controller

#### 43.5.4 DMA

The DMA request line is connected to the DMA Controller (DMAC). Using the DAC Controller DMA requests requires to configure the DMAC first.

#### **Related Links**

28. DMAC - Direct Memory Access Controller

## 43.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the DAC Controller interrupt(s) requires the interrupt controller to be configured first.

## 43.5.6 Events

The events are connected to the Event System.

#### **Related Links**

33. EVSYS – Event System

## 43.5.7 Debug Operation

When the CPU is halted in debug mode the DAC will halt normal operation. Any on-going conversions will be completed. The DAC can be forced to continue normal operation during debugging. If the DAC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

## 43.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

DAC – Digital-to-Analog Converter

| Value | Description                 |

|-------|-----------------------------|

| 0     | No ongoing synchronization. |

| 1     | Synchronization is ongoing. |

## Bit 0 – SWRST Software Reset

This bit is set when CTRLA.SWRST bit is written.

This bit is cleared when CTRLA.SWRST synchronization is completed.

| Value | Description                 |

|-------|-----------------------------|

| 0     | No ongoing synchronization. |

| 1     | Synchronization is ongoing. |

# SAM L10/L11 Family

# **Electrical Characteristics**

| Mode | Conditions | Regulator | PL  | CPU Clock            | Vcc  | Та | Тур. | Max | Units |

|------|------------|-----------|-----|----------------------|------|----|------|-----|-------|

|      |            |           |     |                      | 3.3V | :  | 35.3 | 39  |       |

|      |            |           |     | DFLLULP at<br>32MHz  | 1.8V |    | 55.3 | 68  |       |

|      |            |           |     |                      | 3.3V |    | 32.6 | 41  |       |

|      | WHILE1     | LDO       | PLO | DFLLULP at<br>8MHz   | 1.8V |    | 44.3 | 61  |       |

|      |            |           |     |                      | 3.3V |    | 44.4 | 62  |       |

|      |            |           |     | OSC 8MHz             | 1.8V |    | 47.6 | 60  |       |

|      |            |           |     |                      | 3.3V |    | 50.1 | 63  |       |

|      |            |           |     | OSC 4MHz             | 1.8V |    | 54.6 | 83  |       |

|      |            |           |     |                      | 3.3V |    | 57.7 | 86  |       |

|      |            |           | PL2 | FDPLL96M at          | 1.8V |    | 56.9 | 61  |       |

|      |            |           |     | 32MHz                | 3.3V |    | 57.2 | 62  |       |

|      |            |           |     | DFLLULP at           | 1.8V |    | 50.8 | 66  |       |

|      |            |           |     | 32MHz                | 3.3V |    | 51.0 | 64  |       |

|      |            | BUCK      | PL0 | DFLLULP at<br>8MHz   | 1.8V |    | 28.1 | 40  |       |

|      |            |           |     |                      | 3.3V |    | 18.5 | 27  |       |

|      |            |           |     | OSC 8MHz             | 1.8V |    | 32.2 | 41  |       |

|      |            |           |     |                      | 3.3V |    | 25.3 | 32  |       |

|      |            |           |     | OSC 4MHz             | 1.8V |    | 38.4 | 57  |       |

|      |            |           |     |                      | 3.3V |    | 31.9 | 45  |       |

|      |            |           | PL2 | FDPLL96M at<br>32MHz | 1.8V |    | 41.5 | 46  |       |

|      |            |           |     |                      | 3.3V |    | 24.6 | 28  |       |

|      |            |           |     | DFLLULP at<br>32MHz  | 1.8V |    | 37.1 | 47  |       |

|      |            |           |     |                      | 3.3V |    | 22.0 | 28  |       |

| IDLE |            | LDO       | PL0 | DFLLULP at<br>8MHz   | 1.8V |    | 16.0 | 32  |       |

|      |            |           |     |                      | 3.3V |    | 16.2 | 33  |       |

|      |            |           |     | OSC 8MHz             | 1.8V |    | 19.8 | 33  |       |

|      |            |           |     |                      | 3.3V |    | 22.0 | 36  |       |

|      |            |           |     | OSC 4MHz             | 1.8V |    | 26.2 | 55  |       |

|      |            |           |     |                      | 3.3V |    | 29.2 | 59  |       |

|      |            |           | PL2 | FDPLL96M at<br>32MHz | 1.8V |    | 20.3 | 25  |       |

|      |            |           |     |                      | 3.3V |    | 20.4 | 26  |       |