# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e14a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **DSU - Device Service Unit**

## Table 16-6. AMOD Bit Descriptions for MBIST

| AMOD[1:0] | Description    |

|-----------|----------------|

| 0x0       | Exit on Error  |

| 0x1       | Pause on Error |

| 0x2, 0x3  | Reserved       |

## **Related Links**

## 30. NVMCTRL – Nonvolatile Memory Controller

## 16.10.7 System Services Availability when Accessed Externally

External access: Access performed in the DSU address offset 0x100-0x1FFF range.

Internal access: Access performed in the DSU address offset 0x0-0xFF range.

# Table 16-7. Available Features when Operated From The External Address Range and Device is Protected

| Features                                  | Availability From The External Address Range when DAL<2 |

|-------------------------------------------|---------------------------------------------------------|

| CRC32                                     | No                                                      |

| CoreSight Compliant Device identification | Yes                                                     |

| Debug communication channels              | Yes                                                     |

| Boot communication channels               | Yes                                                     |

| Testing of onboard memories (MBIST)       | No                                                      |

## 18.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | SWRST |

| Access |   |   |   |   |   |   |   | R/W   |

| Reset  |   |   |   |   |   |   |   | 0     |

### Bit 0 - SWRST Software Reset

Writing a zero to this bit has no effect.

Setting this bit to 1 will reset all registers in the GCLK to their initial state after a Power Reset, except for generic clocks and associated Generators that have their WRTLOCK bit in PCHCTRLm set to 1.

Refer to GENCTRL Reset Value for details on GENCTRL register reset.

Refer to PCHCTRL Reset Value for details on PCHCTRL register reset.

Due to synchronization, there is a waiting period between setting CTRLA.SWRST and a completed Reset. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no Reset operation ongoing. |

| 1     | A Reset operation is ongoing.        |

## 19.5.7 Debug Operation

When the CPU is halted in debug mode, the MCLK continues normal operation. In sleep mode, the clocks generated from the MCLK are kept running to allow the debugger accessing any module. As a consequence, power measurements are incorrect in debug mode.

## 19.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

• Interrupt Flag register (INTFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

## **Related Links**

15. PAC - Peripheral Access Controller

## 19.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

### 19.5.10 Analog Connections

Not applicable.

## **19.6** Functional Description

## 19.6.1 Principle of Operation

The CLK\_MAIN clock signal from the GCLK module or the DFLLULP is the source for the main clock, which in turn is the common root for the synchronous clocks for the CPU, APBx, and AHBx modules. The CLK\_MAIN is divided by an 8-bit prescaler. Each of the derived clocks can run from any divided or undivided main clock, ensuring synchronous clock sources for each clock domain. The clock domain (CPU) can be changed on the fly to respond to variable load in the application. The clocks for each module in a clock domain can be masked individually to avoid power consumption in inactive modules. Depending on the sleep mode, some clock domains can be turned off.

## 19.6.2 Basic Operation

## 19.6.2.1 Initialization

After a Reset, the default clock source of the CLK\_MAIN clock (GCLK\_MAIN) is started and calibrated before the CPU starts running. The GCLK\_MAIN clock is selected as the main clock without any prescaler division.

By default, only the necessary clocks are enabled.

## 19.8.6 AHB Mask

| Name:     | AHBMASK              |

|-----------|----------------------|

| Offset:   | 0x10                 |

| Reset:    | 0x000001FFF          |

| Property: | PAC Write-Protection |

| Bit    | 31      | 30  | 29       | 28   | 27       | 26       | 25       | 24       |

|--------|---------|-----|----------|------|----------|----------|----------|----------|

|        |         |     |          |      |          |          |          |          |

| Access |         |     |          |      |          |          |          |          |

| Reset  |         |     |          |      |          |          |          |          |

|        |         |     |          |      |          |          |          |          |

| Bit    | 23      | 22  | 21       | 20   | 19       | 18       | 17       | 16       |

|        |         |     |          |      |          |          |          |          |

| Access |         | I   | I        | 1    |          |          | I        |          |

| Reset  |         |     |          |      |          |          |          |          |

|        |         |     |          |      |          |          |          |          |

| Bit    | 15      | 14  | 13       | 12   | 11       | 10       | 9        | 8        |

|        |         |     |          | TRAM | Reserved | Reserved | Reserved | Reserved |

| Access |         |     |          | R/W  | R/W      | R/W      | R/W      | R/W      |

| Reset  |         |     |          | 1    | 1        | 1        | 1        | 1        |

|        |         |     |          |      |          |          |          |          |

| Bit    | 7       | 6   | 5        | 4    | 3        | 2        | 1        | 0        |

| [      | NVMCTRL | PAC | Reserved | DSU  | DMAC     | APBC     | APBB     | APBA     |

| Access | R/W     | R/W | R/W      | R/W  | R/W      | R/W      | R/W      | R/W      |

| Reset  | 1       | 1   | 1        | 1    | 1        | 1        | 1        | 1        |

## Bit 12 – TRAM TRAM AHB Clock Enable

| I | Value | Description                           |

|---|-------|---------------------------------------|

|   | 0     | The AHB clock for the TRAM is stopped |

|   | 1     | The AHB clock for the TRAM is enabled |

## Bit 11 – Reserved Must Be Set to 1

Bit 11 must always be set to '1' when programming the AHBMASK register.

## Bit 10 - Reserved Must Be Set to 1

Bit 10 must always be set to '1' when programming the AHBMASK register.

## Bit 9 - Reserved Must Be Set to 1

Bit 9 must always be set to '1' when programming the AHBMASK register.

## Bit 8 – Reserved Must Be Set to 1

Bit 8 must always be set to '1' when programming the AHBMASK register.

## Bit 7 – NVMCTRL NVMCTRL AHB Clock Enable

20.8.9 Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | VALUE<br>0x10<br>0x00000000<br>- |    |       |         |    |    |    |

|--------|-----------------------------------------|----------------------------------|----|-------|---------|----|----|----|

| Bit    | 31                                      | 30                               | 29 | 28    | 27      | 26 | 25 | 24 |

|        |                                         |                                  |    |       |         |    |    |    |

| Access |                                         |                                  |    |       |         |    |    |    |

| Reset  |                                         |                                  |    |       |         |    |    |    |

| Bit    | 23                                      | 22                               | 21 | 20    | 19      | 18 | 17 | 16 |

|        |                                         |                                  |    | VALUE | [23:16] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

| Bit    | 15                                      | 14                               | 13 | 12    | 11      | 10 | 9  | 8  |

|        |                                         |                                  |    | VALUE | E[15:8] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 7                                       | 6                                | 5  | 4     | 3       | 2  | 1  | 0  |

|        |                                         |                                  |    |       | E[7:0]  |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

**Bits 23:0 – VALUE[23:0]** Measurement Value Result from measurement.

## 22.7 Register Summary

| Offset | Name     | Bit Pos. |        |         |         |         |             |         |

|--------|----------|----------|--------|---------|---------|---------|-------------|---------|

| 0x01   | SLEEPCFG | 7:0      |        |         |         | S       | LEEPMODE[2: | 0]      |

| 0x02   | PLCFG    | 7:0      | PLDIS  |         |         |         | PLSE        | L[1:0]  |

| 0x03   | PWCFG    | 7:0      |        |         |         |         | RAMPS       | WC[1:0] |

| 0x04   | INTENCLR | 7:0      |        |         |         |         |             | PLRDY   |

| 0x05   | INTENSET | 7:0      |        |         |         |         |             | PLRDY   |

| 0x06   | INTFLAG  | 7:0      |        |         |         |         |             | PLRDY   |

| 0x07   | Reserved |          |        |         |         |         |             |         |

| 0x08   | STDBYCFG | 7:0      | VREGSM | OD[1:0] | DPGPDSW |         |             | PDCFG   |

| 0,00   | STUBTURG | 15:8     |        |         | BBIASTR | BBIASHS |             |         |

## 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 22.5.7 Register Access Protection.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

**OSCCTRL – Oscillators Controller**

| Value | Description                       |

|-------|-----------------------------------|

| 0     | DPLL Lock rise edge not detected. |

| 1     | DPLL Lock rise edge detected.     |

## Bit 10 – DFLLULPNOLOCK DFLLULP No Lock

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | DFLLULP Tuner no lock state is not detected. |

| 1     | DFLLULP Tuner no lock state is detected.     |

## Bit 9 – DFLLULPLOCK DFLLULP Lock

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | DFLLULP Tuner lock state is not detected. |

| 1     | DFLLULP Tuner lock state is detected.     |

## Bit 8 – DFLLULPRDY DFLLULP Ready

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | DFLLULP is not ready.                                     |

| 1     | DFLLULP is stable and ready to be used as a clock source. |

## Bit 4 – OSC16MRDY OSC16M Ready

|   | /alue | Description                                              |

|---|-------|----------------------------------------------------------|

| ( | )     | OSC16M is not ready.                                     |

| - | -     | OSC16M is stable and ready to be used as a clock source. |

## Bit 2 – CLKSW XOSC Clock Switch

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | XOSC is not switched and provides the external clock or crystal oscillator clock. |

| 1     | XOSC is switched and provides the safe clock.                                     |

## Bit 1 – CLKFAIL XOSC Clock Failure

| Value | Description                  |

|-------|------------------------------|

| 0     | No XOSC failure detected.    |

| 1     | A XOSC failure was detected. |

## Bit 0 – XOSCRDY XOSC Ready

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | XOSC is not ready.                                     |

| 1     | XOSC is stable and ready to be used as a clock source. |

## 24.7 Register Summary

| Offset | Name      | Bit Pos. |          |          |          |          |       |            |              |                |

|--------|-----------|----------|----------|----------|----------|----------|-------|------------|--------------|----------------|

|        |           | 7:0      |          |          |          |          |       | CLKFAIL    |              | XOSC32KRD<br>Y |

| 0x00   | INTENCLR  | 15:8     |          |          |          |          |       |            |              |                |

|        |           | 23:16    |          |          |          |          |       |            |              |                |

|        |           | 31:24    |          |          |          |          |       |            |              |                |

|        |           | 7:0      |          |          |          |          |       | CLKFAIL    |              | XOSC32KRD<br>Y |

| 0x04   | INTENSET  | 15:8     |          |          |          |          |       |            |              |                |

|        |           | 23:16    |          |          |          |          |       |            |              |                |

|        |           | 31:24    |          |          |          |          |       |            |              |                |

|        |           | 7:0      |          |          |          |          |       | CLKFAIL    |              | XOSC32KRD<br>Y |

| 0x08   | INTFLAG   | 15:8     |          |          |          |          |       |            |              |                |

|        |           | 23:16    |          |          |          |          |       |            |              |                |

|        |           | 31:24    |          |          |          |          |       |            |              |                |

|        |           | 7:0      |          |          |          | ULP32KSW | CLKSW | CLKFAIL    |              | XOSC32KRD<br>Y |

| 0x0C   | STATUS    | 15:8     |          |          |          |          |       |            |              |                |

|        |           | 23:16    |          |          |          |          |       |            |              |                |

|        |           | 31:24    |          |          |          |          |       |            |              |                |

| 0x10   | RTCCTRL   | 7:0      |          |          |          |          |       |            | RTCSEL[2:0]  |                |

| 0x11   |           |          |          |          |          |          |       |            |              |                |

|        | Reserved  |          |          |          |          |          |       |            |              |                |

| 0x13   |           |          |          |          |          |          |       |            |              |                |

|        |           | 7:0      | ONDEMAND | RUNSTDBY |          | EN1K     | EN32K | XTALEN     | ENABLE       |                |

| 0x14   | XOSC32K   | 15:8     |          |          |          | WRTLOCK  |       |            | STARTUP[2:0] | ]              |

| 0x16   | CFDCTRL   | 7:0      |          |          |          |          |       | CFDPRESC   | SWBACK       | CFDEN          |

| 0x17   | EVCTRL    | 7:0      |          |          |          |          |       |            |              | CFDEO          |

| 0x18   |           |          |          |          |          |          |       |            |              |                |

|        | Reserved  |          |          |          |          |          |       |            |              |                |

| 0x1B   |           |          |          |          |          |          |       |            |              |                |

|        |           | 7:0      |          |          | ULP32KSW |          |       |            |              |                |

| 0.40   |           | 15:8     | WRTLOCK  |          |          |          |       | CALIB[4:0] |              |                |

| 0x1C   | OSCULP32K | 23:16    |          |          |          |          |       |            |              |                |

|        |           | 31:24    |          |          |          |          |       |            |              |                |

## 24.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register and the 8-bit halves of a 16-bit register can be accessed directly.

All registers with write-access can be write-protected optionally by the peripheral access controller (PAC). Optional Write-Protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-

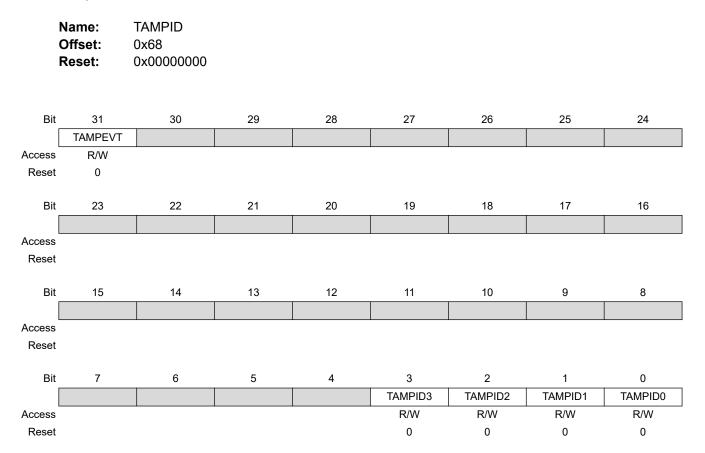

## 27.10.16 Tamper ID

### Bit 31 – TAMPEVT Tamper Event Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | A tamper input event has not been detected |

| 1     | A tamper input event has been detected     |

## Bits 0, 1, 2, 3 - TAMPID Tamper on Channel n Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | A tamper condition has not been detected on Channel n |

| 1     | A tamper condition has been detected on Channel n     |

## PORT - I/O Pin Controller

| , , , , , , , , , , , , , , , , , , , |          |        |        |                       |

|---------------------------------------|----------|--------|--------|-----------------------|

| EVACT0                                | EVACT1   | EVACT2 | EVACT3 | Executed Event Action |

| SET                                   | SET      | SET    | SET    | SET                   |

| CLR                                   | CLR      | CLR    | CLR    | CLR                   |

| All Other Comb                        | inations |        |        | TGL                   |

Table 32-3. Priority on Simultaneous SET/CLR/TGL Event Actions

Be careful when the event is output to pin. Due to the fact the events are received asynchronously, the I/O pin may have unpredictable levels, depending on the timing of when the events are received. When several events are output to the same pin, the lowest event line will get the access. All other events will be ignored.

## **Related Links**

33. EVSYS - Event System

## 32.6.6 PORT Access Priority

The PORT is accessed by different systems:

- The ARM<sup>®</sup> CPU through the ARM<sup>®</sup> single-cycle I/O port (IOBUS)

- The ARM<sup>®</sup> CPU through the high-speed matrix and the AHB/APB bridge (APB)

- EVSYS through four asynchronous input events

The following priority is adopted:

- 1. ARM<sup>®</sup> CPU IOBUS (No wait tolerated)

- 2. APB

- 3. EVSYS input events

For input events that require different actions on the same I/O pin, refer to 32.6.5 Events.

## 32.8.11 Write Configuration

| Name:     | WRCONFIG                         |

|-----------|----------------------------------|

| Offset:   | 0x28                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

This write-only register is used to configure several pins simultaneously with the same configuration and/or peripheral multiplexing.

In order to avoid side effect of non-atomic access, 8-bit or 16-bit writes to this register will have no effect. Reading this register always returns zero.

| Bit    | 31     | 30            | 29     | 28           | 27       | 26        | 25     | 24     |

|--------|--------|---------------|--------|--------------|----------|-----------|--------|--------|

|        | HWSEL  | WRPINCFG      |        | WRPMUX       |          | PMUX[3:0] |        |        |

| Access | W/W*/W | W/W*/W        | •      | W/W*/W       | W/W*/W   | W/W*/W    | W/W*/W | W/W*/W |

| Reset  | 0      | 0             |        | 0            | 0        | 0         | 0      | 0      |

|        |        |               |        |              |          |           |        |        |

| Bit    | 23     | 22            | 21     | 20           | 19       | 18        | 17     | 16     |

|        |        | DRVSTR        |        |              |          | PULLEN    | INEN   | PMUXEN |

| Access |        | W/W*/W        |        |              |          | W/W*/W    | W/W*/W | W/W*/W |

| Reset  |        | 0             |        |              |          | 0         | 0      | 0      |

|        |        |               |        |              |          |           |        |        |

| Bit    | 15     | 14            | 13     | 12           | 11       | 10        | 9      | 8      |

|        |        | PINMASK[15:8] |        |              | SK[15:8] |           |        |        |

| Access | W/W*/W | W/W*/W        | W/W*/W | W/W*/W       | W/W*/W   | W/W*/W    | W/W*/W | W/W*/W |

| Reset  | 0      | 0             | 0      | 0            | 0        | 0         | 0      | 0      |

|        |        |               |        |              |          |           |        |        |

| Bit    | 7      | 6             | 5      | 4            | 3        | 2         | 1      | 0      |

|        |        |               |        | PINMASK[7:0] |          |           |        |        |

| Access | W/W*/W | W/W*/W        | W/W*/W | W/W*/W       | W/W*/W   | W/W*/W    | W/W*/W | W/W*/W |

| Reset  | 0      | 0             | 0      | 0            | 0        | 0         | 0      | 0      |

## Bit 31 – HWSEL Half-Word Select

This bit selects the half-word field of a 32-PORT group to be reconfigured in the atomic write operation.

## EVSYS – Event System

| Value     | Event Generator | Description           |

|-----------|-----------------|-----------------------|

| 0x19-0x1C | DMAC_CH         | DMAC channel          |

| 0x1D      | TC0_OVF         | TC0 overflow          |

| 0x1E-0x1F | TC0_MCX         | TC0 match/compare     |

| 0x20      | TC1_OVF         | TC1 overflow          |

| 0x21-0x22 | TC1_MCX         | TC1 match/compare     |

| 0x23      | TC2_OVF         | TC2 overflow          |

| 0x24-0x25 | TC2_MCX         | TC2 match/compare     |

| 0x26      | ADC_RESRDY      | ADC resolution ready  |

| 0x27      | ADC_WINMON      | ADC window monitor    |

| 0x28-0x29 | AC_COMP         | AC comparator         |

| 0x2A      | AC_WIN          | AC window             |

| 0x2B      | DAC_EMPTY       | DAC empty             |

| 0x2C      | PTC_EOC         | PTC end of conversion |

| 0x2D      | PTC_WCOMP       | PTC window comparator |

| 0x2E      | TRNG_READY      | Data ready            |

| 0x2F-0x30 | CCL_LUTOUT      | CCL output            |

| 0x31      | PAC_ERR         | PAC access error      |

## 35.8.2 Control B

| Name:     | CTRLB                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x04                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Enable-Protected, Write-Synchronized |

| Bit    | 31 | 30     | 29    | 28 | 27 | 26  | 25          | 24     |

|--------|----|--------|-------|----|----|-----|-------------|--------|

|        |    |        |       |    |    |     |             |        |

| Access |    |        |       |    |    |     |             |        |

| Reset  |    |        |       |    |    |     |             |        |

|        |    |        |       |    |    |     |             |        |

| Bit    | 23 | 22     | 21    | 20 | 19 | 18  | 17          | 16     |

|        |    |        |       |    |    |     | RXEN        | TXEN   |

| Access |    |        |       |    |    |     | R/W         | R/W    |

| Reset  |    |        |       |    |    |     | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 15 | 14     | 13    | 12 | 11 | 10  | 9           | 8      |

|        |    |        | PMODE |    |    | ENC | SFDE        | COLDEN |

| Access |    |        | R/W   |    |    | R/W | R/W         | R/W    |

| Reset  |    |        | 0     |    |    | 0   | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 7  | 6      | 5     | 4  | 3  | 2   | 1           | 0      |

|        |    | SBMODE |       |    |    |     | CHSIZE[2:0] |        |

| Access | -  | R/W    | ·     |    |    | R/W | R/W         | R/W    |

| Reset  |    | 0      |       |    |    | 0   | 0           | 0      |

## Bit 17 - RXEN Receiver Enable

Writing '0' to this bit will disable the USART receiver. Disabling the receiver will flush the receive buffer and clear the FERR, PERR and BUFOVF bits in the STATUS register.

Writing '1' to CTRLB.RXEN when the USART is disabled will set CTRLB.RXEN immediately. When the USART is enabled, CTRLB.RXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled, CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the USART is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                            |

| 1     | The receiver is enabled or will be enabled when the USART is enabled. |

## Bit 16 – TXEN Transmitter Enable

Writing '0' to this bit will disable the USART transmitter. Disabling the transmitter will not become effective until ongoing and pending transmissions are completed.

Writing '1' to CTRLB.TXEN when the USART is disabled will set CTRLB.TXEN immediately. When the USART is enabled, CTRLB.TXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the transmitter is enabled. When the transmitter is enabled, CTRLB.TXEN will read back as '1'.

© 2018 Microchip Technology Inc.

## 35.8.11 Receive Error Count

| Name:     | RXERRCNT          |

|-----------|-------------------|

| Offset:   | 0x20              |

| Reset:    | 0x00              |

| Property: | Read-Synchronized |

| Bit    | 7 | 6 | 5 | 4     | 3        | 2 | 1 | 0 |

|--------|---|---|---|-------|----------|---|---|---|

|        |   |   |   | RXERR | CNT[7:0] |   |   |   |

| Access | R | R | R | R     | R        | R | R | R |

| Reset  | 0 | 0 | 0 | 0     | 0        | 0 | 0 | 0 |

## Bits 7:0 - RXERRCNT[7:0] Receive Error Count

This register records the total number of parity errors and NACK errors combined in ISO7816 mode (CTRLA.FORM=0x7).

This register is automatically cleared on read.

TC – Timer/Counter

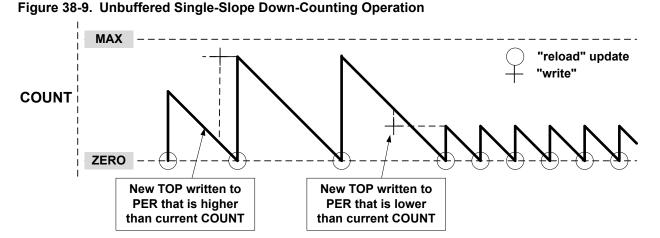

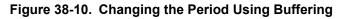

When double buffering is used, the buffer can be written at any time and the counter will still maintain correct operation. The period register is always updated on the update condition, as shown in Figure 38-10. This prevents wraparound and the generation of odd waveforms.

## 38.6.2.8 Capture Operations

To enable and use capture operations, the corresponding Capture Channel x Enable bit in the Control A register (CTRLA.CAPTENx) must be written to '1'.

A capture trigger can be provided by input event line TC\_EV or by asynchronous IO pin WO[x] for each capture channel or by a TC event. To enable the capture from input event line, Event Input Enable bit in the Event Control register (EVCTRL.TCEI) must be written to '1'. To enable the capture from the IO pin, the Capture On Pin x Enable bit in CTRLA register (CTRLA.COPENx) must be written to '1'.

## Note:

- 1. The RETRIGGER, COUNT and START event actions are available only on an event from the Event System.

- 2. Event system channels must be configured to operate in asynchronous mode of operation when used for capture operations.

By default, a capture operation is done when a rising edge is detected on the input signal. Capture on falling edge is available, its activation is depending on the input source:

• When the channel is used with a IO pin, write a '1' to the corresponding Invert Enable bit in the Drive Control register (DRVCTRL.INVENx).

## 38.7.1.3 Control B Set

Name:CTRLBSETOffset:0x05Reset:0x00Property:PAC Write-Protection, Read-synchronized, Write-Synchronized

This register allows the user to set bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Clear register (CTRLBCLR).

| Bit    | 7   | 6        | 5   | 4 | 3 | 2       | 1    | 0   |

|--------|-----|----------|-----|---|---|---------|------|-----|

|        |     | CMD[2:0] |     |   |   | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W |   |   | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   |   |   | 0       | 0    | 0   |

## Bits 7:5 – CMD[2:0] Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a value different from 0x0 to these bits will issue a command for execution.

| Value | Name      | Description                               |

|-------|-----------|-------------------------------------------|

| 0x0   | NONE      | No action                                 |

| 0x1   | RETRIGGER | Force a start, restart or retrigger       |

| 0x2   | STOP      | Force a stop                              |

| 0x3   | UPDATE    | Force update of double buffered registers |

| 0x4   | READSYNC  | Force a read synchronization of COUNT     |

## Bit 2 - ONESHOT One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will enable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

## Bit 1 – LUPD Lock Update

This bit controls the update operation of the TC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the LUPD bit.

## 38.7.1.8 Status

| Name:     | STATUS            |

|-----------|-------------------|

| Offset:   | 0x0B              |

| Reset:    | 0x01              |

| Property: | Read-Synchronized |

| Bit    | 7 | 6 | 5 | 4       | 3       | 2 | 1     | 0    |

|--------|---|---|---|---------|---------|---|-------|------|

| ĺ      |   |   |   | CCBUFVx | PERBUFV |   | SLAVE | STOP |

| Access |   |   |   | R/W     | R/W     |   | R     | R    |

| Reset  |   |   |   | 0       | 0       |   | 0     | 1    |

### Bit 4 – CCBUFVx Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

## Bit 3 – PERBUFV Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. The bit is cleared by writing '1' to the corresponding location when CTRLB.LUPD is set, or automatically cleared by hardware on UPDATE condition. This bit is available only in 8-bit mode and will always read zero in 16- and 32-bit modes.

## Bit 1 – SLAVE Slave Status Flag

This bit is only available in 32-bit mode on the slave TC (i.e., TC1 and/or TC3). The bit is set when the associated master TC (TC0 and TC2, respectively) is set to run in 32-bit mode.

### Bit 0 – STOP Stop Status Flag

This bit is set when the TC is disabled, on a Stop command, or on an overflow/underflow condition when the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT) is '1'.

| Value | Description         |

|-------|---------------------|

| 0     | Counter is running. |

| 1     | Counter is stopped. |

## 41.8.12 Sampling Time Control

| Name:     | SAMPCTRL                                 |

|-----------|------------------------------------------|

| Offset:   | 0x0D                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7       | 6 | 5   | 4   | 3     | 2       | 1   | 0   |

|--------|---------|---|-----|-----|-------|---------|-----|-----|

|        | OFFCOMP |   |     |     | SAMPL | EN[5:0] |     |     |

| Access | R/W     |   | R/W | R/W | R/W   | R/W     | R/W | R/W |

| Reset  | 0       |   | 0   | 0   | 0     | 0       | 0   | 0   |

## Bit 7 – OFFCOMP Comparator Offset Compensation Enable

Setting this bit enables the offset compensation for each sampling period to ensure low offset and immunity to temperature or voltage drift. This compensation increases the sampling time by three clock cycles.

This bit must be set to zero to validate the SAMPLEN value. It's not possible to use OFFCOMP=1 and SAMPLEN>0.

## Bits 5:0 - SAMPLEN[5:0] Sampling Time Length

These bits control the ADC sampling time in number of CLK\_ADC cycles, depending of the prescaler value, thus controlling the ADC input impedance. Sampling time is set according to the equation:

Sampling time =  $(SAMPLEN+1) \cdot (CLK_{ADC})$

## 41.8.19 Synchronization Busy

| Name:     | SYNCBUSY |

|-----------|----------|

| Offset:   | 0x20     |

| Reset:    | 0x0000   |

| Property: | -        |

| Bit    | 15    | 14    | 13       | 12      | 11    | 10        | 9          | 8        |

|--------|-------|-------|----------|---------|-------|-----------|------------|----------|

|        |       |       |          |         |       | SWTRIG    | OFFSETCORR | GAINCORR |

| Access |       |       |          |         |       | R         | R          | R        |

| Reset  |       |       |          |         |       | 0         | 0          | 0        |

|        |       |       |          |         |       |           |            |          |

| Bit    | 7     | 6     | 5        | 4       | 3     | 2         | 1          | 0        |

|        | WINUT | WINLT | SAMPCTRL | AVGCTRL | CTRLC | INPUTCTRL | ENABLE     | SWRST    |

| Access | R     | R     | R        | R       | R     | R         | R          | R        |

| Reset  | 0     | 0     | 0        | 0       | 0     | 0         | 0          | 0        |

## Bit 10 – SWTRIG Software Trigger Synchronization Busy

This bit is cleared when the synchronization of SWTRIG register between the clock domains is complete.

This bit is set when the synchronization of SWTRIG register between clock domains is started.

### Bit 9 - OFFSETCORR Offset Correction Synchronization Busy

This bit is cleared when the synchronization of OFFSETCORR register between the clock domains is complete.

This bit is set when the synchronization of OFFSETCORR register between clock domains is started.

### **Bit 8 – GAINCORR** Gain Correction Synchronization Busy

This bit is cleared when the synchronization of GAINCORR register between the clock domains is complete.

This bit is set when the synchronization of GAINCORR register between clock domains is started.

**Bit 7 – WINUT** Window Monitor Lower Threshold Synchronization Busy This bit is cleared when the synchronization of WINUT register between the clock domains is complete.

This bit is set when the synchronization of WINUT register between clock domains is started.

### Bit 6 - WINLT Window Monitor Upper Threshold Synchronization Busy

This bit is cleared when the synchronization of WINLT register between the clock domains is complete.

This bit is set when the synchronization of WINLT register between clock domains is started.

## **Bit 5 – SAMPCTRL** Sampling Time Control Synchronization Busy

This bit is cleared when the synchronization of SAMPCTRL register between the clock domains is complete.

This bit is set when the synchronization of SAMPCTRL register between clock domains is started.

## **Electrical Characteristics**

| Symbol                                | Parameter    | Conditions               | Min. | Тур. | Max. | Units |

|---------------------------------------|--------------|--------------------------|------|------|------|-------|

|                                       |              | F <sub>OUT</sub> = 12MHz | -    | 0.13 | 0.28 |       |

|                                       |              | F <sub>OUT</sub> = 16MHz | -    | 0.13 | 0.27 |       |

| T <sub>STARTUP</sub> <sup>(2)</sup> S | Startup time | F <sub>OUT</sub> = 4MHz  | -    | 1.16 | 2.96 | μs    |

|                                       |              | F <sub>OUT</sub> = 8MHz  | -    | 1.29 | 2.74 |       |

|                                       |              | F <sub>OUT</sub> = 12MHz | -    | 1.34 | 2.95 |       |

|                                       |              | F <sub>OUT</sub> = 16MHz | -    | 1.39 | 3.11 |       |

| Duty <sup>(1)</sup>                   | Duty Cycle   | -                        | 45   | 50   | 55   | %     |

## Note:

- 1. These values are based on simulation. They are not covered by production test limits or characterization.

- 2. These are based on characterization.

## Table 46-51. Power Consumption

| Symbol                                 | Parameter                                         | Conditions                                       | Та                   | Min. | Тур. | Max. | Units |

|----------------------------------------|---------------------------------------------------|--------------------------------------------------|----------------------|------|------|------|-------|

| I <sub>DD</sub> Current<br>consumption | Current consumption                               | F <sub>out</sub> =4MHz,<br>V <sub>CC</sub> =3.3V | Max.85°C<br>Typ.25°C | -    | 73   | 139  | μA    |

|                                        |                                                   | F <sub>out</sub> =8MHz,<br>V <sub>CC</sub> =3.3V |                      | -    | 106  | 169  |       |

|                                        | F <sub>out</sub> =12MHz,<br>V <sub>CC</sub> =3.3V |                                                  | -                    | 135  | 195  |      |       |

|                                        | F <sub>out</sub> =16MHz,<br>V <sub>CC</sub> =3.3V |                                                  | -                    | 166  | 225  |      |       |

## 46.13.5 Digital Frequency Locked Loop (DFLLULP) Characteristics Table 46-52. Digital Frequency Locked Loop Characteristics<sup>(2)</sup>

| Symbol | Parameter                                                                 |                                                                                                          | Min  | Тур | Max | Unit |

|--------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| FIN    | Input Clock Frequency                                                     |                                                                                                          | 32   | -   | 33  | kHz  |

| FOUT   | Output Clock Frequency                                                    | PL2                                                                                                      | -    | 32  | -   | MHz  |

|        |                                                                           | PL0                                                                                                      | -    | 8   | -   |      |

| Jp     | Period jitter                                                             | PL0, Fin= 32 kHz 50 ppm, Fout = 8MHz                                                                     | -4   | -   | 4   | %    |

|        |                                                                           | PL2, Fin= 32 kHz 50 ppm, Fout = 32 MHz                                                                   | -4.3 | -   | 4.3 |      |

| tLOCK  | Lock Time                                                                 | After startup, time to get lock signal Fin =<br>32768 Hz, Fout = 8MHz, PL0<br>Binary Search mode enabled | -    | 362 | -   | μs   |

|        | After startup, time to get lock signal Fin = 32768 Hz, Fout = 32 MHz, PL2 | -                                                                                                        | 362  | -   | μs  |      |