Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e15a-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 46.1.                                                                                                                                                                | Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 46.2.                                                                                                                                                                | Thermal Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1125     |

| 46.3.                                                                                                                                                                | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 46.4.                                                                                                                                                                | General Operating Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 46.5.                                                                                                                                                                | Supply Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1127     |

| 46.6.                                                                                                                                                                | Maximum Clock Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1127     |

| 46.7.                                                                                                                                                                | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1129     |

| 46.8.                                                                                                                                                                | Wake-Up Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 46.9.                                                                                                                                                                | I/O Pin Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1134     |

| 46.10                                                                                                                                                                | ). Injection Current                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1135     |

| 46.1                                                                                                                                                                 | . Analog Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1136     |

| 46.12                                                                                                                                                                | 2. NVM Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1152     |

| 46.13                                                                                                                                                                | 3. Oscillators Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1153     |

| 46.14                                                                                                                                                                | I. Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 47. 125                                                                                                                                                              | C Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1166     |

| 47 1                                                                                                                                                                 | Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1166     |

|                                                                                                                                                                      | General Operating Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|                                                                                                                                                                      | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|                                                                                                                                                                      | Analog Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|                                                                                                                                                                      | Oscillators Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                                                                                                                                                                      | Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 48. AC                                                                                                                                                               | and DC Characteristics Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1192     |

|                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 85°C                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|                                                                                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 85°C<br>Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                         |          |

| 48.2.                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1194     |

| 48.2.<br>49. Pac                                                                                                                                                     | Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 48.2.<br><b>49. Pac</b><br>49.1.                                                                                                                                     | Typical Power Consumption over Temperature in Sleep Modes - 125°C                                                                                                                                                                                                                                                                                                                                                                                                             | 1194<br> |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.                                                                                                                                   | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information                                                                                                                                                                                                                                                                                                                                                        | 1194<br> |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.                                                                                                                          | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings                                                                                                                                                                                                                                                                                                                                    |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch                                                                                                               | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile.                                                                                                                                                                                                                                                                                                              |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.                                                                                                      | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction                                                                                                                                                                                                                                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.                                                                                             | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile                                                                                                                                                                                                                                                                                                               |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.                                                                                    | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply                                                                                                                                                                                                                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.                                                                           | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections                                                                                                                                                                                                                  |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.                                                                  | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit.                                                                                                                                                                                       |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.                                                         | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins                                                                                                                                                          |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.                                                | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings.<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators                                                                                                                       |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.                                       | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports                                                                                         |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con                            | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations                                                           |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.                   | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation                         |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.<br>51.2.          | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation<br>Memory Size and Type |          |

| 48.2.<br>49. Pac<br>49.1.<br>49.2.<br>49.3.<br>50. Sch<br>50.1.<br>50.2.<br>50.3.<br>50.4.<br>50.5.<br>50.6.<br>50.7.<br>50.8.<br>51. Con<br>51.1.<br>51.2.<br>51.2. | Typical Power Consumption over Temperature in Sleep Modes - 125°C<br>kaging Information<br>Package Marking Information<br>Package Drawings<br>Soldering Profile<br>ematic Checklist<br>Introduction<br>Power Supply<br>External Analog Reference Connections<br>External Reset Circuit<br>Unused or Unconnected Pins<br>Clocks and Crystal Oscillators<br>Programming and Debug Ports<br>Peripherals Considerations<br>Ventions<br>Numerical Notation                         |          |

## **Processor and Architecture**

#### Table 11-3. Interrupt Line Mapping

| Module                                   | Source               | NVIC line |

|------------------------------------------|----------------------|-----------|

| EIC NMI – External Interrupt Controller  | NMI                  | NMI       |

| PM – Power Manager                       | PLRDY                | 0         |

| /ICLK - Main Clock                       | CKRDY                |           |

| DSCCTRL - Oscillators Controller         | XOSCRDY              |           |

|                                          | XOSCFAIL             |           |

|                                          | OSC16MRDY            |           |

|                                          | DFLLULPRDY           |           |

|                                          | DFLLULPLOCK          |           |

|                                          | DFLLULPNOLOCK        |           |

|                                          | DPLLLCKR             |           |

|                                          | DPLLLCKF             |           |

|                                          | DPLLLTO              |           |

|                                          | DPLLLDRTO            |           |

| SC32KCTRL - 32KHz Oscillators Controller | XOSC32KRDY           |           |

|                                          | CLKFAIL              |           |

| UPC - Supply Controller                  | BOD33RDY             |           |

|                                          | BOD33DET             |           |

|                                          | B33SRDY              |           |

|                                          | VREGRDY              |           |

|                                          | VCORERDY             |           |

|                                          | ULPVREFRDY           |           |

| VDT – Watchdog Timer                     | EW                   | 1         |

| RTC – Real Time Counter                  | СМР0                 | 2         |

|                                          | CMP1                 |           |

|                                          | OVF                  |           |

|                                          | PER0                 |           |

|                                          | PER1                 |           |

|                                          | PER2                 |           |

|                                          | PER3                 |           |

|                                          | PER4                 |           |

|                                          | PER5                 |           |

|                                          | PER6                 |           |

|                                          | PER7                 |           |

|                                          | TAMPER               |           |

| EIC – External Interrupt Controller      | EXTINT 0             | 3         |

|                                          | EXTINT 1             | 4         |

|                                          | EXTINT 2             | 5         |

|                                          | EXTINT 3             | 6         |

|                                          | EXTINT 47            | 7         |

|                                          | NSCHK <sup>(1)</sup> |           |

| REQM - Frequency Meter                   | DONE                 | 8         |

| IVMCTRL – Non-Volatile Memory Controller | DONE                 | 9         |

|                                          | PROGE                |           |

**Important:** Chip Erase commands are only issued using the Boot ROM Interactive mode (CMD\_CE0, CMD\_CE1, CMD\_CE2 and CMD\_CHIPERASE commands).

For SAM L10, the chip erase command does not require a key.

For SAM L11, the chip erase commands are protected with keys (CEKEYx) defined in the NVM BOCOR row.

**Note:** The chip erase keys can only be read if BOCOR.BCREN=1.

By default, the devices are delivered with these keys set at "All 1s".

**Important:** If the key is set at "All 0s", the corresponding chip erase command is disabled and it will be impossible for the debugger to use it.

The following table gives the effect of the Chip Erase commands on the different memories: **Table 14-6. Chip Erase Commands Effects**

|                                           |                         | SAM L10                          |                        |                       |

|-------------------------------------------|-------------------------|----------------------------------|------------------------|-----------------------|

| Boot ROM Command                          | ChipErase_NS<br>(CE0)   | ChipErase_S<br>(CE1)             | ChipErase_ALL<br>(CE2) | ChipErase (CHIPERASE) |

| Key Requirement                           | Yes<br>(CEKEY0)         | Yes<br>(CEKEY1)                  | Yes<br>(CEKEY2)        | No                    |

| Flash BOOT area<br>BOOTPROT (BS+BNSC+BNS) | No                      | No                               | Yes                    | No                    |

| Flash Secure APPLICATION (AS)             | No                      | Yes                              | Yes                    | Yes                   |

| Flash Non-secure APPLICATION              | Yes                     | Yes                              | Yes                    | -                     |

| Secure Data Flash (DS)                    | No                      | Yes                              | Yes                    | Yes                   |

| Non-Secure Data Flash                     | Yes                     | Yes                              | Yes                    | -                     |

| NVM User Row (UROW)                       | No                      | No                               | Yes                    | No                    |

| NVM Boot Configuration Row (BOCOR)        | No                      | No                               | Yes                    | No                    |

| Volatile Memories                         | Yes                     | Yes                              | Yes                    | Yes                   |

| Debugger Access Level after reset         | 2 (if DAL was 2) else 1 | 2 (if DAL was 2 or BS==0) else 1 | 2                      | 2                     |

**Note:** Only the ChipErase\_ALL (CE2) command affects rows belonging to the BOOT area (BOOTPROT fuse bits)

#### 14.4.5 Boot ROM Interactive Mode

The interactive mode allows the user to perform several actions on the device during the Boot ROM execution via a debugger connection.

The debugger communicates with the device using the DSU Boot Communication Channels (BCC). This communication is bi-directional and allows the debugger to post commands and receive status from the Boot ROM.

**Note:** Refer to Device Service Unit for more information on BCC.

# 15. PAC - Peripheral Access Controller

#### 15.1 Overview

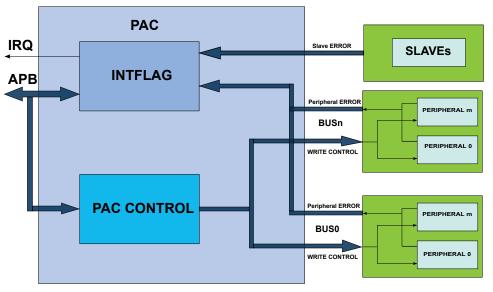

The Peripheral Access Controller provides an interface for the locking and unlocking and for managing security attribution of peripheral registers within the device. It reports all violations that could happen when accessing a peripheral: write protected access, illegal access, enable protected access, access when clock synchronization or software reset is on-going. These errors are reported in a unique interrupt flag for a peripheral. The PAC module also reports errors occurring at the slave bus level, when an access to a non-existing address is detected.

#### 15.2 Features

- Manages write protection access and reports access errors for the peripheral modules or bridges.

- Manages security attribution for the peripheral modules (SAM L11)

#### 15.3 Block Diagram

#### Figure 15-1. PAC Block Diagram

#### **15.4 Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 15.4.1 IO Lines

Not applicable.

#### 15.4.2 Power Management

The PAC can continue to operate in any Sleep mode where the selected source clock is running. The PAC interrupts can be used to wake up the device from Sleep modes. The events can trigger other operations in the system without exiting sleep modes.

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

### **OSCCTRL – Oscillators Controller**

#### Table 23-4. CLK\_DPLL Behavior after First Edge Detection

| LBYPASS | CLK_DPLL Behavior                                                     |

|---------|-----------------------------------------------------------------------|

| 0       | Normal Mode: the CLK_DPLL is turned off when lock signal is low.      |

| 1       | Lock Bypass Mode: the CLK_DPLL is always running, lock is irrelevant. |

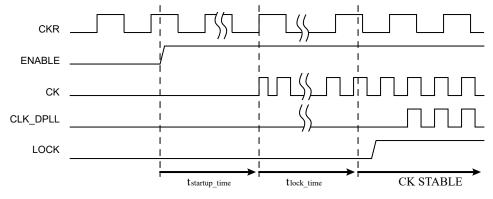

#### Figure 23-5. CK and CLK\_DPLL Output from DPLL Off Mode to Running Mode

#### 23.6.7.1.2 Reference Clock Switching

When a software operation requires reference clock switching, the recommended procedure is to turn the DPLL into the standby mode, modify the DPLLCTRLB.REFCLK to select the desired reference source, and activate the DPLL again.

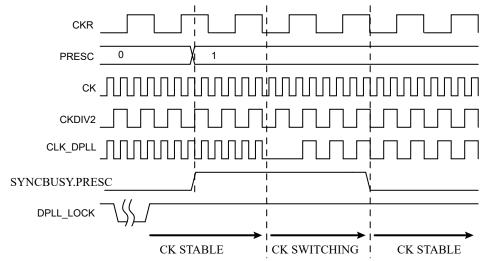

#### 23.6.7.1.3 Output Clock Prescaler

The DPLL controller includes an output prescaler. This prescaler provides three selectable output clocks CK, CKDIV2 and CKDIV4. The Prescaler bit field in the DPLL Prescaler register (DPLLPRESC.PRESC) is used to select a new output clock prescaler. When the prescaler field is modified, the DPLLSYNCBUSY.DPLLPRESC bit is set. It will be cleared by hardware when the synchronization is over.

#### Figure 23-6. Output Clock Switching Operation

#### 23.6.7.1.4 Loop Divider Ratio Updates

The DPLL Controller supports on-the-fly update of the DPLL Ratio Control (DPLLRATIO) register, allowing to modify the loop divider ratio and the loop divider ratio fractional part when the DPLL is enabled.

**Bit 1 – CLKFAIL** XOSC Failure Detection This flag is cleared by writing '1' to it.

This flag is set on a 0-to-1 transition of the XOSC Clock Failure bit in the Status register (STATUS.CLKFAIL) and will generate an interrupt request if INTENSET.CLKFAIL is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the XOSC Clock Fail interrupt flag.

#### Bit 0 – XOSCRDY XOSC Ready

This flag is cleared by writing '1' to it.

This flag is set on a 0-to-1 transition of the XOSC Ready bit in the Status register (STATUS.XOSCRDY) and will generate an interrupt request if INTENSET.XOSCRDY is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the XOSC Ready interrupt flag.

#### 24.6.6 Real-Time Counter Clock Selection

Before enabling the RTC module, the RTC clock must be selected first. All oscillator outputs are valid as RTC clock. The selection is done in the RTC Control register (RTCCTRL). To ensure a proper operation, it is highly recommended to disable the RTC module first, before the RTC clock source selection is changed.

#### **Related Links**

27. RTC - Real-Time Counter

#### 24.6.7 Interrupts

The OSC32KCTRL has the following interrupt sources:

- XOSC32KRDY 32KHz Crystal Oscillator Ready: A 0-to-1 transition on the STATUS.XOSC32KRDY bit is detected

- CLKFAIL Clock Failure Detector: A 0-to-1 transition on the STATUS.CLKFAIL bit is detected

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs. Each interrupt can be enabled individually by setting the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the OSC32KCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSC32KCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

22. PM - Power Manager

#### 24.6.8 Events

The CFD can generate the following output event:

Clock Failure Detector (CLKFAIL): Generated when the Clock Failure Detector status bit is set in the Status register (STATUS.CLKFAIL). The CFD event is not generated when the Clock Switch bit (STATUS.SWBACK) in the Status register is set.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.CFDEO) enables the CFD output event. Writing a '0' to this bit disables the CFD output event. Refer to the Event System chapter for details on configuring the event system.

#### Bit 7 - ONDEMAND On Demand Control

This bit controls how the XOSC32K behaves when a peripheral clock request is detected. For details, refer to XOSC32K Sleep Behavior.

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the XOSC32K behaves during standby sleep mode. For details, refer to XOSC32K Sleep Behavior.

#### Bit 4 – EN1K 1KHz Output Enable

| Value | Description                  |

|-------|------------------------------|

| 0     | The 1KHz output is disabled. |

| 1     | The 1KHz output is enabled.  |

#### Bit 3 – EN32K 32KHz Output Enable

| Value | Description                   |

|-------|-------------------------------|

| 0     | The 32KHz output is disabled. |

| 1     | The 32KHz output is enabled.  |

#### Bit 2 – XTALEN Crystal Oscillator Enable

This bit controls the connections between the I/O pads and the external clock or crystal oscillator.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | External clock connected on XIN32. XOUT32 can be used as general-purpose I/O. |

| 1     | Crystal connected to XIN32/XOUT32.                                            |

#### Bit 1 – ENABLE Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

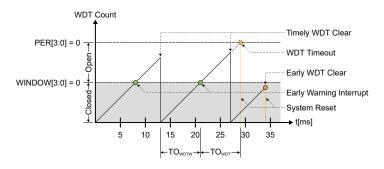

disabled again by writing a '1' to the Early Warning Interrupt bit in the Interrupt Enable Clear (INTENCLR.EW) register.

If the Early Warning interrupt is enabled in Window mode, the interrupt is generated at the start of the open window period, i.e. after TO<sub>WDTW</sub>. The Window mode operation is illustrated in figure Window-Mode Operation.

#### Figure 26-3. Window-Mode Operation

#### 26.6.3 DMA Operation

Not applicable.

#### 26.6.4 Interrupts

The WDT has the following interrupt source:

- Early Warning (EW): Indicates that the counter is approaching the time-out condition.

- This interrupt is an asynchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the WDT is reset. See the 26.8.6 INTFLAG register description for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

22. PM – Power Manager22.6.3.3 Sleep Mode Controller

#### 26.6.5 Events

Not applicable.

- Set the next descriptor address (DESCADDR)

- Set the destination address (DSTADDR)

- Set the source address (SRCADDR)

- Configure the block transfer control (BTCTRL) including

- Optionally enable the Suspend block action

- Set the descriptor VALID bit

- 5. Clear the VALID bit for the existing list and for the descriptor which has to be updated.

- 6. Read DESCADDR from the Write-Back memory.

- If the DMA has not already fetched the descriptor which requires changes (i.e., DESCADDR is wrong):

- Update the DESCADDR location of the descriptor from the List

- Optionally clear the Suspend block action

- Set the descriptor VALID bit to '1'

- Optionally enable the Resume software command

- If the DMA is executing the same descriptor as the one which requires changes:

- Set the Channel Suspend software command and wait for the Suspend interrupt

- Update the next descriptor address (DESCRADDR) in the write-back memory

- Clear the interrupt sources and set the Resume software command

- Update the DESCADDR location of the descriptor from the List

- Optionally clear the Suspend block action

- Set the descriptor VALID bit to '1'

- 7. Go to step 4 if needed.

#### 28.6.3.1.3 Adding a Descriptor Between Existing Descriptors

To insert a new descriptor 'C' between two existing descriptors ('A' and 'B'), the descriptor currently executed by the DMA must be identified.

- 1. If DMA is executing descriptor B, descriptor C cannot be inserted.

- 2. If DMA has not started to execute descriptor A, follow the steps:

- 2.1. Set the descriptor A VALID bit to '0'.

- 2.2. Set the DESCADDR value of descriptor A to point to descriptor C instead of descriptor B.

- 2.3. Set the DESCADDR value of descriptor C to point to descriptor B.

- 2.4. Set the descriptor A VALID bit to '1'.

- 3. If DMA is executing descriptor A:

- 3.1. Apply the software suspend command to the channel and

- 3.2. Perform steps 2.1 through 2.4.

- 3.3. Apply the software resume command to the channel.

#### 28.6.3.2 Channel Suspend

The channel operation can be suspended at any time by software by writing a '1' to the Suspend command in the Command bit field of Channel Control B register (CHCTRLB.CMD). After the ongoing burst transfer is completed, the channel operation is suspended and the suspend command is automatically cleared.

When suspended, the Channel Suspend Interrupt flag in the Channel Interrupt Status and Clear register is set (CHINTFLAG.SUSP=1) and the optional suspend interrupt is generated.

The tamper full erase routine operates at the highest priority. If a remanence routine executing when a tamper full erase occurs, the remanence routine is immediately terminated. If the CPU attempts to write a new scramble key at the same time the tamper key erase routine is active, the CPU data is ignored, but no bus error will occur. If a CPU security routine access is requested during a tamper full erase, the CPU transaction will be ignored and treated as a bus error similar to accessing the module during a software reset.

**Important:** In STANDBY low power mode, it is mandatory to enable the dynamic power gating feature (STDBYCFG.DPGPDSW) to ensure TrustRAM erasing when the power domain PDSW is in a retention state.

#### 31.6.3 Interrupts

The TRAM has the following interrupt sources:

- Data Remanence Prevention (DRP): Indicates that the data remanence prevention routine has ended.

- Data Read Error (ERR): Indicates when there is a RAM readout error.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TRAM is reset. See 22.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### 31.6.4 Sleep Mode Operation

The TRAM continues to operate during sleep. When it receives events from the Event System, it will request its own clock in order to perform the requested operation.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering an interrupt. In this case, the CPU will continue executing from the instruction following the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *EVSYS – Event System* for more information.

#### 31.6.5 Synchronization

Due to the asynchronicity between event sources and CLK\_TRAM\_APB some registers must be synchronized when accessed. A register can require:

Synchronization when written

#### 33.5 Functional Description

#### 33.5.1 Principle of Operation

The Event System consists of several channels which route the internal events from peripherals (generators) to other internal peripherals or I/O pins (users). Each event generator can be selected as source for multiple channels, but a channel cannot be set to use multiple event generators at the same time.

A channel path can be configured in asynchronous, synchronous or resynchronized mode of operation. The mode of operation must be selected based on the requirements of the application.

When using synchronous or resynchronized path, the Event System includes options to transfer events to users when rising, falling or both edges are detected on event generators.

For further details, refer to the Channel Path section of this chapter.

#### **Related Links**

33.5.2.6 Channel Path

#### 33.5.2 Basic Operation

#### 33.5.2.1 Initialization

Before enabling event routing within the system, the Event Users Multiplexer and Event Channels must be selected in the Event System (EVSYS), and the two peripherals that generate and use the event have to be configured. The recommended sequence is:

- 1. In the event generator peripheral, enable output of event by writing a '1' to the respective Event Output Enable bit ("EO") in the peripheral's Event Control register (e.g., TCC.EVCTRL.MCEO1, AC.EVCTRL.WINEO0, RTC.EVCTRL.OVFEO).

- 2. Configure the EVSYS:

- 2.1. Configure the Event User multiplexer by writing the respective EVSYS.USERm register, see also 33.5.2.3 User Multiplexer Setup.

- 2.2. Configure the Event Channel by writing the respective EVSYS.CHANNELn register, see also 33.5.2.4 Event System Channel.

- Configure the action to be executed by the event user peripheral by writing to the Event Action bits (EVACT) in the respective Event control register (e.g., TC.EVCTRL.EVACT, PDEC.EVCTRL.EVACT). Note: not all peripherals require this step.

- 4. In the event user peripheral, enable event input by writing a '1' to the respective Event Input Enable bit ("EI") in the peripheral's Event Control register (e.g., AC.EVCTRL.IVEI0, ADC.EVCTRL.STARTEI).

#### 33.5.2.2 Enabling, Disabling, and Resetting

The EVSYS is always enabled.

The EVSYS is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the EVSYS will be reset to their initial state and all ongoing events will be canceled.

Refer to CTRLA.SWRST register for details.

#### 33.5.2.3 User Multiplexer Setup

The user multiplexer defines the channel to be connected to which event user. Each user multiplexer is dedicated to one event user. A user multiplexer receives all event channels output and must be configured to select one of these channels, as shown in Block Diagram section. The channel is selected with the Channel bit group in the User register (USERm.CHANNEL).

#### 33.5.3 Interrupts

The EVSYS has the following interrupt sources for each channel:

- Overrun Channel n interrupt (OVR)

- Event Detected Channel n interrupt (EVD)

These interrupts events are asynchronous wake-up sources.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the corresponding Channel n Interrupt Flag Status and Clear (CHINTFLAG) register is set when the interrupt condition occurs.

**Note:** Interrupts must be globally enabled to allow the generation of interrupt requests.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Channel n Interrupt Enable Set (CHINTENSET) register, and disabled by writing a '1' to the corresponding bit in the Channel n Interrupt Enable Clear (CHINTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the Event System is reset. All interrupt requests are ORed together on system level to generate one combined interrupt request to the NVIC.

The user must read the Channel Interrupt Status (INTSTATUS) register to identify the channels with pending interrupts, and must read the Channel n Interrupt Flag Status and Clear (CHINTFLAG) register to determine which interrupt condition is present for the corresponding channel. It is also possible to read the Interrupt Pending register (INTPEND), which provides the highest priority channel with pending interrupt and the respective interrupt flags.

#### 33.5.4 Sleep Mode Operation

The Event System can generate interrupts to wake up the device from IDLE or STANDBY sleep mode.

To be able to run in standby, the Run in Standby bit in the Channel register (CHANNELn.RUNSTDBY) must be set to '1'. When the Generic Clock On Demand bit in Channel register (CHANNELn.ONDEMAND) is set to '1' and the event generator is detected, the event channel will request its clock (GCLK\_EVSYS\_CHANNEL\_n). The event latency for a resynchronized channel path will increase by two GCLK\_EVSYS\_CHANNEL\_n clock (i.e., up to five GCLK\_EVSYS\_CHANNEL\_n clock cycles).

A channel will behave differently in different sleep modes regarding to CHANNELn.RUNSTDBY and CHANNELn.ONDEMAND:

| CHANNELn.PAT<br>H | CHANNELn.<br>ONDEMAND | CHANNELn.<br>RUNSTDBY | Sleep Behavior                                                                                                              |

|-------------------|-----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| ASYNC             | 0                     | 0                     | Only run in IDLE sleep modes if an event<br>must be propagated. Disabled in STANDBY<br>sleep mode.                          |

| SYNC/RESYNC       | 0                     | 1                     | Run in both IDLE and STANDBY sleep modes.                                                                                   |

| SYNC/RESYNC       | 1                     | 0                     | Only run in IDLE sleep modes if an event<br>must be propagated. Disabled in STANDBY<br>sleep mode. Two GCLK_EVSYS_n latency |

#### Table 33-1. Event Channel Sleep Behavior

- 7.2. Configure the Parity Mode bit in the CTRLB register (CTRLB.PMODE) for even or odd parity.

- 8. Configure the number of stop bits in the Stop Bit Mode bit in the CTRLB register (CTRLB.SBMODE).

- 9. When using an internal clock, write the Baud register (BAUD) to generate the desired baud rate.

- 10. Enable the transmitter and receiver by writing '1' to the Receiver Enable and Transmitter Enable bits in the CTRLB register (CTRLB.RXEN and CTRLB.TXEN).

#### 35.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

Refer to the CTRLA register description for details.

#### 35.6.2.3 Clock Generation and Selection

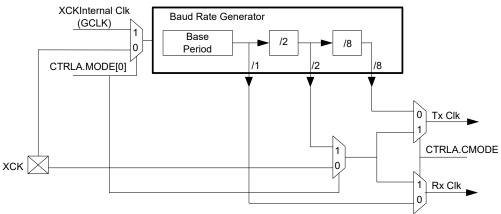

For both synchronous and asynchronous modes, the clock used for shifting and sampling data can be generated internally by the SERCOM baud-rate generator or supplied externally through the XCK line.

The synchronous mode is selected by writing a '1' to the Communication Mode bit in the Control A register (CTRLA.CMODE), the asynchronous mode is selected by writing a zero to CTRLA.CMODE.

The internal clock source is selected by writing 0x1 to the Operation Mode bit field in the Control A register (CTRLA.MODE), the external clock source is selected by writing 0x0 to CTRLA.MODE.

The SERCOM baud-rate generator is configured as in the figure below.

In asynchronous mode (CTRLA.CMODE=0), the 16-bit Baud register value is used.

In synchronous mode (CTRLA.CMODE=1), the eight LSBs of the Baud register are used. Refer to *Clock Generation – Baud-Rate Generator* for details on configuring the baud rate.

#### Figure 35-3. Clock Generation

#### **Related Links**

34.6.2.3 Clock Generation – Baud-Rate Generator 34.6.2.3.1 Asynchronous Arithmetic Mode BAUD Value Selection

#### 35.6.2.3.1 Synchronous Clock Operation

In synchronous mode, the CTRLA.MODE bit field determines whether the transmission clock line (XCK) serves either as input or output. The dependency between clock edges, data sampling, and data change

#### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

#### 38.7.1.6 Interrupt Enable Set

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

| [      |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

**Bit 4 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will set the corresponding Match or Capture Channel x Interrupt Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### Bit 0 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Valu | ue | Description                         |

|------|----|-------------------------------------|

| 0    |    | The Overflow interrupt is disabled. |

| 1    |    | The Overflow interrupt is enabled.  |

## **Electrical Characteristics**

| Symb  | Parameters                                    | ameters Conditions                                          |                                | Measur | Unit    |             |      |  |

|-------|-----------------------------------------------|-------------------------------------------------------------|--------------------------------|--------|---------|-------------|------|--|

| ol    | Farameters                                    | Conditions                                                  |                                |        | Тур     | Max         | Omt  |  |

|       |                                               |                                                             | Vref=3V Vddana=1.6V to<br>3.6V | -      | +/-1.82 | +/-14.<br>9 |      |  |

|       |                                               |                                                             | Bandgap Reference              | -      | +/-2.07 | +/-15.<br>8 |      |  |

|       |                                               |                                                             | Vref=Vddana=1.6V to<br>3.6V    | -      | +/-1.82 | +/-15.<br>3 |      |  |

| SFDR  | Spurious Free<br>Dynamic<br>Range             | Fs = 1MHz /<br>Fin = 13 kHz /<br>Full range<br>Input signal | in = 13 kHz /<br>ull range     | 58.1   | 70.5    | 77.5        | dB   |  |

| SINAD | Signal to<br>Noise and<br>Distortion<br>ratio |                                                             | Input signal                   |        | 56.7    | 63.4        | 66.5 |  |

| SNR   | Signal to<br>Noise ratio                      |                                                             |                                | 56.5   | 64.4    | 67.1        |      |  |

| THD   | Total<br>Harmonic<br>Distortion               |                                                             |                                | -74.7  | -68.7   | -57.7       |      |  |

| -     | Noise RMS                                     | External Refere                                             | nce voltage                    | -      | 0.42    | -           | mV   |  |

#### Note:

1. These are given without any ADC oversampling and decimation features enabled.

## Table 46-25. Single-Ended Mode (1)

| Symbol | Paramete                      | Conditions                                        | tions                                     |     | Measurements |        |      |  |  |

|--------|-------------------------------|---------------------------------------------------|-------------------------------------------|-----|--------------|--------|------|--|--|

| Symbol | rs                            | Conditions                                        | •                                         | Min | Тур          | Max    | Unit |  |  |

| ENOB   | Effective                     | Fadc =                                            | Vref=2.0V Vddana=3.0V                     | 8.0 | 9.3          | 9.7    | bits |  |  |

|        | Number of bits                | 1Msps                                             | Vref=1.0V Vddana=1.6V to 3.6V             | 7.9 | 8.2          | 9.4    |      |  |  |

|        |                               |                                                   | Vref=Vddana=1.6V to 3.6V                  | 8.6 | 9.2          | 9.9    |      |  |  |

|        |                               |                                                   | Bandgap Reference,<br>Vddana=1.6V to 3.6V | 7.8 | 8.4          | 8.9    |      |  |  |

| TUE    | Total<br>Unadjuste<br>d Error | without<br>offset and<br>gain<br>compensa<br>tion | Vref=2.0V Vddana=3.0V                     | -   | 12           | 63     | LSB  |  |  |

| INL    | Integral<br>Non<br>Linearity  | without<br>offset and<br>gain                     | Vref=2.0V Vddana=3.0V                     | -   | +/-3.4       | +/-8.9 |      |  |  |

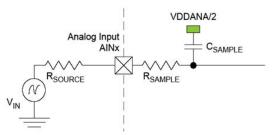

#### Figure 46-2. ADC Analog Input AINx

The minimum sampling time  $t_{\text{samplehold}}$  for a given  $R_{\text{source}}$  can be found using this formula:

$t_{\text{samplehold}} \ge (R_{\text{sample}} + R_{\text{source}}) \times C_{\text{sample}} \times (n+2) \times \ln(2)$ For 12-bit accuracy:

$t_{\text{samplehold}} \ge (R_{\text{sample}} + R_{\text{source}}) \times C_{\text{sample}} \times 9.7$ where  $t_{\text{samplehold}} \ge \frac{1}{2 \times f_{\text{ADC}}}$ .

# 46.11.5 Digital-to-Analog Converter (DAC) Characteristics

#### Table 46-26. Operating Conditions<sup>(1)</sup>

| Symbol | Parameters                   | Conditions            | Min  | Тур    | Мах         | Unit |

|--------|------------------------------|-----------------------|------|--------|-------------|------|

| AVREF  | External reference voltage   |                       | 1    | -      | VDDANA-0.6  | V    |

|        | Internal reference voltage 1 |                       | -    | 1      | -           | V    |

|        | Internal reference voltage 2 |                       | -    | VDDANA | -           | V    |

|        | Linear output voltage range  |                       | 0.05 | -      | VDDANA-0.05 | V    |

|        | Minimum resistive load       |                       | 5    | -      | -           | kOhm |

|        | Maximum capacitance load     |                       | -    | -      | 100         | pF   |

| IDD    | DC supply current(2)         | Voltage pump disabled | -    | 175    | 247         | μA   |

#### Note:

- 1. The values in this table are based on specifications otherwise noted.

- 2. These values are based on characterization. These values are not covered in test limits in production.

#### Table 46-27. Clock and Timing

| Parameter       | Conditions                |                                |   | Тур. | Max. | Units |

|-----------------|---------------------------|--------------------------------|---|------|------|-------|

| Conversion rate | Cload=100pF Rload > 5kOhm | 00pF Rload > 5kOhm Normal mode |   |      | 350  | ksps  |

|                 |                           | For DDATA=+/-1                 |   |      | 1000 |       |

| Startup time    | VDDANA > 2.6V             | VDDANA > 2.6V                  | - | -    | 2.85 | μs    |

|                 | VDDANA < 2.6V             | VDDANA < 2.6V                  | - | -    | 10   | μs    |

**Note:** These values are based on simulation. These values are not covered by test limits in production or characterization.

## **Electrical Characteristics**

| Symbol | Parameters                                                                   | Conditions        | Та                   | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------------------------------------|-------------------|----------------------|------|------|------|------|

| IDD    | DC supply current (Voltage<br>Doubler OFF)<br>Voltage Doubler<br>consumption | Mode 3,VCC =3.3V  | Max 85°C Typ<br>25°C | -    | 235  | 400  | μA   |

|        |                                                                              | Mode 2,VCC =3.3V  |                      | -    | 94   | 166  |      |

|        |                                                                              | Mode 1,VCC =3.3V  |                      | -    | 26   | 47   |      |

|        |                                                                              | Mode 0 ,VCC =3.3V |                      | -    | 7    | 13   |      |

|        |                                                                              | VCC =3.3V         |                      | -    | 0.70 | 1.4  |      |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

Table 46-34. Static Characteristics in 1X Gain<sup>(1)</sup>

Table 46-33. Power Consumption<sup>(1)</sup>

| Symbol             | Parameters                          | Conditions | Min. | Тур.      | Max.  | Unit |

|--------------------|-------------------------------------|------------|------|-----------|-------|------|

| G0                 | Open loop gain                      | Mode 3     | -    | 114.5     | -     | dB   |

|                    |                                     | Mode 2     | -    | 117.6     | -     |      |

|                    |                                     | Mode 1     | -    | 116.8     | -     |      |

|                    |                                     | Mode 0     | -    | 108.5     | -     |      |

| GBW                | Gain Bandwidth                      | Mode 3     | -    | 7.1       | -     | MHz  |

|                    |                                     | Mode 2     | -    | 2.8       | -     |      |

|                    |                                     | Mode 1     | -    | 0.85      | -     |      |

|                    |                                     | Mode 0     | -    | 0.2       | -     |      |

| φ <sub>m</sub>     | Phase margin                        | Mode 3     | -    | 71.5      | -     | deg  |

|                    |                                     | Mode 2     | -    | 64        | -     |      |

|                    |                                     | Mode 1     | -    | 56        | -     |      |

|                    |                                     | Mode 0     | -    | 52        | -     |      |

| T <sub>r1</sub>    | Response Time at 240µV (X1 gain)    | Mode 3     | -    | 1.3       | -     | μs   |

|                    |                                     | Mode 2     | -    | 3.3       | -     |      |

|                    |                                     | Mode 1     | -    | 13        | -     |      |

|                    |                                     | Mode 0     | -    | 52        | -     |      |

| ΔT <sub>r1</sub>   | Response Time<br>Variation for 10mV | Mode 3     | -    | 100       | -     | ns   |

| T <sub>start</sub> | Start-up time (Enable               | Mode 3     | -    | 2.7       | -     | μs   |

|                    | to Ready), (Voltage<br>Doubler OFF) | Mode 2     | -    | 6.35      | -     |      |

|                    |                                     | Mode 1     | -    | 21.5      | -     |      |

|                    |                                     | Mode 0     | -    | 88.5      | -     |      |

| Oe                 | Input Offset Voltage                |            | -    | -         | +-3.5 | mV   |

| SR                 | Slew rate                           | Mode 3     | -    | - 2.8/2.6 | -     | V/µs |

|                    |                                     | Mode 2     | -    | -1.2/1.1  | -     |      |