# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-VQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e15a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 22.4.   | Signal Description                      |     |

|---------|-----------------------------------------|-----|

| 22.5.   | Product Dependencies                    |     |

| 22.6.   | Functional Description                  | 245 |

| 22.7.   | Register Summary                        |     |

| 22.8.   | Register Description                    |     |

|         |                                         |     |

|         | CCTRL – Oscillators Controller          |     |

| 23.1.   | Overview                                | 271 |

| 23.2.   | Features                                |     |

| 23.3.   | Block Diagram                           | 272 |

| 23.4.   | Signal Description                      | 272 |

| 23.5.   | Product Dependencies                    | 272 |

| 23.6.   | Functional Description                  |     |

| 23.7.   | Register Summary                        |     |

| 23.8.   | Register Description                    |     |

| 24 050  | C32KCTRL – 32KHz Oscillators Controller | 210 |

|         |                                         |     |

|         | Overview                                |     |

|         | Features                                |     |

|         | Block Diagram                           |     |

|         | Signal Description                      |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

| 24.8.   | Register Description                    |     |

| 25 SUF  | PC – Supply Controller                  | 339 |

|         | Overview                                |     |

|         | Features                                |     |

|         |                                         |     |

|         | Block Diagram                           |     |

|         |                                         |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

| 25.8.   | Register Description                    |     |

| 26. WD  | T – Watchdog Timer                      |     |

| 26.1.   | Overview                                | 366 |

|         | Features                                |     |

|         | Block Diagram                           |     |

|         | Signal Description                      |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

|         | Register Description                    |     |

| 20.0.   |                                         |     |

| 27. RTC | c – Real-Time Counter                   |     |

| 27.1    | Overview                                |     |

|         |                                         |     |

# 17. Clock System

This chapter summarizes the clock distribution and terminology in the SAM L10/L11 device. This document will not explain every detail of its configuration, hence for in-depth details, refer to the respective peripherals descriptions and the *Generic Clock* documentation.

# 17.1 Clock Distribution

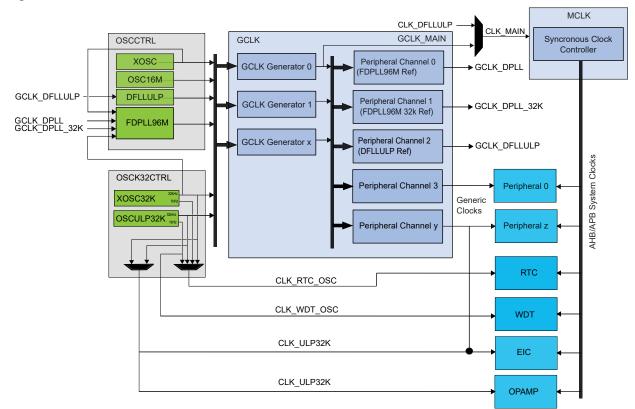

Figure 17-1. Clock Distribution

The SAM L10/L11 clock system consists of these features:

- Clock sources, that is oscillators controlled by OSCCTRL and OSC32KCTRL

- A clock source provides a time base that is used by other components, such as Generic Clock Generators. Example clock sources are the internal 16MHz oscillator (OSC16M), external crystal oscillator (XOSC) and the Fractional Digital Phase Locked Loop (FDPLL96M).

- *Generic Clock Controller (GCLK),* which generates, controls and distributes the asynchronous clock consisting of:

- Generic Clock Generators: These are programmable prescalers that can use any of the system clock sources as a time base. The Generic Clock Generator 0 generates the clock signal GCLK\_MAIN, which is used by the Power Manager and the Main Clock (MCLK) module, which in turn generates synchronous clocks.

- Generic Clocks: These are clock signals generated by Generic Clock Generators and output by the Peripheral Channels, and serve as clocks for the peripherals of the system. Multiple instances of a peripheral will typically have a separate Generic Clock for each instance.

If the Output Enable bit in the Generator Control register is set (GENCTRLn.OE = 1) and the generator is enabled (GENCTRLn.GENEN=1), the Generator requests its clock source and the GCLK\_GEN clock is output to an I/O pin.

**Note:** The I/O pin (GCLK/IO[n]) must first be configured as output by writing the corresponding PORT registers.

If GENCTRLn.OE is 0, the according I/O pin is set to an Output Off Value, which is selected by GENCTRLn.OOV: If GENCTRLn.OOV is '0', the output clock will be low. If this bit is '1', the output clock will be high.

In Standby mode, if the clock is output (GENCTRLn.OE=1), the clock on the I/O pin is frozen to the OOV value if the Run In Standby bit of the Generic Control register (GENCTRLn.RUNSTDBY) is zero. **Note:** With GENCTRLn.OE=1 and RUNSTDBY=0, entering the Standby mode can take longer due to a clock source dependent delay between turning off Power Domain PDSW. The maximum delay can be equal to the clock source period multiplied by the division factor.

If GENCTRLn.RUNSTDBY is '1', the GCLKGEN clock is kept running and output to the I/O pin.

#### **Related Links**

22.6.3.5 Power Domain Controller

#### 18.6.3 Peripheral Clock

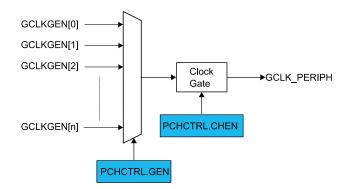

Figure 18-4. Peripheral Clock

#### 18.6.3.1 Enabling a Peripheral Clock

Before a Peripheral Clock is enabled, one of the Generators must be enabled (GENCTRLn.GENEN) and selected as source for the Peripheral Channel by setting the Generator Selection bits in the Peripheral Channel Control register (PCHCTRL.GEN). Any available Generator can be selected as clock source for each Peripheral Channel.

When a Generator has been selected, the peripheral clock is enabled by setting the Channel Enable bit in the Peripheral Channel Control register, PCHCTRLm.CHEN = 1. The PCHCTRLm.CHEN bit must be synchronized to the generic clock domain. PCHCTRLm.CHEN will continue to read as its previous state until the synchronization is complete.

#### 18.6.3.2 Disabling a Peripheral Clock

A Peripheral Clock is disabled by writing PCHCTRLm.CHEN=0. The PCHCTRLm.CHEN bit must be synchronized to the Generic Clock domain. PCHCTRLm.CHEN will stay in its previous state until the synchronization is complete. The Peripheral Clock is gated when disabled.

#### **Related Links**

18.8.4 PCHCTRLm

#### 27.8.11 Compare 0 Value in COUNT32 mode (CTRLA.MODE=0)

| Name:     | COMP                                     |

|-----------|------------------------------------------|

| Offset:   | 0x20                                     |

| Reset:    | 0x0000000                                |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 31  | 30  | 29  | 28   | 27      | 26  | 25  | 24  |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

|        |     |     |     | COMP | [31:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19      | 18  | 17  | 16  |

|        |     |     |     | COMP | [23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|        |     |     |     | COMF | P[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        |     |     |     | COM  | P[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

### Bits 31:0 - COMP[31:0] Compare Value

The 32-bit value of COMP0 is continuously compared with the 32-bit COUNT value. When a match occurs, the Compare 0 interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next counter cycle, and the counter value is cleared if CTRLA.MATCHCLR is '1'.

# SAM L10/L11 Family

# RTC – Real-Time Counter

| Offset           | Name      | Bit Pos. |                     |           |                    |         |                |           |         |         |

|------------------|-----------|----------|---------------------|-----------|--------------------|---------|----------------|-----------|---------|---------|

|                  |           | 7:0      |                     |           | l                  | GP      | <b>P</b> [7:0] |           | I       |         |

|                  | 0.54      | 15:8     |                     | GP[15:8]  |                    |         |                |           |         |         |

| 0x44             | GP1       | 23:16    |                     |           |                    | GP[2    | 23:16]         |           |         |         |

|                  |           | 31:24    |                     |           |                    | GP[     | 31:24]         |           |         |         |

| 0x48<br><br>0x5F | Reserved  |          |                     |           |                    |         |                |           |         |         |

|                  |           | 7:0      | IN3AC               | CT[1:0]   | IN2A0              | CT[1:0] | IN1AC          | CT[1:0]   | IN0A0   | CT[1:0] |

| 0x60             | TAMPCTRL  | 15:8     |                     |           |                    |         |                |           |         |         |

| 0,000            | IAMPCTRE  | 23:16    |                     |           |                    |         | TAMLVL3        | TAMLVL2   | TAMLVL1 | TAMLVL0 |

|                  |           | 31:24    |                     |           |                    |         | DEBNC3         | DEBNC2    | DEBNC1  | DEBNC0  |

|                  |           | 7:0      | MINU                | FE[1:0]   | E[1:0] SECOND[5:0] |         |                |           |         |         |

| 0x64             | TIMESTAMP | 15:8     | HOUR[3:0]           |           |                    |         | MINU           | TE[5:2]   |         |         |

| 0704             | TIMEOTAW  | 23:16    | MONTH[1:0] DAY[4:0] |           |                    |         |                | HOUR[4:4] |         |         |

|                  |           | 31:24    |                     | YEAR[5:0] |                    |         | MONTH[3:2]     |           |         |         |

|                  |           | 7:0      |                     |           |                    |         | TAMPID3        | TAMPID2   | TAMPID1 | TAMPID0 |

| 0x68             | TAMPID    | 15:8     |                     |           |                    |         |                |           |         |         |

| 0,00             |           | 23:16    |                     |           |                    |         |                |           |         |         |

|                  |           | 31:24    | TAMPEVT             |           |                    |         |                |           |         |         |

|                  |           | 7:0      |                     |           |                    |         | ALSI3          | ALSI2     | ALSI1   | ALSI0   |

| 0x6C             | TAMPCTRLB | 15:8     |                     |           |                    |         |                |           |         |         |

| 0.00             |           | 23:16    |                     |           |                    |         |                |           |         |         |

|                  |           | 31:24    |                     |           |                    |         |                |           |         |         |

# 27.12 Register Description - Mode 2 - Clock/Calendar

This Register Description section is valid if the RTC is in Clock/Calendar mode (CTRLA.MODE=2).

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

#### 27.12.2 Control B in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x2                                    |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15    | 14     | 13        | 12     | 11 | 10  | 9         | 8     |

|--------|-------|--------|-----------|--------|----|-----|-----------|-------|

| ĺ      | SEPTO |        | ACTF[2:0] |        |    |     | DEBF[2:0] |       |

| Access | R/W   | R/W    | R/W       | R/W    |    | R/W | R/W       | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    | 0   | 0         | 0     |

|        |       |        |           |        |    |     |           |       |

| Bit    | 7     | 6      | 5         | 4      | 3  | 2   | 1         | 0     |

|        | DMAEN | RTCOUT | DEBASYNC  | DEBMAJ |    |     |           | GP0EN |

| Access | R/W   | R/W    | R/W       | R/W    |    |     |           | R/W   |

| Reset  | 0     | 0      | 0         | 0      |    |     |           | 0     |

#### Bit 15 – SEPTO Separate Tamper Outputs

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | IN[n] is compared tp OUT[0] (backward-compatible). |

| 1     | IN[n] is compared tp OUT[n].                       |

#### Bits 14:12 – ACTF[2:0] Active Layer Frequency

These bits define the prescaling factor for the RTC clock output (OUT) used during active layer protection in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_OUT = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_OUT = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_OUT = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_OUT = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_OUT = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_OUT = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_OUT = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_OUT = CLK_RTC / 256 |

#### Bits 10:8 – DEBF[2:0] Debounce Frequency

These bits define the prescaling factor for the input debouncers in terms of the CLK\_RTC.

| Value | Name   | Description                 |

|-------|--------|-----------------------------|

| 0x0   | DIV2   | CLK_RTC_DEB = CLK_RTC / 2   |

| 0x1   | DIV4   | CLK_RTC_DEB = CLK_RTC / 4   |

| 0x2   | DIV8   | CLK_RTC_DEB = CLK_RTC / 8   |

| 0x3   | DIV16  | CLK_RTC_DEB = CLK_RTC / 16  |

| 0x4   | DIV32  | CLK_RTC_DEB = CLK_RTC / 32  |

| 0x5   | DIV64  | CLK_RTC_DEB = CLK_RTC / 64  |

| 0x6   | DIV128 | CLK_RTC_DEB = CLK_RTC / 128 |

| 0x7   | DIV256 | CLK_RTC_DEB = CLK_RTC / 256 |

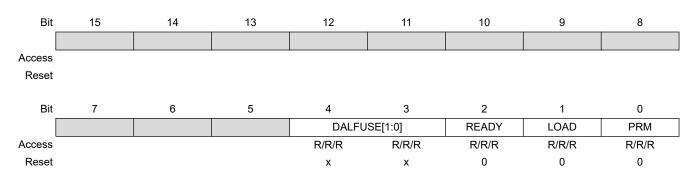

#### 30.8.8 Status

| Name:     | STATUS       |

|-----------|--------------|

| Offset:   | 0x18         |

| Reset:    | 0x0X00       |

| Property: | Write-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in NONSEC register.

#### Bits 4:3 - DALFUSE[1:0] DAL Fuse Value

This field is the current debugger access level fuse value.

| Value | Description                                                                                      |

|-------|--------------------------------------------------------------------------------------------------|

| 0     | DAL = 0 : Access to very limited features.                                                       |

| 1     | DAL = 1 ( <b>SAM L11 only</b> ): Access to all non-secure memory. Can debug non-secure CPU code. |

| 2     | DAL = 2 : Access to all memory. Can debug Secure and non-secure CPU code.                        |

| 3     | Reserved                                                                                         |

#### Bit 2 - READY NVM Ready

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The NVM controller is busy programming or erasing.   |

| 1     | The NVM controller is ready to accept a new command. |

#### Bit 1 - LOAD NVM Page Buffer Active Loading

This bit indicates that the NVM page buffer has been loaded with one or more words. Immediately after an NVM load has been performed, this flag is set. It remains set until a page write or a page buffer clear (PBC) command is given.

#### Bit 0 – PRM Power Reduction Mode

This bit indicates the current NVM power reduction state. The NVM block can be set in power reduction mode in two ways: through the command interface or automatically when entering sleep with SLEEPPRM set accordingly.

# SAM L10/L11 Family TRAM - TrustRAM

| Offset | Name  | Bit Pos. |            |           |  |      |         |  |  |  |

|--------|-------|----------|------------|-----------|--|------|---------|--|--|--|

|        |       | 7:0      |            | DATA[7:0] |  |      |         |  |  |  |

| 0.0150 | RAM63 | 15:8     | DATA[15:8] |           |  |      |         |  |  |  |

| 0x01FC |       | 23:16    |            |           |  | DATA | [23:16] |  |  |  |

|        |       | 31:24    |            |           |  | DATA | [31:24] |  |  |  |

# 31.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Refer to PAC - Peripheral Access Controller and 39.6.6 Synchronization for details.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

# SAM L10/L11 Family

# EVSYS – Event System

| _              |             |          |          |          |  |     |          |        |        |

|----------------|-------------|----------|----------|----------|--|-----|----------|--------|--------|

| Offset         | Name        | Bit Pos. |          |          |  |     |          |        |        |

| 0x26           | CHINTFLAG0  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x27           | CHSTATUS0   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0x28           | CHANNEL1    | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| UNEO OF MINIEL | 23:16       |          |          |          |  |     |          |        |        |

|                |             | 31:24    |          |          |  |     |          |        |        |

| 0x2C           | CHINTENCLR1 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2D           | CHINTENSET1 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2E           | CHINTFLAG1  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2F           | CHSTATUS1   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0x30           | CHANNEL2    | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| 0,00           | CHANNELZ    | 23:16    |          |          |  |     |          |        |        |

|                |             | 31:24    |          |          |  |     |          |        |        |

| 0x34           | CHINTENCLR2 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x35           | CHINTENSET2 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x36           | CHINTFLAG2  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x37           | CHSTATUS2   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                | CHANNEL3    | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0x38           |             | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

|                |             | 23:16    |          |          |  |     |          |        |        |

|                |             | 31:24    |          |          |  |     |          |        |        |

| 0x3C           | CHINTENCLR3 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3D           | CHINTENSET3 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3E           | CHINTFLAG3  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3F           | CHSTATUS3   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                |             | 7:0      |          |          |  | EVG | EN[5:0]  |        | 1      |

| 040            |             | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| 0x40           | CHANNEL4    | 23:16    |          |          |  |     |          |        |        |

|                |             | 31:24    |          |          |  |     |          |        |        |

| 0x44           | CHINTENCLR4 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x45           | CHINTENSET4 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x46           | CHINTFLAG4  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x47           | CHSTATUS4   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 010            |             | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATI   | H[1:0] |

| 0x48           | CHANNEL5    | 23:16    |          |          |  |     |          |        |        |

|                |             | 31:24    |          |          |  |     |          |        |        |

| 0x4C           | CHINTENCLR5 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4D           | CHINTENSET5 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4E           | CHINTFLAG5  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4F           | CHSTATUS5   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|                |             | 7:0      |          |          |  | EVG | EN[5:0]  |        | 1      |

| a ==           |             | 15:8     | ONDEMAND | RUNSTDBY |  |     | SEL[1:0] | PATH   | H[1:0] |

| 0x50           | CHANNEL6    | 00.40    |          |          |  |     |          |        |        |

|                |             | 23:16    |          |          |  |     |          |        |        |

This bit is not synchronized.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Asynchronous communication. |

| 1     | Synchronous communication.  |

#### Bits 27:24 – FORM[3:0] Frame Format

These bits define the frame format.

These bits are not synchronized.

| FORM[3:0] | Description                                            |

|-----------|--------------------------------------------------------|

| 0x0       | USART frame                                            |

| 0x1       | USART frame with parity                                |

| 0x2-0x3   | Reserved                                               |

| 0x4       | Auto-baud (LIN Slave) - break detection and auto-baud. |

| 0x5       | Auto-baud - break detection and auto-baud with parity  |

| 0x6       | Reserved                                               |

| 0x7       | ISO 7816                                               |

| 0x8-0xF   | Reserved                                               |

#### Bits 23:22 – SAMPA[1:0] Sample Adjustment

These bits define the sample adjustment.

These bits are not synchronized.

| SAMPA[1:0] | 16x Over-sampling (CTRLA.SAMPR=0 or 1) | 8x Over-sampling (CTRLA.SAMPR=2 or 3) |

|------------|----------------------------------------|---------------------------------------|

| 0x0        | 7-8-9                                  | 3-4-5                                 |

| 0x1        | 9-10-11                                | 4-5-6                                 |

| 0x2        | 11-12-13                               | 5-6-7                                 |

| 0x3        | 13-14-15                               | 6-7-8                                 |

### Bits 21:20 - RXPO[1:0] Receive Data Pinout

These bits define the receive data (RxD) pin configuration.

These bits are not synchronized.

| RXPO[1:0] | Name   | Description                              |

|-----------|--------|------------------------------------------|

| 0x0       | PAD[0] | SERCOM PAD[0] is used for data reception |

| 0x1       | PAD[1] | SERCOM PAD[1] is used for data reception |

| 0x2       | PAD[2] | SERCOM PAD[2] is used for data reception |

| 0x3       | PAD[3] | SERCOM PAD[3] is used for data reception |

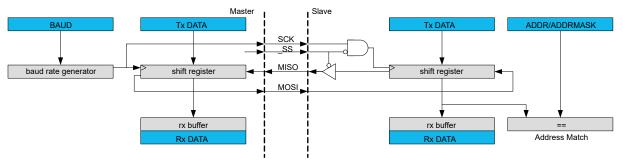

# 36.3 Block Diagram

Figure 36-1. Full-Duplex SPI Master Slave Interconnection

# 36.4 Signal Description

#### Table 36-1. SERCOM SPI Signals

| Signal Name | Туре        | Description         |

|-------------|-------------|---------------------|

| PAD[3:0]    | Digital I/O | General SERCOM pins |

One signal can be mapped to one of several pins.

### 36.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 36.5.1 I/O Lines

In order to use the SERCOM's I/O lines, the I/O pins must be configured using the IO Pin Controller (PORT).

When the SERCOM is configured for SPI operation, the SERCOM controls the direction and value of the I/O pins according to the table below. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver is disabled, the data input pin can be used for other purposes. In master mode, the slave select line ( $\overline{SS}$ ) is hardware controlled when the Master Slave Select Enable bit in the Control B register (CTRLB.MSSEN) is '1'.

#### Table 36-2. SPI Pin Configuration

| Pin  | Master SPI             | Slave SPI |

|------|------------------------|-----------|

| MOSI | Output                 | Input     |

| MISO | Input                  | Output    |

| SCK  | Output                 | Input     |

| SS   | Output (CTRLB.MSSEN=1) | Input     |

The combined configuration of PORT, the Data In Pinout and the Data Out Pinout bit groups in the Control A register (CTRLA.DIPO and CTRLA.DOPO) define the physical position of the SPI signals in the table above.

#### **Related Links**

#### 37.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

22. PM - Power Manager

#### 37.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Main Clock Controller. Refer to *Peripheral Clock Masking* for details and default status of this clock.

Two generic clocks are used by SERCOM, GCLK\_SERCOMx\_CORE and GCLK\_SERCOM\_SLOW. The core clock (GCLK\_SERCOMx\_CORE) can clock the I<sup>2</sup>C when working as a master. The slow clock (GCLK\_SERCOM\_SLOW) is required only for certain functions, e.g. SMBus timing. These two clocks must be configured and enabled in the Generic Clock Controller (GCLK) before using the I<sup>2</sup>C.

These generic clocks are asynchronous to the bus clock (CLK\_SERCOMx\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to 37.6.6 Synchronization for further details.

#### **Related Links**

GCLK - Generic Clock Controller

19.6.2.6 Peripheral Clock Masking

PM – Power Manager

#### 37.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

28. DMAC - Direct Memory Access Controller

#### 37.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### 37.5.6 Events

Not applicable.

#### 37.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 37.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

#### 38.7.1.4 Event Control

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x06                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15 | 14 | 13    | 12    | 11 | 10  | 9          | 8     |

|--------|----|----|-------|-------|----|-----|------------|-------|

|        |    |    | MCEOx | MCEOx |    |     |            | OVFEO |

| Access |    |    | R/W   | R/W   |    |     |            | R/W   |

| Reset  |    |    | 0     | 0     |    |     |            | 0     |

|        |    |    |       |       |    |     |            |       |

| Bit    | 7  | 6  | 5     | 4     | 3  | 2   | 1          | 0     |

|        |    |    | TCEI  | TCINV |    |     | EVACT[2:0] |       |

| Access |    |    | R/W   | R/W   |    | R/W | R/W        | R/W   |

| Reset  |    |    | 0     | 0     |    | 0   | 0          | 0     |

**Bits 13,12 – MCEOx** Match or Capture Channel x Event Output Enable [x = 1..0] These bits enable the generation of an event for every match or capture on channel x.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Match/Capture event on channel x is disabled and will not be generated.              |

| 1     | Match/Capture event on channel x is enabled and will be generated for every compare/ |

|       | capture.                                                                             |

#### Bit 8 - OVFEO Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

#### Bit 5 - TCEI TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

#### Bit 4 – TCINV TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Input event source is not inverted. |

| 1     | Input event source is inverted.     |

#### Bits 2:0 – EVACT[2:0] Event Action

These bits define the event action the TC will perform on an event.

# SAM L10/L11 Family

TC – Timer/Counter

| Value | Name      | Description                                |

|-------|-----------|--------------------------------------------|

| 0x0   | OFF       | Event action disabled                      |

| 0x1   | RETRIGGER | Start, restart or retrigger TC on event    |

| 0x2   | COUNT     | Count on event                             |

| 0x3   | START     | Start TC on event                          |

| 0x4   | STAMP     | Time stamp capture                         |

| 0x5   | PPW       | Period captured in CC0, pulse width in CC1 |

| 0x6   | PWP       | Period captured in CC1, pulse width in CC0 |

| 0x7   | PW        | Pulse width capture                        |

- Gain Correction (GAINCORR)

- Offset Correction (OFFSETCORR)

When one of these registers is written, the data is stored in the corresponding buffer as long as the current conversion is not impacted, and the corresponding busy status will be set in the Synchronization Busy register (SYNCBUSY). When a new RESULT is available, data stored in the buffer registers will be transfered to the ADC and a new conversion can start.

#### 41.6.3.2 Device Temperature Measurement

#### Principle

The device has an integrated temperature sensor which is part of the Supply Controller (SUPC). The analog signal of that sensor can be converted into a digital value by the ADC. The digital value can be converted into a temperature in °C by following the steps in this section.

#### **Configuration and Conditions**

In order to conduct temperature measurements, configure the device according to these steps.

- 1. Configure the clocks and device frequencies according to the Electrical Characteristics chapters.

- 2. Configure the Voltage References System of the Supply Controller (SUPC):

- 2.1. Enable the temperature sensor by writing a '1' to the Temperature Sensor Enable bit in the VREF Control register (SUPC.VREF.TSEN).

- 2.2. Select the required voltage for the internal voltage reference INTREF by writing to the Voltage Reference Selection bits (SUPC.VREF.SEL). The required value can be found in the Electrical Characteristics chapters.

- 2.3. Enable routing INTREF to the ADC by writing a '1' to the Voltage Reference Output Enable bit (SUPC.VREF.VREFOE).

- 3. Configure the ADC:

- 3.1. Select the internal voltage reference INTREF as ADC reference voltage by writing to the Reference Control register (ADC.REFCTRL.REFSEL).

- 3.2. Select the temperature sensor vs. internal GND as input by writing TEMP and GND to the positive and negative MUX Input Selection bit fields (ADC.INPUTCTRL.MUXNEG and .MUXPOS, respectively).

- 3.3. Configure the remaining ADC parameters according to the Electrical Characteristics chapters.

- 3.4. Enable the ADC and acquire a value, ADC<sub>m</sub>.

#### Calculation Parameter Values

The temperature sensor behavior is linear, but it is sensitive to several parameters such as the internal voltage reference - which itself depends on the temperature. To take this into account, each device contains a Temperature Log row with individual calibration data measured and written during the production tests. These calibration values are read by software to infer the most accurate temperature readings possible.

The Temperature Log Row basically contains the following parameter set for two different temperatures ("ROOM" and "HOT"):

- Calibration temperatures in °C. One at room temperature *temp*<sub>R</sub>, one at a higher temperature *temp*<sub>H</sub>:

- ROOM\_TEMP\_VAL\_INT and ROOM\_TEMP\_VAL\_DEC contain the measured temperature at room insertion, *temp*<sub>R</sub>, in °C, separated in integer and decimal value.

#### 41.8.16 Offset Correction

| Name:     | OFFSETCORR                               |

|-----------|------------------------------------------|

| Offset:   | 0x14                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15              | 14  | 13  | 12  | 11  | 10      | 9         | 8   |

|--------|-----------------|-----|-----|-----|-----|---------|-----------|-----|

|        |                 |     |     |     |     | OFFSETC | ORR[11:8] |     |

| Access |                 |     |     |     | R/W | R/W     | R/W       | R/W |

| Reset  |                 |     |     |     | 0   | 0       | 0         | 0   |

|        |                 |     |     |     |     |         |           |     |

| Bit    | 7               | 6   | 5   | 4   | 3   | 2       | 1         | 0   |

|        | OFFSETCORR[7:0] |     |     |     |     |         |           |     |

| Access | R/W             | R/W | R/W | R/W | R/W | R/W     | R/W       | R/W |

| Reset  | 0               | 0   | 0   | 0   | 0   | 0       | 0         | 0   |

Bits 11:0 - OFFSETCORR[11:0] Offset Correction Value

If CTRLC.CORREN=1, these bits define how the ADC conversion result is compensated for offset error before being written to the Result register. This OFFSETCORR value is in two's complement format.

#### 43.8.3 Event Control

| Name:     | EVCTRL               |

|-----------|----------------------|

| Offset:   | 0x02                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1       | 0       |

|--------|---|---|---|---|---|-------|---------|---------|

|        |   |   |   |   |   | INVEI | EMPTYEO | STARTEI |

| Access |   |   |   |   |   | R/W   | R/W     | R/W     |

| Reset  |   |   |   |   |   | 0     | 0       | 0       |

**Bit 2 – INVEI** Enable Inversion Data Buffer Empty Event Output This bit defines the edge detection of the input event for STARTEI.

| Value | Description   |

|-------|---------------|

| 0     | Rising edge.  |

| 1     | Falling edge. |

#### Bit 1 – EMPTYEO Data Buffer Empty Event Output

This bit indicates whether or not the Data Buffer Empty event is enabled and will be generated when the Data Buffer register is empty.

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Data Buffer Empty event is disabled and will not be generated. |

| 1     | Data Buffer Empty event is enabled and will be generated.      |

#### Bit 0 – STARTEI Start Conversion Event Input

This bit indicates whether or not the Start Conversion event is enabled and data are loaded from the Data Buffer register to the Data register upon event reception.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | A new conversion will not be triggered on any incoming event. |

| 1     | A new conversion will be triggered on any incoming event.     |

### 43.8.9 Data Buffer

| Name:     | DATABUF            |

|-----------|--------------------|

| Offset:   | 0x0C               |

| Reset:    | 0x0000             |

| Property: | Write-Synchronized |

| 15            | 14          | 13                | 12                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                                                                                                                | 8                                                                                                                                                                                                                |

|---------------|-------------|-------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATABUF[15:8] |             |                   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                                                  |

| W             | W           | W                 | W                       | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W                                                                                                                                                                                | W                                                                                                                                                                                                                |

| 0             | 0           | 0                 | 0                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                | 0                                                                                                                                                                                                                |

|               |             |                   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                                                  |

| 7             | 6           | 5                 | 4                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                | 0                                                                                                                                                                                                                |

| DATABUF[7:0]  |             |                   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                                                  |

| W             | W           | W                 | W                       | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W                                                                                                                                                                                | W                                                                                                                                                                                                                |

| 0             | 0           | 0                 | 0                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                | 0                                                                                                                                                                                                                |

|               | W<br>0<br>7 | W W<br>0 0<br>7 6 | W W W<br>0 0 0<br>7 6 5 | DATABI           W         W         W         W         O         O         O         O         O         O         O         DATABI         DATABIA         DATABIA | W         W         W         W         W         W         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O | DATABUF[15:8]         W       W       W       W       W         0       0       0       0       0       0         7       6       5       4       3       2         DATABUF[7:0] | DATABUF[15:8]         W       W       W       W       W       W         0       0       0       0       0       0       0       0         7       6       5       4       3       2       1         DATABUF[7:0] |

# Bits 15:0 - DATABUF[15:0] Data Buffer

DATABUF contains the value to be transferred into DATA register.

# 44.6 Functional Description

#### 44.6.1 Principle of Operation

Each OPAMP has one positive and one negative input. Each input may be chosen from either a selection of analog input pins, or internal inputs such as the DAC, the resistor ladder, and the ground and output of another OPAMP.

Each OPAMP can be configured with built-in feedback to support various functions with programmable or unity gain.

I/O pins are externally accessible so that the operational amplifier can be configured with external feedback.

All OPAMPs can be cascaded to support circuits such as differential amplifiers.

#### 44.6.2 Basic Operation

Each operational amplifier can be configured in different modes, selected by the OPAMP Control x register (OPAMPCTRLx):

- Standalone operational amplifier

- Operational amplifier with built-in feedback

After being enabled, a start-up delay is added before the output of the operational amplifier is available. This start-up time is measured internally to account for environmental changes such as temperature or voltage supply level.

When the OPAMP is ready, the respective Ready x bit in the Status register is set (STATUS.READYx=1).

If the supply voltage is below 2.5V, the start-up time is also dependent on the voltage doubler. If the supply voltage is always above 2.5V, the voltage doubler can be disabled by setting the Low-Power Mux bit in the Control A Register (CTRLA.LPMUX).

#### 44.6.2.1 Initialization

The OPAMP must be configured with the desired properties and inputs before it is enabled.

The asynchronous clocks CLK\_ULP32K must be configured in the OSC32KCTRL module before enabling individual OPAMPs. See OSC32KCTRL – 32KHz Oscillators Controller for further details.

#### **Related Links**

24. OSC32KCTRL - 32KHz Oscillators Controller

#### 44.6.2.2 Enabling, Disabling, and Resetting

The OPAMP is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The OPAMP is disabled by writing a '0' to CTRLA.ENABLE.

Each OPAMP sub-module is enabled by writing a '1' to the Enable bit in the OPAMP Control x register (OPAMPCTRLx.ENABLE). Each OPAMP sub-module is disabled by writing a '0' to OPAMPCTRLx.ENABLE.

The OPAMP module is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the OPAMP will be reset to their initial state, and the OPAMP will be disabled. Refer to 44.8.1 CTRLA for details.

#### 44.6.3 DMA Operation

Not applicable.