# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e15a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 16.12.13 CoreSight ROM Table Entry 0

| ENTRY0               |

|----------------------|

| 0x1000               |

| 0xXXXXX00X           |

| PAC Write-Protection |

|                      |

| Bit    | 31 | 30   | 29      | 28    | 27       | 26 | 25  | 24    |

|--------|----|------|---------|-------|----------|----|-----|-------|

|        |    |      |         | ADDOF | F[19:12] |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | x  | x    | x       | x     | x        | x  | x   | x     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 23 | 22   | 21      | 20    | 19       | 18 | 17  | 16    |

|        |    |      |         | ADDO  | FF[11:4] |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | x  | х    | х       | х     | х        | х  | x   | х     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 15 | 14   | 13      | 12    | 11       | 10 | 9   | 8     |

|        |    | ADDO | FF[3:0] |       |          |    |     |       |

| Access | R  | R    | R       | R     |          |    |     |       |

| Reset  | х  | х    | x       | х     |          |    |     |       |

|        |    |      |         |       |          |    |     |       |

| Bit    | 7  | 6    | 5       | 4     | 3        | 2  | 1   | 0     |

|        |    |      |         |       |          |    | FMT | EPRES |

| Access |    |      |         |       |          |    | R   | R     |

| Reset  |    |      |         |       |          |    | 1   | x     |

|        |    |      |         |       |          |    |     |       |

#### Bits 31:12 - ADDOFF[19:0] Address Offset

The base address of the component, relative to the base address of this ROM table.

#### Bit 1 – FMT Format

Always reads as '1', indicating a 32-bit ROM table.

## Bit 0 – EPRES Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

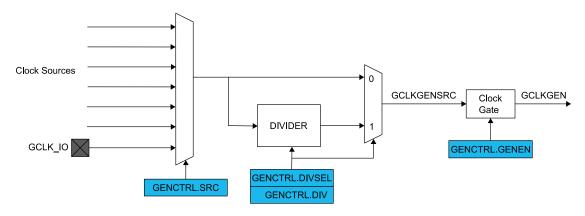

## Figure 18-3. Generic Clock Generator

#### **Related Links**

19. MCLK – Main Clock

#### 18.6.2.4 Enabling a Generator

A Generator is enabled by writing a '1' to the Generator Enable bit in the Generator Control register (GENCTRLn.GENEN=1).

## 18.6.2.5 Disabling a Generator

A Generator is disabled by writing a '0' to GENCTRLn.GENEN. When GENCTRLn.GENEN=0, the GCLK\_GEN[n] clock is disabled and gated.

#### 18.6.2.6 Selecting a Clock Source for the Generator

Each Generator can individually select a clock source by setting the Source Select bit group in the Generator Control register (GENCTRLn.SRC).

Changing from one clock source, for example A, to another clock source, B, can be done on the fly: If clock source B is not ready, the Generator will continue using clock source A. As soon as source B is ready, the Generator will switch to it. During the switching operation, the Generator maintains clock requests to both clock sources A and B, and will release source A as soon as the switch is done. The according bit in SYNCBUSY register (SYNCBUSY.GENCTRLn) will remain '1' until the switch operation is completed.

The available clock sources are device dependent (usually the oscillators, RC oscillators, DPLL, and DFLLULP). Only Generator 1 can be used as a common source for all other generators.

#### 18.6.2.7 Changing the Clock Frequency

The selected source for a Generator can be divided by writing a division value in the Division Factor bit field of the Generator Control register (GENCTRLn.DIV). How the actual division factor is calculated is depending on the Divide Selection bit (GENCTRLn.DIVSEL).

If GENCTRLn.DIVSEL=0 and GENCTRLn.DIV is either 0 or 1, the output clock will be undivided.

Note: The number of available DIV bits may vary from Generator to Generator.

#### 18.6.2.8 Duty Cycle

When dividing a clock with an odd division factor, the duty-cycle will not be 50/50. Setting the Improve Duty Cycle bit of the Generator Control register (GENCTRLn.IDC) will result in a 50/50 duty cycle.

## 18.6.2.9 External Clock

The output clock (GCLK\_GEN) of each Generator can be sent to I/O pins (GCLK\_IO).

The STATUS.VCORERDY bit is set to '1' as soon as the VDDCORE voltage has reached the target voltage. During voltage transition, STATUS.VCORERDY will read '0'. The Voltage Ready interrupt (VCORERDY) can be used to detect a 0-to-1 transition of STATUS.VCORERDY, see also 25.6.4 Interrupts.

When entering the Standby Sleep mode and when no sleepwalking task is requested, the VDDCORE Voltage scaling control is not used.

## 25.6.1.5 Sleep Mode Operation

In Standby mode, the low-power voltage regulator (LPVREG) is used to supply VDDCORE.

When the Run in Standby bit in the VREG register (VREG.RUNSTDBY) is written to '1', VDDCORE is supplied by the main voltage regulator. Depending on the Standby in PL0 bit in the Voltage Regulator register (VREG.STDBYPL0), the VDDCORE level is either set to the PL0 voltage level, or remains in the current performance level.

| Table 25-1 | VDDCORE | Level in | Standby | / Mode |

|------------|---------|----------|---------|--------|

|------------|---------|----------|---------|--------|

| VREG.RUNSTDBY | VREG.STDBYPL0 | VDDCORE Supply in Standby Mode                       |

|---------------|---------------|------------------------------------------------------|

| 0             | -             | LPVREG                                               |

| 1             | 0             | MAINVREG in current performance level <sup>(1)</sup> |

| 1             | 1             | MAINVREG in PL0                                      |

## Note:

When the device is in PL0 but VREG.STDBYPL0=0, the MAINVREG is operating in normal power mode. To minimize power consumption, operate MAINVREG in PL0 mode by selecting VREG.STDBYPL0=1.

By writing the Low-Power mode Efficiency bit in the VREG register (VREG.LPEFF) to '1', the efficiency of the regulator in LPVREG can be improved when the application uses a limited VDD range (2.5 to 3.63V). It is also possible to use the BOD33 in order to monitor the VDD and change this LPEFF value on the fly according to VDD level.

## **Related Links**

22.6.3.3 Sleep Mode Controller

## 25.6.2 Voltage Reference System Operation

The reference voltages are generated by a functional block DETREF inside of the SUPC. DETREF is providing a fixed-voltage source, BANDGAP=1.1V, and a variable voltage, INTREF.

## 25.6.2.1 Initialization

The voltage reference output and the temperature sensor are disabled after any Reset.

## 25.6.2.2 Enabling, Disabling, and Resetting

The voltage reference output is enabled/disabled by setting/clearing the Voltage Reference Output Enable bit in the Voltage Reference register (VREF.VREFOE).

The temperature sensor is enabled/disabled by setting/clearing the Temperature Sensor Enable bit in the Voltage Reference register (VREF.TSEN).

**Note:** When VREF.ONDEMAND=0, it is not recommended to enable both voltage reference output and temperature sensor at the same time - only the voltage reference output will be present at both ADC inputs.

| (     | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x06<br>0x00<br>N/A |   |   |   |   |   |     |

|-------|-----------------------------------------|--------------------------------|---|---|---|---|---|-----|

| Bit   | 7                                       | 6                              | 5 | 4 | 3 | 2 | 1 | 0   |

| l     |                                         |                                |   |   |   |   |   | EW  |

| cess  |                                         |                                |   |   |   |   |   | R/W |

| Reset |                                         |                                |   |   |   |   |   | 0   |

This flag is cleared by writing a '1' to it.

Interrupt Flag Status and Clear

26.8.6

This hag is cleared by whiling a T to it.

This flag is set when an Early Warning interrupt occurs, as defined by the EWOFFSET bit group in EWCTRL.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Early Warning interrupt flag.

# 27.8.14 Timestamp

| Name:     | TIMESTAMP |

|-----------|-----------|

| Offset:   | 0x64      |

| Reset:    | 0x0       |

| Property: | Read-Only |

| Bit    | 31 | 30          | 29 | 28   | 27       | 26 | 25 | 24 |

|--------|----|-------------|----|------|----------|----|----|----|

|        |    |             |    | COUN | [31:24]  |    |    |    |

| Access | RO | RO          | RO | RO   | RO       | RO | RO | RO |

| Reset  | 0  | 0           | 0  | 0    | 0        | 0  | 0  | 0  |

|        |    |             |    |      |          |    |    |    |

| Bit    | 23 | 22          | 21 | 20   | 19       | 18 | 17 | 16 |

|        |    |             |    | COUN | Г[23:16] |    |    |    |

| Access | RO | RO          | RO | RO   | RO       | RO | RO | RO |

| Reset  | 0  | 0           | 0  | 0    | 0        | 0  | 0  | 0  |

|        |    |             |    |      |          |    |    |    |

| Bit    | 15 | 14          | 13 | 12   | 11       | 10 | 9  | 8  |

|        |    | COUNT[15:8] |    |      |          |    |    |    |

| Access | RO | RO          | RO | RO   | RO       | RO | RO | RO |

| Reset  | 0  | 0           | 0  | 0    | 0        | 0  | 0  | 0  |

|        |    |             |    |      |          |    |    |    |

| Bit    | 7  | 6           | 5  | 4    | 3        | 2  | 1  | 0  |

|        |    |             |    | COUN | IT[7:0]  |    |    |    |

| Access | RO | RO          | RO | RO   | RO       | RO | RO | RO |

| Reset  | 0  | 0           | 0  | 0    | 0        | 0  | 0  | 0  |

|        |    |             |    |      |          |    |    |    |

Bits 31:0 - COUNT[31:0] Count Timestamp Value

The 32-bit value of COUNT is captured by the TIMESTAMP when a tamper condition occurs

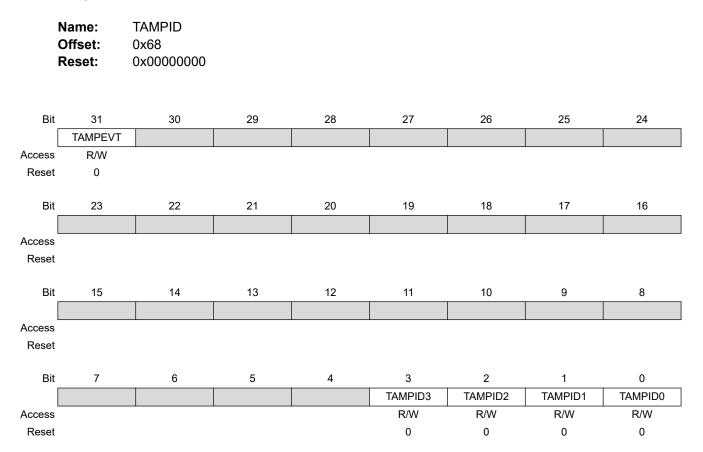

## 27.8.15 Tamper ID

#### Bit 31 – TAMPEVT Tamper Event Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Valu | Description                                |  |

|------|--------------------------------------------|--|

| 0    | A tamper input event has not been detected |  |

| 1    | A tamper input event has been detected     |  |

#### Bits 0, 1, 2, 3 - TAMPID Tamper on Channel n Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | A tamper condition has not been detected on Channel n |

| 1     | A tamper condition has been detected on Channel n     |

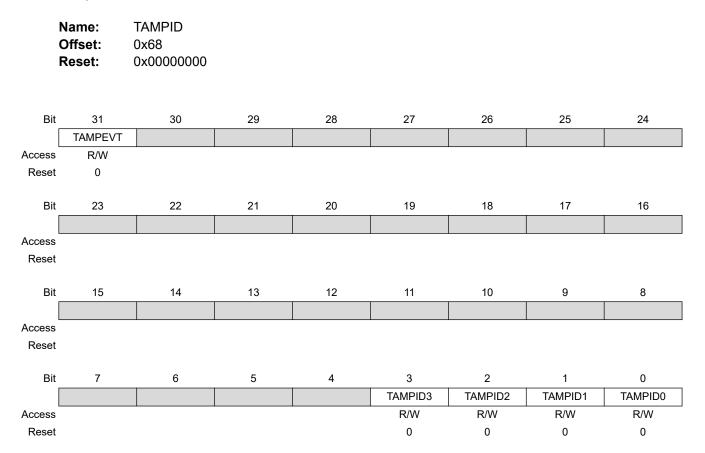

## 27.10.16 Tamper ID

#### Bit 31 – TAMPEVT Tamper Event Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | A tamper input event has not been detected |

| 1     | A tamper input event has been detected     |

#### Bits 0, 1, 2, 3 - TAMPID Tamper on Channel n Detected

Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the tamper detection bit.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | A tamper condition has not been detected on Channel n |

| 1     | A tamper condition has been detected on Channel n     |

## 27.12.5 Interrupt Enable Set in Clock/Calendar mode (CTRLA.MODE=2)

Name:INTENSETOffset:0x0AReset:0x0000Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| Bit    | 15   | 14     | 13   | 12   | 11   | 10   | 9    | 8      |

|--------|------|--------|------|------|------|------|------|--------|

|        | OVF  | TAMPER |      |      |      |      |      | ALARM0 |

| Access | R/W  | R/W    |      |      |      |      |      | R/W    |

| Reset  | 0    | 0      |      |      |      |      |      | 0      |

|        |      |        |      |      |      |      |      |        |

| Bit    | 7    | 6      | 5    | 4    | 3    | 2    | 1    | 0      |

|        | PER7 | PER6   | PER5 | PER4 | PER3 | PER2 | PER1 | PER0   |

| Access | R/W  | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W    |

| Reset  | 0    | 0      | 0    | 0    | 0    | 0    | 0    | 0      |

## Bit 15 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### **Bit 14 – TAMPER** Tamper Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Tamper Interrupt Enable bit, which enables the Tamper interrupt.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The Tamper interrupt it disabled. |

| 1     | The Tamper interrupt is enabled.  |

#### Bit 8 – ALARMO Alarm 0 Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Alarm 0 Interrupt Enable bit, which enables the Alarm 0 interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Alarm 0 interrupt is disabled. |

| 1     | The Alarm 0 interrupt is enabled.  |

#### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PERn Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Periodic Interval n Interrupt Enable bit, which enables the Periodic Interval n interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

- The transfer descriptor must be made valid by writing a one to the Valid bit in the Block Transfer Control register (BTCTRL.VALID)

- Number of beats in the block transfer must be selected by writing the Block Transfer Count (BTCNT) register

- Source address for the block transfer must be selected by writing the Block Transfer Source Address (SRCADDR) register

- Destination address for the block transfer must be selected by writing the Block Transfer Destination Address (DSTADDR) register

If CRC calculation is needed, the CRC engine must be configured before it is enabled, as outlined by the following steps:

- The CRC input source must selected by writing the CRC Input Source bit group in the CRC Control register (CRCCTRL.CRCSRC)

- The type of CRC calculation must be selected by writing the CRC Polynomial Type bit group in the CRC Control register (CRCCTRL.CRCPOLY)

- If I/O is selected as input source, the beat size must be selected by writing the CRC Beat Size bit group in the CRC Control register (CRCCTRL.CRCBEATSIZE)

## 28.6.2.2 Enabling, Disabling, and Resetting

The DMAC is enabled by writing the DMA Enable bit in the Control register (CTRL.DMAENABLE) to '1'. The DMAC is disabled by writing a '0' to CTRL.DMAENABLE.

A DMA channel is enabled by writing the Enable bit in the Channel Control A register (CHCTRLA.ENABLE) to '1', after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). A DMA channel is disabled by writing a '0' to CHCTRLA.ENABLE.

The CRC is enabled by writing a '1' to the CRC Enable bit in the Control register (CTRL.CRCENABLE). The CRC is disabled by writing a '0' to CTRL.CRCENABLE.

The DMAC is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST) while the DMAC and CRC are disabled. All registers in the DMAC except DBGCTRL will be reset to their initial state.

A DMA channel is reset by writing a '1' to the Software Reset bit in the Channel Control A register (CHCTRLA.SWRST), after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). The channel registers will be reset to their initial state. The corresponding DMA channel must be disabled in order for the reset to take effect.

## 28.6.2.3 Transfer Descriptors

Together with the channel configurations the transfer descriptors decides how a block transfer should be executed. Before a DMA channel is enabled (CHCTRLA.ENABLE is written to one), and receives a transfer trigger, its first transfer descriptor has to be initialized and valid (BTCTRL.VALID). The first transfer descriptor describes the first block transfer of a transaction.

All transfer descriptors must reside in SRAM. The addresses stored in the Descriptor Memory Section Base Address (BASEADDR) and Write-Back Memory Section Base Address (WRBADDR) registers tell the DMAC where to find the descriptor memory section and the write-back memory section.

The descriptor memory section is where the DMAC expects to find the first transfer descriptors for all DMA channels. As BASEADDR points only to the first transfer descriptor of channel 0 (see figure below), all first transfer descriptors must be stored in a contiguous memory section, where the transfer descriptors must be ordered according to their channel number. For further details on linked descriptors, refer to 28.6.3.1 Linked Descriptors.

#### 28.8.14 Active Channel and Levels

|        | Name:<br>Offset:<br>Reset:<br>Property: | ACTIVE<br>0x30<br>0x00000000<br>- |    |      |        |         |        |        |

|--------|-----------------------------------------|-----------------------------------|----|------|--------|---------|--------|--------|

| Bit    | 31                                      | 30                                | 29 | 28   | 27     | 26      | 25     | 24     |

|        |                                         |                                   |    | BTCN | [15:8] |         |        |        |

| Access | R                                       | R                                 | R  | R    | R      | R       | R      | R      |

| Reset  | 0                                       | 0                                 | 0  | 0    | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |      |        |         |        |        |

| Bit    | 23                                      | 22                                | 21 | 20   | 19     | 18      | 17     | 16     |

|        |                                         |                                   |    | BTCN | T[7:0] |         |        |        |

| Access | R                                       | R                                 | R  | R    | R      | R       | R      | R      |

| Reset  | 0                                       | 0                                 | 0  | 0    | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |      |        |         |        |        |

| Bit    |                                         | 14                                | 13 | 12   | 11     | 10      | 9      | 8      |

|        | ABUSY                                   |                                   |    |      |        | ID[4:0] |        |        |

| Access | R                                       |                                   |    | R    | R      | R       | R      | R      |

| Reset  | 0                                       |                                   |    | 0    | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |      |        |         |        |        |

| Bit    | 7                                       | 6                                 | 5  | 4    | 3      | 2       | 1      | 0      |

|        |                                         |                                   |    |      | LVLEXx | LVLEXx  | LVLEXx | LVLEXx |

| Access |                                         |                                   |    |      | R      | R       | R      | R      |

| Reset  |                                         |                                   |    |      | 0      | 0       | 0      | 0      |

## Bits 31:16 - BTCNT[15:0] Active Channel Block Transfer Count

These bits hold the 16-bit block transfer count of the ongoing transfer. This value is stored in the active channel and written back in the corresponding Write-Back channel memory location when the arbiter grants a new channel access. The value is valid only when the active channel active busy flag (ABUSY) is set.

#### Bit 15 - ABUSY Active Channel Busy

This bit is cleared when the active transfer count is written back in the write-back memory section.

This bit is set when the next descriptor transfer count is read from the write-back memory section.

## Bits 12:8 - ID[4:0] Active Channel ID

These bits hold the channel index currently stored in the active channel registers. The value is updated each time the arbiter grants a new channel transfer access request.

## Bits 3,2,1,0 – LVLEXx Level x Channel Trigger Request Executing [x=3..0]

This bit is set when a level-x channel trigger request is executing or pending.

This bit is cleared when no request is pending or being executed.

| Property: |     | PAC Write-Pre | otection, Ena | ble-Protected |          |          |     |     |

|-----------|-----|---------------|---------------|---------------|----------|----------|-----|-----|

|           |     |               |               |               |          |          |     |     |

|           |     |               |               |               |          |          |     |     |

| Bit       | 31  | 30            | 29            | 28            | 27       | 26       | 25  | 24  |

|           |     |               |               |               |          |          |     |     |

| Access    |     |               |               |               |          |          |     |     |

| Reset     |     |               |               |               |          |          |     |     |

|           |     |               |               |               |          |          |     |     |

| Bit       | 23  | 22            | 21            | 20            | 19       | 18       | 17  | 16  |

|           |     |               |               |               |          |          |     |     |

| Access    |     | ·             |               |               |          | -        |     |     |

| Reset     |     |               |               |               |          |          |     |     |

|           |     |               |               |               |          |          |     |     |

| Bit       | 15  | 14            | 13            | 12            | 11       | 10       | 9   | 8   |

|           |     |               |               |               | WRBAD    | DR[13:8] |     |     |

| Access    |     | ŀ             | R/W           | R/W           | R/W      | R/W      | R/W | R/W |

| Reset     |     |               | 0             | 0             | 0        | 0        | 0   | 0   |

|           |     |               |               |               |          |          |     |     |

| Bit       | 7   | 6             | 5             | 4             | 3        | 2        | 1   | 0   |

|           |     |               |               | WRBAD         | DDR[7:0] |          |     |     |

| Access    | R/W | R/W           | R/W           | R/W           | R/W      | R/W      | R/W | R/W |

| Reset     | 0   | 0             | 0             | 0             | 0        | 0        | 0   | 0   |

## 28.8.16 Write-Back Memory Section Base Address

0x38

WRBADDR

0x00000000

Name:

Offset:

Reset:

**Bits 13:0 – WRBADDR[13:0]** Write-Back Memory Base Address These bits store the Write-Back memory base address. The value must be 128-bit aligned.

#### 29.8.11 Debouncer Enable

| Name:     | DEBOUNCEN                                          |

|-----------|----------------------------------------------------|

| Offset:   | 0x30                                               |

| Reset:    | 0x0000000                                          |

| Property: | PAC Write-Protection, Enable-Protected, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the external interrupt x (EXTINTx) is set as Non-Secure in the NONSEC register (NONSEC.EXTINTx bit). Some restrictions apply for the Non-Secure accesses to an Enabled-Protected register as it will not be possible for the Non-Secure to configure it once this register is enabled by the Secure application. This will require some veneers to be implemented on Secure side.

| Bit    | 31        | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|        |           |           |           |           |           |           |           |           |

| Access |           |           |           |           |           |           |           |           |

| Reset  |           |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |           |           |           |           |           |           |           |           |

| Access |           |           |           |           |           |           |           |           |

| Reset  |           |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 15        | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

|        |           |           |           |           |           |           |           |           |

| Access |           |           |           |           |           |           |           |           |

| Reset  |           |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|        |           |           |           | DEBOUN    | ICEN[7:0] |           |           |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

## Bits 7:0 – DEBOUNCEN[7:0] Debouncer Enable

The bit x of DEBOUNCEN set the Debounce mode for the interrupt associated with the EXTINTx pin.

| Valu | e Description                             |

|------|-------------------------------------------|

| 0    | The EXTINT x edge input is not debounced. |

| 1    | The EXTINT x edge input is debounced.     |

# 32.7 Register Summary

## Important:

For SAM L11, the PORT register map is automatically duplicated in a Secure and Non-Secure alias:

- The Non-Secure alias is at the peripheral base address

- The Secure alias is located at the peripheral base address + 0x200

Refer to Mix-Secure Peripherals for more information on register access rights

| Offset | Name     | Bit Pos. |               |

|--------|----------|----------|---------------|

|        |          | 7:0      | DIR[7:0]      |

| 000    | DIR      | 15:8     | DIR[15:8]     |

| 0x00   |          | 23:16    | DIR[23:16]    |

|        |          | 31:24    | DIR[31:24]    |

|        |          | 7:0      | DIRCLR[7:0]   |

| 004    |          | 15:8     | DIRCLR[15:8]  |

| 0x04   | DIRCLR   | 23:16    | DIRCLR[23:16] |

|        |          | 31:24    | DIRCLR[31:24] |

|        |          | 7:0      | DIRSET[7:0]   |

|        | DIDOFT   | 15:8     | DIRSET[15:8]  |

| 0x08   | DIRSET   | 23:16    | DIRSET[23:16] |

|        |          | 31:24    | DIRSET[31:24] |

|        |          | 7:0      | DIRTGL[7:0]   |

|        | DIRTGL   | 15:8     | DIRTGL[15:8]  |

| 0x0C   |          | 23:16    | DIRTGL[23:16] |

|        |          | 31:24    | DIRTGL[31:24] |

|        | OUT      | 7:0      | OUT[7:0]      |

|        |          | 15:8     | OUT[15:8]     |

| 0x10   |          | 23:16    | OUT[23:16]    |

|        |          | 31:24    | OUT[31:24]    |

|        |          | 7:0      | OUTCLR[7:0]   |

|        |          | 15:8     | OUTCLR[15:8]  |

| 0x14   | OUTCLR   | 23:16    | OUTCLR[23:16] |

|        |          | 31:24    | OUTCLR[31:24] |

|        |          | 7:0      | OUTSET[7:0]   |

|        |          | 15:8     | OUTSET[15:8]  |

| 0x18   | OUTSET   | 23:16    | OUTSET[23:16] |

|        |          | 31:24    | OUTSET[31:24] |

|        |          | 7:0      | OUTTGL[7:0]   |

|        | 0.177.01 | 15:8     | OUTTGL[15:8]  |

| 0x1C   | OUTTGL   | 23:16    | OUTTGL[23:16] |

|        |          | 31:24    | OUTTGL[31:24] |

|        |          | 7:0      | IN[7:0]       |

| 0x20   | IN       | 15:8     | IN[15:8]      |

|        |          | 23:16    | IN[23:16]     |

## Bit 17 – INEN Input Enable

This bit determines the new value written to PINCFGy.INEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

## Bit 16 – PMUXEN Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

## Bits 15:0 – PINMASK[15:0] Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

## These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

## 37.8.8 Address

| Name:     | ADDR                                   |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31       | 30  | 29  | 28            | 27  | 26  | 25           | 24         |

|--------|----------|-----|-----|---------------|-----|-----|--------------|------------|

|        |          |     |     |               |     |     | ADDRMASK[9:7 | <b>'</b> ] |

| Access |          |     |     | •             |     | R/W | R/W          | R/W        |

| Reset  |          |     |     |               |     | 0   | 0            | 0          |

|        |          |     |     |               |     |     |              |            |

| Bit    | 23       | 22  | 21  | 20            | 19  | 18  | 17           | 16         |

|        |          |     |     | ADDRMASK[6:0] |     |     |              |            |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W | R/W          |            |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0   | 0            |            |

|        |          |     |     |               |     |     |              |            |

| Bit    | 15       | 14  | 13  | 12            | 11  | 10  | 9            | 8          |

|        | TENBITEN |     |     |               |     |     | ADDR[9:7]    |            |

| Access | R/W      |     |     |               |     | R/W | R/W          | R/W        |

| Reset  | 0        |     |     |               |     | 0   | 0            | 0          |

|        |          |     |     |               |     |     |              |            |

| Bit    | 7        | 6   | 5   | 4             | 3   | 2   | 1            | 0          |

|        |          |     |     | ADDR[6:0]     |     |     |              | GENCEN     |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W | R/W          | R/W        |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0   | 0            | 0          |

|        |          |     |     |               |     |     |              |            |

## Bits 26:17 – ADDRMASK[9:0] Address Mask

These bits act as a second address match register, an address mask register or the lower limit of an address range, depending on the CTRLB.AMODE setting.

## **Bit 15 – TENBITEN** Ten Bit Addressing Enable

| Value | Description                          |

|-------|--------------------------------------|

| 0     | 10-bit address recognition disabled. |

| 1     | 10-bit address recognition enabled.  |

#### Bits 10:1 - ADDR[9:0] Address

These bits contain the I<sup>2</sup>C slave address used by the slave address match logic to determine if a master has addressed the slave.

When using 7-bit addressing, the slave address is represented by ADDR[6:0].

When using 10-bit addressing (ADDR.TENBITEN=1), the slave address is represented by ADDR[9:0]

When the address match logic detects a match, INTFLAG.AMATCH is set and STATUS.DIR is updated to indicate whether it is a read or a write transaction.

#### Bit 0 – GENCEN General Call Address Enable

A general call address is an address consisting of all-zeroes, including the direction bit (master write).

© 2018 Microchip Technology Inc.

## 38.7.1.16 Period Buffer Value, 8-bit Mode

Name:PERBUFOffset:0x2FReset:0xFFProperty:Write-Synchronized

| Bit    | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|

|        | PERBUF[7:0] |     |     |     |     |     |     |     |

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

## Bits 7:0 – PERBUF[7:0] Period Buffer Value

These bits hold the value of the period buffer register. The value is copied to PER register on UPDATE condition.

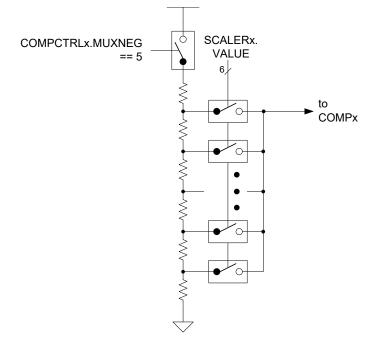

## Figure 42-5. VDD Scaler

## 42.6.6 Input Hysteresis

Application software can selectively enable/disable hysteresis for the comparison. Applying hysteresis will help prevent constant toggling of the output, which can be caused by noise when the input signals are close to each other.

Hysteresis is enabled for each comparator individually by the Hysteresis Enable bit in the Comparator x Control register (COMPCTRLx.HYSTEN). Furthermore, when enabled, the level of hysteresis is programmable through the Hysteresis Level bits also in the Comparator x Control register (COMPCTRLx.HYST). Hysteresis is available only in continuous mode (COMPCTRLx.SINGLE=0).

## 42.6.7 Propagation Delay vs. Power Consumption

It is possible to trade off comparison speed for power efficiency to get the shortest possible propagation delay or the lowest power consumption. The speed setting is configured for each comparator individually by the Speed bit group in the Comparator x Control register (COMPCTRLx.SPEED). The Speed bits select the amount of bias current provided to the comparator, and as such will also affect the start-up time.

## 42.6.8 Filtering

The output of the comparators can be filtered digitally to reduce noise. The filtering is determined by the Filter Length bits in the Comparator Control x register (COMPCTRLx.FLEN), and is independent for each comparator. Filtering is selectable from none, 3-bit majority (N=3) or 5-bit majority (N=5) functions. Any change in the comparator output is considered valid only if N/2+1 out of the last N samples agree. The filter sampling rate is the GCLK\_AC frequency.

Note that filtering creates an additional delay of N-1 sampling cycles from when a comparison is started until the comparator output is validated. For continuous mode, the first valid output will occur when the required number of filter samples is taken. Subsequent outputs will be generated every cycle based on the current sample plus the previous N-1 samples, as shown in Figure 42-6. For single-shot mode, the comparison completes after the Nth filter sample, as shown in Figure 42-7.

© 2018 Microchip Technology Inc.

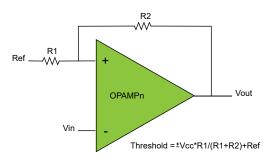

## Figure 44-11. Inverting comparator with programmable hysteresis

To configure an OPAMP as a non-inverting comparator with programmable hysteresis, the OPAMPCTRLx register can be configured as follows:

Table 44-17. Configuration of Input Multiplexes for OPAMP0 and OPAMP1 (Example: Vth = 1/3\*Vcc, Ref = Gnd)

|        | MUXPOS | MUXNEG | RES1MUX | ΡΟΤΜUΧ | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| OPAMP1 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| OPAMP2 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| Value | R1  | R2  | Threshold = Vcc * R1 / R2 |

|-------|-----|-----|---------------------------|

| 0x0   | 14R | 2R  | Vcc * 7 (unused)          |

| 0x1   | 12R | 4R  | Vcc * 3 (unused)          |

| 0x2   | 8R  | 8R  | Vcc (unused)              |

| 0x3   | 6R  | 10R | 0.6* Vcc                  |

| 0x4   | 4R  | 12R | 1/3 * Vcc                 |

| 0x5   | 3R  | 13R | 3/13 *Vcc                 |

| 0x6   | 2R  | 14R | 1/7 * Vcc                 |

| 0x7   | R   | 15R | 1/15 * Vcc                |

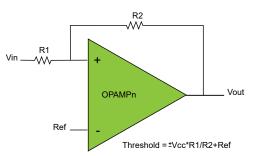

## Figure 44-12. Non-Inverting comparator with programmable hysteresis

2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

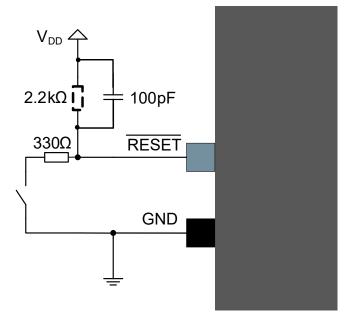

## 50.4 External Reset Circuit

The external Reset circuit is connected to the RESET pin when the external Reset function is used. The circuit is not necessary when the RESET pin is not driven LOW externally by the application circuitry.

The reset switch can also be removed, if a manual reset is not desired. The RESET pin itself has an internal pull-up resistor, hence it is optional to add any external pull-up resistor.

#### Figure 50-5. External Reset Circuit Schematic

A pull-up resistor makes sure that the reset does not go low and unintentionally causing a device reset. An additional resistor has been added in series with the switch to safely discharge the filtering capacitor, i.e. preventing a current surge when shorting the filtering capacitor which again can cause a noise spike that can have a negative effect on the system.

|  | Table 50-3. | Reset | Circuit | Connections |

|--|-------------|-------|---------|-------------|

|--|-------------|-------|---------|-------------|

| Signal Name | Recommended Pin Connection                                                           | Description |

|-------------|--------------------------------------------------------------------------------------|-------------|

| RESET       | Reset low level threshold voltage $V_{DDIO}$ = 1.62V - 2.0V: Below 0.33 * $V_{DDIO}$ | Reset pin   |

|             | V <sub>DDIO</sub> = 2.7V - 3.63V: Below 0.36 * V <sub>DDIO</sub>                     |             |

|             | Decoupling/filter capacitor 100pF <sup>(1)</sup>                                     |             |

|             | Pull-up resistor 2.2k $\Omega^{(1,2)}$                                               |             |

|             | Resistor in series with the switch $330\Omega^{(1)}$                                 |             |

1. These values are only given as a typical example.

2. The SAM L10/L11 features an internal pull-up resistor on the RESET pin, hence an external pull-up is optional.

## 50.5 Unused or Unconnected Pins

For unused pins the default state of the pins will give the lowest current leakage. Thus there is no need to do any configuration of the unused pins in order to lower the power consumption.

## 50.6 Clocks and Crystal Oscillators

The SAM L10/L11 can be run from internal or external clock sources, or a mix of internal and external sources. An example of usage can be to use the internal 16MHz oscillator as source for the system clock and an external 32.768kHz watch crystal as clock source for the Real-Time counter (RTC).

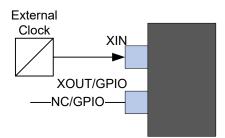

## 50.6.1 External Clock Source

## Figure 50-6. External Clock Source Schematic

## Table 50-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    | NC/GPIO                            |

## 50.6.2 Crystal Oscillator

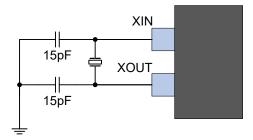

## Figure 50-7. Crystal Oscillator Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause too high load to operate the crystal, and cause crosstalk to other parts of the system.

Table 50-5.

Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 32MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |