# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e15a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

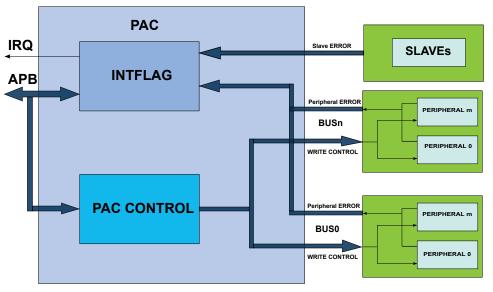

## 15. PAC - Peripheral Access Controller

## 15.1 Overview

The Peripheral Access Controller provides an interface for the locking and unlocking and for managing security attribution of peripheral registers within the device. It reports all violations that could happen when accessing a peripheral: write protected access, illegal access, enable protected access, access when clock synchronization or software reset is on-going. These errors are reported in a unique interrupt flag for a peripheral. The PAC module also reports errors occurring at the slave bus level, when an access to a non-existing address is detected.

## 15.2 Features

- Manages write protection access and reports access errors for the peripheral modules or bridges.

- Manages security attribution for the peripheral modules (SAM L11)

## 15.3 Block Diagram

## Figure 15-1. PAC Block Diagram

## **15.4 Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 15.4.1 IO Lines

Not applicable.

## 15.4.2 Power Management

The PAC can continue to operate in any Sleep mode where the selected source clock is running. The PAC interrupts can be used to wake up the device from Sleep modes. The events can trigger other operations in the system without exiting sleep modes.

## **OSCCTRL – Oscillators Controller**

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The DFLLULP Ready interrupt is disabled.                                                |

| 1     | The DFLLULP Ready interrupt is enabled, and an interrupt request will be generated when |

|       | the DFLLULP Ready Interrupt flag is set.                                                |

### **Bit 4 – OSC16MRDY** OSC16M Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the OSC16M Ready Interrupt Enable bit, which disables the OSC16M Ready interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The OSC16M Ready interrupt is disabled.                                                |

| 1     | The OSC16M Ready interrupt is enabled, and an interrupt request will be generated when |

|       | the OSC16M Ready Interrupt flag is set.                                                |

Bit 1 – CLKFAIL Clock Failure Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the XOSC Clock Failure Interrupt Enable bit, which disables the XOSC Clock Failure interrupt.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The XOSC Clock Failure interrupt is disabled.                                           |

| 1     | The XOSC Clock Failure interrupt is enabled, and an interrupt request will be generated |

|       | when the XOSC Clock Failure Interrupt flag is set.                                      |

#### **Bit 0 – XOSCRDY** XOSC Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the XOSC Ready Interrupt Enable bit, which disables the XOSC Ready interrupt.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The XOSC Ready interrupt is disabled.                                                    |

| 1     | The XOSC Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | XOSC Ready Interrupt flag is set.                                                        |

The Write-Synchronization of the Enable bit is triggered by writing a '1' to the Enable bit of the BOD33 Control register. The Synchronization Ready bit (STATUS.B33SRDY) in the STATUS register will be cleared when the Write-Synchronization starts, and set again when the Write-Synchronization is complete. Writing to the same register while the Write-Synchronization is ongoing (STATUS.B33SRDY is '0') will generate a PAC error without stalling the APB bus.

## 25.6.7 Low Power VREF in Active Mode

During active functional mode, the brownout detector BOD33 and the main voltage regulator (VREG) can reduce their power consumption by using the low power voltage reference (ULPVREF).

The low power voltage reference is ready and can be selected when ULPVREFRDY bit in STATUS register is high. The ULPVREF Ready (ULPVREFRDY) interrupt can also be used to detect a zero-to-one transition of the STATUS.ULPVREFRDY bit.

Writing the VREF bit in the BOD33 register to '1' selects ULPVREF as voltage reference for the BOD33.

If the chip operated in PL0 ((PM->PLCFG.PLSEL=0) or Performance Level is disabled (PM->PLCFG.PLDIS=1), writing the VREFSEL bit in the VREG register to '1' selects ULPVREF as voltage reference for the main voltage regulator.

#### 25.8.3 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x08Reset:x initially determined from NVM User Row after resetProperty:-

| Bit    | 31      | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|---------|----|----|----|------------|----------|----------|----------|

|        |         |    |    |    |            |          |          |          |

| Access |         |    |    |    |            |          |          |          |

| Reset  |         |    |    |    |            |          |          |          |

|        |         |    |    |    |            |          |          |          |

| Bit    | 23      | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |         |    |    |    |            |          |          |          |

| Access |         |    |    |    |            |          |          |          |

| Reset  |         |    |    |    |            |          |          |          |

|        |         |    |    |    |            |          |          |          |

| Bit    | 15      | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |         |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |         |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |         |    |    |    | 0          | 0        |          | 1        |

|        |         |    |    |    |            |          |          |          |

| Bit    | 7       | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |         |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access | <u></u> | •  | •  |    | •          | R/W      | R/W      | R/W      |

| Reset  |         |    |    |    |            | 0        | 0        | х        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit will clear on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY) and will generate an interrupt request if INTENSET.ULPVREFRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the ULPVREFRDY interrupt flag.

Bit 10 – VCORERDY VDDCORE Voltage Ready

This flag is cleared by writing a '1 to it.

This flag is set on a zero-to-one transition of the VDDCORE Ready bit in the Status register (STATUS.VCORERDY) and will generate an interrupt request if INTENSET.VCORERDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the VCORERDY interrupt flag.

Bit 8 – VREGRDY Voltage Regulator Ready

This flag is cleared by writing a '1' to it.

© 2018 Microchip Technology Inc.

## 26.8.1 Control A

| Name:     | CTRLA                                                |

|-----------|------------------------------------------------------|

| Offset:   | 0x00                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Synchronized             |

| Bit    | 7        | 6        | 5 | 4 | 3 | 2   | 1      | 0 |

|--------|----------|----------|---|---|---|-----|--------|---|

|        | ALWAYSON | RUNSTDBY |   |   |   | WEN | ENABLE |   |

| Access | R/W      | R/W      |   |   |   | R/W | R/W    |   |

| Reset  | x        | x        |   |   |   | x   | x      |   |

### Bit 7 – ALWAYSON Always-On

This bit allows the WDT to run continuously. After being set, this bit cannot be written to '0', and the WDT will remain enabled until a power-on Reset is received. When this bit is '1', the Control A register (CTRLA), the Configuration register (CONFIG) and the Early Warning Control register (EWCTRL) will be read-only, and any writes to these registers are not allowed.

Writing a '0' to this bit has no effect.

This bit is not Enable-Protected.

This bit is loaded from NVM User Row at start-up.

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The WDT is enabled and disabled through the ENABLE bit.                |

| 1     | The WDT is enabled and can only be disabled by a power-on reset (POR). |

#### Bit 6 - RUNSTDBY Run in Standby

This bit controls the behavior of the watchdog during standby sleep mode. This bit can only be written when CTRLA.ENABLE is zero or CTRLA.ALWAYSON is one:

- When CTRLA.ALWAYSON=0, this bit is enable-protected by CTRLA.ENABLE.

- When CTRLA.ALWAYSON=1, this bit is not enable-protected by CTRLA.ENABLE.

These bits are loaded from NVM User Row at startup.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The WDT is disabled during standby sleep.                     |

| 1     | The WDT is enabled continues to operate during standby sleep. |

#### **Bit 2 – WEN** Watchdog Timer Window Mode Enable

This bit enables Window mode. It can only be written if the peripheral is disabled unless CTRLA.ALWAYSON=1. The initial value of this bit is loaded from Flash Calibration.

This bit is loaded from NVM User Row at startup.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Window mode is disabled (normal operation). |

| 1     | Window mode is enabled.                     |

## 27.8.11 Compare 0 Value in COUNT32 mode (CTRLA.MODE=0)

| Name:     | COMP                                     |

|-----------|------------------------------------------|

| Offset:   | 0x20                                     |

| Reset:    | 0x0000000                                |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 31        | 30  | 29  | 28   | 27      | 26  | 25  | 24  |

|--------|-----------|-----|-----|------|---------|-----|-----|-----|

| [      |           |     |     | COMP | [31:24] |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |           |     |     |      |         |     |     |     |

| Bit    | 23        | 22  | 21  | 20   | 19      | 18  | 17  | 16  |

|        |           |     |     | COMP | [23:16] |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |           |     |     |      |         |     |     |     |

| Bit    | 15        | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|        |           |     |     | COMF | P[15:8] |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |           |     |     |      |         |     |     |     |

| Bit    | 7         | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        | COMP[7:0] |     |     |      |         |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

## Bits 31:0 - COMP[31:0] Compare Value

The 32-bit value of COMP0 is continuously compared with the 32-bit COUNT value. When a match occurs, the Compare 0 interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next counter cycle, and the counter value is cleared if CTRLA.MATCHCLR is '1'.

## 27.10.7 Debug Control

Name:DBGCTRLOffset:0x0EReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

## Bit 0 – DBGRUN Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

| Value | e Description                                                                      |

|-------|------------------------------------------------------------------------------------|

| 0     | The RTC is halted when the CPU is halted by an external debugger.                  |

| 1     | The RTC continues normal operation when the CPU is halted by an external debugger. |

## 27.10.14 Tamper Control

| Name:     | TAMPCTRL                               |

|-----------|----------------------------------------|

| Offset:   | 0x60                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31          | 30 | 29          | 28 | 27      | 26      | 25      | 24      |

|--------|-------------|----|-------------|----|---------|---------|---------|---------|

|        |             |    |             |    | DEBNC3  | DEBNC2  | DEBNC1  | DEBNC0  |

| Access |             |    | ·           | •  |         |         |         |         |

| Reset  |             |    |             |    | 0       | 0       | 0       | 0       |

|        |             |    |             |    |         |         |         |         |

| Bit    | 23          | 22 | 21          | 20 | 19      | 18      | 17      | 16      |

|        |             |    |             |    | TAMLVL3 | TAMLVL2 | TAMLVL1 | TAMLVL0 |

| Access |             | •  | •           | •  |         |         |         |         |

| Reset  |             |    |             |    | 0       | 0       | 0       | 0       |

|        |             |    |             |    |         |         |         |         |

| Bit    | 15          | 14 | 13          | 12 | 11      | 10      | 9       | 8       |

|        |             |    |             |    |         |         |         |         |

| Access |             | •  | •           |    |         |         |         |         |

| Reset  |             |    |             |    |         |         |         |         |

|        |             |    |             |    |         |         |         |         |

| Bit    | 7           | 6  | 5           | 4  | 3       | 2       | 1       | 0       |

|        | IN3ACT[1:0] |    | IN2ACT[1:0] |    | IN1AC   | T[1:0]  | IN0AC   | T[1:0]  |

| Access |             |    |             |    |         |         |         |         |

| Reset  | 0           | 0  | 0           | 0  | 0       | 0       | 0       | 0       |

### Bits 24, 25, 26, 27 - DEBNC Debounce Enable of Tamper Input INn

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Debouncing is disabled for Tamper input INn |

| 1     | Debouncing is enabled for Tamper input INn  |

### Bits 16, 17, 18, 19 - TAMLVL Tamper Level Select of Tamper Input INn

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | A falling edge condition will be detected on Tamper input INn. |

| 1     | A rising edge condition will be detected on Tamper input INn.  |

## Bits 0:1, 2:3, 4:5, 6:7 - INACT Tamper Channel n Action

These bits determine the action taken by Tamper Channel n.

| Value | Name    | Description                                                          |

|-------|---------|----------------------------------------------------------------------|

| 0x0   | OFF     | Off (Disabled)                                                       |

| 0x1   | WAKE    | Wake and set Tamper flag                                             |

| 0x2   | CAPTURE | Capture timestamp and set Tamper flag                                |

| 0x3   | ACTL    | Compare RTC signal routed between INn and OUT pins . When a mismatch |

|       |         | occurs, capture timestamp and set Tamper flag                        |

## 30.8.12 NVM Parameter

| Name:     | PARAM        |

|-----------|--------------|

| Offset:   | 0x24         |

| Reset:    | 0x000XXXXX   |

| Property: | Write-Secure |

| Bit    | 31            | 30    | 29      | 28    | 27      | 26    | 25       | 24    |

|--------|---------------|-------|---------|-------|---------|-------|----------|-------|

|        | DFLASHP[11:4] |       |         |       |         |       |          |       |

| Access | R/R/R         | R/R/R | R/R/R   | R/R/R | R/R/R   | R/R/R | R/R/R    | R/R/R |

| Reset  | 0             | 0     | 0       | 0     | 0       | 0     | 0        | 0     |

|        |               |       |         |       |         |       |          |       |

| Bit    | 23            | 22    | 21      | 20    | 19      | 18    | 17       | 16    |

|        |               | DFLAS | HP[3:0] |       |         |       | PSZ[2:0] |       |

| Access | R/R/R         | R/R/R | R/R/R   | R/R/R |         | R/R/R | R/R/R    | R/R/R |

| Reset  | 0             | 0     | 0       | 0     |         | x     | x        | x     |

|        |               |       |         |       |         |       |          |       |

| Bit    | 15            | 14    | 13      | 12    | 11      | 10    | 9        | 8     |

|        |               |       |         | FLASH | P[15:8] |       |          |       |

| Access | R/R/R         | R/R/R | R/R/R   | R/R/R | R/R/R   | R/R/R | R/R/R    | R/R/R |

| Reset  | x             | x     | x       | x     | x       | х     | x        | x     |

|        |               |       |         |       |         |       |          |       |

| Bit    | 7             | 6     | 5       | 4     | 3       | 2     | 1        | 0     |

|        |               |       |         | FLASH | IP[7:0] |       |          |       |

| Access | R/R/R         | R/R/R | R/R/R   | R/R/R | R/R/R   | R/R/R | R/R/R    | R/R/R |

| Reset  | х             | x     | x       | x     | x       | x     | x        | x     |

## Bits 31:20 – DFLASHP[11:0] Data FLASH area Pages

Indicates the number of pages in the Data FLASH array.

## Bits 18:16 - PSZ[2:0] Page Size

Indicates the page size. Not all devices of the device families will provide all the page sizes indicated in the table.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | 8    | 8 bytes     |

| 0x1   | 16   | 16 bytes    |

| 0x2   | 32   | 32 bytes    |

| 0x3   | 64   | 64 bytes    |

| 0x4   | 128  | 128 bytes   |

| 0x5   | 256  | 256 bytes   |

| 0x6   | 512  | 512 bytes   |

| 0x7   | 1024 | 1024 bytes  |

## Bits 15:0 - FLASHP[15:0] FLASH Pages

Indicates the number of pages in the FLASH array.

## 31.8.3 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x005                |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|---|---|---|---|---|---|-----|-----|

|        |   |   |   |   |   |   | DRP | ERR |

| Access |   |   |   |   |   |   | R/W | R/W |

| Reset  |   |   |   |   |   |   | 0   | 0   |

**Bit 1 – DRP** Data Remanence Prevention Complete Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will set the Data Remanence Prevention Complete Interrupt Enable bit, which enables the data remanence prevention complete interrupt.

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | Data remanence prevention complete interrupt is disabled. |

| 1     | Data remanence prevention complete interrupt is enabled.  |

Bit 0 – ERR TrustRAM Read Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the TrustRAM Read Error Interrupt Enable bit, which enables the TrustRAM read error interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | TrustRAM read error interrupt is disabled. |

| 1     | TrustRAM read error interrupt is enabled.  |

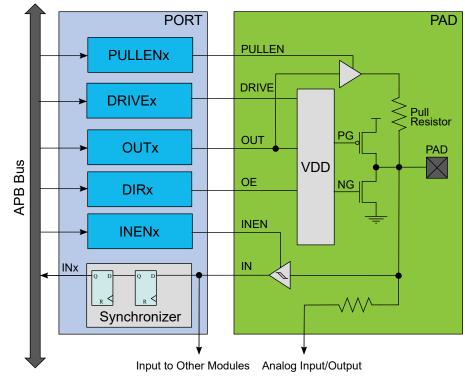

## 32.5.10 CPU Local Bus

The CPU local bus (IOBUS) is an interface that connects the CPU directly to the PORT. It is a singlecycle bus interface, which does not support wait states. It supports 8-bit, 16-bit and 32-bit sizes.

This bus is generally used for low latency operation. The Data Direction (DIR) and Data Output Value (OUT) registers can be read, written, set, cleared or be toggled using this bus, and the Data Input Value (IN) registers can be read.

Since the IOBUS cannot wait for IN register resynchronization, the Control register (CTRL) must be configured to continuous sampling of all pins that need to be read via the IOBUS in order to prevent stale data from being read.

**Note:** Refer to the *Product Mapping* chapter for the IOBUS address.

## 32.6 Functional Description

## Figure 32-2. Overview of the PORT

## 32.6.1 Principle of Operation

Each PORT group of up to 32 pins is controlled by the registers in PORT, as described in the figure. These registers in PORT are duplicated for each PORT group, with increasing base addresses. The number of PORT groups may depend on the package/number of pins.

## PORT - I/O Pin Controller

| Offset | Name     | Bit Pos. |                |                 |         |         |            |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

|--------|----------|----------|----------------|-----------------|---------|---------|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|        |          | 31:24    |                | IN[31:24]       |         |         |            |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

|        |          | 7:0      |                | SAMPLING[7:0]   |         |         |            |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x24   | CTRL     | 15:8     | SAMPLING[15:8] |                 |         |         |            |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| UX24   | CIRL     | 23:16    |                | SAMPLING[23:16] |         |         |            |            | PMUXEN   PMUXEN |        |

|        |          | 31:24    |                |                 |         | SAMPLIN | NG[31:24]  |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

|        |          | 7:0      |                | PINMASK[7:0]    |         |         |            |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x28   | WRCONFIG | 15:8     |                |                 |         | PINMAS  | SK[15:8]   |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0,20   | WRCONFIG | 23:16    |                | DRVSTR          |         |         | PULLEN     |            | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

|        |          | 31:24    | HWSEL          | WRPINCFG        |         | WRPMUX  |            | PMU        | <b>&lt;</b> [3:0]                                                                                                                                                                                                                                                                                                                                                                       |        |

|        |          | 7:0      | PORTEIX        | EVAC            | Tx[1:0] |         |            | PIDx[4:0]  |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 000    | EV(CTD)  | 15:8     | PORTEIX        | EVAC            | Tx[1:0] |         |            | PIDx[4:0]  |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x2C   | EVCTRL   | 23:16    | PORTEIx        | EVAC            | Tx[1:0] |         |            | PIDx[4:0]  |                                                                                                                                                                                                                                                                                                                                                                                         |        |

|        |          | 31:24    | PORTEIx        | EVAC            | Tx[1:0] |         |            | PIDx[4:0]  |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x30   | PMUX0    | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x31   | PMUX1    | 7:0      |                |                 | (O[3:0] |         |            | PMUX       |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x32   | PMUX2    | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x33   | PMUX3    | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x34   | PMUX4    | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x35   | PMUX5    | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x36   | PMUX6    | 7:0      |                | PMU             | (O[3:0] |         | PMUXE[3:0] |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x37   | PMUX7    | 7:0      |                | PMU             | (O[3:0] |         | PMUXE[3:0] |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x38   | PMUX8    | 7:0      |                |                 | (O[3:0] |         | PMUXE[3:0] |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x39   | PMUX9    | 7:0      |                |                 | (O[3:0] |         | PMUXE[3:0] |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x3A   | PMUX10   | 7:0      |                | PMUX0[3:0]      |         |         |            | PMUXE[3:0] |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x3B   | PMUX11   | 7:0      |                | PMUXO[3:0]      |         |         |            | PMUX       |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x3C   | PMUX12   | 7:0      |                | PMU             | (O[3:0] |         | PMUXE[3:0] |            |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x3D   | PMUX13   | 7:0      |                |                 | (O[3:0] |         |            | PMUX       |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x3E   | PMUX14   | 7:0      |                | PMU             | (O[3:0] |         |            | PMUX       | E[3:0]                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x3F   | PMUX15   | 7:0      |                |                 | (O[3:0] |         |            | PMUX       |                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 0x40   | PINCFG0  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x41   | PINCFG1  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x42   | PINCFG2  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x43   | PINCFG3  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x44   | PINCFG4  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x45   | PINCFG5  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x46   | PINCFG6  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x47   | PINCFG7  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x48   | PINCFG8  | 7:0      | DRVSTR         |                 |         |         | PULLEN     | INEN       | PMUXEN                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 0x49   | PINCFG9  | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x4A   | PINCFG10 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x4B   | PINCFG11 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x4C   | PINCFG12 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x4D   | PINCFG13 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

| 0x4E   | PINCFG14 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x4F   | PINCFG15 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 0x50   | PINCFG16 | 7:0      |                | DRVSTR          |         |         |            | PULLEN     | INEN                                                                                                                                                                                                                                                                                                                                                                                    | PMUXEN |

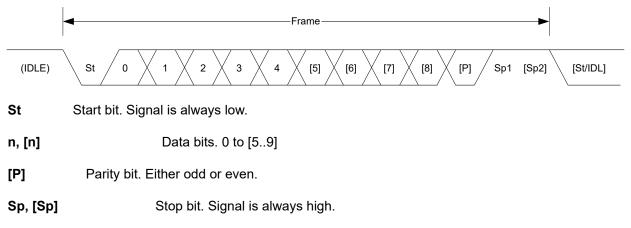

follow immediately, or the communication line can return to the idle (high) state. The figure below illustrates the possible frame formats. Brackets denote optional bits.

## Figure 35-2. Frame Formats

**IDLE** No frame is transferred on the communication line. Signal is always high in this state.

## 35.6.2 Basic Operation

## 35.6.2.1 Initialization

The following registers are enable-protected, meaning they can only be written when the USART is disabled (CTRL.ENABLE=0):

- Control A register (CTRLA), except the Enable (ENABLE) and Software Reset (SWRST) bits.

- Control B register (CTRLB), except the Receiver Enable (RXEN) and Transmitter Enable (TXEN) bits.

- Baud register (BAUD)

When the USART is enabled or is being enabled (CTRLA.ENABLE=1), any writing attempt to these registers will be discarded. If the peripheral is being disabled, writing to these registers will be executed after disabling is completed. Enable-protection is denoted by the "Enable-Protection" property in the register description.

Before the USART is enabled, it must be configured by these steps:

- 1. Select either external (0x0) or internal clock (0x1) by writing the Operating Mode value in the CTRLA register (CTRLA.MODE).

- 2. Select either asynchronous (0) or or synchronous (1) communication mode by writing the Communication Mode bit in the CTRLA register (CTRLA.CMODE).

- 3. Select pin for receive data by writing the Receive Data Pinout value in the CTRLA register (CTRLA.RXPO).

- 4. Select pads for the transmitter and external clock by writing the Transmit Data Pinout bit in the CTRLA register (CTRLA.TXPO).

- 5. Configure the Character Size field in the CTRLB register (CTRLB.CHSIZE) for character size.

- 6. Set the Data Order bit in the CTRLA register (CTRLA.DORD) to determine MSB- or LSB-first data transmission.

- 7. To use parity mode:

- 7.1. Enable parity mode by writing 0x1 to the Frame Format field in the CTRLA register (CTRLA.FORM).

#### 38.7.1.6 Interrupt Enable Set

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

| [      |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

**Bit 4 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will set the corresponding Match or Capture Channel x Interrupt Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

## Bit 0 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Valu | ue | Description                         |

|------|----|-------------------------------------|

| 0    |    | The Overflow interrupt is disabled. |

| 1    |    | The Overflow interrupt is enabled.  |

## TC – Timer/Counter

| Offset | Name   | Bit Pos. |               |

|--------|--------|----------|---------------|

|        |        | 23:16    | PERBUF[23:16] |

|        |        | 31:24    | PERBUF[31:24] |

|        |        | 7:0      | CCBUF[7:0]    |

| 0x30   | CCBUF0 | 15:8     | CCBUF[15:8]   |

| 0x30   |        | 23:16    | CCBUF[23:16]  |

|        |        | 31:24    | CCBUF[31:24]  |

|        |        | 7:0      | CCBUF[7:0]    |

| 0x34   | CCBUF1 | 15:8     | CCBUF[15:8]   |

| 0x34   |        | 23:16    | CCBUF[23:16]  |

|        |        | 31:24    | CCBUF[31:24]  |

### 38.7.3.8 Status

| Name:     | STATUS            |

|-----------|-------------------|

| Offset:   | 0x0B              |

| Reset:    | 0x01              |

| Property: | Read-Synchronized |

| Bit    | 7 | 6 | 5 | 4       | 3       | 2 | 1     | 0    |

|--------|---|---|---|---------|---------|---|-------|------|

| ĺ      |   |   |   | CCBUFVx | PERBUFV |   | SLAVE | STOP |

| Access |   |   |   | R/W     | R/W     |   | R     | R    |

| Reset  |   |   |   | 0       | 0       |   | 0     | 1    |

#### Bit 4 – CCBUFVx Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

### Bit 3 – PERBUFV Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. The bit is cleared by writing '1' to the corresponding location when CTRLB.LUPD is set, or automatically cleared by hardware on UPDATE condition. This bit is available only in 8-bit mode and will always read zero in 16- and 32-bit modes.

#### Bit 1 – SLAVE Slave Status Flag

This bit is only available in 32-bit mode on the slave TC (i.e., TC1 and/or TC3). The bit is set when the associated master TC (TC0 and TC2, respectively) is set to run in 32-bit mode.

#### Bit 0 – STOP Stop Status Flag

This bit is set when the TC is disabled, on a Stop command, or on an overflow/underflow condition when the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT) is '1'.

| Value | Description         |

|-------|---------------------|

| 0     | Counter is running. |

| 1     | Counter is stopped. |

The AC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the AC will be reset to their initial state, and the AC will be disabled. Refer to *CTRLA* for details.

## 42.6.2.3 Comparator Configuration

Each individual comparator must be configured by its respective Comparator Control register (COMPCTRLx) before that comparator is enabled. These settings cannot be changed while the comparator is enabled.

- Select the desired measurement mode with COMPCTRLx.SINGLE. See Starting a Comparison for more details.

- Select the desired hysteresis with COMPCTRLx.HYSTEN and COMPCTRLx.HYST. See Input Hysteresis for more details.

- Select the comparator speed versus power with COMPCTRLx.SPEED. See Propagation Delay vs. Power Consumption for more details.

- Select the interrupt source with COMPCTRLx.INTSEL.

- Select the positive and negative input sources with the COMPCTRLx.MUXPOS and COMPCTRLx.MUXNEG bits. See Selecting Comparator Inputs for more details.

- Select the filtering option with COMPCTRLx.FLEN.

- Select standby operation with Run in Standby bit (COMPCTRLx.RUNSTDBY).

The individual comparators are enabled by writing a '1' to the Enable bit in the Comparator x Control registers (COMPCTRLx.ENABLE). The individual comparators are disabled by writing a '0' to COMPCTRLx.ENABLE. Writing a '0' to CTRLA.ENABLE will also disable all the comparators, but will not clear their COMPCTRLx.ENABLE bits.

#### 42.6.2.4 Starting a Comparison

Each comparator channel can be in one of two different measurement modes, determined by the Single bit in the Comparator x Control register (COMPCTRLx.SINGLE):

- Continuous measurement

- Single-shot

After being enabled, a start-up delay is required before the result of the comparison is ready. This start-up time is measured automatically to account for environmental changes, such as temperature or voltage supply level, and is specified in the *Electrical Characteristics* chapters. During the start-up time, the COMP output is not available.

The comparator can be configured to generate interrupts when the output toggles, when the output changes from '0' to '1' (rising edge), when the output changes from '1' to '0' (falling edge) or at the end of the comparison. An end-of-comparison interrupt can be used with the Single-Shot mode to chain further events in the system, regardless of the state of the comparator outputs. The Interrupt mode is set by the Interrupt Selection bit group in the Comparator Control register (COMPCTRLx.INTSEL). Events are generated using the comparator output state, regardless of whether the interrupt is enabled or not.

#### 42.6.2.4.1 Continuous Measurement

Continuous measurement is selected by writing COMPCTRLx.SINGLE to zero. In continuous mode, the comparator is continuously enabled and performing comparisons. This ensures that the result of the latest comparison is always available in the Current State bit in the Status A register (STATUSA.STATEx).

After the start-up time has passed, a comparison is done and STATUSA is updated. The Comparator x Ready bit in the Status B register (STATUSB.READYx) is set, and the appropriate peripheral events and

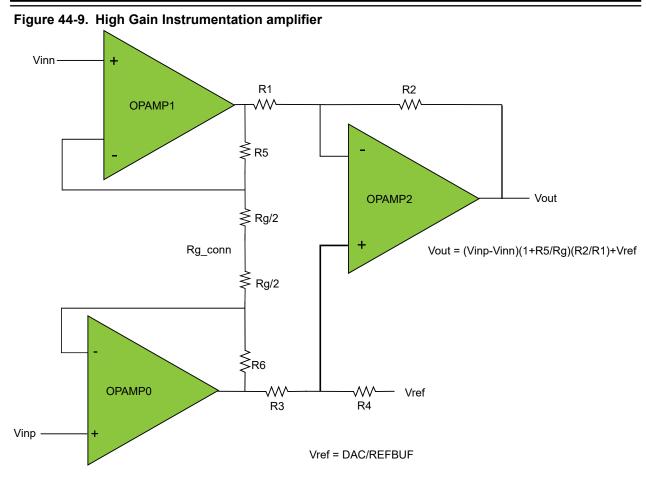

## **OPAMP – Operational Amplifier Controller**

## 44.6.10.9 Transimpedance amplifier

Each OPAMP can be configured as a transimpedance amplifier (current to voltage converter). In this mode the positive input is connected to ground. The negative input is connected to the output through the resistor ladder. The OPAMPCTRLx register can be configured as follows:

|        | MUXPOS | MUXNEG | RES1MUX | ΡΟΤΜUΧ | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 0010   | 000    | 001     | 000    | 0       | 1       | 1      | 0      |

| OPAMP1 | 0010   | 000    | 001     | 000    | 0       | 1       | 1      | 0      |

| OPAMP2 | 0010   | 000    | 001     | 000    | 0       | 1       | 1      | 0      |

Table 44-14. Transimpedance Amplifier

## **Electrical Characteristics**

| Symbol | Parameters                                                              | Conditions | Min. | Тур.       | Max. | Unit               |

|--------|-------------------------------------------------------------------------|------------|------|------------|------|--------------------|

|        |                                                                         | Mode 1     | -    | -0.3/0.3   | -    |                    |

|        |                                                                         | Mode 0     | -    | -0.09/0.07 | -    |                    |

| CMRR   | 1X gain                                                                 | Mode 3     | -    | 83         | -    | dB                 |

|        |                                                                         | Mode 2     | -    | 84         | -    |                    |

|        |                                                                         | Mode 1     | -    | 84         | -    |                    |

|        |                                                                         | Mode 0     | -    | 83         | -    |                    |

| PSRR   | 1X gain                                                                 | Mode 3     | -    | 76         | -    | dB                 |

|        |                                                                         | Mode 2     | -    | 76         | -    |                    |

|        |                                                                         | Mode 1     | -    | 76         | -    |                    |

|        |                                                                         | Mode 0     | -    | 75         | -    |                    |

| -      | Integrated Noise,<br>BW=[0.1Hz-10kHz],<br>x1 gain - VOUT=1V             | Mode 3     | -    | 7.9        | -    | µ <sup>V</sup> RMS |

|        |                                                                         | Mode 2     | -    | 8.3        | -    |                    |

|        |                                                                         | Mode 1     | -    | 9.9        | -    |                    |

|        |                                                                         | Mode 0     | -    | 12.7       | -    |                    |

| -      | Integrated Noise,<br>BW=[0.1Hz-1MHz],<br>x1 gain - V <sub>OUT</sub> =1V | Mode 3     | -    | 18.2       | -    | µ <sup>V</sup> RMS |

|        |                                                                         | Mode 2     | -    | 22.8       | -    |                    |

|        |                                                                         | Mode 1     | -    | 36.7       | -    |                    |

|        |                                                                         | Mode 0     | -    | 44.4       | -    |                    |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

## Table 46-35. PGA Electrical Characteristics<sup>(1)</sup>

| Symbol | Parameters                                                           | Conditions | Min. | Тур.  | Max.   | Unit  |

|--------|----------------------------------------------------------------------|------------|------|-------|--------|-------|

| -      | Gain accuracy                                                        | 16X Gain   | -    | -     | +/-2.4 | %     |

|        |                                                                      | 4X Gain    | -    | -     | +/-1.1 |       |

|        |                                                                      | 1X Gain    | -    | -     | +/-2.6 |       |

| THD    | Total Harmonic Distortion @ 10kHz - mode 3                           | 16X Gain   | -    | -77   | -      | dB    |

|        |                                                                      | 4X Gain    | -    | -72.8 | -      |       |

|        |                                                                      | 1X Gain    | -    | -82.6 | -      |       |

| -      | Integrated Noise, BW=[0.1Hz-10 kHz], 16X gain - V <sub>OUT</sub> =1V | Mode 3     | -    | 147   | -      | µVrms |

|        |                                                                      | Mode 2     | -    | 147   | -      |       |

|        |                                                                      | Mode 1     | -    | 162   | -      |       |

|        |                                                                      | Mode 0     | -    | 191   | -      |       |

| -      | Integrated Noise, BW=[0.1Hz-1MHz], 16X gain - VOUT=1V                | Mode 3     | -    | 262   | -      | μVrms |

|        |                                                                      | Mode 2     | -    | 247   | -      |       |

|        |                                                                      | Mode 1     | -    | 235   | -      |       |

|        |                                                                      | Mode 0     | -    | 235   | -      |       |

## **Electrical Characteristics**

| Symbol | Parameters | Drift<br>Calibration | PTC<br>scan rate<br>(msec) | Oversamples | Та | Тур. | Max. | Units |

|--------|------------|----------------------|----------------------------|-------------|----|------|------|-------|

|        |            |                      | 100                        | 4           |    | 1.7  | 43.2 |       |

|        |            |                      |                            | 16          |    | 2.4  | 43.9 |       |

|        |            |                      | 200                        | 4           |    | 1.4  | 42.8 |       |

|        |            |                      |                            | 16          |    | 1.8  | 43.2 |       |

|        |            | Enabled              | 10                         | 4           |    | 8.3  | 51.7 |       |

|        |            |                      |                            | 16          |    | 14.2 | 60.5 |       |

|        |            |                      | 50                         | 4           |    | 3.0  | 44.8 |       |

|        |            |                      |                            | 16          |    | 4.8  | 47.0 |       |

|        |            |                      | 100                        | 4           |    | 2.3  | 44.5 |       |

|        |            |                      |                            | 16          |    | 2.8  | 45.4 |       |

|        |            |                      | 200                        | 4           |    | 1.9  | 43.9 |       |

|        |            |                      |                            | 16          |    | 2.4  | 44.2 |       |

## Note:

1. These are based on characterization.

## 46.12 NVM Characteristics

## Table 46-39. NVM Max Speed Characteristics <sup>(1)</sup>

|                           | Conditions                | CPU Fmax (MHz) |     |     |  |  |

|---------------------------|---------------------------|----------------|-----|-----|--|--|

|                           |                           | ows            | 1WS | 2WS |  |  |

| PL0                       | V <sub>DDIO</sub> >1.62 V | 6              | 8   | 8   |  |  |

| (-40/85°C)<br>(-40/125°C) | V <sub>DDIO</sub> >2.7 V  | 7.5            | 8   | 8   |  |  |

| PL2                       | V <sub>DDIO</sub> >1.62 V | 14             | 28  | 32  |  |  |

| (-40/85°C)<br>(-40/125°C) | V <sub>DDIO</sub> >2.7 V  | 14             | 32  | 32  |  |  |

## Table 46-40. NVM Timing Characteristics <sup>(1)</sup>

| Symbol           | Timings    | Мах | Units |

|------------------|------------|-----|-------|

| t <sub>FPP</sub> | Page Write | 2.5 | ms    |

| t <sub>FRE</sub> | Row erase  | 6   |       |

Note: