#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml10e16a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SAM L10/L11 Family Pinouts

|            | Р          | in          |                           | Pin<br>Name            | Supply | A             |     |     | в <u>(</u> | <u>1)</u> |     |       | C <u>(2)(3)</u> | D(2)(3)                       | E             | G             | н              | I      | Reset<br>State   |

|------------|------------|-------------|---------------------------|------------------------|--------|---------------|-----|-----|------------|-----------|-----|-------|-----------------|-------------------------------|---------------|---------------|----------------|--------|------------------|

| SSOP2<br>4 | VQFN2<br>4 | WLCSP<br>32 | TQFP32<br>/<br>VQFN3<br>2 |                        |        | EIC           | REF | ADC | AC         | РТС       | DAC | OPAMP | SERCO<br>M      | SERCO<br>M<br>ALTER<br>NATIVE | тс            | RTC/<br>Debug | AC/<br>GCLK    | CCL    |                  |

| 3          | 24         | B2          | 31                        | PA30 /<br>SWCLK        | VDDIO  | EXTIN<br>T[6] |     |     |            | XY[18]    |     |       |                 | SERCO<br>M1/<br>PAD[2]        | TC1/<br>WO[0] | SWCLK         | GCLK_I<br>O[0] | IN[3]  | SWCLK<br>, I, PU |

| 4          | 1          | C3          | 32                        | PA31 /<br>SWDIO(<br>4) | VDDIO  | EXTIN<br>T[7] |     |     |            | XY[19]    |     |       |                 | SERCO<br>M1/<br>PAD[3]        | TC1/<br>WO[1] |               |                | OUT[1] | I/O, Hi-Z        |

- 1. All analog pin functions are on the peripheral function B. The peripheral function B must be selected to disable the digital control of the pin.

- 2. Refer to SERCOM Configurations to get the list of the supported features for each SERCOM instance.

- 3. 24-pin packages only have two SERCOM instances: SERCOM0 and SERCOM1.

- 4. The following pins are High Sink pins and have different properties than standard pins: PA16, PA17, PA22, PA23 and PA31.

## 4.2 Oscillators Pinout

The oscillators are not mapped to the I/O Pin Controller (PORT) functions and their multiplexing is controlled by the Oscillators Controller (OSCCTRL) and 32 kHz Oscillators Controller (OSC32KCTRL) registers.

#### Table 4-2. Oscillator Pinout

| Oscillator | Supply | Signal | I/O pin |

|------------|--------|--------|---------|

| XOSC       | VDDIO  | XIN    | PA14    |

|            |        | XOUT   | PA15    |

| XOSC32K    | VDDANA | XIN32  | PA00    |

|            |        | XOUT32 | PA01    |

To improve the cycle-to-cycle jitter of the XOSC32 oscillator, it is recommended to keep the neighboring pins of XIN32 and the following pins of XOUT32 as static as possible:

#### Table 4-3. XOSC32 Jitter Minimization

| Package Pin Count | Static Signal Recommended |

|-------------------|---------------------------|

| 32                | PA02, PA03                |

| 24                | PA02, PA03                |

## 4.3 Serial Wire Debug Interface Pinout

The SWCLK pin is by default assigned to the SWCLK peripheral function G to allow debugger probe detection.

A debugger probe detection (cold-plugging or hot-plugging) will automatically switch the SWDIO I/O pin to the SWDIO function, as long as the SWLCK peripheral function is selected.

# SAM L10/L11 Family

### **Processor and Architecture**

| Features                       | Cortex-M23 Configurable<br>Options                             | SAM L10 Implementation | SAM L11 Implementation |

|--------------------------------|----------------------------------------------------------------|------------------------|------------------------|

| Cross Trigger Interface (CTI)  | Present or absent                                              | Absent                 | Absent                 |

| Micro Trace Buffer (MTB)       | Present or absent                                              | Absent                 | Absent                 |

| Embedded Trace Macrocell (ETM) | Present or absent                                              | Absent                 | Absent                 |

| JTAGnSW debug protocol         | Selects between JTAG or Serial-<br>Wire interfaces for the DAP | Serial-Wire            | Serial-Wire            |

| Multi-drop for Serial Wire     | Present or absent                                              | Absent                 | Absent                 |

#### Note:

1. Refer to Table 11-3 for more information.

For more details, refer to the ARM Cortex-M23 Processor Technical Reference Manual (http://www.arm.com).

#### 11.1.2 Cortex-M23 Core Peripherals

The processor has the following core peripheral:

- System Timer (SysTick)

- The System Timer is a 24-bit timer clocked by the core frequency.

**Important:** On SAM L11 devices, there are two System timers, one for Secure state and one for Non-secure state.

- Nested Vectored Interrupt Controller (NVIC)

- The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

**Important:** On SAM L11 devices, there are two Vector tables: the Secure Vector table and the Non-Secure Vector table.

- System Control Block (SCB)

- The System Control Block (SCB) provides system implementation information and system control that includes configuration, control, and reporting of system exceptions

- Memory Protection Unit (MPU)

- The MPU improves system reliability by defining the memory attributes for different memory regions.

| 7 |

|---|

|   |

**Important:** On SAM L11 devices, there are two MPUs: one for the Secure state and one for the Non-secure state. Each MPU can define memory access permissions and attributes independently.

- Security Attribution Unit (SAU)

- The SAU improves system security by defining security attributes for different regions.

#### 14.4.2.1.3 CRC Computation and Programming

The CRCs needs to be recalculated and updated in their respective NVM row as soon as a data from any of the checked regions is changed.

**Important:** USERCRC and BOCORCRC CRCs programming must be done by any programming tool supporting the SAM L11 devices.

The algorithm is a CRC-32 module embedded in the DSU peripheral and that uses for both CRC calculation with the following parameters:

- Width = 32 bits

- Polynomial = 0x04C11DB7 (Poly)

- Initial Value = 0xFFFFFFFF (Init)

- Input Data is reflected (RefIn)

- Output Data is reflected (RefOut)

- No XOR is performed on the output CRC (XorOut)

Example: the DSU CRC of 0x31, 0x32, 0x33, 0x34, 0x35, 0x36, 0x37, 0x38, 0x39 is 0x340BC6D9

#### 14.4.2.2 Memories and Peripherals Configurations Initialization

For SAM L11 devices, memories and peripherals security attributions are done by reading the different fuses values from the NVM User (UROW) and Boot Configuration (BOCOR) rows.

The Boot ROM is responsible for setting these attributions on the different concerned memory and peripheral controllers:

- Set memory security attribution according to AS, ANSC, DS, RS, BS, BSNC and BOOTPROT fuses

- Set peripherals security attribution according to NONSECA, NONSECB and NONSECC fuses

**Important:** The Boot ROM does not perform any consistency checks on the configured memory attributions (e.g setting BS>BOOTPROT will not trigger any errors during Boot ROM execution).

#### 14.4.2.3 Secure Boot

Depending on the BOOTOPT fuse value (from BOCOR NVM row), the following secure boot integrity checks will be performed on:

- The Flash BS memory area which is composed by:

- The Flash Secure BOOT memory region

- The Flash Non-Secure Callable BOOT memory region

- And the NVM Boot Configuration row (BOCOR)

#### Table 14-4. Secure Boot Options

| вооторт | Verified Areas         | Verification Method |

|---------|------------------------|---------------------|

| 0       | None                   | -                   |

| 1       | Flash BS Memory Region | SHA-256             |

|         | +                      |                     |

|         | NVM BOCOR row          |                     |

Hot plugging in standby mode is supported except if the power domain PDSW is in retention state.

Cold plugging in OFF mode is supported as long as the reset duration is superior to (Tmin).

#### 22.5.7 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

• Interrupt Flag register (INTFLAG).

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 22.5.8 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 22.5.9 Analog Connections

Not applicable.

### 22.6 Functional Description

#### 22.6.1 Terminology

The following is a list of terms used to describe the Power Managemement features of this microcontroller.

#### 22.6.1.1 Performance Levels

To help balance between performance and power consumption, the device has two performance levels. Each of the performance levels has a maximum operating frequency and a corresponding maximum consumption in  $\mu$ A/MHz.

It is the application's responsibility to configure the appropriate PL depending on the application activity level. When the application selects a new PL, the voltage applied on the full logic area moves from one value to another. This voltage scaling technique allows to reduce the active power consumption while decreasing the maximum frequency of the device.

#### 22.6.1.1.1 PL0

Performance Level 0 (PL0) provides the maximum energy efficiency configuration.

Refer to the *Electrical Characteristics* chapters for details on energy consumption and maximum operating frequency.

|       | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x06<br>0x00<br>- |   |   |   |   |   |       |

|-------|-----------------------------------------|------------------------------|---|---|---|---|---|-------|

| Bit   | 7                                       | 6                            | 5 | 4 | 3 | 2 | 1 | 0     |

|       |                                         |                              |   |   |   |   |   | PLRDY |

| ccess |                                         |                              |   |   |   |   |   | R/W   |

| Reset |                                         |                              |   |   |   |   |   | 0     |

#### Bit 0 – PLRDY Performance Level Ready

This flag is set when the performance level is ready and will generate an interrupt if INTENCLR/ SET.PLRDY is '1'.

Writing a '1' to this bit has no effect.

Interrupt Flag Status and Clear

22.8.6

Writing a '1' to this bit clears the Performance Ready interrupt flag.

#### 23.8.10 DFLLULP Dither Control

| Name:     | DFLLULPDITHER                          |

|-----------|----------------------------------------|

| Offset:   | 0x1E                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 7 | 6   | 5        | 4   | 3 | 2   | 1         | 0   |

|--------|---|-----|----------|-----|---|-----|-----------|-----|

|        |   |     | PER[2:0] |     |   |     | STEP[2:0] |     |

| Access | R | R/W | R/W      | R/W | R | R/W | R/W       | R/W |

| Reset  | 0 | 0   | 0        | 0   | 0 | 0   | 0         | 0   |

#### Bits 6:4 - PER[2:0] Dither Period

These bits define the number of reference clock periods over which dithering is applied.

| Value | Name  | Description                            |  |  |  |

|-------|-------|----------------------------------------|--|--|--|

| 0x0   | PER1  | Dither over 1 reference clock period   |  |  |  |

| 0x1   | PER2  | ther over 2 reference clock periods    |  |  |  |

| 0x2   | PER4  | ither over 4 reference clock periods   |  |  |  |

| 0x3   | PER8  | Dither over 8 reference clock periods  |  |  |  |

| 0x4   | PER16 | Dither over 16 reference clock periods |  |  |  |

| 0x5   | PER32 | Dither over 32 reference clock periods |  |  |  |

| 0x6 - | -     | Reserved                               |  |  |  |

| 0x7   |       |                                        |  |  |  |

#### Bits 2:0 – STEP[2:0] Dither Step

This field defines the dithering step size.

| Value | Name  | Description     |

|-------|-------|-----------------|

| 0x0   | STEP1 | Dither step = 1 |

| 0x1   | STEP2 | Dither step = 2 |

| 0x2   | STEP4 | Dither step = 4 |

| 0x3   | STEP8 | Dither step = 8 |

| 0x4 - | -     | Reserved        |

| 0x7   |       |                 |

# 27. RTC – Real-Time Counter

## 27.1 Overview

The Real-Time Counter (RTC) is a 32-bit counter with a 10-bit programmable prescaler that typically runs continuously to keep track of time. The RTC can wake up the device from sleep modes using the alarm/ compare wake up, periodic wake up, or overflow wake up mechanisms, or from the wake inputs.

The RTC can generate periodic peripheral events from outputs of the prescaler, as well as alarm/compare interrupts and peripheral events, which can trigger at any counter value. Additionally, the timer can trigger an overflow interrupt and peripheral event, and can be reset on the occurrence of an alarm/compare match. This allows periodic interrupts and peripheral events at very long and accurate intervals.

The 10-bit programmable prescaler can scale down the clock source. By this, a wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the minimum counter tick interval is  $30.5\mu$ s, and time-out periods can range up to 36 hours. For a counter tick interval of 1s, the maximum time-out period is more than 136 years.

## 27.2 Features

- 32-bit counter with 10-bit prescaler

- Multiple clock sources

- 32-bit or 16-bit counter mode

- One 32-bit or two 16-bit compare values

- Clock/Calendar mode

- Time in seconds, minutes, and hours (12/24)

- Date in day of month, month, and year

- Leap year correction

- Digital prescaler correction/tuning for increased accuracy

- Overflow, alarm/compare match and prescaler interrupts and events

- Optional clear on alarm/compare match

- 2 general purpose registers

- Tamper Detection

- Timestamp on event or up to 5 inputs with debouncing

- Active layer protection

# EIC – External Interrupt Controller

• The configuration of secured external interrupts can only be changed in the secure alias. Attempt to change the configuration in non-secure mode is silently ignored. Affected configuration registers are: CTRLA, NMICTRL, NMIFLAG, EVCTRL, INTENCLR, INTENSET, INTFLAG, ASYNCH, CONFIGn, DEBOUNCEN, DPRESCALER.

**Note:** Refer to the *Mix-Secure Peripherals* section in the SAM L11 *Security Features* chapter for more information.

#### 29.5.10 Analog Connections

Not applicable.

#### 29.6 Functional Description

#### 29.6.1 Principle of Operation

The EIC detects edge or level condition to generate interrupts to the CPU interrupt controller or events to the Event System. Each external interrupt pin (EXTINT) can be filtered using majority vote filtering, clocked by GCLK\_EIC or by CLK\_ULP32K.

#### 29.6.2 Basic Operation

#### 29.6.2.1 Initialization

The EIC must be initialized in the following order:

- 1. Enable CLK\_EIC\_APB

- 2. If required, configure the NMI by writing the Non-Maskable Interrupt Control register (29.8.2 NMICTRL)

- 3. Enable GCLK\_EIC or CLK\_ULP32K when one of the following configuration is selected:

- the NMI uses edge detection or filtering.

- one EXTINT uses filtering.

- one EXTINT uses synchronous edge detection.

- one EXTINT uses debouncing.

GCLK\_EIC is used when a frequency higher than 32KHz is required for filtering.

CLK\_ULP32K is recommended when power consumption is the priority. For CLK\_ULP32K write a '1' to the Clock Selection bit in the Control A register (CTRLA.CKSEL).

- 4. Configure the EIC input sense and filtering by writing the Configuration n register (CONFIG).

- 5. Optionally, enable the asynchronous mode.

- 6. Optionally, enable the debouncer mode.

- 7. Enable the EIC by writing a '1' to CTRLA.ENABLE.

The following bits are enable-protected, meaning that it can only be written when the EIC is disabled (CTRLA.ENABLE=0):

Clock Selection bit in Control A register (CTRLA.CKSEL)

The following registers are enable-protected:

- Event Control register (29.8.5 EVCTRL)

- Configuration n register (CONFIG).

- External Interrupt Asynchronous Mode register (29.8.9 ASYNCH)

#### 29.8.6 Interrupt Enable Clear

| Name:     | INTENCLR                         |

|-----------|----------------------------------|

| Offset:   | 0x0C                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the external interrupt x (EXTINTx) is set as Non-Secure in the NONSEC register (NONSEC.EXTINTx bit).

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit         | 31             | 30             | 29             | 28        | 27        | 26        | 25        | 24        |

|-------------|----------------|----------------|----------------|-----------|-----------|-----------|-----------|-----------|

|             | NSCHK          |                |                |           |           |           |           |           |

| Access      | RW/RW/RW       |                |                |           |           |           |           |           |

| Reset       | 0              |                |                |           |           |           |           |           |

|             |                |                |                |           |           |           |           |           |

| Bit         | 23             | 22             | 21             | 20        | 19        | 18        | 17        | 16        |

|             |                |                |                |           |           |           |           |           |

| Access      |                |                |                |           |           |           |           |           |

| Reset       |                |                |                |           |           |           |           |           |

|             |                |                |                |           |           |           |           |           |

| Bit         | 15             | 14             | 13             | 12        | 11        | 10        | 9         | 8         |

|             |                |                |                |           |           |           |           |           |

| Access      |                |                |                |           |           |           |           |           |

| Reset       |                |                |                |           |           |           |           |           |

| <b>D</b> :4 | 7              | 0              | -              |           | 0         | 0         |           | 0         |

| Bit         | 7              | 6              | 5              | 4         | 3         | 2         | 1         | 0         |

|             |                |                |                | EXTIN     |           |           |           |           |

| Access      |                |                |                | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset       | RW/RW*/RW<br>0 | RW/RW*/RW<br>0 | RW/RW*/RW<br>0 | 0         | 0         | 0         | 0         | 0         |

Bit 31 – NSCHK Non-secure Check Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the NSCHK Interrupt Enable bit.

#### Bits 7:0 – EXTINT[7:0] External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

# 31.7 Register Summary

| Offset | Name             | Bit Pos. |           |     |               |                  |        |  |  |

|--------|------------------|----------|-----------|-----|---------------|------------------|--------|--|--|

| 0x00   | CTRLA            | 7:0      | SILACC    | DRP | TAMPERS       | ENABLE           | SWRST  |  |  |

| 0x01   |                  |          |           |     |               |                  |        |  |  |

|        | Reserved         |          |           |     |               |                  |        |  |  |

| 0x03   |                  |          |           |     |               |                  |        |  |  |

| 0x04   | INTENCLR         | 7:0      |           |     |               | DRP              | ERR    |  |  |

| 0x05   | INTENSET         | 7:0      |           |     |               | DRP              | ERR    |  |  |

| 0x06   | INTFLAG          | 7:0      |           |     |               | DRP              | ERR    |  |  |

| 0x07   | STATUS           | 7:0      |           |     |               | DRP              | RAMINV |  |  |

|        |                  | 7:0      |           |     |               | ENABLE           | SWRST  |  |  |

| 0.00   | <b>EVALOPHEX</b> | 15:8     |           |     |               |                  |        |  |  |

| 0x08   | SYNCBUSY         | 23:16    |           |     |               |                  |        |  |  |

|        |                  | 31:24    |           |     |               |                  |        |  |  |

|        |                  | 7:0      |           |     | DSCKEY[7:0]   |                  |        |  |  |

| 0.00   | Dage             | 15:8     |           |     | DSCKEY[15:8]  |                  |        |  |  |

| 0x0C   | DSCC             | 23:16    |           |     | DSCKEY[23:16] |                  |        |  |  |

|        |                  | 31:24    | DSCEN     |     | DSCKEY        | <i>'</i> [29:24] |        |  |  |

| 0x10   | PERMW            | 7:0      |           |     |               | DATA[2:0]        |        |  |  |

| 0x11   | PERMR            | 7:0      |           |     |               | DATA[2:0]        |        |  |  |

| 0x12   |                  |          |           |     |               |                  |        |  |  |

|        | Reserved         |          |           |     |               |                  |        |  |  |

| 0xFF   |                  |          |           |     |               |                  |        |  |  |

|        |                  | 7:0      |           |     | DATA[7:0]     |                  |        |  |  |

| 0.0100 | <b>DAMA</b>      | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

| 0x0100 | RAM0             | 23:16    |           |     | DATA[23:16]   |                  |        |  |  |

|        |                  | 31:24    |           |     | DATA[31:24]   |                  |        |  |  |

|        |                  | 7:0      | DATA[7:0] |     |               |                  |        |  |  |

|        |                  | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

| 0x0104 | RAM1             | 23:16    |           |     | DATA[23:16]   |                  |        |  |  |

|        |                  | 31:24    |           |     | DATA[31:24]   |                  |        |  |  |

|        |                  | 7:0      |           |     | DATA[7:0]     |                  |        |  |  |

|        |                  | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

| 0x0108 | RAM2             | 23:16    |           |     | DATA[23:16]   |                  |        |  |  |

|        |                  | 31:24    |           |     | DATA[31:24]   |                  |        |  |  |

|        |                  | 7:0      |           |     | DATA[7:0]     |                  |        |  |  |

|        |                  | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

| 0x010C | RAM3             | 23:16    |           |     | DATA[23:16]   |                  |        |  |  |

|        |                  | 31:24    |           |     | DATA[31:24]   |                  |        |  |  |

|        |                  | 7:0      |           |     | DATA[7:0]     |                  |        |  |  |

|        |                  | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

| 0x0110 | RAM4             | 23:16    |           |     | DATA[23:16]   |                  |        |  |  |

|        |                  | 31:24    |           |     | DATA[31:24]   |                  |        |  |  |

|        |                  | 7:0      |           |     | DATA[7:0]     |                  |        |  |  |

| 0x0114 | RAM5             | 15:8     |           |     | DATA[15:8]    |                  |        |  |  |

|        |                  | 10.0     |           |     | DATA[15.0]    |                  |        |  |  |

#### 31.8.1 Control A

| Name:     | CTRLA                |

|-----------|----------------------|

| Offset:   | 0x000                |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7      | 6   | 5 | 4       | 3 | 2 | 1      | 0     |

|--------|--------|-----|---|---------|---|---|--------|-------|

|        | SILACC | DRP |   | TAMPERS |   |   | ENABLE | SWRST |

| Access | R/W    | R/W |   | R/W     |   |   | R/W    | R/W   |

| Reset  | 0      | 0   |   | 0       |   |   | 0      | 0     |

**Bit 7 – SILACC** Silent Access Enables differential storage of data.

| Value | Description                |

|-------|----------------------------|

| 0     | Silent access is disabled. |

| 1     | Silent access is enabled.  |

#### **Bit 6 – DRP** Data Remanence Prevention

Enables periodic DRP in TrustRAM.

| Value | Description                            |

|-------|----------------------------------------|

| 0     | Data remanence prevention is disabled. |

| 1     | Data remanence prevention is enabled.  |

#### Bit 4 – TAMPERS Tamper Erase

Auto-erases TrustRAM and DSCC.DSCKEY on tamper event.

| Value | Description               |

|-------|---------------------------|

| 0     | Tamper erase is disabled. |

| 1     | Tamper erase is enabled.  |

#### Bit 1 – ENABLE Enable

| Value | Description           |

|-------|-----------------------|

| 0     | The TRAM is disabled. |

| 1     | The TRAM is enabled.  |

#### Bit 0 – SWRST Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the TRAM to their initial state, and the TRAM will be disabled. This bit can also be set via hardware when a tamper occurs while CTRLA.TAMPERS is set.

Writing a one to CTRLA.SWRST will always take precedence, meaning that all other writes in the same writeoperation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

#### 33.7.16 Interrupt Flag Status and Clear

| Name:     | INTFLAG |  |  |  |  |

|-----------|---------|--|--|--|--|

| Offset:   | 0x1D6   |  |  |  |  |

| Reset:    | 0x0     |  |  |  |  |

| Property: | -       |  |  |  |  |

| <b>&gt;</b> | Important: | This register i | s only availab | le for SAM L | 11 and has no | o effect for <b>S</b> A | M L10.                                                                                                                                          |

|-------------|------------|-----------------|----------------|--------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | 6          | 5               | 4              | 3            | 2             | 1                       | 0                                                                                                                                               |

|             |            |                 |                |              |               |                         | NSCHK                                                                                                                                           |

|             |            |                 |                |              |               |                         | RW/RW/RW                                                                                                                                        |

|             |            |                 |                |              |               |                         | 0                                                                                                                                               |

|             | 7          | 2               | 2              | 2            | 2             | 2                       | Important:       This register is only available for SAM L11 and has no effect for SA         7       6       5       4       3       2       1 |

#### Bit 0 – NSCHK Non-Secure Check

This flag is set when a bit in NSCHKCHAN is 1 and the corresponding bit in NONSECCHAN is cleared, or when a bit in NSCHKCHAN is 0 and the corresponding bit in NONSECCHAN is set, or when a bit in NSCHKUSER is 1 and the corresponding bit in NONSECUSER is cleared, or when a bit in NSCHKUSER is 0 and the corresponding bit in NONSECUSER is set.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Non-Secure Check interrupt flag.

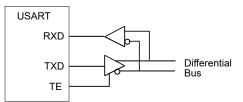

#### Figure 35-13. RS485 Bus Connection

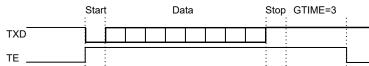

The TE pin will remain high for the complete frame including stop bit(s). If a Guard Time is programmed in the Control C register (CTRLC.GTIME), the line will remain driven after the last character completion. The following figure shows a transfer with one stop bit and CTRLC.GTIME=3.

#### Figure 35-14. Example of TE Drive with Guard Time

The Transmit Complete interrupt flag (INTFLAG.TXC) will be raised after the guard time is complete and TE goes low.

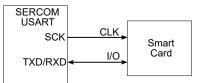

#### 35.6.3.6 ISO 7816 for Smart Card Interfacing

The SERCOM USART features an ISO/IEC 7816-compatible operating mode. This mode permits interfacing with smart cards and Security Access Modules (SAM) communicating through an ISO 7816 link. Both T=0 and T=1 protocols defined by the ISO 7816 specification are supported.

ISO 7816 is available with the following configuration:

- ISO 7816 format (CTRLA.FORM = 0x07)

- Inverse transmission and reception (CTRLA.RXINV=1 and CTRLA.TXINV=1)

- Single bidirectional data line (CTRLA.TXPO and CTRLA.RXPO configured to use the same data pin)

- Even parity (CTRLB.PMODE=0)

- 8-bit character size (CTRLB.CHSIZE=0)

- T=0 (CTRLA.CMODE=1) or T=1 (CTRLA.CMODE=0)

ISO 7816 is a half duplex communication on a single bidirectional line. The USART connects to a smart card as shown below. The output is only driven when the USART is transmitting. The USART is considered as the master of the communication as it generates the clock.

#### Figure 35-15. Connection of a Smart Card to the SERCOM USART

ISO 7816 characters are specified as 8 bits with even parity. The USART must be configured accordingly.

The USART cannot operate concurrently in both receiver and transmitter modes as the communication is unidirectional. It has to be configured according to the required mode by enabling or disabling either the receiver or the transmitter as desired. Enabling both the receiver and the transmitter at the same time in ISO 7816 mode may lead to unpredictable results.

The ISO 7816 specification defines an inverse transmission format. Data bits of the character must be transmitted on the I/O line at their negative value (CTRLA.RXINV=1 and CTRLA.TXINV=1).

© 2018 Microchip Technology Inc.

## 37.7 Register Summary - I2C Slave

| Offset | Name     | Bit Pos. |                    |         |       |           |           |        |              |          |  |

|--------|----------|----------|--------------------|---------|-------|-----------|-----------|--------|--------------|----------|--|

|        |          | 7:0      | RUNSTDBY           |         |       |           | MODE[2:0] | J      | ENABLE       | SWRST    |  |

| 0x00   |          | 15:8     |                    |         |       |           |           |        |              |          |  |

|        | CTRLA    | 23:16    | SEXTTOEN           |         | SDAHC | DLD[1:0]  |           |        |              | PINOUT   |  |

|        |          | 31:24    |                    | LOWTOUT |       |           | SCLSM     |        | SPEE         | D[1:0]   |  |

|        |          | 7:0      |                    |         |       |           |           |        |              |          |  |

| 004    |          | 15:8     | AMOE               | DE[1:0] |       |           |           | AACKEN | GCMD         | SMEN     |  |

| 0x04   | CTRLB    | 23:16    |                    |         |       |           | ACKACT    |        | CME          | CMD[1:0] |  |

|        |          | 31:24    |                    |         |       |           |           |        |              |          |  |

| 0x08   |          |          |                    |         |       |           |           |        |              |          |  |

|        | Reserved |          |                    |         |       |           |           |        |              |          |  |

| 0x13   |          |          |                    |         |       |           |           |        |              |          |  |

| 0x14   | INTENCLR | 7:0      | ERROR              |         |       |           |           | DRDY   | AMATCH       | PREC     |  |

| 0x15   | Reserved |          |                    |         |       |           |           |        |              |          |  |

| 0x16   | INTENSET | 7:0      | ERROR              |         |       |           |           | DRDY   | AMATCH       | PREC     |  |

| 0x17   | Reserved |          |                    |         |       |           |           |        |              |          |  |

| 0x18   | INTFLAG  | 7:0      | ERROR              |         |       |           |           | DRDY   | AMATCH       | PREC     |  |

| 0x19   | Reserved |          |                    |         |       |           |           |        |              |          |  |

| 0x1A   | STATUS   | 7:0      | CLKHOLD            | LOWTOUT |       | SR        | DIR       | RXNACK | COLL         | BUSERR   |  |

|        |          | 15:8     |                    |         |       |           | LENERR    | HS     | SEXTTOUT     |          |  |

|        | SYNCBUSY | 7:0      |                    |         |       |           |           |        | ENABLE       | SWRST    |  |

| 0.40   |          | 15:8     |                    |         |       |           |           |        |              |          |  |

| 0x1C   |          | 23:16    |                    |         |       |           |           |        |              |          |  |

|        |          | 31:24    |                    |         |       |           |           |        |              |          |  |

| 0x20   |          |          |                    |         |       |           |           |        |              |          |  |

|        | Reserved |          |                    |         |       |           |           |        |              |          |  |

| 0x23   |          |          |                    |         |       |           |           |        |              |          |  |

| 0.01   |          | 7:0      |                    |         |       | ADDR[6:0] |           |        |              | GENCEN   |  |

|        |          | 15:8     | TENBITEN ADDR[9:7] |         |       |           |           |        |              |          |  |

| 0x24   | ADDR     | 23:16    | ADDRMASK[6:0]      |         |       |           |           |        |              |          |  |

|        |          | 31:24    |                    |         |       |           |           |        | ADDRMASK[9:7 | ]        |  |

| 000    | DATA     | 7:0      |                    |         |       | DAT       | ſA[7:0]   |        |              |          |  |

| 0x28   | DATA     | 15:8     |                    |         |       |           |           |        |              |          |  |

## 37.8 Register Description - I<sup>2</sup>C Slave

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 37.5.8 Register Access Protection.

# SAM L10/L11 Family SERCOM I2C – SERCOM Inter-Integrated Circ...

| CMD[1:0] | DIR                                                                             | R Action                                                                              |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| 0x0      | Х                                                                               | (No action)                                                                           |  |  |  |  |  |

| 0x1      | Х                                                                               | (Reserved)                                                                            |  |  |  |  |  |

| 0x2      | Used to complete a transaction in response to a data interrupt (DRDY)           |                                                                                       |  |  |  |  |  |

|          | 0 (Master write)                                                                | write) Execute acknowledge action succeeded by waiting for any start (S/Sr) condition |  |  |  |  |  |

|          | 1 (Master read) Wait for any start (S/Sr) condition                             |                                                                                       |  |  |  |  |  |

| 0x3      | Used in response to an address interrupt (AMATCH)                               |                                                                                       |  |  |  |  |  |

|          | 0 (Master write) Execute acknowledge action succeeded by reception of next byte |                                                                                       |  |  |  |  |  |

|          | 1 (Master read)                                                                 | Execute acknowledge action succeeded by slave data interrupt                          |  |  |  |  |  |

|          | Used in respons                                                                 | e to a data interrupt (DRDY)                                                          |  |  |  |  |  |

|          | 0 (Master write) Execute acknowledge action succeeded by reception of next byte |                                                                                       |  |  |  |  |  |

|          | 1 (Master read)                                                                 | Execute a byte read operation followed by ACK/NACK reception                          |  |  |  |  |  |

#### Table 37-3. Command Description

#### Bits 15:14 - AMODE[1:0] Address Mode

These bits set the addressing mode.

These bits are not write-synchronized.

| Value | Name    | Description                                                                |

|-------|---------|----------------------------------------------------------------------------|

| 0x0   | MASK    | The slave responds to the address written in ADDR.ADDR masked by the value |

|       |         | in ADDR.ADDRMASK.                                                          |

|       |         | See SERCOM – Serial Communication Interface for additional information.    |

| 0x1   | 2_ADDRS | The slave responds to the two unique addresses in ADDR.ADDR and            |

|       |         | ADDR.ADDRMASK.                                                             |

| 0x2   | RANGE   | The slave responds to the range of addresses between and including         |

|       |         | ADDR.ADDR and ADDR.ADDRMASK. ADDR.ADDR is the upper limit.                 |

| 0x3   | -       | Reserved.                                                                  |

#### Bit 10 – AACKEN Automatic Acknowledge Enable

This bit enables the address to be automatically acknowledged if there is an address match.

This bit is not write-synchronized.

| Value | Description                        |

|-------|------------------------------------|

| 0     | Automatic acknowledge is disabled. |

| 1     | Automatic acknowledge is enabled.  |

#### Bit 9 – GCMD PMBus Group Command

This bit enables PMBus group command support. When enabled, the Stop Recived interrupt flag (INTFLAG.PREC) will be set when a STOP condition is detected if the slave has been addressed since the last STOP condition on the bus.

This bit is not write-synchronized.

#### 38.7.1.15 Channel x Compare/Capture Value, 8-bit Mode

Name:CCxOffset:0x1C + x\*0x01 [x=0..1]Reset:0x00Property:Write-Synchronized, Read-Synchronized

| Bit    | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|------|-----|-----|-----|

|        |     |     |     | CC[ | 7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

Bits 7:0 - CC[7:0] Channel x Compare/Capture Value

These bits contain the compare/capture value in 8-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (WAVE.WAVEGEN), the CC0 register is used as a period register.

#### 38.7.3.13 Counter Value, 32-bit Mode

Name:COUNTOffset:0x14Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

**Note:** Prior to any read access, this register must be synchronized by user by writing the according TC Command value to the Control B Set register (CTRLBSET.CMD=READSYNC).

| Bit    | 31  | 30  | 29  | 28   | 27       | 26  | 25  | 24  |

|--------|-----|-----|-----|------|----------|-----|-----|-----|

|        |     |     |     | COUN | [31:24]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

|        |     |     |     |      |          |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19       | 18  | 17  | 16  |

|        |     |     |     | COUN | Г[23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

|        |     |     |     |      |          |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11       | 10  | 9   | 8   |

|        |     |     |     | COUN | T[15:8]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

|        |     |     |     |      |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3        | 2   | 1   | 0   |

|        |     |     |     | COUN | IT[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

Bits 31:0 - COUNT[31:0] Counter Value

These bits contain the current counter value.

# SAM L10/L11 Family

DAC – Digital-to-Analog Converter

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Internal DAC output not enabled.                         |

| 1     | Internal DAC output enabled to be used by the AC or ADC. |

Bit 0 – EOEN External Output Enable

| Va | alue | Description                                                                     |

|----|------|---------------------------------------------------------------------------------|

| 0  |      | The DAC output is turned off.                                                   |

| 1  |      | The high-drive output buffer drives the DAC output to the V <sub>OUT</sub> pin. |

## AC and DC Characteristics Graphs

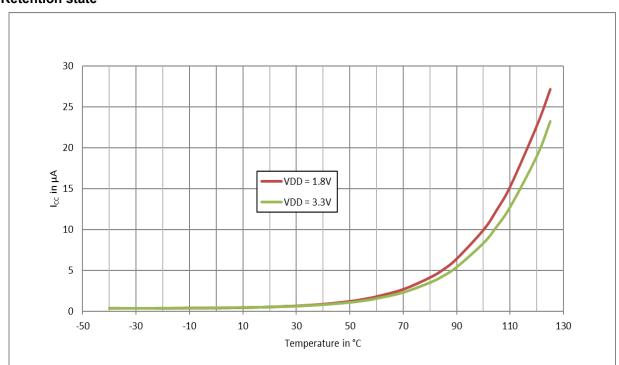

# Figure 48-5. Power Consumption over Temperature in Standby Sleep Mode with PDSW in Retention state

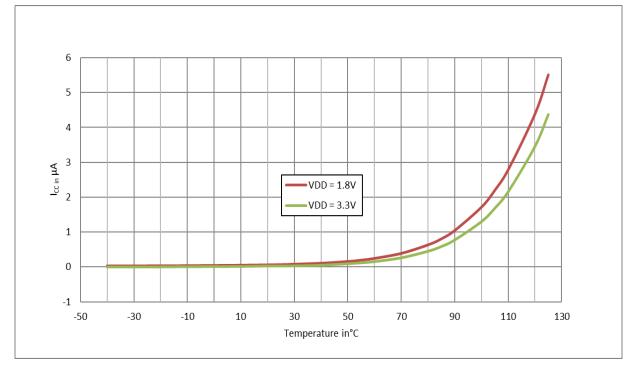

### Power Consumption in Off Sleep Mode

Operating conditions:

• VDDIO = 3.3V or 1.8V

Figure 48-6. Power Consumption over Temperature in Off Sleep Mode

WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2017, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-3156-5

# Quality Management System Certified by DNV

#### ISO/TS 16949

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and

© 2018 Microchip Technology Inc.