#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d14a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SAM L10/L11 Family SAM L11 Security Features

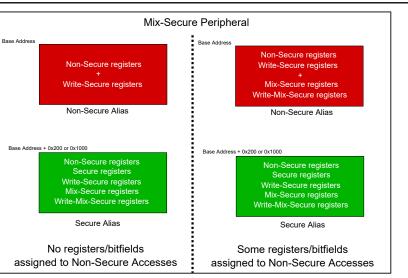

Mix-Secure peripherals have always the following registers:

- NONSEC register is a generic register that tells the Non-Secure application which resources inside a Mix-Secure peripheral can be used

- NSCHK register is a register allowing the Non-Secure application to be notified when the security configuration of a Mix-Secure peripheral is being modified during application execution

**Important:** It is recommended that the Non-Secure application first copy the content of NONSEC register inside NSCHK register, and then enable the NSCHK interrupt flags. Once done, any changes to the NONSEC register by the Secure application will trigger an interrupt so that Non-Secure application can take appropriate actions. This mechanism allows the Secure application to dynamically change the security attribution of a Mix-Secure peripheral and avoid illegal accesses from the Non-Secure application. The interrupt handler should always copy the NONSEC register to NSCHK register before exiting it.

Mix-Secure peripherals can have five type of registers:

- Non-Secure: these registers will always be available in both the Secure and Non-Secure aliases

- Secure: these registers will never be available in the Non-Secure alias and always available in the Secure alias

- Write-Secure: these are registers than can:

- Be written or read by the Secure application only in the Secure alias

- Only read by the Non-Secure application in Non-Secure alias. Write is forbidden.

- **Mix-Secure** registers : these ones are used when a resource can be allocated to either the Secure and Non-Secure alias

- Note that, in some cases, the Mix-Secure properties apply to a bitfield only (like one I/O bit in the PORT peripheral register)

- Write-Mix-Secure registers (NVMCTRL peripheral only): these are Mix-Secure registers, which:

- can be written or read by the Secure application only in the Secure alias

- can only be read by the Non-Secure application in Non-Secure alias <u>except</u> if Non-Secure writes are authorized in NVMCTRL.NONSEC register

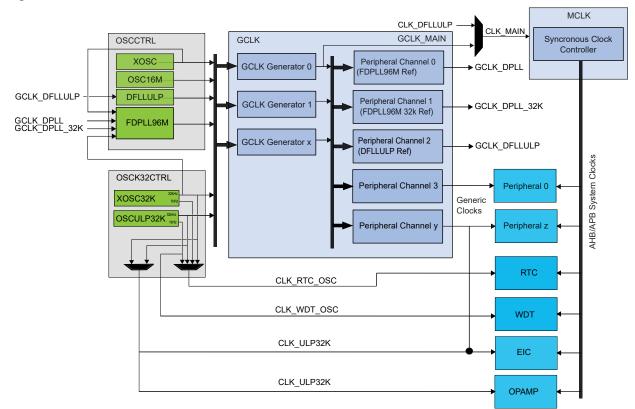

# 17. Clock System

This chapter summarizes the clock distribution and terminology in the SAM L10/L11 device. This document will not explain every detail of its configuration, hence for in-depth details, refer to the respective peripherals descriptions and the *Generic Clock* documentation.

# 17.1 Clock Distribution

Figure 17-1. Clock Distribution

The SAM L10/L11 clock system consists of these features:

- Clock sources, that is oscillators controlled by OSCCTRL and OSC32KCTRL

- A clock source provides a time base that is used by other components, such as Generic Clock Generators. Example clock sources are the internal 16MHz oscillator (OSC16M), external crystal oscillator (XOSC) and the Fractional Digital Phase Locked Loop (FDPLL96M).

- *Generic Clock Controller (GCLK),* which generates, controls and distributes the asynchronous clock consisting of:

- Generic Clock Generators: These are programmable prescalers that can use any of the system clock sources as a time base. The Generic Clock Generator 0 generates the clock signal GCLK\_MAIN, which is used by the Power Manager and the Main Clock (MCLK) module, which in turn generates synchronous clocks.

- Generic Clocks: These are clock signals generated by Generic Clock Generators and output by the Peripheral Channels, and serve as clocks for the peripherals of the system. Multiple instances of a peripheral will typically have a separate Generic Clock for each instance.

After enabling OSC16M, the OSC16M clock is output as soon as the oscillator is ready (STATUS.OSC16MRDY=1). User must ensure that the OSC16M is fully disabled before enabling it by reading STATUS.OSC16MRDY=0.

After reset, OSC16M is enabled and serves as the default clock source at 4MHz.

OSC16M will behave differently in different sleep modes based on the settings of OSC16MCTRL.RUNSTDBY, OSC16MCTRL.ONDEMAND, and OSC16MCTRL.ENABLE. If OSC16MCTRL.ENABLE=0, the OSC16M will be always stopped. For OSC16MCTRL.ENABLE=1, this table is valid:

| CPU Mode       | OSC16MCTRL.RUN<br>STDBY | OSC16MCTRL.OND<br>EMAND | Sleep Behavior                 |

|----------------|-------------------------|-------------------------|--------------------------------|

| Active or Idle | -                       | 0                       | Always run                     |

| Active or Idle | -                       | 1                       | Run if requested by peripheral |

| Standby        | 1                       | 0                       | Always run                     |

| Standby        | 1                       | 1                       | Run if requested by peripheral |

| Standby        | 0                       | -                       | Run if requested by peripheral |

#### Table 23-2. OSC16M Sleep Behavior

OSC16M is used as a clock source for the generic clock generators. This is configured by the Generic Clock Generator Controller.

#### **Related Links**

18. GCLK - Generic Clock Controller

# 23.6.5 Ultra Low-Power Digital Frequency Locked Loop (DFLLULP) Operation

The Ultra Low-Power Digital Frequency Locked Loop (DFLLULP) is an internal oscillator that can output a selectable frequency based on user inputs. The frequency is a multiplication ratio relative to a given reference clock using the tuning feature. The oscillator has to be enabled for the tuner to work.

#### Figure 23-2. Block Diagram

#### 23.6.5.1 Basic Operation

# 23.6.5.1.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the DFLLULP is disabled (DFLLULPCTRL.ENABLE is zero):

- Binary Search Enable bit in Control register (DFLLULPCTRL.BINSE)

- Safe Mode bit in Control register (DFLLULPCTRL.SAFE)

- Dither Mode bit in Control register (DFLLULPCTRL.DITHER)

- Division Factor bits in Control register (DFLLULPCTRL.DIV)

The following registers are enable-protected:

- Dither Control register (DFLLULPDITHER)

- Target Ratio register (DFLLULPRATIO)

Enable-protected bits in the DFLLULPCTRL register can be written at the same time as DFLLULPCTRL.ENABLE is written to one, but not at the same time as DFLLULPCTRL.ENABLE is written to zero.

# SAM L10/L11 Family OSC32KCTRL – 32KHz Oscillators Controller

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x08<br>0x00000000<br>- |    |    |    |         |    |            |

|--------|-----------------------------------------|------------------------------------|----|----|----|---------|----|------------|

| Bit    | 31                                      | 30                                 | 29 | 28 | 27 | 26      | 25 | 24         |

|        |                                         |                                    |    |    |    |         |    |            |

| Access |                                         |                                    |    |    |    |         |    |            |

| Reset  |                                         |                                    |    |    |    |         |    |            |

| Bit    | 23                                      | 22                                 | 21 | 20 | 19 | 18      | 17 | 16         |

|        |                                         |                                    |    |    |    |         |    |            |

| Access |                                         |                                    |    |    |    |         |    |            |

| Reset  |                                         |                                    |    |    |    |         |    |            |

| Bit    | 15                                      | 14                                 | 13 | 12 | 11 | 10      | 9  | 8          |

|        |                                         |                                    |    |    |    |         |    |            |

| Access |                                         |                                    |    |    |    |         |    |            |

| Reset  |                                         |                                    |    |    |    |         |    |            |

| Bit    | 7                                       | 6                                  | 5  | 4  | 3  | 2       | 1  | 0          |

|        |                                         |                                    |    |    |    | CLKFAIL |    | XOSC32KRDY |

| Access |                                         |                                    |    |    |    | R/W     |    | R/W        |

| Reset  |                                         |                                    |    |    |    | 0       |    | 0          |

# 24.8.3 Interrupt Flag Status and Clear

Bit 2 – CLKFAIL XOSC32K Clock Failure Detection

This flag is cleared by writing a '1' to it.

This flag is set on a zero-to-one transition of the XOSC32K Clock Failure Detection bit in the Status register (STATUS.CLKFAIL) and will generate an interrupt request if INTENSET.CLKFAIL is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Clock Failure Detection flag.

# Bit 0 – XOSC32KRDY XOSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the XOSC32K Ready bit in the Status register (STATUS.XOSC32KRDY), and will generate an interrupt request if INTENSET.XOSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the XOSC32K Ready interrupt flag.

#### 25.8.1 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|----|----|----|----|------------|----------|----------|----------|

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 23 | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 15 | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |    |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |    |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |    |    |    |    | 0          | 0        |          | 0        |

|        |    |    |    |    |            |          |          |          |

| Bit    | 7  | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |    |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access | -  |    |    |    |            | R/W      | R/W      | R/W      |

| Reset  |    |    |    |    |            | 0        | 0        | 0        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit will clear on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY).

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Low Power Ready interrupt is disabled.                                                                                     |

| 1     | The Low Power Ready interrupt is enabled and an interrupt request will be generated when the ULPVREFRDY Interrupt Flag is set. |

Bit 10 – VCORERDY VDDCORE Voltage Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the VDDCORE Ready Interrupt Enable bit, which disables the VDDCORE Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The VDDCORE Ready interrupt is disabled.                                                                                   |

| 1     | The VDDCORE Ready interrupt is enabled and an interrupt request will be generated when the VCORERDY Interrupt Flag is set. |

# 26.8.2 Configuration

| Name:     | CONFIG                                               |

|-----------|------------------------------------------------------|

| Offset:   | 0x01                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection                                 |

| Bit    | 7           | 6   | 5   | 4        | 3   | 2   | 1   | 0   |

|--------|-------------|-----|-----|----------|-----|-----|-----|-----|

|        | WINDOW[3:0] |     |     | PER[3:0] |     |     |     |     |

| Access | R/W         | R/W | R/W | R/W      | R/W | R/W | R/W | R/W |

| Reset  | х           | x   | x   | x        | х   | x   | x   | x   |

#### Bits 7:4 – WINDOW[3:0] Window Mode Time-Out Period

In Window mode, these bits determine the watchdog closed window period as a number of cycles of the 1.024kHz CLK\_WDT\_OSC clock.

These bits are loaded from NVM User Row at start-up.

| Value   | Name     | Description        |

|---------|----------|--------------------|

| 0x0     | CYC8     | 8 clock cycles     |

| 0x1     | CYC16    | 16 clock cycles    |

| 0x2     | CYC32    | 32 clock cycles    |

| 0x3     | CYC64    | 64 clock cycles    |

| 0x4     | CYC128   | 128 clock cycles   |

| 0x5     | CYC256   | 256 clock cycles   |

| 0x6     | CYC512   | 512 clock cycles   |

| 0x7     | CYC1024  | 1024 clock cycles  |

| 0x8     | CYC2048  | 2048 clock cycles  |

| 0x9     | CYC4096  | 4096 clock cycles  |

| 0xA     | CYC8192  | 8192 clock cycles  |

| 0xB     | CYC16384 | 16384 clock cycles |

| 0xC-0xF | Reserved | Reserved           |

# Bits 3:0 – PER[3:0] Time-Out Period

These bits determine the watchdog time-out period as a number of 1.024kHz CLK\_WDTOSC clock cycles. In Window mode operation, these bits define the open window period.

These bits are loaded from NVM User Row at startup.

| Value | Name    | Description       |

|-------|---------|-------------------|

| 0x0   | CYC8    | 8 clock cycles    |

| 0x1   | CYC16   | 16 clock cycles   |

| 0x2   | CYC32   | 32 clock cycles   |

| 0x3   | CYC64   | 64 clock cycles   |

| 0x4   | CYC128  | 128 clock cycles  |

| 0x5   | CYC256  | 256 clock cycles  |

| 0x6   | CYC512  | 512 clock cycles  |

| 0x7   | CYC1024 | 1024 clock cycles |

| 0x8   | CYC2048 | 2048 clock cycles |

# 27.6.8 Additional Features

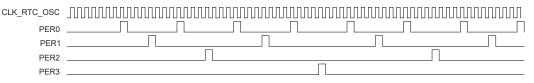

#### 27.6.8.1 Periodic Intervals

The RTC prescaler can generate interrupts and events at periodic intervals, allowing flexible system tick creation. Any of the upper eight bits of the prescaler (bits 2 to 9) can be the source of an interrupt/event. When one of the eight Periodic Event Output bits in the Event Control register (EVCTRL.PEREO[n=0..7]) is '1', an event is generated on the 0-to-1 transition of the related bit in the prescaler, resulting in a periodic event frequency of:

$$f_{\text{PERIODIC}(n)} = \frac{f_{\text{CLK}_{\text{RTC}_{\text{OSC}}}}}{2^{n+3}}$$

$f_{CLK\_RTC\_OSC}$  is the frequency of the internal prescaler clock CLK\_RTC\_OSC, and n is the position of the EVCTRL.PEREOn bit. For example, PER0 will generate an event every eight CLK\_RTC\_OSC cycles, PER1 every 16 cycles, etc. This is shown in the figure below.

Periodic events are independent of the prescaler setting used by the RTC counter, except if CTRLA.PRESCALER is zero. Then, no periodic events will be generated.

#### Figure 27-5. Example Periodic Events

#### 27.6.8.2 Frequency Correction

The RTC Frequency Correction module employs periodic counter corrections to compensate for a tooslow or too-fast oscillator. Frequency correction requires that CTRLA.PRESCALER is greater than 1.

The digital correction circuit adds or subtracts cycles from the RTC prescaler to adjust the frequency in approximately 1ppm steps. Digital correction is achieved by adding or skipping a single count in the prescaler once every 8192 CLK\_RTC\_OSC cycles. The Value bit group in the Frequency Correction register (FREQCORR.VALUE) determines the number of times the adjustment is applied over 128 of these periods. The resulting correction is as follows:

Correction in ppm  $= \frac{\text{FREQCORR.VALUE}}{8192 \cdot 128} \cdot 10^6 \text{ppm}$

This results in a resolution of 0.95367ppm.

The Sign bit in the Frequency Correction register (FREQCORR.SIGN) determines the direction of the correction. A positive value will add counts and increase the period (reducing the frequency), and a negative value will reduce counts per period (speeding up the frequency).

Digital correction also affects the generation of the periodic events from the prescaler. When the correction is applied at the end of the correction cycle period, the interval between the previous periodic event and the next occurrence may also be shortened or lengthened depending on the correction value.

# 27.6.8.3 General Purpose Registers

The RTC includes four General Purpose registers (GPn). These registers are reset only when the RTC is reset or when tamper detection occurs while CTRLA.GPTRST=1, and remain powered while the RTC is powered. They can be used to store user-defined values while other parts of the system are powered off.

The general purpose registers 2\*n and 2\*n+1 are enabled by writing a '1' to the General Purpose Enable bit n in the Control B register (CTRLB.GPnEN).

© 2018 Microchip Technology Inc.

# SAM L10/L11 Family

RTC – Real-Time Counter

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x0C<br>0x0000<br>- |      |      |      |      |      |        |

|--------|-----------------------------------------|--------------------------------|------|------|------|------|------|--------|

| Bit    | 15                                      | 14                             | 13   | 12   | 11   | 10   | 9    | 8      |

|        | OVF                                     | TAMPER                         |      |      |      |      |      | ALARM0 |

| Access | R/W                                     | R/W                            |      |      |      |      |      | R/W    |

| Reset  | 0                                       | 0                              |      |      |      |      |      | 0      |

|        |                                         |                                |      |      |      |      |      |        |

| Bit    | 7                                       | 6                              | 5    | 4    | 3    | 2    | 1    | 0      |

|        | PER7                                    | PER6                           | PER5 | PER4 | PER3 | PER2 | PER1 | PER0   |

| Access | R/W                                     | R/W                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W    |

| Reset  | 0                                       | 0                              | 0    | 0    | 0    | 0    | 0    | 0      |

# 27.12.6 Interrupt Flag Status and Clear in Clock/Calendar mode (CTRLA.MODE=2)

# Bit 15 – OVF Overflow

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after an overflow condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

#### Bit 14 – TAMPER Tamper

This flag is set after a tamper condition occurs, and an interrupt request will be generated if INTENCLR.TAMPER/INTENSET.TAMPER is '1'. Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the Tamper interrupt flag.

#### Bit 8 – ALARM0 Alarm 0

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with the compare condition, and an interrupt request will be generated if INTENCLR/SET.ALARM0 is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Alarm 0 interrupt flag.

# Bits 0, 1, 2, 3, 4, 5, 6, 7 – PERn Periodic Interval n [n = 7..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the 0-to-1 transition of prescaler bit [n+2], and an interrupt request will be generated if INTENCLR/SET.PERx is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Periodic Interval n interrupt flag.

- The transfer descriptor must be made valid by writing a one to the Valid bit in the Block Transfer Control register (BTCTRL.VALID)

- Number of beats in the block transfer must be selected by writing the Block Transfer Count (BTCNT) register

- Source address for the block transfer must be selected by writing the Block Transfer Source Address (SRCADDR) register

- Destination address for the block transfer must be selected by writing the Block Transfer Destination Address (DSTADDR) register

If CRC calculation is needed, the CRC engine must be configured before it is enabled, as outlined by the following steps:

- The CRC input source must selected by writing the CRC Input Source bit group in the CRC Control register (CRCCTRL.CRCSRC)

- The type of CRC calculation must be selected by writing the CRC Polynomial Type bit group in the CRC Control register (CRCCTRL.CRCPOLY)

- If I/O is selected as input source, the beat size must be selected by writing the CRC Beat Size bit group in the CRC Control register (CRCCTRL.CRCBEATSIZE)

# 28.6.2.2 Enabling, Disabling, and Resetting

The DMAC is enabled by writing the DMA Enable bit in the Control register (CTRL.DMAENABLE) to '1'. The DMAC is disabled by writing a '0' to CTRL.DMAENABLE.

A DMA channel is enabled by writing the Enable bit in the Channel Control A register (CHCTRLA.ENABLE) to '1', after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). A DMA channel is disabled by writing a '0' to CHCTRLA.ENABLE.

The CRC is enabled by writing a '1' to the CRC Enable bit in the Control register (CTRL.CRCENABLE). The CRC is disabled by writing a '0' to CTRL.CRCENABLE.

The DMAC is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST) while the DMAC and CRC are disabled. All registers in the DMAC except DBGCTRL will be reset to their initial state.

A DMA channel is reset by writing a '1' to the Software Reset bit in the Channel Control A register (CHCTRLA.SWRST), after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). The channel registers will be reset to their initial state. The corresponding DMA channel must be disabled in order for the reset to take effect.

# 28.6.2.3 Transfer Descriptors

Together with the channel configurations the transfer descriptors decides how a block transfer should be executed. Before a DMA channel is enabled (CHCTRLA.ENABLE is written to one), and receives a transfer trigger, its first transfer descriptor has to be initialized and valid (BTCTRL.VALID). The first transfer descriptor describes the first block transfer of a transaction.

All transfer descriptors must reside in SRAM. The addresses stored in the Descriptor Memory Section Base Address (BASEADDR) and Write-Back Memory Section Base Address (WRBADDR) registers tell the DMAC where to find the descriptor memory section and the write-back memory section.

The descriptor memory section is where the DMAC expects to find the first transfer descriptors for all DMA channels. As BASEADDR points only to the first transfer descriptor of channel 0 (see figure below), all first transfer descriptors must be stored in a contiguous memory section, where the transfer descriptors must be ordered according to their channel number. For further details on linked descriptors, refer to 28.6.3.1 Linked Descriptors.

#### 29.8.14 Security Attribution Check

| Name:     | NSCHK                |

|-----------|----------------------|

| Offset:   | 0x3C                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to select one or more external pins to check their security attribution as nonsecured.

|        | <b>&gt;</b> | Important: | This register i | s only availab | ble for SAM L | <b>11</b> and has no | o effect for <b>S</b> / | AM L10.  |

|--------|-------------|------------|-----------------|----------------|---------------|----------------------|-------------------------|----------|

|        |             |            |                 |                |               |                      |                         |          |

| Bit    | 31          | 30         | 29              | 28             | 27            | 26                   | 25                      | 24       |

|        | NMI         |            |                 |                |               |                      |                         |          |

| Access | RW/RW/RW    |            |                 |                |               |                      |                         |          |

| Reset  | 0           |            |                 |                |               |                      |                         |          |

|        |             |            |                 |                |               |                      |                         |          |

| Bit    | 23          | 22         | 21              | 20             | 19            | 18                   | 17                      | 16       |

|        |             |            |                 |                |               |                      |                         |          |

| Access |             |            |                 |                |               |                      |                         |          |

| Reset  |             |            |                 |                |               |                      |                         |          |

| Bit    | 15          | 14         | 13              | 12             | 11            | 10                   | 9                       | 8        |

| ы.     | 10          | 14         | 13              | 12             | 11            | 10                   | 9                       | 0        |

| Access |             |            |                 |                |               |                      |                         |          |

| Reset  |             |            |                 |                |               |                      |                         |          |

| 110301 |             |            |                 |                |               |                      |                         |          |

| Bit    | 7           | 6          | 5               | 4              | 3             | 2                    | 1                       | 0        |

| [      |             |            |                 | EXTIN          | NT[7:0]       |                      |                         |          |

| Access | RW/RW/RW    | RW/RW/RW   | RW/RW/RW        | RW/RW/RW       | RW/RW/RW      | RW/RW/RW             | RW/RW/RW                | RW/RW/RW |

| Reset  | 0           | 0          | 0               | 0              | 0             | 0                    | 0                       | 0        |

|        |             |            |                 |                |               |                      |                         |          |

Bit 31 – NMI Non-Maskable Interrupt Security Attribution Check

This bit selects the Non-Maskable Interrupt pin for security attribution check. If the NMI bit in NONSECNMI is set to the opposite value, then the NSCHK interrupt flag will be set.

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | 0-to-1 transition will be detected on corresponding NONSEC bit. |

| 1     | 1-to-0 transition will be detected on corresponding NONSEC bit. |

# Bits 7:0 – EXTINT[7:0] External Interrupts Security Attribution Check

These bits select the individual pins for security attribution check. If any pin selected in NSCHK has the corresponding bit in NONSEC set to the opposite value, then the NSCHK interrupt flag will be set.

#### 30.8.13 Data Scramble Control

| Name:     | DSCC                                           |

|-----------|------------------------------------------------|

| Offset:   | 0x30                                           |

| Reset:    | 0x0000000                                      |

| Property: | PAC Write-Protection, Secure, Enable-Protected |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

| Bit    | 31    | 30    | 29    | 28    | 27       | 26       | 25    | 24    |

|--------|-------|-------|-------|-------|----------|----------|-------|-------|

|        |       |       |       |       | DSCKE    | Y[29:24] |       |       |

| Access |       |       | W/-/W | W/-/W | W/-/W    | W/-/W    | W/-/W | W/-/W |

| Reset  |       |       | 0     | 0     | 0        | 0        | 0     | 0     |

|        |       |       |       |       |          |          |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19       | 18       | 17    | 16    |

| [      |       |       |       | DSCKE | Y[23:16] |          |       |       |

| Access | W/-/W | W/-/W | W/-/W | W/-/W | W/-/W    | W/-/W    | W/-/W | W/-/W |

| Reset  | 0     | 0     | 0     | 0     | 0        | 0        | 0     | 0     |

|        |       |       |       |       |          |          |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11       | 10       | 9     | 8     |

| [      |       |       |       | DSCKE | Y[15:8]  |          |       |       |

| Access | W/-/W | W/-/W | W/-/W | W/-/W | W/-/W    | W/-/W    | W/-/W | W/-/W |

| Reset  | 0     | 0     | 0     | 0     | 0        | 0        | 0     | 0     |

|        |       |       |       |       |          |          |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3        | 2        | 1     | 0     |

| [      |       |       |       | DSCK  | EY[7:0]  |          |       |       |

| Access | W/-/W | W/-/W | W/-/W | W/-/W | W/-/W    | W/-/W    | W/-/W | W/-/W |

| Reset  | 0     | 0     | 0     | 0     | 0        | 0        | 0     | 0     |

|        |       |       |       |       |          |          |       |       |

#### Bits 29:0 – DSCKEY[29:0] Data Scramble Key

This key value is used for data scrambling of the Secure Data Flash. After reset the key is 0. When written, the new value in the register is an XOR of the value written and the previous value of DSCC.DSCKEY.

This register is write only and will always read back as zero.

This register is Enable-Protected with SECCTRL.DSCEN meaning that it can't be modified when DSCEN=1 otherwise a PAC error is generated.

Updated DSCC.DSCKEY contents <- DSCC.DSCKEY XOR value written.

#### 31.8.8 Permutation Write

Name:PERMWOffset:0x010Reset:0x00Property:PAC Write-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1         | 0 |

|--------|---|---|---|---|---|---|-----------|---|

|        |   |   |   |   |   |   | DATA[2:0] |   |

| Access |   |   |   |   |   | W | W         | W |

| Reset  |   |   |   |   |   | 0 | 0         | 0 |

|        |   |   |   |   |   |   |           |   |

**Bits 2:0 – DATA[2:0]** Permutation Write Data Data is the input value for the scrambler permutation function:

PERMR.DATA = Permutate(PERMW.DATA, DSCC.DSCKEY)

These bits will always return zero when read.

#### 32.8.7 Data Output Value Set

| Name:     | OUTSET                           |

|-----------|----------------------------------|

| Offset:   | 0x18                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

This register allows the user to set one or more output I/O pin drive levels high, without doing a readmodify-write operation. Changes in this register will also be reflected in the Data Output Value (OUT), Data Output Value Toggle (OUTTGL) and Data Output Value Clear (OUTCLR) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31        | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Dir I  | 01        |           | 20        |           | T[31:24]  | 20        | 20        |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        | -         | -         | -         | -         | -         | -         | -         | -         |

| Bit    | 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |           |           |           | OUTSE     | T[23:16]  |           |           |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |           |           |           |           |           |           |           |           |

| Bit    | 15        | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

|        |           |           |           | OUTSE     | T[15:8]   |           |           |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |           |           |           |           |           |           |           |           |

| Bit    | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|        |           |           |           | OUTS      | ET[7:0]   |           |           |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

# Bits 31:0 – OUTSET[31:0] PORT Data Output Value Set

Writing '0' to a bit has no effect.

# Bits 17:16 – TXPO[1:0] Transmit Data Pinout

These bits define the transmit data (TxD) and XCK pin configurations.

This bit is not synchronized.

| ТХРО | TxD Pin Location | XCK Pin Location (When<br>Applicable) | RTS/TE        | стѕ           |

|------|------------------|---------------------------------------|---------------|---------------|

| 0x0  | SERCOM PAD[0]    | SERCOM PAD[1]                         | N/A           | N/A           |

| 0x1  | SERCOM PAD[2]    | SERCOM PAD[3]                         | N/A           | N/A           |

| 0x2  | SERCOM PAD[0]    | N/A                                   | SERCOM PAD[2] | SERCOM PAD[3] |

| 0x3  | SERCOM_PAD[0]    | SERCOM_PAD[1]                         | SERCOM_PAD[2] | N/A           |

# Bits 15:13 – SAMPR[2:0] Sample Rate

These bits select the sample rate.

These bits are not synchronized.

| SAMPR[2:0] | Description                                              |

|------------|----------------------------------------------------------|

| 0x0        | 16x over-sampling using arithmetic baud rate generation. |

| 0x1        | 16x over-sampling using fractional baud rate generation. |

| 0x2        | 8x over-sampling using arithmetic baud rate generation.  |

| 0x3        | 8x over-sampling using fractional baud rate generation.  |

| 0x4        | 3x over-sampling using arithmetic baud rate generation.  |

| 0x5-0x7    | Reserved                                                 |

# Bit 10 - RXINV Receive Data Invert

This bit controls whether the receive data (RxD) is inverted or not.

**Note:** Start, parity and stop bit(s) are unchanged. When enabled, parity is calculated on the inverted data.

| Value | Description          |

|-------|----------------------|

| 0     | RxD is not inverted. |

| 1     | RxD is inverted.     |

# Bit 9 – TXINV Transmit Data Invert

This bit controls whether the transmit data (TxD) is inverted or not.

**Note:** Start, parity and stop bit(s) are unchanged. When enabled, parity is calculated on the inverted data.

| Value | Description          |

|-------|----------------------|

| 0     | TxD is not inverted. |

| 1     | TxD is inverted.     |

# Bit 8 – IBON Immediate Buffer Overflow Notification

This bit controls when the buffer overflow status bit (STATUS.BUFOVF) is asserted when a buffer overflow occurs.

This bit has no effect when input capture operation is enabled.

| Value | Description                                                                            |  |  |  |  |

|-------|----------------------------------------------------------------------------------------|--|--|--|--|

| 0     | The CCBUFx and PERBUF buffer registers value are copied into CCx and PER registers on  |  |  |  |  |

|       | hardware update condition.                                                             |  |  |  |  |

| 1     | The CCBUFx and PERBUF buffer registers value are not copied into CCx and PER registers |  |  |  |  |

|       | on hardware update condition.                                                          |  |  |  |  |

#### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|

| 0     | The timer/counter is counting up (incrementing).   |  |  |  |  |

| 1     | The timer/counter is counting down (decrementing). |  |  |  |  |

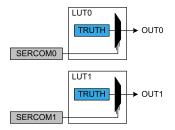

#### Figure 40-11. SERCOM Input Selection

# **Related Links**

- 32. PORT I/O Pin Controller

- 18. GCLK Generic Clock Controller

- 42. AC Analog Comparators

- 38. TC Timer/Counter

- 34. SERCOM Serial Communication Interface

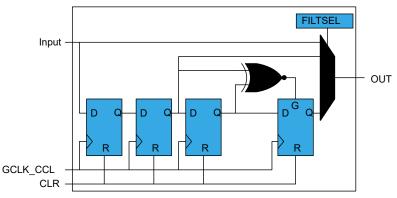

#### 40.6.2.5 Filter

By default, the LUT output is a combinatorial function of the LUT inputs. This may cause some short glitches when the inputs change value. These glitches can be removed by clocking through filters, if demanded by application needs.

The Filter Selection bits in LUT Control register (LUTCTRLx.FILTSEL) define the synchronizer or digital filter options. When a filter is enabled, the OUT output will be delayed by two to five GCLK cycles. One APB clock after the corresponding LUT is disabled, all internal filter logic is cleared. **Note:** Events used as LUT input will also be filtered, if the filter is enabled.

#### Figure 40-12. Filter

# 40.6.2.6 Edge Detector

The edge detector can be used to generate a pulse when detecting a rising edge on its input. To detect a falling edge, the TRUTH table should be inverted.

The edge detector is enabled by writing '1' to the Edge Selection bit in LUT Control register (LUTCTRLx.EDGESEL). In order to avoid unpredictable behavior, either the filter or synchronizer must be enabled.

Edge detection is disabled by writing a '0' to LUTCTRLx.EDGESEL. After disabling a LUT, the corresponding internal Edge Detector logic is cleared one APB clock cycle later.

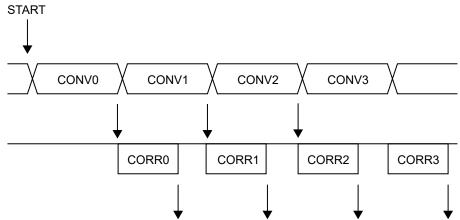

(OFFSETCORR). The offset correction value is subtracted from the converted data before writing the Result register (RESULT).

The gain error is defined as the deviation of the last output step's midpoint from the ideal straight line, after compensating for offset error. The gain error cancellation is handled by the Gain Correction register (GAINCORR).

To correct these two errors, the Digital Correction Logic Enabled bit in the Control C register (CTRLC.CORREN) must be set.

Offset and gain error compensation results are both calculated according to:

Result =  $(Conversion value + - OFFSETCORR) \cdot GAINCORR$

The correction will introduce a latency of 13 CLK\_ADC clock cycles. In free running mode this latency is introduced on the first conversion only, since its duration is always less than the propagation delay. In single conversion mode this latency is introduced for each conversion.

# Figure 41-8. ADC Timing Correction Enabled

# 41.6.2.15 Reference Buffer Compensation Offset

A hardware compensation using a reference buffer can be used.

When the REFCTRL.REFCOMP bit is set, the offset of the reference buffer is sensed during the ADC sampling phase. This offset will be then cancelled during the conversion phase. This feature allows to decrease the overall gain error of the ADC.

There is also a digital gain correction (refer to Offset and gain correction chapter) but contrary to that digital gain correction, the hardware compensation won't introduce any latency.

# 41.6.3 Additional Features

# 41.6.3.1 Double Buffering

The following registers are double buffered:

- Input Control (INPUTCTRL)

- Control C (CTRLC)

- Average Control (AVGCTRL)

- Sampling Time Control (SAMPCTRL)

- Window Monitor Lower Threshold (WINLT)

- Window Monitor Upper Threshold (WINUT)

# 42.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access |   |   |   |   |   |   | R/W    | W     |

| Reset  |   |   |   |   |   |   | 0      | 0     |

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from updating the register until the peripheral is enabled/disabled. The value written to CTRL.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the peripheral is enabled/disabled.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The AC is disabled.                                                                       |

| 1     | The AC is enabled. Each comparator must also be enabled individually by the Enable bit in |

|       | the Comparator Control register (COMPCTRLn.ENABLE).                                       |

#### Bit 0 – SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the AC to their initial state, and the AC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 43.8.6 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x06Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | EMPTY | UNDERRUN |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

#### Bit 1 – EMPTY Data Buffer Empty

This flag is cleared by writing a '1' to it or by writing new data to DATABUF.

This flag is set when data is transferred from DATABUF to DATA, and the DAC is ready to receive new data in DATABUF, and will generate an interrupt request if INTENCLR/SET.EMPTY is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Empty interrupt flag.

#### Bit 0 – UNDERRUN Underrun

This flag is cleared by writing a '1' to it.

This flag is set when a start conversion event occurs when DATABUF is empty, and will generate an interrupt request if INTENCLR/SET.UNDERRUN is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Underrun interrupt flag.

# **52.** Acronyms and Abbreviations

The below table contains acronyms and abbreviations used in this document.

# Table 52-1. Acronyms and Abbreviations

| Abbreviation | Description                                         |  |  |  |

|--------------|-----------------------------------------------------|--|--|--|

| AC           | Analog Comparator                                   |  |  |  |

| ADC          | Analog-to-Digital Converter                         |  |  |  |

| ADDR         | Address                                             |  |  |  |

| AES          | Advanced Encryption Standard                        |  |  |  |

| АНВ          | Advanced High-performance Bus                       |  |  |  |

| AMBA         | Advanced Microcontroller Bus Architecture           |  |  |  |

| APB          | AMBA Advanced Peripheral Bus                        |  |  |  |

| AREF         | Analog Reference Voltage                            |  |  |  |

| BOD          | Brown-out Detector                                  |  |  |  |

| CAL          | Calibration                                         |  |  |  |

| CC           | Compare/Capture                                     |  |  |  |

| CCL          | Configurable Custom Logic                           |  |  |  |

| CLK          | Clock                                               |  |  |  |

| CRC          | Cyclic Redundancy Check                             |  |  |  |

| CTRL         | Control                                             |  |  |  |

| DAC          | Digital-to-Analog Converter                         |  |  |  |

| DAP          | Debug Access Port                                   |  |  |  |

| DFLL         | Digital Frequency Locked Loop                       |  |  |  |

| DPLL         | Digital Phase Locked Loop                           |  |  |  |

| DMAC         | DMA (Direct Memory Access) Controller               |  |  |  |

| DSU          | Device Service Unit                                 |  |  |  |

| EEPROM       | Electrically Erasable Programmable Read-Only Memory |  |  |  |

| EIC          | External Interrupt Controller                       |  |  |  |

| EVSYS        | Event System                                        |  |  |  |

| FDPLL        | Fractional Digital Phase Locked Loop, also DPLL     |  |  |  |

| FREQM        | Frequency Meter                                     |  |  |  |

| GCLK         | Generic Clock Controller                            |  |  |  |

| GND Ground   |                                                     |  |  |  |

|              |                                                     |  |  |  |