#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

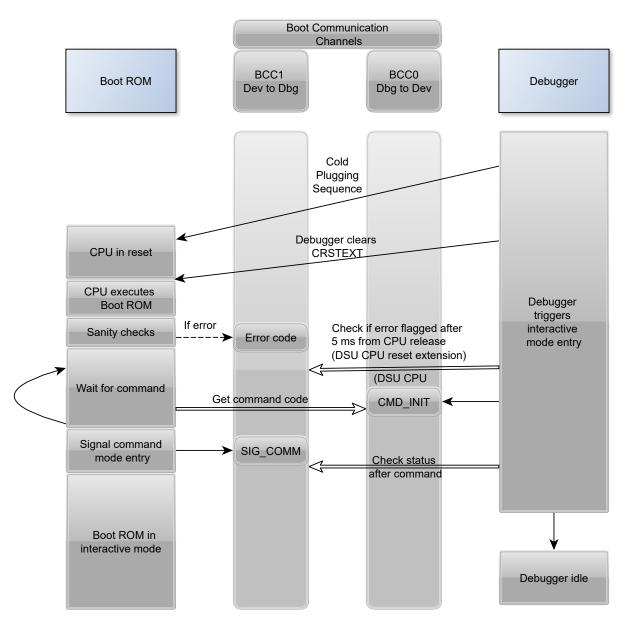

# 14.4.5.1.1 CMD\_INIT

Figure 14-7. CMD\_INIT Flow diagram

### 14.4.5.2 Exit Interactive Mode (CMD\_EXIT)

This command allows exiting the Boot Interactive mode.

Exiting the Boot Interactive mode allows to jump to one of the following:

- The Application

- The CPU Park Mode

# 15.7.13 Peripheral Non-Secure Status - Bridge B

| Name:     | NONSECB                                              |

|-----------|------------------------------------------------------|

| Offset:   | 0x58                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | Write-Secure                                         |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

#### Reading NONSEC register returns peripheral security attribution status:

|                 | Value |    | Description       |            |       |         |       |       |

|-----------------|-------|----|-------------------|------------|-------|---------|-------|-------|

|                 | 0     |    | Peripheral is see | cured.     |       |         |       |       |

|                 | 1     |    | Peripheral is not | n-secured. |       |         |       |       |

| Bit             | 31    | 30 | 29                | 28         | 27    | 26      | 25    | 24    |

| Access          |       |    |                   |            |       |         |       |       |

| Reset           |       |    |                   |            |       |         |       |       |

| Bit             | 23    | 22 | 21                | 20         | 19    | 18      | 17    | 16    |

| Access          |       |    |                   |            |       |         |       |       |

| Reset           |       |    |                   |            |       |         |       |       |

| Bit             | 15    | 14 | 13                | 12         | 11    | 10      | 9     | 8     |

| A               |       |    |                   |            |       |         |       |       |

| Access<br>Reset |       |    |                   |            |       |         |       |       |

| Bit             | 7     | 6  | 5                 | 4          | 3     | 2       | 1     | 0     |

|                 |       |    |                   | HMATRIXHS  | DMAC  | NVMCTRL | DSU   | IDAU  |

| Access          |       |    |                   | R/R/R      | R/R/R | R/R/R   | R/R/R | R/R/R |

| Reset           |       |    |                   | x          | x     | 0       | 1     | 0     |

Bit 4 – HMATRIXHS Peripheral HMATRIXHS Non-Secure

Bit 3 – DMAC Peripheral DMAC Non-Secure

**Bit 2 – NVMCTRL** Peripheral NVMCTRL Non-Secure The NVMCTRL Peripheral is always secured.

**Bit 1 – DSU** Peripheral DSU Non-Secure The DSU Peripheral is always non-secured.

© 2018 Microchip Technology Inc.

#### 16.6.3 Debugger Probe Detection

#### 16.6.3.1 Cold Plugging

Cold-Plugging is the detection of a debugger when the system is in reset. Cold-Plugging is detected when the CPU reset extension is requested, as described above.

#### 16.6.3.2 Hot Plugging

Hot-Plugging is the detection of a debugger probe when the system is not in reset. Hot-Plugging is not possible under reset because the detector is reset when POR or RESET are asserted. Hot-Plugging is active when a SWCLK falling edge is detected. The SWCLK pad is multiplexed with other functions and the user must ensure that its default function is assigned to the debug system. If the SWCLK function is changed, the Hot-Plugging feature is disabled until a power-reset or external reset occurs. Availability of the Hot-Plugging feature can be read from the Hot-Plugging Enable bit of the Status B register (STATUSB.HPE).

#### Figure 16-3. Hot-Plugging Detection Timing Diagram

| SWCLK        |       |         |  |

|--------------|-------|---------|--|

| RESET        |       |         |  |

| CPU_STATE    | reset | running |  |

| Hot-Plugging |       | Π       |  |

The presence of a debugger probe is detected when either Hot-Plugging or Cold-Plugging is detected. Once detected, the Debugger Present bit of the Status B register (STATUSB.DBGPRES) is set. For security reasons, Hot-Plugging is not available when DAL equals to 0x0.

This detection requires that pads are correctly powered. Thus, at cold startup, this detection cannot be done until POR is released. If DAL equals 0x0, Cold-Plugging is the only way to detect a debugger probe, and so the external reset timing must be longer than the POR timing. If external reset is de-asserted before POR release, the user must retry the procedure above until it gets connected to the device.

#### **Related Links**

30. NVMCTRL – Nonvolatile Memory Controller

## 16.6.4 Boot Communication Channels

Boot Communication Channels allow communication between a debug adapter and the CPU executing the Boot ROM at startup. The Boot ROM implements system level commands. Refer to 14. Boot ROM for more information.

# 16.7 **Programming**

Programming the Flash or RAM memories is only possible when the debugger access level is sufficient to access the desired resource:

If DAL is equal to:

- 0x2: debugger can access secured and non-secure areas

- 0x1 (SAM L11 only): debugger can access only non-secure areas, refer to Table 16-4.

# DSU - Device Service Unit

### 16.12.21 Peripheral Identification 3

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID3<br>0x1FEC<br>0x00000000<br>- |         |    |    |    |         |    |

|--------|-----------------------------------------|-----------------------------------|---------|----|----|----|---------|----|

| Bit    | 31                                      | 30                                | 29      | 28 | 27 | 26 | 25      | 24 |

|        |                                         |                                   |         |    |    |    |         |    |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

|        |                                         |                                   |         |    |    |    |         |    |

| Bit    | 23                                      | 22                                | 21      | 20 | 19 | 18 | 17      | 16 |

|        |                                         |                                   |         |    |    |    |         |    |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Bit    | 15                                      | 14                                | 13      | 12 | 11 | 10 | 9       | 8  |

| DIL    | 15                                      | 14                                | 13      | 12 | 11 | 10 | 9       | 0  |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Bit    | 7                                       | 6                                 | 5       | 4  | 3  | 2  | 1       | 0  |

|        |                                         |                                   | ND[3:0] |    |    |    | DD[3:0] |    |

| Access | R                                       | R                                 | R       | R  | R  | R  | R       | R  |

| Reset  | 0                                       | 0                                 | 0       | 0  | 0  | 0  | 0       | 0  |

|        |                                         |                                   |         |    |    |    |         |    |

**Bits 7:4 – REVAND[3:0]** Revision Number These bits will always return 0x0 when read.

Bits 3:0 – CUSMOD[3:0] ARM CUSMOD

These bits will always return 0x0 when read.

#### 24.5.3 Clocks

The OSC32KCTRL gathers controls for all 32KHz oscillators and provides clock sources to the Generic Clock Controller (GCLK), Real-Time Counter (RTC), and Watchdog Timer (WDT).

The available clock sources are: XOSC32K and OSCULP32K.

The OSC32KCTRL bus clock (CLK\_OSC32KCTRL\_APB) can be enabled and disabled in the Main Clock module (MCLK).

#### **Related Links**

19.6.2.6 Peripheral Clock Masking

#### 24.5.4 Interrupts

The interrupt request lines are connected to the interrupt controller. Using the OSC32KCTRL interrupts requires the interrupt controller to be configured first.

#### 24.5.5 Events

The events of this peripheral are connected to the Event System.

#### Related Links

33. EVSYS – Event System

#### 24.5.6 Debug Operation

When the CPU is halted in debug mode, OSC32KCTRL will continue normal operation. If OSC32KCTRL is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 24.5.7 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

• Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

# 24.5.8 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

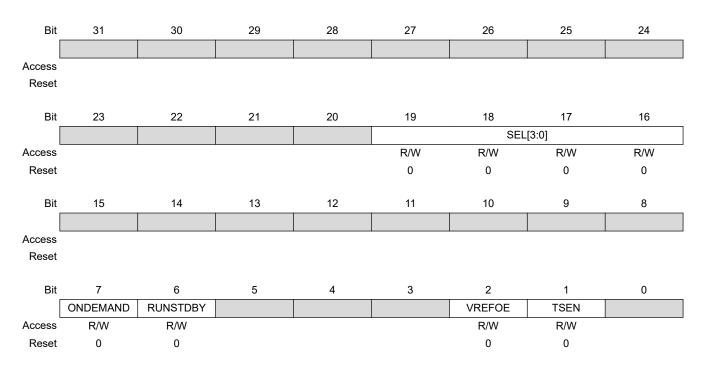

#### 25.8.7 Voltage References System (VREF) Control

| Name:     | VREF                 |

|-----------|----------------------|

| Offset:   | 0x1C                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

**Bits 19:16 – SEL[3:0]** Voltage Reference Selection These bits select the Voltage Reference for the ADC/DAC.

| Value  | Name | Description                                                                          |

|--------|------|--------------------------------------------------------------------------------------|

| 0x0    | 1V0  | 1.0V voltage reference typical value                                                 |

| 0x1    | 1V1  | 1.1V voltage reference typical valueThe 1.1V voltage reference typical value must be |

|        |      | selected for DAC use. Other values are not permitted.                                |

| 0x2    | 1V2  | 1.2V voltage reference typical value                                                 |

| 0x3    | 1V25 | 1.25V voltage reference typical value                                                |

| 0x4    | 2V0  | 2.0V voltage reference typical value                                                 |

| 0x5    | 2V2  | 2.2V voltage reference typical value                                                 |

| 0x6    | 2V4  | 2.4V voltage reference typical value                                                 |

| 0x7    | 2V5  | 2.5V voltage reference typical value                                                 |

| Others |      | Reserved                                                                             |

### Bit 7 - ONDEMAND On Demand Control

The On Demand operation mode allows to enable or disable the voltage reference depending on peripheral requests.

# SAM L10/L11 Family

# RTC – Real-Time Counter

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Tamper event output is disabled, and will not be generated.                   |

| 1     | Tamper event output is enabled, and will be generated for every tamper input. |

#### Bits 8, 9 – CMPEOn Compare n Event Output Enable [n = 1..0]

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | Compare n event is disabled and will not be generated.                    |

| 1     | Compare n event is enabled and will be generated for every compare match. |

# Bits 0, 1, 2, 3, 4, 5, 6, 7 – PEREOn Periodic Interval n Event Output Enable [n = 7..0]

| Value | Description                                                      |

|-------|------------------------------------------------------------------|

| 0     | Periodic Interval n event is disabled and will not be generated. |

| 1     | Periodic Interval n event is enabled and will be generated.      |

#### 27.10.4 Interrupt Enable Clear in COUNT16 mode (CTRLA.MODE=1)

Name:INTENCLROffset:0x08Reset:0x0000Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 15          | 14          | 13          | 12          | 11          | 10          | 9           | 8           |

|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|        | OVF         | TAMPER      |             |             |             |             |             |             |

| Access | R/W         | R/W         |             |             |             |             |             |             |

| Reset  | 0           | 0           |             |             |             |             |             |             |

|        |             |             |             |             |             |             |             |             |

| Bit    | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|        |             |             |             |             |             |             |             |             |

|        | PER7        | PER6        | PER5        | PER4        | PER3        | PER2        | CMP1        | CMP0        |

| Access | PER7<br>R/W | PER6<br>R/W | PER5<br>R/W | PER4<br>R/W | PER3<br>R/W | PER2<br>R/W | CMP1<br>R/W | CMP0<br>R/W |

#### Bit 15 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### **Bit 14 – TAMPER** Tamper Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Tamper Interrupt Enable bit, which disables the Tamper interrupt.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The Tamper interrupt is disabled. |

| 1     | The Tamper interrupt is enabled.  |

#### Bits 0, 1 – CMPn Compare n Interrupt Enable [n = 1..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Compare n Interrupt Enable bit, which disables the Compare n interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The Compare n interrupt is disabled. |

| 1     | The Compare n interrupt is enabled.  |

### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PERn Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Periodic Interval n Interrupt Enable bit, which disables the Periodic Interval n interrupt.

| Va | lue | Description                                |

|----|-----|--------------------------------------------|

| 0  |     | Periodic Interval n interrupt is disabled. |

| 1  |     | Periodic Interval n interrupt is enabled.  |

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 2 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 2 priority. |

### Bits 19:16 – LVLPRI2[3:0] Level 2 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN2=1) for priority level 2, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 2.

When static arbitration is enabled (PRICTRL0.RRLVLEN2=0) for priority level 2, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN2 written to '0').

### Bit 15 – RRLVLEN1 Level 1 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to 28.6.2.4 Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 1 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 1 priority. |

## Bits 11:8 – LVLPRI1[3:0] Level 1 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN1=1) for priority level 1, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 1.

When static arbitration is enabled (PRICTRL0.RRLVLEN1=0) for priority level 1, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN1 written to '0').

### Bit 7 – RRLVLEN0 Level 0 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to 28.6.2.4 Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 0 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 0 priority. |

### Bits 3:0 – LVLPRI0[3:0] Level 0 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN0=1) for priority level 0, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 0.

When static arbitration is enabled (PRICTRL0.RRLVLEN0=0) for priority level 0, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN0 written to '0').

#### 28.10.1 Block Transfer Control

| Name:     | BTCTRL |

|-----------|--------|

| Offset:   | 0x00   |

| Property: | -      |

The BTCTRL register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 15            | 14 | 13 | 12      | 11       | 10     | 9             | 8     |

|--------|---------------|----|----|---------|----------|--------|---------------|-------|

|        | STEPSIZE[2:0] |    |    | STEPSEL | DSTINC   | SRCINC | BEATSIZE[1:0] |       |

| Access |               |    |    |         |          |        |               |       |

| Reset  |               |    |    |         |          |        |               |       |

|        |               |    |    |         |          |        |               |       |

| Bit    | 7             | 6  | 5  | 4       | 3        | 2      | 1             | 0     |

|        |               |    |    | BLOCKA  | ACT[1:0] | EVOSI  | EL[1:0]       | VALID |

| Access |               | •  |    |         |          |        |               | ••    |

Reset

#### Bits 15:13 – STEPSIZE[2:0] Address Increment Step Size

These bits select the address increment step size. The setting apply to source or destination address, depending on STEPSEL setting.

| Value | Name | Description                                  |

|-------|------|----------------------------------------------|

| 0x0   | X1   | Next ADDR = ADDR + (Beat size in byte) * 1   |

| 0x1   | X2   | Next ADDR = ADDR + (Beat size in byte) * 2   |

| 0x2   | X4   | Next ADDR = ADDR + (Beat size in byte) * 4   |

| 0x3   | X8   | Next ADDR = ADDR + (Beat size in byte) * 8   |

| 0x4   | X16  | Next ADDR = ADDR + (Beat size in byte) * 16  |

| 0x5   | X32  | Next ADDR = ADDR + (Beat size in byte) * 32  |

| 0x6   | X64  | Next ADDR = ADDR + (Beat size in byte) * 64  |

| 0x7   | X128 | Next ADDR = ADDR + (Beat size in byte) * 128 |

#### Bit 12 – STEPSEL Step Selection

This bit selects if source or destination addresses are using the step size settings.

| Value | Name | Description                                         |

|-------|------|-----------------------------------------------------|

| 0x0   | DST  | Step size settings apply to the destination address |

| 0x1   | SRC  | Step size settings apply to the source address      |

#### Bit 11 – DSTINC Destination Address Increment Enable

Writing a '0' to this bit will disable the destination address incrementation. The address will be kept fixed during the data transfer.

Writing a '1' to this bit will enable the destination address incrementation. By default, the destination address is incremented by 1. If the STEPSEL bit is cleared, flexible step-size settings are available in the STEPSIZE register.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Destination Address Increment is disabled. |

| 1     | The Destination Address Increment is enabled.  |

# 30. NVMCTRL – Nonvolatile Memory Controller

# 30.1 Overview

Non-Volatile Memory (NVM) is a reprogrammable Flash memory that retains program and data storage even with power off. It embeds three separate arrays namely FLASH, Data FLASH and AUX FLASH. The Data FLASH array can be programmed while reading the FLASH array. It is intended to store data while executing from the FLASH without stalling. AUX FLASH stores data needed during the device startup such as calibration and system configuration. The NVM Controller (NVMCTRL) connects to the AHB and APB bus interfaces for system access to the NVM block. The AHB interface is used for reads and writes to the NVM block, while the APB interface is used for commands and configuration.

# 30.2 Features

- 32-bit AHB interface for reads and writes

- Write-While-Read (WWR) Data Flash

- All NVM Sections are Memory Mapped to the AHB, Including Calibration and System Configuration

- 32-bit APB Interface for Commands and Control

- Programmable Wait States for Read Optimization

- 6 Regions can be Individually Protected or Unprotected

- Additional Protection for Bootloader

- Interface to Power Manager for Power-Down of Flash Blocks in Sleep Modes

- Can Optionally Wake-up on Exit from Sleep or on First Access

- Direct-mapped Cache

- TrustZone Support (SAM L11)

**Note:** A register with property "Enable-Protected" may contain bits that are *not* enable-protected.

#### 30.8.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG          |

|-----------|------------------|

| Offset:   | 0x14             |

| Reset:    | 0x00             |

| Property: | Write-Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

| Bit    | 7 | 6 | 5         | 4         | 3         | 2         | 1         | 0         |

|--------|---|---|-----------|-----------|-----------|-----------|-----------|-----------|

|        |   |   | NSCHK     | KEYE      | NVME      | LOCKE     | PROGE     | DONE      |

| Access |   |   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  |   |   | 0         | 0         | 0         | 0         | 0         | 0         |

### Bit 5 – NSCHK Non-Secure Check

This flag is set when the NONSEC register is changed and the new value differs from the NSCHK value.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | The NONSEC configuration has not changed since last clear.                          |

| 1     | At least one change has been made to the NONSEC configuration since the last clear. |

### Bit 4 – KEYE Key Error

This flag is set when a key write-protected register has been accessed in write with a bad key. A one indicates that at least one write access has been discarded.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | No key error occured since the last clear.           |

| 1     | At least one key error occured since the last clear. |

#### Bit 3 – NVME NVM internal Error

This flag is set on the occurrence of a NVM internal error.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | No NVM internal error has happened since this bit was last cleared.           |

| 1     | At least one NVM internal error has happened since this bit was last cleared. |

### Bit 2 – LOCKE Lock Error

This flag is set on the occurrence of a LOCKE error.

This bit can be cleared by writing a '1' to its bit location.

The tamper full erase routine operates at the highest priority. If a remanence routine executing when a tamper full erase occurs, the remanence routine is immediately terminated. If the CPU attempts to write a new scramble key at the same time the tamper key erase routine is active, the CPU data is ignored, but no bus error will occur. If a CPU security routine access is requested during a tamper full erase, the CPU transaction will be ignored and treated as a bus error similar to accessing the module during a software reset.

**Important:** In STANDBY low power mode, it is mandatory to enable the dynamic power gating feature (STDBYCFG.DPGPDSW) to ensure TrustRAM erasing when the power domain PDSW is in a retention state.

## 31.6.3 Interrupts

The TRAM has the following interrupt sources:

- Data Remanence Prevention (DRP): Indicates that the data remanence prevention routine has ended.

- Data Read Error (ERR): Indicates when there is a RAM readout error.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TRAM is reset. See 22.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

### 31.6.4 Sleep Mode Operation

The TRAM continues to operate during sleep. When it receives events from the Event System, it will request its own clock in order to perform the requested operation.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering an interrupt. In this case, the CPU will continue executing from the instruction following the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *EVSYS – Event System* for more information.

### 31.6.5 Synchronization

Due to the asynchronicity between event sources and CLK\_TRAM\_APB some registers must be synchronized when accessed. A register can require:

Synchronization when written

#### 33.7.4 Channel Pending Interrupt

| Name:     | INTPEND |

|-----------|---------|

| Offset:   | 0x10    |

| Reset:    | 0x4000  |

| Property: | Secure  |

An interrupt that handles several channels should consult the INTPEND register to find out which channel number has priority (ignoring/filtering each channel that has its own interrupt line). An interrupt dedicated to only one channel must not use the INTPEND register.

| Bit    | 15    | 14    | 13 | 12 | 11 | 10 | 9                | 8       |

|--------|-------|-------|----|----|----|----|------------------|---------|

|        | BUSY  | READY |    |    |    |    | EVD              | OVR     |

| Access | R/-/R | R/-/R |    |    |    |    | RW/-/RW          | RW/-/RW |

| Reset  | 0     | 1     |    |    |    |    | 0                | 0       |

|        |       |       |    |    |    |    |                  |         |

| Bit    | 7     | 6     | 5  | 4  | 3  | 2  | 1                | 0       |

|        |       |       |    |    |    |    | ID[ <sup>*</sup> | 1:0]    |

| Access |       |       |    |    |    |    | RW/-/RW          | RW/-/RW |

| Reset  |       |       |    |    |    |    | 0                | 0       |

### Bit 15 - BUSY Busy

This bit is read '1' when the event on a channel selected by Channel ID field (ID) has not been handled by all the event users connected to this channel.

#### Bit 14 – READY Ready

This bit is read '1' when all event users connected to the channel selected by Channel ID field (ID) are ready to handle incoming events on this channel.

### Bit 9 - EVD Channel Event Detected

This flag is set on the next CLK\_EVSYS\_APB cycle when an event is being propagated through the channel, and an interrupt request will be generated if CHINTENCLR/SET.EVD is '1'.

When the event channel path is asynchronous, the EVD bit will not be set.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear it. It will also clear the corresponding flag in the Channel n Interrupt Flag Status and Clear register (CHINTFLAGn) of this peripheral, where n is determined by the Channel ID bit field (ID) in this register.

#### Bit 8 – OVR Channel Overrun

This flag is set on the next CLK\_EVSYS cycle after an overrun channel condition occurs, and an interrupt request will be generated if CHINTENCLR/SET.OVRx is '1'.

There are two possible overrun channel conditions:

- One or more of the event users on channel selected by Channel ID field (ID) are not ready when a new event occurs

- An event happens when the previous event on channel selected by Channel ID field (ID) has not yet been handled by all event users

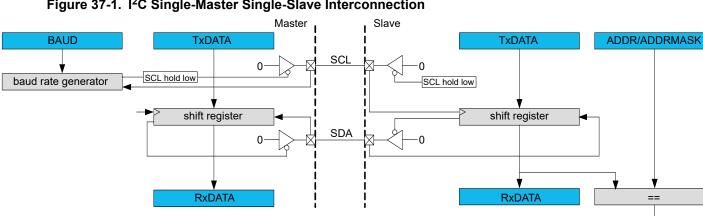

#### 37.3 **Block Diagram**

Figure 37-1. I<sup>2</sup>C Single-Master Single-Slave Interconnection

#### 37.4 Signal Description

| Signal Name | Туре        | Description                |

|-------------|-------------|----------------------------|

| PAD[0]      | Digital I/O | SDA                        |

| PAD[1]      | Digital I/O | SCL                        |

| PAD[2]      | Digital I/O | SDA_OUT (4-wire operation) |

| PAD[3]      | Digital I/O | SCL_OUT (4-wire operation) |

One signal can be mapped on several pins.

Not all the pins are I<sup>2</sup>C pins.

# **Related Links**

37.6.3.3 4-Wire Mode

#### 37.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 37.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

When the SERCOM is used in I<sup>2</sup>C mode, the SERCOM controls the direction and value of the I/O pins. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver or transmitter is disabled, these pins can be used for other purposes.

### **Related Links**

32. PORT - I/O Pin Controller

==

# SAM L10/L11 Family

TC – Timer/Counter

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | The LUPD bit is not affected on overflow/underflow, and re-trigger event. |

| 1     | The LUPD bit is set on each overflow/underflow or re-trigger event.       |

#### Bits 10:8 - PRESCALER[2:0] Prescaler

These bits select the counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

### Bit 7 - ONDEMAND Clock On Demand

This bit selects the clock requirements when the TC is stopped.

In standby mode, if the Run in Standby bit (CTRLA.RUNSTDBY) is '0', ONDEMAND is forced to '0'.

This bit is not synchronized.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The On Demand is disabled. If On Demand is disabled, the TC will continue to request the   |

|       | clock when its operation is stopped (STATUS.STOP=1).                                       |

| 1     | The On Demand is enabled. When On Demand is enabled, the stopped TC will not request       |

|       | the clock. The clock is requested when a software re-trigger command is applied or when an |

|       | event with start/re-trigger action is detected.                                            |

#### Bit 6 – RUNSTDBY Run in Standby

This bit is used to keep the TC running in standby mode.

This bit is not synchronized.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The TC is halted in standby.        |

| 1     | The TC continues to run in standby. |

#### Bits 5:4 - PRESCSYNC[1:0] Prescaler and Counter Synchronization

These bits select whether the counter should wrap around on the next GCLK\_TCx clock or the next prescaled GCLK\_TCx clock. It also makes it possible to reset the prescaler.

These bits are not synchronized.

| Value | Name   | Description                                                                    |

|-------|--------|--------------------------------------------------------------------------------|

| 0x0   | GCLK   | Reload or reset the counter on next generic clock                              |

| 0x1   | PRESC  | Reload or reset the counter on next prescaler clock                            |

| 0x2   | RESYNC | Reload or reset the counter on next generic clock. Reset the prescaler counter |

| 0x3   | -      | Reserved                                                                       |

#### 41.6.2.10 Averaging

Averaging is a feature that increases the sample accuracy, at the cost of a reduced sampling rate. This feature is suitable when operating in noisy conditions.

Averaging is done by accumulating m samples, as described in 41.6.2.9 Accumulation, and dividing the result by m. The averaged result is available in the RESULT register. The number of samples to be accumulated is specified by writing to AVGCTRL.SAMPLENUM as shown in Table 41-2.

The division is obtained by a combination of the automatic right shift described above, and an additional right shift that must be specified by writing to the Adjusting Result/Division Coefficient field in AVGCTRL (AVGCTRL.ADJRES), as described in Table 41-2.

**Note:** To perform the averaging of two or more samples, the Conversion Result Resolution field in the Control C register (CTRLC.RESSEL) must be set.

Averaging AVGCTRL.SAMPLENUM samples will reduce the un-averaged sampling rate by a factor

#### AVGCTRL.SAMPLENUM

When the averaged result is available, the INTFLAG.RESRDY bit will be set.

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result<br>Precision | Number of<br>Automatic<br>Right<br>Shifts | Division<br>Factor | AVGCTRL.ADJRES | Total<br>Number<br>of Right<br>Shifts | Final<br>Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|--------------------|----------------|---------------------------------------|------------------------------|---------------------------------|

| 1                                   | 0x0                   | 12 bits                             | 0                                         | 1                  | 0x0            |                                       | 12 bits                      | 0                               |

| 2                                   | 0x1                   | 13                                  | 0                                         | 2                  | 0x1            | 1                                     | 12 bits                      | 0                               |

| 4                                   | 0x2                   | 14                                  | 0                                         | 4                  | 0x2            | 2                                     | 12 bits                      | 0                               |

| 8                                   | 0x3                   | 15                                  | 0                                         | 8                  | 0x3            | 3                                     | 12 bits                      | 0                               |

| 16                                  | 0x4                   | 16                                  | 0                                         | 16                 | 0x4            | 4                                     | 12 bits                      | 0                               |

| 32                                  | 0x5                   | 17                                  | 1                                         | 16                 | 0x4            | 5                                     | 12 bits                      | 2                               |

| 64                                  | 0x6                   | 18                                  | 2                                         | 16                 | 0x4            | 6                                     | 12 bits                      | 4                               |

| 128                                 | 0x7                   | 19                                  | 3                                         | 16                 | 0x4            | 7                                     | 12 bits                      | 8                               |

| 256                                 | 0x8                   | 20                                  | 4                                         | 16                 | 0x4            | 8                                     | 12 bits                      | 16                              |

| 512                                 | 0x9                   | 21                                  | 5                                         | 16                 | 0x4            | 9                                     | 12 bits                      | 32                              |

| 1024                                | 0xA                   | 22                                  | 6                                         | 16                 | 0x4            | 10                                    | 12 bits                      | 64                              |

| Reserved                            | 0xB –0xF              |                                     |                                           |                    | 0x0            |                                       | 12 bits                      | 0                               |

#### Table 41-2. Averaging

#### 41.6.2.11 Oversampling and Decimation

By using oversampling and decimation, the ADC resolution can be increased from 12 bits up to 16 bits, for the cost of reduced effective sampling rate.

To increase the resolution by n bits, 4<sup>n</sup> samples must be accumulated. The result must then be rightshifted by n bits. This right-shift is a combination of the automatic right-shift and the value written to AVGCTRL.ADJRES. To obtain the correct resolution, the ADJRES must be configured as described in the table below. This method will result in n bit extra LSB resolution.

# SAM L10/L11 Family

**AC – Analog Comparators**

- Software Reset bit in control register (CTRLA.SWRST)

- Enable bit in control register (CTRLA.ENABLE)

- Enable bit in Comparator Control register (COMPCTRLn.ENABLE)

The following registers are synchronized when written:

• Window Control register (WINCTRL)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

### 44.6.4 Interrupts

Not applicable.

## 44.6.5 Events

Not applicable.

# 44.6.6 Sleep Mode Operation

The OPAMPs can also be used during sleep modes. The 32KHz clock source used by the voltage doubler must remain active. See Voltage Doubler for more details.

Each OPAMP x can be configured to behave differently in different sleep modes. The behavior is determined by the individual Run in Standby and On Demand bits in the OPAMP Control x registers (OPAMPCTRLx.RUNSTDBY, and OPAMPCTRLx.ONDEMAND), as well as the common Enable bit in the Control A register (CTRLA.ENABLE).

## Table 44-1. Individual OPAMP Sleep Mode Operation

| OPAMPCTRLx.RUNSTDBY | OPAMPCTRLx.ONDEMAND | CTRLA.ENABLE | Sleep Behavior                                                                      |

|---------------------|---------------------|--------------|-------------------------------------------------------------------------------------|

| -                   | -                   | 0            | Disabled                                                                            |

| 0                   | 0                   | 1            | Always run in all sleep modes except STANDBY sleep mode                             |

| 0                   | 1                   | 1            | Only run in all sleep modes except STANDBY sleep mode if requested by a peripheral. |

| 1                   | 0                   | 1            | Always run in all sleep mode                                                        |

| 1                   | 1                   | 1            | Only run in all sleep modes if requested by a peripheral.                           |

### Note:

When OPAMPCTRLx.ONDEMAND=1, the analog block is powered off for the lowest power consumption if it is not requested.

When requested, a start-up time delay is necessary when the system returns from sleep. The start-up time is depending on the Bias Selection bits in the OPAMP Control x register (OPAMPCTRLx.BIAS) and the corresponding speed/current consumption requirements.

# 44.6.7 Synchronization

Not applicable.

# 44.6.8 Configuring the Operational Amplifiers

Each individual operational amplifier is configured by its respective Operational Amplifier Control x register (OPAMPCTRLx). These settings must be configured before the amplifier is started.

- Select the positive input in OPAMPCTRLx.MUXPOS

- Select the negative input in OPAMPCTRLx.MUXNEG

- Select RES1EN if resistor ladder is used

- Select the input for the resistor ladder in OPAMPCTRLx.RES1MUX

- Select the potentiometer selection of the resistor ladder in OPAMPCTRLx.POTMUX

- Select the VCC input for the resistor ladder in OPAMPCTRLx.RES2VCC

- · Connect the operational amplifier output to the resistor ladder using OPAMPCTRLx.RES2OUT

- Select the trade-off between speed and energy consumption in OPAMPCTRLx.BIAS

Select RES3TAP as positive input for the OPAMP2 and connect the resistor ladder to OA0OUT by setting the RESCTRL.RES2OUT bit only if OPAMPs are configured as a High Gain Instrumentation Amplifier

### 44.6.9 Standalone Mode

Each operational amplifier can be used as standalone amplifier. In this mode, positive input, negative input and the output are routed from/to external I/Os, requiring external feedback. OPAMPs can also be cascaded to support multiple OPAMP configurations. Refer to Operational Amplifier Control x register (OPAMPCTRLx) for further details on how to configure OPAMP I/Os.

### 44.6.10 Built-in Modes

#### 44.6.10.1 Voltage Follower

In this mode the unity gain path is selected for the negative input. The OPAMPCTRLx register can be configured as follows:

|        | MUXPOS | MUXNEG | RES1MUX | ΡΟΤΜUΧ | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 0000   | 011    | 011     | 000    | 0       | 0       | 0      | 0      |

| OPAMP1 | 0000   | 011    | 011     | 000    | 0       | 0       | 0      | 0      |

| OPAMP2 | 0000   | 011    | 011     | 000    | 0       | 0       | 0      | 0      |

Table 44-2. Configuration - Three Independent Unitary Gain Followers

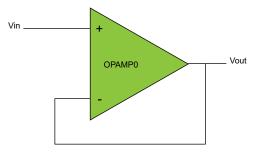

### Figure 44-2. Voltage follower

### 44.6.10.2 Inverting PGA

For inverting programmable gain amplifier operation, the OPAMPCTRLx registers can be configured as follows:

### Table 44-3. Configuration - Three Independent Inverting PGAs

|        | MUXPOS | MUXNEG | RES1MUX | ΡΟΤΜUΧ | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 0010   | 001    | 001     | 100    | 0       | 1       | 1      | 0      |

| OPAMP1 | 0010   | 001    | 001     | 100    | 0       | 1       | 1      | 0      |

| OPAMP2 | 0010   | 001    | 001     | 100    | 0       | 1       | 1      | 0      |

Inverting PGA (Example: Vout=-3.Vin, R1=4R, R2=12R)