#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Memories

| Bit Pos. | Name                      | Usage                                                  | Factory Setting | Related Peripheral Register |

|----------|---------------------------|--------------------------------------------------------|-----------------|-----------------------------|

| 25       | WDT_RUNSTDBY              | WDT Runstdby at power-on                               | 0x0             | WDT.CTRLA                   |

| 26       | WDT_ENABLE                | WDT Enable at power-on                                 | 0x0             | WDT.CTRLA                   |

| 27       | WDT_ALWAYSON              | WDT Always-On at power-on                              | 0x0             | WDT.CTRLA                   |

| 31:28    | WDT_PER                   | WDT Period at power-on                                 | 0xB             | WDT.CONFIG                  |

| 35:32    | WDT_WINDOW                | WDT Window mode time-out at power-on                   | 0xB             | WDT.CONFIG                  |

| 39:36    | WDT_EWOFFSET              | WDT Early Warning Interrupt Time Offset at power-on    | 0xB             | WDT.EWCTRL                  |

| 40       | WDT_WEN                   | WDT Timer Window Mode Enable at power-on               | 0x0             | WDT.CTRLA                   |

| 41       | BOD33_HYST                | BOD33 Hysteresis configuration at power-on             | 0x0             | SUPC.BOD33                  |

| 42       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 43       | RXN                       | RAM is eXecute Never                                   | 0x1             | IDAU.SECCTRL                |

| 44       | DXN                       | Data Flash is eXecute Never                            | 0x1             | NVMCTRL.SECCTRL             |

| 63:45    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 71:64    | AS                        | Flash Application Secure Size = AS*0x100               | 0xFF            | IDAU.SCFGA                  |

| 77:72    | ANSC                      | Flash Application Non-Secure Callable Size = ANSC*0x20 | 0x0             | IDAU.SCFGA                  |

| 79:78    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 83:80    | DS                        | Data Flash Secure Size = DS*0x100                      | 0x8             | IDAU.SCFGA                  |

| 87:84    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 94:88    | RS                        | RAM Secure Size = RS*0x80                              | 0x7F            | IDAU.SCFGR                  |

| 95       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 96       | URWEN                     | User Row Write Enable                                  | 0x1             | NVMCTRL.SCFGAD              |

| 127:97   | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 159:128  | NONSECA <sup>(1)</sup>    | Peripherals Non-Secure Status Fuses for Bridge A       | 0x0000_0000     | PAC.NONSECA                 |

| 191:160  | NONSECB <sup>(2, 3)</sup> | Peripherals Non-Secure Status Fuses for Bridge B       | 0x0000_0000     | PAC.NONSECB                 |

| 223:192  | NONSECC                   | Peripherals Non-Secure Status Fuses for Bridge C       | 0x0000_0000     | PAC.NONSECC                 |

| 255:224  | USERCRC                   | CRC of NVM User Row bits 223:64                        | 0x8433651E      | Boot ROM                    |

#### Note:

- 1. The PAC Peripheral is always secured regardless of its bit value

- 2. The IDAU and NVMCTRL peripherals are always secured regardless of their bit values.

- 3. The DSU peripheral is always non-secured regardless of its bit value.

##

1. BOD12 is calibrated in production and its calibration parameters must not be changed to ensure the correct device behavior.

| Table 10-11. | SAM L11 | UROW | Mapping |

|--------------|---------|------|---------|

|--------------|---------|------|---------|

| Offset | Bit<br>Pos. | Name                         |   |               |  |             |

|--------|-------------|------------------------------|---|---------------|--|-------------|

| 0x00   | 7:0         | BOD33 Level                  | - | NSULCK SULCK  |  | SULCK       |

| 0x01   | 15:8        | BOD33 Action                 |   | BOD33 Disable |  | BOD33 Level |

| 0x02   | 23:16       | BOD12 Calibration Parameters |   |               |  |             |

### **Processor and Architecture**

The priority order for concurrent accesses are decided by two factors:

- As first priority, the QoS level for the master.

- As a second priority, a static priority given by the port ID. The lowest port ID has the highest static priority.

See the tables below for more details.

#### Table 11-8. HS SRAM Port Connections QoS

| HS SRAM Port Connection                                         | Port ID | Connection Type | QoS                                  | default QoS |

|-----------------------------------------------------------------|---------|-----------------|--------------------------------------|-------------|

| DMAC - Direct Memory Access<br>Controller - Write-Back 1 Access | 6       | Direct          | DMAC QOSCTRL.WRBQOS                  | 0x2         |

| DMAC - Direct Memory Access<br>Controller - Write-Back 0 Access | 5       | Direct          | DMAC QOSCTRL.WRBQOS                  | 0x2         |

| DMAC - Direct Memory Access<br>Controller - Fetch 1 Access      | 4       | Direct          | DMAC QOSCTRL.FQOS                    | 0x2         |

| DMAC - Direct Memory Access<br>Controller - Fetch 0 Access      | 3       | Direct          | DMAC QOSCTRL.FQOS                    | 0x2         |

| DMAC - Direct Memory Access<br>Controller - Data Access         | 2       | Bus Matrix      | DMAC QOSCTRL.DQOS                    | 0x2         |

| DSU - Device Service Unit                                       | 1       | Bus Matrix      | DSU CFG.LQOS                         | 0x2         |

| CM23 - Cortex M23 Processor                                     | 0       | Bus Matrix      | 0x41008114, bits[1:0] <sup>(1)</sup> | 0x3         |

#### Note:

1. The CPU QoS level can be written/read, using 32-bit access only.

#### 22. PM - Power Manager

#### 19.5.3 Clocks

The MCLK bus clock (CLK\_MCLK\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_MCLK\_APB can be found in the Peripheral Clock Masking section. If this clock is disabled, it can only be re-enabled by a reset.

The Generic Clock GCLK\_MAIN or the DFLLULP Clock CLK\_DFLLULP is required to generate the Main Clocks. GCLK\_MAIN is configured in the Generic Clock Controller, and can be re-configured by the user if needed. CLK\_DFLLULP is configured in the Oscillators Controller (OSCCTRL).

#### **Related Links**

18. GCLK - Generic Clock Controller19.6.2.6 Peripheral Clock Masking

#### 19.5.3.1 Main Clock

The main clock CLK\_MAIN is the common source for the synchronous clocks. This is fed into the common 8-bit prescaler that is used to generate synchronous clocks to the CPU, AHBx, and APBx modules.

#### 19.5.3.2 CPU Clock

The CPU clock (CLK\_CPU) is routed to the CPU. Halting the CPU clock inhibits the CPU from executing instructions.

#### 19.5.3.3 APBx and AHBx Clock

The APBx clocks (CLK\_APBx) and the AHBx clocks (CLK\_AHBx) are the root clock source used by modules requiring a clock on the APBx and the AHBx bus. These clocks are always synchronous to the CPU clock, and can run even when the CPU clock is turned off in sleep mode. A clock gater is inserted after the common APB clock to gate any APBx clock of a module on APBx bus, as well as the AHBx clock.

#### 19.5.3.4 Clock Domains

The device has these synchronous clock domains:

• CPU synchronous clock domain (CPU Clock Domain). Frequency is f<sub>CPU</sub>.

See also the related links for the clock domain partitioning.

#### **Related Links**

19.6.2.6 Peripheral Clock Masking

#### 19.5.4 DMA

Not applicable.

#### 19.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the MCLK interrupt requires the Interrupt Controller to be configured first.

#### 19.5.6 Events

Not applicable.

### **19.7 Register Summary**

| Offset   | Name      | Bit Pos. |         |          |                |           |          |          |          |          |

|----------|-----------|----------|---------|----------|----------------|-----------|----------|----------|----------|----------|

| 0x00     | CTRLA     | 7:0      |         |          |                |           |          | CKSEL    |          |          |

| 0x01     | INTENCLR  | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x02     | INTENSET  | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x03     | INTFLAG   | 7:0      |         |          |                |           |          |          |          | CKRDY    |

| 0x04     | Reserved  |          |         |          |                |           |          |          |          |          |

| 0x05     | CPUDIV    | 7:0      |         |          |                | CPUD      | IV[7:0]  | 1        |          |          |

| 0x06     |           |          |         |          |                |           |          |          |          |          |

| <br>0x0F | Reserved  |          |         |          |                |           |          |          |          |          |

|          |           | 7:0      | NVMCTRL | PAC      | Reserved       | DSU       | DMAC     | APBC     | APBB     | APBA     |

| 0x10     | AHBMASK   | 15:8     |         |          |                | TRAM      | Reserved | Reserved | Reserved | Reserved |

| 0.00     | AHBMASK   | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          | 7         | 7:0      | GCLK    | SUPC     | OSC32KCTR<br>L | OSCCTRL   | RSTC     | MCLK     | PM       | PAC      |

| 0x14     | APBAMASK  | 15:8     |         | Reserved | AC             | PORT      | FREQM    | EIC      | RTC      | WDT      |

|          |           | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          |           | 7:0      |         |          |                | HMATRIXHS |          | NVMCTRL  | DSU      | IDAU     |

| 0x18     | APBBMASK  | 15:8     |         |          |                |           |          |          |          |          |

| 0,10     | AI DEMAOR | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

|          |           | 7:0      | ADC     | TC2      | TC1            | TC0       | SERCOM2  | SERCOM1  | SERCOM0  | EVSYS    |

| 0x1C     | APBCMASK  | 15:8     |         |          |                | OPAMP     | CCL      | TRNG     | PTC      | DAC      |

|          |           | 23:16    |         |          |                |           |          |          |          |          |

|          |           | 31:24    |         |          |                |           |          |          |          |          |

### 19.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers can be write-protected optionally by the Peripheral Access Controller (PAC). This is denoted by the property "PAC Write-Protection" in each individual register description. Refer to the 19.5.8 Register Access Protection for details.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

**OSCCTRL – Oscillators Controller**

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

## **OSCCTRL – Oscillators Controller**

| Value | Name | Description                     |  |

|-------|------|---------------------------------|--|

| 0x4   | 8MS  | Time-out if no lock within 8ms  |  |

| 0x5   | 9MS  | Time-out if no lock within 9ms  |  |

| 0x6   | 10MS | Time-out if no lock within 10ms |  |

| 0x7   | 11MS | Time-out if no lock within 11ms |  |

**Bits 5:4 – REFCLK[1:0]** Reference Clock Selection Write these bits to select the DPLL clock reference:

| Value | Name     | Description               |

|-------|----------|---------------------------|

| 0x0   | XOSC32K  | XOSC32K clock reference   |

| 0x1   | XOSC     | XOSC clock reference      |

| 0x2   | GCLK     | GCLK_DPLL clock reference |

| 0x3   | Reserved | -                         |

#### Bit 3 - WUF Wake Up Fast

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | DPLL clock is output after startup and lock time. |

| 1     | DPLL clock is output after startup time.          |

#### Bit 2 – LPEN Low-Power Enable

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The low-power mode is disabled. Time to Digital Converter is enabled.                   |

| 1     | The low-power mode is enabled. Time to Digital Converter is disabled. This will improve |

|       | power consumption but increase the output jitter.                                       |

## Bits 1:0 – FILTER[1:0] Proportional Integral Filter Selection

#### These bits select the DPLL filter type:

| Value | Name    | Description           |

|-------|---------|-----------------------|

| 0x0   | DEFAULT | Default filter mode   |

| 0x1   | LBFILT  | Low bandwidth filter  |

| 0x2   | HBFILT  | High bandwidth filter |

| 0x3   | HDFILT  | High damping filter   |

## SUPC – Supply Controller

| Value | Name     | Description           |

|-------|----------|-----------------------|

| 0xA   | DIV2048  | Divide clock by 2048  |

| 0xB   | DIV4096  | Divide clock by 4096  |

| 0xC   | DIV8192  | Divide clock by 8192  |

| 0xD   | DIV16384 | Divide clock by 16384 |

| 0xE   | DIV32768 | Divide clock by 32768 |

| 0xF   | DIV65536 | Divide clock by 65536 |

**Bit 11 – VREFSEL** BOD33 Voltage Reference Selection This bit is not synchronized.

| ſ | Value | Description                    |

|---|-------|--------------------------------|

| Γ | 0     | Selects VREF for the BOD33.    |

|   | 1     | Selects ULPVREF for the BOD33. |

**Bit 8 – ACTCFG** BOD33 Configuration in Active Sleep Mode

This bit is not synchronized.

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | In active mode, the BOD33 operates in continuous mode. |

| 1     | In active mode, the BOD33 operates in sampling mode.   |

#### Bit 6 – RUNSTDBY Run in Standby

This bit is not synchronized.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | In standby sleep mode, the BOD33 is disabled. |

| 1     | In standby sleep mode, the BOD33 is enabled.  |

#### **Bit 5 – STDBYCFG** BOD33 Configuration in Standby Sleep Mode

If the RUNSTDBY bit is set to '1', the STDBYCFG bit sets the BOD33 configuration in standby sleep mode.

This bit is not synchronized.

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | In standby sleep mode, the BOD33 is enabled and configured in continuous mode. |

| 1     | In standby sleep mode, the BOD33 is enabled and configured in sampling mode.   |

#### Bits 4:3 – ACTION[1:0] BOD33 Action

These bits are used to select the BOD33 action when the supply voltage crosses below the BOD33 threshold.

These bits are loaded from NVM User Row at start-up.

This bit field is not synchronized.

| Value | Name  | Description                 |

|-------|-------|-----------------------------|

| 0x0   | NONE  | No action                   |

| 0x1   | RESET | The BOD33 generates a reset |

#### 27.10.14 Tamper Control

| Name:     | TAMPCTRL                               |

|-----------|----------------------------------------|

| Offset:   | 0x60                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31          | 30 | 29          | 28 | 27          | 26      | 25          | 24      |

|--------|-------------|----|-------------|----|-------------|---------|-------------|---------|

|        |             |    |             |    | DEBNC3      | DEBNC2  | DEBNC1      | DEBNC0  |

| Access |             |    | ·           | •  |             |         |             |         |

| Reset  |             |    |             |    | 0           | 0       | 0           | 0       |

|        |             |    |             |    |             |         |             |         |

| Bit    | 23          | 22 | 21          | 20 | 19          | 18      | 17          | 16      |

|        |             |    |             |    | TAMLVL3     | TAMLVL2 | TAMLVL1     | TAMLVL0 |

| Access |             | •  | •           | •  |             |         |             |         |

| Reset  |             |    |             |    | 0           | 0       | 0           | 0       |

|        |             |    |             |    |             |         |             |         |

| Bit    | 15          | 14 | 13          | 12 | 11          | 10      | 9           | 8       |

|        |             |    |             |    |             |         |             |         |

| Access |             | •  | •           |    |             |         |             |         |

| Reset  |             |    |             |    |             |         |             |         |

|        |             |    |             |    |             |         |             |         |

| Bit    | 7           | 6  | 5           | 4  | 3           | 2       | 1           | 0       |

|        | IN3ACT[1:0] |    | IN2ACT[1:0] |    | IN1ACT[1:0] |         | IN0ACT[1:0] |         |

| Access |             |    |             |    |             |         |             |         |

| Reset  | 0           | 0  | 0           | 0  | 0           | 0       | 0           | 0       |

#### Bits 24, 25, 26, 27 - DEBNC Debounce Enable of Tamper Input INn

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Debouncing is disabled for Tamper input INn |

| 1     | Debouncing is enabled for Tamper input INn  |

#### Bits 16, 17, 18, 19 - TAMLVL Tamper Level Select of Tamper Input INn

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | A falling edge condition will be detected on Tamper input INn. |

| 1     | A rising edge condition will be detected on Tamper input INn.  |

## Bits 0:1, 2:3, 4:5, 6:7 - INACT Tamper Channel n Action

These bits determine the action taken by Tamper Channel n.

| Value | Name    | Description                                                          |

|-------|---------|----------------------------------------------------------------------|

| 0x0   | OFF     | Off (Disabled)                                                       |

| 0x1   | WAKE    | Wake and set Tamper flag                                             |

| 0x2   | CAPTURE | Capture timestamp and set Tamper flag                                |

| 0x3   | ACTL    | Compare RTC signal routed between INn and OUT pins . When a mismatch |

|       |         | occurs, capture timestamp and set Tamper flag                        |

#### 28.10.5 Next Descriptor Address

Reset

Name:DESCADDROffset:0x0CProperty:-

The DESCADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 31 | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----|----|----|--------|-----------|----|----|----|

|        |    |    |    | DESCAD | DR[31:24] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |    |    |    | DESCAD | DR[23:16] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |    |    |    | DESCAL | DDR[15:8] |    |    |    |

| Access | L  |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

|        |    |    |    | DESCA  | DDR[7:0]  |    |    |    |

| Access | L  |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

Bits 31:0 – DESCADDR[31:0] Next Descriptor Address

This bit group holds the SRAM address of the next descriptor. The value must be 128-bit aligned. If the value of this SRAM register is 0x00000000, the transaction will be terminated when the DMAC tries to load the next transfer descriptor.

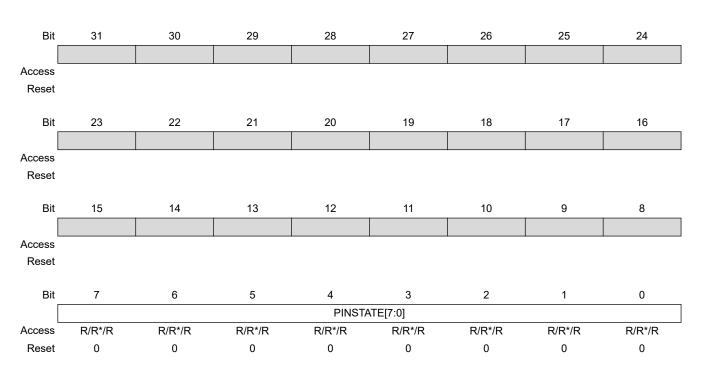

#### 29.8.13 Pin State

| Name:     | PINSTATE       |

|-----------|----------------|

| Offset:   | 0x38           |

| Reset:    | 0x00000000     |

| Property: | PAC Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read accesses (R\*) are allowed only if the external interrupt x (EXTINTx) is set as Non-Secure in the NONSEC register (NONSEC.EXTINTx bit).

#### Bits 7:0 - PINSTATE[7:0] Pin State

These bits return the valid pin state of the debounced external interrupt pin EXTINTx.

## SAM L10/L11 Family PORT - I/O Pin Controller

| 055    |          |          |                 |        |  |       |          |        |      |        |

|--------|----------|----------|-----------------|--------|--|-------|----------|--------|------|--------|

| Offset | Name     | Bit Pos. |                 |        |  |       |          |        |      |        |

| 0x51   | PINCFG17 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x52   | PINCFG18 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x53   | PINCFG19 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x54   | PINCFG20 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x55   | PINCFG21 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x56   | PINCFG22 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x57   | PINCFG23 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x58   | PINCFG24 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x59   | PINCFG25 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5A   | PINCFG26 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5B   | PINCFG27 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5C   | PINCFG28 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5D   | PINCFG29 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5E   | PINCFG30 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

| 0x5F   | PINCFG31 | 7:0      |                 | DRVSTR |  |       |          | PULLEN | INEN | PMUXEN |

|        |          | 7:0      |                 |        |  |       |          |        |      | NSCHK  |

| 0x60   | INTENCLR | 15:8     |                 |        |  |       |          |        |      |        |

| 0,00   | INTENCER | 23:16    |                 |        |  |       |          |        |      |        |

|        |          | 31:24    |                 |        |  |       |          |        |      |        |

|        |          | 7:0      |                 |        |  |       |          |        |      | NSCHK  |

| 0x64   | INTENSET | 15:8     |                 |        |  |       |          |        |      |        |

| 0,04   | INTENSET | 23:16    |                 |        |  |       |          |        |      |        |

|        |          | 31:24    |                 |        |  |       |          |        |      |        |

|        |          | 7:0      |                 |        |  |       |          |        |      | NSCHK  |

| 0x68   | INTFLAG  | 15:8     |                 |        |  |       |          |        |      |        |

| 0,00   |          | 23:16    |                 |        |  |       |          |        |      |        |

|        |          | 31:24    |                 |        |  |       |          |        |      |        |

|        |          | 7:0      |                 |        |  | NONS  | EC[7:0]  |        |      |        |

| 0x6C   | NONSEC   | 15:8     |                 |        |  | NONSE | C[15:8]  |        |      |        |

|        | NONOLU   | 23:16    |                 |        |  | NONSE | C[23:16] |        |      |        |

|        |          | 31:24    | 4 NONSEC[31:24] |        |  |       |          |        |      |        |

|        |          | 7:0      |                 |        |  | NSCH  | IK[7:0]  |        |      |        |

| 0x70   | NSCHK    | 15:8     |                 |        |  |       | K[15:8]  |        |      |        |

| 0.10   | NOOTIN   | 23:16    |                 |        |  | NSCH  | ([23:16] |        |      |        |

|        |          | 31:24    |                 |        |  | NSCH  | ([31:24] |        |      |        |

## 32.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 32.5.8 Register Access Protection.

On SAM L11 devices, the Mix-Secure peripheral has different types of registers (Non-Secure, Secure, Write-Secure, Mix-Secure, and Write-Mix-Secure) with different access permissions for each bitfield.

© 2018 Microchip Technology Inc.

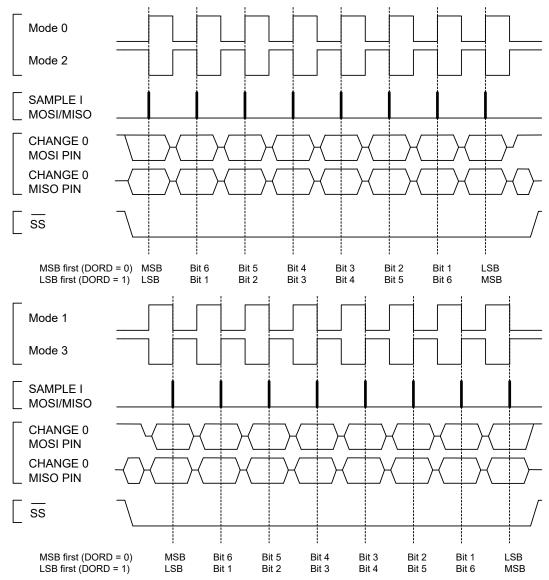

#### Figure 36-3. SPI Transfer Modes

#### 36.6.2.6 Transferring Data

#### 36.6.2.6.1 Master

In master mode (CTRLA.MODE=0x3), when Master Slave Enable Select (CTRLB.MSSEN) is '1', hardware will control the  $\overline{SS}$  line.

When Master Slave Select Enable (CTRLB.MSSEN) is '0', the  $\overline{SS}$  line must be configured as an output.  $\overline{SS}$  can be assigned to any general purpose I/O pin. When the SPI is ready for a data transaction, software must pull the  $\overline{SS}$  line low.

When writing a character to the Data register (DATA), the character will be transferred to the shift register. Once the content of TxDATA has been transferred to the shift register, the Data Register Empty flag in the Interrupt Flag Status and Clear register (INTFLAG.DRE) will be set. And a new character can be written to DATA.

Each time one character is shifted out from the master, another character will be shifted in from the slave simultaneously. If the receiver is enabled (CTRLA.RXEN=1), the contents of the shift register will be

© 2018 Microchip Technology Inc.

## 36.7 Register Summary

| Offset           | Name     | Bit Pos. |          |         |       |        |           |        |             |           |

|------------------|----------|----------|----------|---------|-------|--------|-----------|--------|-------------|-----------|

|                  |          | 7:0      | RUNSTDBY |         |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0.00             |          | 15:8     |          |         |       |        |           |        |             | IBON      |

| 0x00             | CTRLA    | 23:16    |          |         | DIPC  | D[1:0] |           |        | DOPO        | D[1:0]    |

|                  |          | 31:24    |          | DORD    | CPOL  | CPHA   |           | FOR    | V[3:0]      |           |

|                  |          | 7:0      |          | PLOADEN |       |        |           |        | CHSIZE[2:0] |           |

| 004              |          | 15:8     | AMOD     | E[1:0]  | MSSEN |        |           |        | SSDE        |           |

| 0x04             | CTRLB    | 23:16    |          |         |       |        |           |        | RXEN        |           |

|                  |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x08<br><br>0x0B | Reserved |          |          |         |       |        |           |        |             |           |

| 0x0C             | BAUD     | 7:0      |          |         |       | BAU    | D[7:0]    |        |             |           |

| 0x0D             |          |          |          |         |       |        |           |        |             |           |

| <br>0x13         | Reserved |          |          |         |       |        |           |        |             |           |

| 0x14             | INTENCLR | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x15             | Reserved |          |          |         |       |        |           |        |             |           |

| 0x16             | INTENSET | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x17             | Reserved |          |          |         |       |        |           |        |             |           |

| 0x18             | INTFLAG  | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x19             | Reserved |          |          |         |       |        |           |        |             |           |

| 0x1A             | STATUS   | 7:0      |          |         |       |        |           | BUFOVF |             |           |

| UXIA             | 51A105   | 15:8     |          |         |       |        |           |        |             |           |

|                  |          | 7:0      |          |         |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1C             | SYNCBUSY | 15:8     |          |         |       |        |           |        |             |           |

| 0,10             | STREBUET | 23:16    |          |         |       |        |           |        |             |           |

|                  |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x20<br><br>0x23 | Reserved |          |          |         |       |        |           |        |             |           |

|                  |          | 7:0      |          |         |       | ADD    | R[7:0]    |        |             |           |

| 0.04             | 4000     | 15:8     |          |         |       |        |           |        |             |           |

| 0x24             | ADDR     | 23:16    |          |         |       | ADDRM  | 1ASK[7:0] |        |             |           |

|                  |          | 31:24    |          |         |       |        |           |        |             |           |

| 0.00             | DATA     | 7:0      |          |         |       | DAT    | A[7:0]    |        |             |           |

| 0x28             | DATA     | 15:8     |          |         |       |        |           |        |             | DATA[8:8] |

| 0x2A             |          |          |          |         |       |        |           |        |             |           |

|                  | Reserved |          |          |         |       |        |           |        |             |           |

| 0x2F             |          |          |          |         |       |        |           |        |             |           |

| 0x30             | DBGCTRL  | 7:0      |          |         |       |        |           |        |             | DBGSTOP   |

#### 37.10.9 Address

| Name:     | ADDR               |

|-----------|--------------------|

| Offset:   | 0x24               |

| Reset:    | 0x0000             |

| Property: | Write-Synchronized |

| Bit    | 31       | 30  | 29    | 28   | 27     | 26  | 25         | 24  |

|--------|----------|-----|-------|------|--------|-----|------------|-----|

| Access |          |     |       |      |        |     |            |     |

| Reset  |          |     |       |      |        |     |            |     |

|        |          |     |       |      |        |     |            |     |

| Bit    | 23       | 22  | 21    | 20   | 19     | 18  | 17         | 16  |

|        |          |     |       | LEN  | [7:0]  |     |            |     |

| Access | R/W      | R/W | R/W   | R/W  | R/W    | R/W | R/W        | R/W |

| Reset  | 0        | 0   | 0     | 0    | 0      | 0   | 0          | 0   |

|        |          |     |       |      |        |     |            |     |

| Bit    | 15       | 14  | 13    | 12   | 11     | 10  | 9          | 8   |

|        | TENBITEN | HS  | LENEN |      |        |     | ADDR[10:8] |     |

| Access | R/W      | R/W | R/W   |      |        | R/W | R/W        | R/W |

| Reset  | 0        | 0   | 0     |      |        | 0   | 0          | 0   |

|        |          |     |       |      |        |     |            |     |

| Bit    | 7        | 6   | 5     | 4    | 3      | 2   | 1          | 0   |

|        |          |     |       | ADDI | R[7:0] |     |            |     |

| Access | R/W      | R/W | R/W   | R/W  | R/W    | R/W | R/W        | R/W |

| Reset  | 0        | 0   | 0     | 0    | 0      | 0   | 0          | 0   |

#### Bits 23:16 – LEN[7:0] Transaction Length

These bits define the transaction length of a DMA transaction from 0 to 255 bytes. The Transfer Length Enable (LENEN) bit must be written to '1' in order to use DMA.

#### Bit 15 – TENBITEN Ten Bit Addressing Enable

This bit enables 10-bit addressing. This bit can be written simultaneously with ADDR to indicate a 10-bit or 7-bit address transmission.

| Value | Description                 |

|-------|-----------------------------|

| 0     | 10-bit addressing disabled. |

| 1     | 10-bit addressing enabled.  |

#### Bit 14 – HS High Speed

This bit enables High-speed mode for the current transfer from repeated START to STOP. This bit can be written simultaneously with ADDR for a high speed transfer.

| Value | Description                   |

|-------|-------------------------------|

| 0     | High-speed transfer disabled. |

| 1     | High-speed transfer enabled.  |

Bit 13 – LENEN Transfer Length Enable

#### **Bits 3:2 – MODE[1:0]** Timer Counter Mode These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

### ADC – Analog-to-Digital Converter

| CTRLA.RUNSTDBY | CTRLA.ONDEMAND | CTRLA.ENABLE | Description                        |

|----------------|----------------|--------------|------------------------------------|

| 1              | 0              | 1            | Run in all sleep modes.            |

| 1              | 1              | 1            | Run in all sleep modes on request. |

#### 41.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

The following registers are synchronized when written:

- Input Control register (INPUTCTRL)

- Control C register (CTRLC)

- Average control register (AVGCTRL)

- Sampling time control register (SAMPCTRL)

- Window Monitor Lower Threshold register (WINLT)

- Window Monitor Upper Threshold register (WINUT)

- Gain correction register (GAINCORR)

- Offset Correction register (OFFSETCORR)

- Software Trigger register (SWTRIG)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

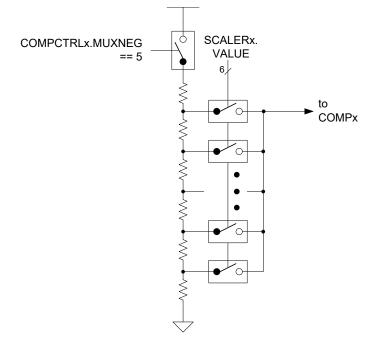

#### Figure 42-5. VDD Scaler

#### 42.6.6 Input Hysteresis

Application software can selectively enable/disable hysteresis for the comparison. Applying hysteresis will help prevent constant toggling of the output, which can be caused by noise when the input signals are close to each other.

Hysteresis is enabled for each comparator individually by the Hysteresis Enable bit in the Comparator x Control register (COMPCTRLx.HYSTEN). Furthermore, when enabled, the level of hysteresis is programmable through the Hysteresis Level bits also in the Comparator x Control register (COMPCTRLx.HYST). Hysteresis is available only in continuous mode (COMPCTRLx.SINGLE=0).

#### 42.6.7 Propagation Delay vs. Power Consumption

It is possible to trade off comparison speed for power efficiency to get the shortest possible propagation delay or the lowest power consumption. The speed setting is configured for each comparator individually by the Speed bit group in the Comparator x Control register (COMPCTRLx.SPEED). The Speed bits select the amount of bias current provided to the comparator, and as such will also affect the start-up time.

#### 42.6.8 Filtering

The output of the comparators can be filtered digitally to reduce noise. The filtering is determined by the Filter Length bits in the Comparator Control x register (COMPCTRLx.FLEN), and is independent for each comparator. Filtering is selectable from none, 3-bit majority (N=3) or 5-bit majority (N=5) functions. Any change in the comparator output is considered valid only if N/2+1 out of the last N samples agree. The filter sampling rate is the GCLK\_AC frequency.

Note that filtering creates an additional delay of N-1 sampling cycles from when a comparison is started until the comparator output is validated. For continuous mode, the first valid output will occur when the required number of filter samples is taken. Subsequent outputs will be generated every cycle based on the current sample plus the previous N-1 samples, as shown in Figure 42-6. For single-shot mode, the comparison completes after the Nth filter sample, as shown in Figure 42-7.

© 2018 Microchip Technology Inc.

#### 43.8.2 Control B

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x01                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 7    | 6       | 5      | 4 | 3   | 2       | 1    | 0    |

|--------|------|---------|--------|---|-----|---------|------|------|

|        | REFS | EL[1:0] | DITHER |   | VPD | LEFTADJ | IOEN | EOEN |

| Access | R/W  | R/W     | R/W    |   | R/W | R/W     | R/W  | R/W  |

| Reset  | 0    | 0       | 0      |   | 0   | 0       | 0    | 0    |

#### Bits 7:6 – REFSEL[1:0] Reference Selection

This bit field selects the Reference Voltage for the DAC.

**Important:** For the SAM L10/L11 devices, the 1.1V voltage reference typical value must be selected in case of an internal voltage reference (INTREF). Refer to the *Supply Controller VREF* register.

| Value | Name   | Description                |

|-------|--------|----------------------------|

| 0x0   | INTREF | Internal voltage reference |

| 0x1   | VDDANA | Analog voltage supply      |

| 0x2   | VREFA  | External reference         |

| 0x3   |        | Reserved                   |

#### Bit 5 – DITHER Dithering Mode

This bit controls dithering operation according to 43.6.8.4 Dithering mode.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Dithering mode is disabled. |

| 1     | Dithering mode is enabled.  |

#### Bit 3 – VPD Voltage Pump Disabled

This bit controls the behavior of the voltage pump.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Voltage pump is turned on/off automatically |

| 1     | Voltage pump is disabled.                   |

#### Bit 2 - LEFTADJ Left-Adjusted Data

This bit controls how the 10-bit conversion data is adjusted in the Data and Data Buffer registers.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | DATA and DATABUF registers are right-adjusted. |

| 1     | DATA and DATABUF registers are left-adjusted.  |

#### Bit 1 - IOEN Internal Output Enable

## **Electrical Characteristics**

| Mode | Conditions | Regulator | PL       | CPU Clock           | Vcc  | Та   | Тур. | Мах | Units |

|------|------------|-----------|----------|---------------------|------|------|------|-----|-------|

|      |            |           |          | DFLLULP at          | 1.8V |      | 14.3 | 19  |       |

|      |            |           |          | 32MHz               | 3.3V |      | 14.4 | 19  |       |

|      |            | BUCK      | PL0      |                     | 1.8V |      | 11.1 | 21  |       |

|      |            |           | 8MHz     | 3.3V                |      | 8.3  | 16   |     |       |

|      |            |           | OSC 8MHz | 1.8V                |      | 15.5 | 24   |     |       |

|      |            |           |          |                     | 3.3V |      | 15.2 | 21  |       |

|      |            |           |          | OSC 4MHz            | 1.8V |      | 21.3 | 39  |       |

|      |            |           |          |                     | 3.3V |      | 21.6 | 35  |       |

|      |            |           | PL2      | 32MHz<br>DFLLULP at | 1.8V |      | 14.9 | 19  |       |

|      |            |           |          |                     | 3.3V |      | 9.1  | 12  |       |

|      |            |           |          |                     | 1.8V |      | 10.6 | 14  |       |

|      |            |           |          |                     | 3.3V |      | 6.7  | 9   |       |

#### Table 46-9. Standby and Off Mode Current Consumption

| Mode    | Conditions                                                | Regulator Mode                                                                           | Vcc  | Та   | Тур. | Max. | Units |

|---------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|-------|

| STANDBY | All 16 kB RAM retained,<br>PDSW domain in active<br>state | LPVREG with LPEFF Disable                                                                | 1.8V | 25°C | 1.3  | 3.5  | μΑ    |

|         |                                                           |                                                                                          |      | 85°C | 18.4 | 66.0 |       |

|         |                                                           | LPVREG with LPEFF Enable                                                                 | 3.3V | 25°C | 1.1  | 3.0  |       |

|         |                                                           |                                                                                          |      | 85°C | 14.2 | 41.8 |       |

|         |                                                           | BUCK in standby with                                                                     | 1.8V | 25°C | 1.2  | 2.9  |       |

|         |                                                           | MAINVREG in PL0 mode<br>(VREG.RUNSTDBY=1 and<br>VREG.STDBYPL0=1)                         |      | 85°C | 14.6 | 42.9 |       |

|         |                                                           |                                                                                          | 3.3V | 25°C | 1.1  | 2.2  |       |

|         |                                                           |                                                                                          |      | 85°C | 9.6  | 28.6 |       |

|         | All 16 kB RAM retained,<br>PDSW domain in<br>retention    | LPVREG with LPEFF Disable                                                                | 1.8V | 25°C | 0.6  | 1.1  |       |

|         |                                                           |                                                                                          |      | 85°C | 5.1  | 14.9 |       |

|         |                                                           | LPVREG with LPEFF Enable                                                                 | 3.3V | 25°C | 0.5  | 1.0  |       |

|         |                                                           |                                                                                          |      | 85°C | 4.3  | 12.1 |       |

|         |                                                           | BUCK in standby with<br>MAINVREG in PL0 mode<br>(VREG.RUNSTDBY=1 and<br>VREG.STDBYPL0=1) | 1.8V | 25°C | 0.8  | 1.1  |       |

|         |                                                           |                                                                                          |      | 85°C | 4.3  | 11.9 |       |

|         |                                                           |                                                                                          | 3.3V | 25°C | 0.8  | 1.5  |       |

|         |                                                           |                                                                                          |      | 85°C | 3.4  | 8.5  |       |

2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

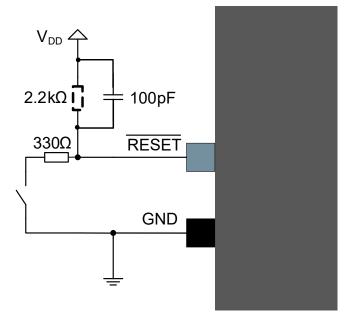

#### 50.4 External Reset Circuit

The external Reset circuit is connected to the RESET pin when the external Reset function is used. The circuit is not necessary when the RESET pin is not driven LOW externally by the application circuitry.

The reset switch can also be removed, if a manual reset is not desired. The RESET pin itself has an internal pull-up resistor, hence it is optional to add any external pull-up resistor.

#### Figure 50-5. External Reset Circuit Schematic

A pull-up resistor makes sure that the reset does not go low and unintentionally causing a device reset. An additional resistor has been added in series with the switch to safely discharge the filtering capacitor, i.e. preventing a current surge when shorting the filtering capacitor which again can cause a noise spike that can have a negative effect on the system.

|  | Table 50-3. | Reset | Circuit | Connections |

|--|-------------|-------|---------|-------------|

|--|-------------|-------|---------|-------------|

| Signal Name | Recommended Pin Connection                                                           | Description |

|-------------|--------------------------------------------------------------------------------------|-------------|

| RESET       | Reset low level threshold voltage $V_{DDIO}$ = 1.62V - 2.0V: Below 0.33 * $V_{DDIO}$ | Reset pin   |

|             | V <sub>DDIO</sub> = 2.7V - 3.63V: Below 0.36 * V <sub>DDIO</sub>                     |             |

|             | Decoupling/filter capacitor 100pF <sup>(1)</sup>                                     |             |

|             | Pull-up resistor 2.2k $\Omega^{(1,2)}$                                               |             |

|             | Resistor in series with the switch $330\Omega^{(1)}$                                 |             |

1. These values are only given as a typical example.

2. The SAM L10/L11 features an internal pull-up resistor on the RESET pin, hence an external pull-up is optional.