#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 22.4.   | Signal Description                      |     |

|---------|-----------------------------------------|-----|

| 22.5.   | Product Dependencies                    |     |

| 22.6.   | Functional Description                  | 245 |

| 22.7.   | Register Summary                        |     |

| 22.8.   | Register Description                    |     |

|         |                                         |     |

|         | CCTRL – Oscillators Controller          |     |

| 23.1.   | Overview                                | 271 |

| 23.2.   | Features                                |     |

| 23.3.   | Block Diagram                           | 272 |

| 23.4.   | Signal Description                      | 272 |

| 23.5.   | Product Dependencies                    | 272 |

| 23.6.   | Functional Description                  |     |

| 23.7.   | Register Summary                        |     |

| 23.8.   | Register Description                    |     |

| 24 050  | C32KCTRL – 32KHz Oscillators Controller | 210 |

|         |                                         |     |

|         | Overview                                |     |

|         | Features                                |     |

|         | Block Diagram                           |     |

|         | Signal Description                      |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

| 24.8.   | Register Description                    |     |

| 25 SUF  | PC – Supply Controller                  | 339 |

|         | Overview                                |     |

|         | Features                                |     |

|         |                                         |     |

|         | Block Diagram                           |     |

|         |                                         |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

| 25.8.   | Register Description                    |     |

| 26. WD  | T – Watchdog Timer                      |     |

| 26.1.   | Overview                                | 366 |

|         | Features                                |     |

|         | Block Diagram                           |     |

|         | Signal Description                      |     |

|         | Product Dependencies                    |     |

|         | Functional Description                  |     |

|         | Register Summary                        |     |

|         | Register Description                    |     |

| 20.0.   |                                         |     |

| 27. RTC | c – Real-Time Counter                   |     |

| 27.1    | Overview                                |     |

|         |                                         |     |

# SAM L10/L11 Family

# Memories

| Bit Pos. | Name                      | Usage                                                  | Factory Setting | Related Peripheral Register |

|----------|---------------------------|--------------------------------------------------------|-----------------|-----------------------------|

| 25       | WDT_RUNSTDBY              | WDT Runstdby at power-on                               | 0x0             | WDT.CTRLA                   |

| 26       | WDT_ENABLE                | WDT Enable at power-on                                 | 0x0             | WDT.CTRLA                   |

| 27       | WDT_ALWAYSON              | WDT Always-On at power-on                              | 0x0             | WDT.CTRLA                   |

| 31:28    | WDT_PER                   | WDT Period at power-on                                 | 0xB             | WDT.CONFIG                  |

| 35:32    | WDT_WINDOW                | WDT Window mode time-out at power-on                   | 0xB             | WDT.CONFIG                  |

| 39:36    | WDT_EWOFFSET              | WDT Early Warning Interrupt Time Offset at power-on    | 0xB             | WDT.EWCTRL                  |

| 40       | WDT_WEN                   | WDT Timer Window Mode Enable at power-on               | 0x0             | WDT.CTRLA                   |

| 41       | BOD33_HYST                | BOD33 Hysteresis configuration at power-on             | 0x0             | SUPC.BOD33                  |

| 42       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 43       | RXN                       | RAM is eXecute Never                                   | 0x1             | IDAU.SECCTRL                |

| 44       | DXN                       | Data Flash is eXecute Never                            | 0x1             | NVMCTRL.SECCTRL             |

| 63:45    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 71:64    | AS                        | Flash Application Secure Size = AS*0x100               | 0xFF            | IDAU.SCFGA                  |

| 77:72    | ANSC                      | Flash Application Non-Secure Callable Size = ANSC*0x20 | 0x0             | IDAU.SCFGA                  |

| 79:78    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 83:80    | DS                        | Data Flash Secure Size = DS*0x100                      | 0x8             | IDAU.SCFGA                  |

| 87:84    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 94:88    | RS                        | RAM Secure Size = RS*0x80                              | 0x7F            | IDAU.SCFGR                  |

| 95       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 96       | URWEN                     | User Row Write Enable                                  | 0x1             | NVMCTRL.SCFGAD              |

| 127:97   | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 159:128  | NONSECA <sup>(1)</sup>    | Peripherals Non-Secure Status Fuses for Bridge A       | 0x0000_0000     | PAC.NONSECA                 |

| 191:160  | NONSECB <sup>(2, 3)</sup> | Peripherals Non-Secure Status Fuses for Bridge B       | 0x0000_0000     | PAC.NONSECB                 |

| 223:192  | NONSECC                   | Peripherals Non-Secure Status Fuses for Bridge C       | 0x0000_0000     | PAC.NONSECC                 |

| 255:224  | USERCRC                   | CRC of NVM User Row bits 223:64                        | 0x8433651E      | Boot ROM                    |

# Note:

- 1. The PAC Peripheral is always secured regardless of its bit value

- 2. The IDAU and NVMCTRL peripherals are always secured regardless of their bit values.

- 3. The DSU peripheral is always non-secured regardless of its bit value.

#

1. BOD12 is calibrated in production and its calibration parameters must not be changed to ensure the correct device behavior.

| Table 10-11. | SAM L11 | UROW | Mapping |

|--------------|---------|------|---------|

|--------------|---------|------|---------|

| Offset | Bit<br>Pos. | Name                         |        |                           |  |  |  |  |

|--------|-------------|------------------------------|--------|---------------------------|--|--|--|--|

| 0x00   | 7:0         | BOD33 Level                  | -      | NSULCK SULCK              |  |  |  |  |

| 0x01   | 15:8        | BOD33                        | Action | BOD33 Disable BOD33 Level |  |  |  |  |

| 0x02   | 23:16       | BOD12 Calibration Parameters |        |                           |  |  |  |  |

The NVM Temperature Log Row can be read at address 0x00806038.

Table 10-14.

Temperature Log Row Bitfields Definition

| Bit Position | Name              | Description                                                                                         |

|--------------|-------------------|-----------------------------------------------------------------------------------------------------|

| 7:0          | ROOM_TEMP_VAL_INT | Integer part of room temperature in °C                                                              |

| 11:8         | ROOM_TEMP_VAL_DEC | Decimal part of room temperature                                                                    |

| 19:12        | HOT_TEMP_VAL_INT  | Integer part of hot temperature in °C                                                               |

| 23:20        | HOT_TEMP_VAL_DEC  | Decimal part of hot temperature                                                                     |

| 31:24        | ROOM_INT1V_VAL    | 2's complement of the internal 1V reference drift at room temperature (versus a 1.0 centered value) |

| 39:32        | HOT_INT1V_VAL     | 2's complement of the internal 1V reference drift at hot temperature (versus a 1.0 centered value)  |

| 51:40        | ROOM_ADC_VAL      | Temperature sensor 12bit ADC conversion at room temperature                                         |

| 63:52        | HOT_ADC_VAL       | Temperature sensor 12bit ADC conversion at hot temperature                                          |

**Important:** Hot temperature corresponds to the max operating temperature +/- 5%, so 85°C +/- 5% (package grade 'U') or 125°C +/- 5% (package grade 'F').

# Table 10-15. Temperature Log Row Mapping

| Offset | Bit<br>Pos. | Name                               |                   |  |  |  |  |

|--------|-------------|------------------------------------|-------------------|--|--|--|--|

| 0x00   | 7:0         | ROOM_TEM                           | ROOM_TEMP_VAL_INT |  |  |  |  |

| 0x01   | 15:8        | HOT_TEMP_VAL_INT ROOM_TEMP_VAL_DEC |                   |  |  |  |  |

| 0x02   | 23:16       | HOT_TEMP_VAL_DEC HOT_TEMP_VAL_INT  |                   |  |  |  |  |

| 0x03   | 31:24       | ROOM_INT1V_VAL                     |                   |  |  |  |  |

| 0x04   | 39:32       | HOT_INT1V_VAL                      |                   |  |  |  |  |

| 0x05   | 47:40       | ROOM_ADC_VAL                       |                   |  |  |  |  |

| 0x06   | 55:48       | HOT_ADC_VAL ROOM_ADC_VAL           |                   |  |  |  |  |

| 0x07   | 63:56       | HOT_ADC_VAL                        |                   |  |  |  |  |

# 10.2.4 NVM Boot Configuration Row (BOCOR)

The Non-Volatile Memory Boot Configuration Row (BOCOR) contains device configuration data that are automatically read by the Boot ROM program at device startup.

This row can be updated using the NVMCTRL peripheral.

When writing to the NVM Boot Configuration Row, the new values are not loaded by the other peripherals on the device until a device reset occurs.

The NVM Boot Configuration Row can be read at address 0x0080C000.

SAM L10 and SAM L11 have different NVM Boot Configuration Row mappings.

# 10.2.4.1 SAM L10 Boot Configuration Row

# Table 10-16. SAM L10 BOCOR Bitfields Definition

| Bit Pos. | Name     | Usage                                 | Factory Setting | Related Peripheral Register |

|----------|----------|---------------------------------------|-----------------|-----------------------------|

| 31:0     | Reserved | Reserved                              | Reserved        | Reserved                    |

| 39:32    | BOOTPROT | Boot Protection size = BOOTPROT*0x100 | 0x00            | Boot ROM                    |

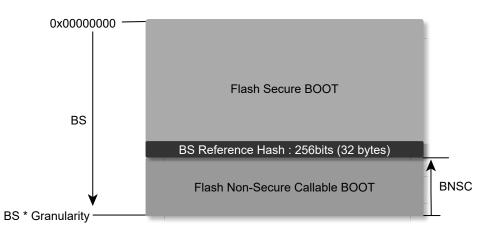

# Figure 14-4. BS Hash location in BS memory area

**Important:** The Non-Secure BOOT region as well as Secure or Non-Secure APPLICATION regions are not part of the Secure Boot verification. So if an authentication of one of these memory regions is required, it must be handled by the user code itself.

# 14.4.2.3.3 BOCOR Verification

When BOOTOPT>0, the hash for the NVM BOCOR row is computed on the whole NVM BOCOR row excluding BOCORHASH fuse value which is the fuse where to store the hash reference value [0x80C00E0:0x80C00FF]:

| BOCOR Offset | Bit Position | Name      |

|--------------|--------------|-----------|

| 0xE0-0xFF    | 2047:1792    | BOCORHASH |

# 14.4.2.4 Typical Boot Timings

Depending on the boot authentication options, the Boot ROM will require a certain time to complete its different tasks.

The delay is given from the release of the CPU reset to the execution of the first instruction of the user code.

# Table 14-5. SAM L11 Typical Boot Timings

| Boot options       | Time to reach User Code |

|--------------------|-------------------------|

| BOOTOPT=0          | 2.30 ms                 |

| BOOTOPT=1, BS=0x40 | 207 ms                  |

| BOOTOPT=1, BS=0x80 | 409 ms                  |

| BOOTOPT=2, BS=0x40 | 209 ms                  |

| BOOTOPT=2, BS=0x80 | 411 ms                  |

# 14.4.3 Debug Access Levels

The SAM L10 has only two debug access levels (DAL):

- DAL2: Highest debug level access with no restrictions in term of memory and peripheral accesses.

- DAL0: No access is authorized except with a debugger using the Boot ROM Interactive mode.

#### 16.6.3 Debugger Probe Detection

# 16.6.3.1 Cold Plugging

Cold-Plugging is the detection of a debugger when the system is in reset. Cold-Plugging is detected when the CPU reset extension is requested, as described above.

#### 16.6.3.2 Hot Plugging

Hot-Plugging is the detection of a debugger probe when the system is not in reset. Hot-Plugging is not possible under reset because the detector is reset when POR or RESET are asserted. Hot-Plugging is active when a SWCLK falling edge is detected. The SWCLK pad is multiplexed with other functions and the user must ensure that its default function is assigned to the debug system. If the SWCLK function is changed, the Hot-Plugging feature is disabled until a power-reset or external reset occurs. Availability of the Hot-Plugging feature can be read from the Hot-Plugging Enable bit of the Status B register (STATUSB.HPE).

# Figure 16-3. Hot-Plugging Detection Timing Diagram

| SWCLK        |       |         |  |

|--------------|-------|---------|--|

| RESET        |       |         |  |

| CPU_STATE    | reset | running |  |

| Hot-Plugging |       | Π       |  |

The presence of a debugger probe is detected when either Hot-Plugging or Cold-Plugging is detected. Once detected, the Debugger Present bit of the Status B register (STATUSB.DBGPRES) is set. For security reasons, Hot-Plugging is not available when DAL equals to 0x0.

This detection requires that pads are correctly powered. Thus, at cold startup, this detection cannot be done until POR is released. If DAL equals 0x0, Cold-Plugging is the only way to detect a debugger probe, and so the external reset timing must be longer than the POR timing. If external reset is de-asserted before POR release, the user must retry the procedure above until it gets connected to the device.

#### **Related Links**

30. NVMCTRL – Nonvolatile Memory Controller

# 16.6.4 Boot Communication Channels

Boot Communication Channels allow communication between a debug adapter and the CPU executing the Boot ROM at startup. The Boot ROM implements system level commands. Refer to 14. Boot ROM for more information.

# 16.7 **Programming**

Programming the Flash or RAM memories is only possible when the debugger access level is sufficient to access the desired resource:

If DAL is equal to:

- 0x2: debugger can access secured and non-secure areas

- 0x1 (SAM L11 only): debugger can access only non-secure areas, refer to Table 16-4.

| Name:<br>Offset:<br>Reset:<br>Property: |    | PID4<br>0x1FD0<br>0x00000000<br>- |        |    |    |      |        |    |

|-----------------------------------------|----|-----------------------------------|--------|----|----|------|--------|----|

| Bit                                     | 31 | 30                                | 29     | 28 | 27 | 26   | 25     | 24 |

|                                         |    |                                   |        |    |    |      |        |    |

| Access                                  |    |                                   |        |    |    |      |        |    |

| Reset                                   |    |                                   |        |    |    |      |        |    |

| Bit                                     | 23 | 22                                | 21     | 20 | 19 | 18   | 17     | 16 |

|                                         |    |                                   |        |    |    |      |        |    |

| Access                                  |    |                                   |        |    |    |      |        |    |

| Reset                                   |    |                                   |        |    |    |      |        |    |

| Bit                                     | 15 | 14                                | 13     | 12 | 11 | 10   | 9      | 8  |

|                                         |    |                                   |        |    |    |      |        |    |

| Access                                  |    |                                   |        |    |    |      |        |    |

| Reset                                   |    |                                   |        |    |    |      |        |    |

| Bit                                     | 7  | 6                                 | 5      | 4  | 3  | 2    | 1      | 0  |

|                                         |    | FKBC                              | C[3:0] |    |    | JEPC | C[3:0] |    |

| Access                                  | R  | R                                 | R      | R  | R  | R    | R      | R  |

| Reset                                   | 0  | 0                                 | 0      | 0  | 0  | 0    | 0      | 0  |

# 16.12.17 Peripheral Identification 4

# Bits 7:4 - FKBC[3:0] 4KB Count

These bits will always return zero when read, indicating that this debug component occupies one 4KB block.

# Bits 3:0 – JEPCC[3:0] JEP-106 Continuation Code

These bits will always return zero when read.

# 23.8.9 DFLLULP Control

| Name:     | DFLLULPCTRL                                                |

|-----------|------------------------------------------------------------|

| Offset:   | 0x1C                                                       |

| Reset:    | 0x0000                                                     |

| Property: | PAC Write-Protection, Enable-Protected, Write-synchronized |

| Bit    | 15       | 14       | 13     | 12   | 11    | 10  | 9        | 8   |

|--------|----------|----------|--------|------|-------|-----|----------|-----|

|        |          |          |        |      |       |     | DIV[2:0] |     |

| Access | R        | R        | R      | R    | R     | R/W | R/W      | R/W |

| Reset  | 0        | 0        | 0      | 0    | 0     | 0   | 0        | 0   |

|        |          |          |        |      |       |     |          |     |

| Bit    | 7        | 6        | 5      | 4    | 3     | 2   | 1        | 0   |

|        | ONDEMAND | RUNSTDBY | DITHER | SAFE | BINSE |     | ENABLE   |     |

| Access | R/W      | R/W      | R/W    | R/W  | R/W   |     | R/W      | R   |

| Reset  | 0        | 0        | 0      | 0    | 0     |     | 0        | 0   |

# Bits 10:8 - DIV[2:0] Division Factor

This field defines the division factor for the output frequency of the DFLLULP.

This value from production test, which depends on PL0 or PL2 mode, must be copied from the NVM software calibration row into the DFLLULPCTRL register by software.

The value must be changed before switching on a new Performance Level mode (PL0 or PL2).

These bits are not synchronized.

| Value | Name  | Description             |

|-------|-------|-------------------------|

| 0x0   | DIV1  | Frequency divided by 1  |

| 0x1   | DIV2  | Frequency divided by 2  |

| 0x2   | DIV4  | Frequency divided by 4  |

| 0x3   | DIV8  | Frequency divided by 8  |

| 0x4   | DIV16 | Frequency divided by 16 |

| 0x5   | DIV32 | Frequency divided by 32 |

| 0x6 - | -     | Reserved                |

| 0x7   |       |                         |

# Bit 7 - ONDEMAND On Demand

The On Demand operation mode allows the oscillator to be enabled or disabled, depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

This bit is not enabled-protected. This bit is not synchronized.

# 25.8.4 Status

| Name:     | STATUS                                                 |

|-----------|--------------------------------------------------------|

| Offset:   | 0x0C                                                   |

| Reset:    | x,y initially determined from NVM User Row after reset |

| Property: | -                                                      |

| Bit    | 31 | 30 | 29 | 28         | 27 | 26       | 25       | 24       |

|--------|----|----|----|------------|----|----------|----------|----------|

|        |    |    |    |            |    |          |          |          |

| Access |    |    |    |            |    |          |          |          |

| Reset  |    |    |    |            |    |          |          |          |

|        |    |    |    |            |    |          |          |          |

| Bit    | 23 | 22 | 21 | 20         | 19 | 18       | 17       | 16       |

|        |    |    |    |            |    |          |          |          |

| Access |    |    |    |            |    |          |          |          |

| Reset  |    |    |    |            |    |          |          |          |

|        |    |    |    |            |    |          |          |          |

| Bit    | 15 | 14 | 13 | 12         | 11 | 10       | 9        | 8        |

|        |    |    |    | ULPVREFRDY |    | VCORERDY |          | VREGRDY  |

| Access |    |    |    | R          |    | R        |          | R        |

| Reset  |    |    |    | х          |    | 1        |          | 1        |

|        |    |    |    |            |    |          |          |          |

| Bit    | 7  | 6  | 5  | 4          | 3  | 2        | 1        | 0        |

|        |    |    |    |            |    | B33SRDY  | BOD33DET | BOD33RDY |

| Access |    | •  | •  | •          |    | R        | R        | R        |

| Reset  |    |    |    |            |    | 0        | 0        | У        |

# Bit 12 – ULPVREFRDY Low Power Voltage Reference Ready

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The ULPVREF voltage is not as expected.    |

| 1     | The ULPVREF voltage is the target voltage. |

# Bit 10 - VCORERDY VDDCORE Voltage Ready

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The VDDCORE voltage is not as expected.    |

| 1     | The VDDCORE voltage is the target voltage. |

# Bit 8 – VREGRDY Voltage Regulator Ready

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The selected voltage regulator in VREG.SEL is not ready.                               |

| 1     | The voltage regulator selected in VREG.SEL is ready and the core domain is supplied by |

|       | this voltage regulator.                                                                |

# Bit 2 – B33SRDY BOD33 Synchronization Ready

# 26.8.1 Control A

| Name:     | CTRLA                                                |

|-----------|------------------------------------------------------|

| Offset:   | 0x00                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Synchronized             |

| Bit    | 7        | 6        | 5 | 4 | 3 | 2   | 1      | 0 |

|--------|----------|----------|---|---|---|-----|--------|---|

|        | ALWAYSON | RUNSTDBY |   |   |   | WEN | ENABLE |   |

| Access | R/W      | R/W      |   |   |   | R/W | R/W    |   |

| Reset  | x        | x        |   |   |   | x   | x      |   |

# Bit 7 – ALWAYSON Always-On

This bit allows the WDT to run continuously. After being set, this bit cannot be written to '0', and the WDT will remain enabled until a power-on Reset is received. When this bit is '1', the Control A register (CTRLA), the Configuration register (CONFIG) and the Early Warning Control register (EWCTRL) will be read-only, and any writes to these registers are not allowed.

Writing a '0' to this bit has no effect.

This bit is not Enable-Protected.

This bit is loaded from NVM User Row at start-up.

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The WDT is enabled and disabled through the ENABLE bit.                |

| 1     | The WDT is enabled and can only be disabled by a power-on reset (POR). |

# Bit 6 - RUNSTDBY Run in Standby

This bit controls the behavior of the watchdog during standby sleep mode. This bit can only be written when CTRLA.ENABLE is zero or CTRLA.ALWAYSON is one:

- When CTRLA.ALWAYSON=0, this bit is enable-protected by CTRLA.ENABLE.

- When CTRLA.ALWAYSON=1, this bit is not enable-protected by CTRLA.ENABLE.

These bits are loaded from NVM User Row at startup.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The WDT is disabled during standby sleep.                     |

| 1     | The WDT is enabled continues to operate during standby sleep. |

# **Bit 2 – WEN** Watchdog Timer Window Mode Enable

This bit enables Window mode. It can only be written if the peripheral is disabled unless CTRLA.ALWAYSON=1. The initial value of this bit is loaded from Flash Calibration.

This bit is loaded from NVM User Row at startup.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Window mode is disabled (normal operation). |

| 1     | Window mode is enabled.                     |

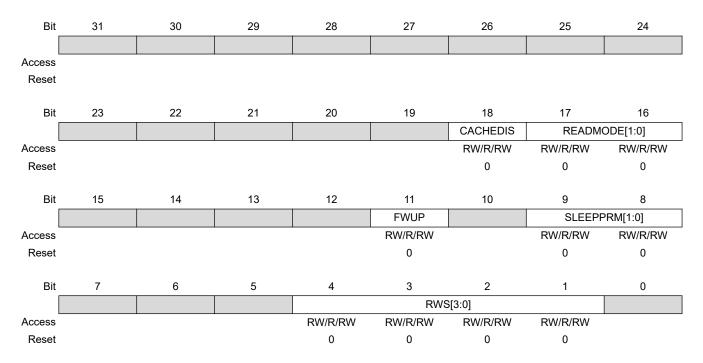

# 30.8.2 Control B

| Name:     | CTRLB                              |

|-----------|------------------------------------|

| Offset:   | 0x04                               |

| Reset:    | 0x0000080                          |

| Property: | PAC Write-Protection, Write-Secure |

# Bit 18 - CACHEDIS Cache Disable

This bit is used to disable the cache.

| Value | Description           |

|-------|-----------------------|

| 0     | The cache is enabled  |

| 1     | The cache is disabled |

# Bits 17:16 - READMODE[1:0] NVMCTRL Read Mode

| Value | Name            | Description                                                                                                                                                                                                                                            |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0   | NO_MISS_PENALTY | The NVM Controller (cache system) does not insert wait states on a cache miss. Gives the best system performance.                                                                                                                                      |

| 0x1   | LOW_POWER       | Reduces power consumption of the cache system, but inserts a wait<br>state each time there is a cache miss. This mode may not be relevant<br>if CPU performance is required, as the application will be stalled and<br>may lead to increased run time. |

| 0x2   | DETERMINISTIC   | The cache system ensures that a cache hit or miss takes the same<br>amount of time, determined by the number of programmed Flash wait<br>states. This mode can be used for real-time applications that require<br>deterministic execution timings.     |

| 0x3   | Reserved        |                                                                                                                                                                                                                                                        |

# 31.8.3 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x005                |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|---|---|---|---|---|---|-----|-----|

|        |   |   |   |   |   |   | DRP | ERR |

| Access |   |   |   |   |   |   | R/W | R/W |

| Reset  |   |   |   |   |   |   | 0   | 0   |

**Bit 1 – DRP** Data Remanence Prevention Complete Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will set the Data Remanence Prevention Complete Interrupt Enable bit, which enables the data remanence prevention complete interrupt.

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | Data remanence prevention complete interrupt is disabled. |

| 1     | Data remanence prevention complete interrupt is enabled.  |

Bit 0 – ERR TrustRAM Read Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the TrustRAM Read Error Interrupt Enable bit, which enables the TrustRAM read error interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | TrustRAM read error interrupt is disabled. |

| 1     | TrustRAM read error interrupt is enabled.  |

# SAM L10/L11 Family

# PORT - I/O Pin Controller

| PMUXO[3:0] | Name | Description                    |

|------------|------|--------------------------------|

| 0x8        | I    | Peripheral function I selected |

| 0x9-0xF    | -    | Reserved                       |

Bits 3:0 – PMUXE[3:0] Peripheral Multiplexing for Even-Numbered Pin

These bits select the peripheral function for even-numbered pins (2\*n) of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations.*

| PMUXE[3:0] | Name | Description                    |

|------------|------|--------------------------------|

| 0x0        | А    | Peripheral function A selected |

| 0x1        | В    | Peripheral function B selected |

| 0x2        | С    | Peripheral function C selected |

| 0x3        | D    | Peripheral function D selected |

| 0x4        | E    | Peripheral function E selected |

| 0x5        | -    | Reserved                       |

| 0x6        | G    | Peripheral function G selected |

| 0x7        | Н    | Peripheral function H selected |

| 0x8        | I    | Peripheral function I selected |

| 0x9-0xF    | -    | Reserved                       |

# 33.7.18 Channel Security Attribution Check

| Name:     | NSCHKCHAN            |

|-----------|----------------------|

| Offset:   | 0x1DC                |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to select one or more channels to check their security attribution as non-secured.

|        | Important: This register is only available for SAM L11 and has no effect for SAM L10. |          |          |          |          |          | <b>\M L10</b> . |          |

|--------|---------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------------|----------|

|        |                                                                                       |          |          |          |          |          |                 |          |

| Bit    | 31                                                                                    | 30       | 29       | 28       | 27       | 26       | 25              | 24       |

|        |                                                                                       |          |          |          |          |          |                 |          |

| Access |                                                                                       |          | 1        | 1        |          |          |                 |          |

| Reset  |                                                                                       |          |          |          |          |          |                 |          |

|        |                                                                                       |          |          |          |          |          |                 |          |

| Bit    | 23                                                                                    | 22       | 21       | 20       | 19       | 18       | 17              | 16       |

|        |                                                                                       |          |          |          |          |          |                 |          |

| Access |                                                                                       |          |          |          |          |          |                 |          |

| Reset  |                                                                                       |          |          |          |          |          |                 |          |

| Bit    | 15                                                                                    | 14       | 13       | 12       | 11       | 10       | 9               | 8        |

| DIL    | 15                                                                                    | 14       | 13       | 12       | 11       | 10       | 9               | °        |

| Access |                                                                                       |          |          |          |          |          |                 |          |

| Reset  |                                                                                       |          |          |          |          |          |                 |          |

| 10000  |                                                                                       |          |          |          |          |          |                 |          |

| Bit    | 7                                                                                     | 6        | 5        | 4        | 3        | 2        | 1               | 0        |

|        |                                                                                       |          |          | CHANN    | ELn[7:0] |          |                 |          |

| Access | RW/RW/RW                                                                              | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW        | RW/RW/RW |

| Reset  | 0                                                                                     | 0        | 0        | 0        | 0        | 0        | 0               | 0        |

|        |                                                                                       |          |          |          |          |          |                 |          |

# Bits 7:0 – CHANNELn[7:0] Channel n Selection [n=7..0]

These bits selects the individual channels for security attribution check. If any channel selected in NSCHKCHAN has the corresponding bit in NONSECCHAN set to the opposite value, then the NSCHK interrupt flag will be set.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | 0-to-1 transition will be detected on corresponding NONSECCHAN bit. |

| 1     | 1-to-0 transition will be detected on corresponding NONSECCHAN bit. |

# 35.6.2.6 Data Reception

The receiver accepts data when a valid start bit is detected. Each bit following the start bit will be sampled according to the baud rate or XCK clock, and shifted into the receive shift register until the first stop bit of a frame is received. The second stop bit will be ignored by the receiver.

When the first stop bit is received and a complete serial frame is present in the receive shift register, the contents of the shift register will be moved into the two-level or four-level receive buffer. Then, the Receive Complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set, and the optional interrupt will be generated.

The received data can be read from the DATA register when the Receive Complete interrupt flag is set.

# 35.6.2.6.1 Disabling the Receiver

Writing '0' to the Receiver Enable bit in the CTRLB register (CTRLB.RXEN) will disable the receiver, flush the two-level or four-level receive buffer, and data from ongoing receptions will be lost.

# 35.6.2.6.2 Error Bits

The USART receiver has three error bits in the Status (STATUS) register: Frame Error (FERR), Buffer Overflow (BUFOVF), and Parity Error (PERR). Once an error happens, the corresponding error bit will be set until it is cleared by writing '1' to it. These bits are also cleared automatically when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the Immediate Buffer Overflow Notification bit in the Control A register (CTRLA.IBON):

When CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA, until the receiver complete interrupt flag (INTFLAG.RXC) is cleared.

When CTRLA.IBON=0, the buffer overflow condition is attending data through the receive FIFO. After the received data is read, STATUS.BUFOVF will be set along with INTFLAG.RXC.

# 35.6.2.6.3 Asynchronous Data Reception

The USART includes a clock recovery and data recovery unit for handling asynchronous data reception.

The clock recovery logic can synchronize the incoming asynchronous serial frames at the RxD pin to the internally generated baud-rate clock.

The data recovery logic samples and applies a low-pass filter to each incoming bit, thereby improving the noise immunity of the receiver.

# 35.6.2.6.4 Asynchronous Operational Range

The operational range of the asynchronous reception depends on the accuracy of the internal baud-rate clock, the rate of the incoming frames, and the frame size (in number of bits). In addition, the operational range of the receiver is depending on the difference between the received bit rate and the internally generated baud rate. If the baud rate of an external transmitter is too high or too low compared to the internally generated baud rate, the receiver will not be able to synchronize the frames to the start bit.

There are two possible sources for a mismatch in baud rate: First, the reference clock will always have some minor instability. Second, the baud-rate generator cannot always do an exact division of the reference clock frequency to get the baud rate desired. In this case, the BAUD register value should be set to give the lowest possible error. Refer to *Clock Generation – Baud-Rate Generator* for details.

Recommended maximum receiver baud-rate errors for various character sizes are shown in the table below.

# 38.7.2.1 Control A

| Name:     | CTRLA                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x00                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Write-Synchronized, Enable-Protected |

| Bit    | 31       | 30       | 29     | 28       | 27    | 26     | 25            | 24      |

|--------|----------|----------|--------|----------|-------|--------|---------------|---------|

|        |          |          |        |          |       |        |               |         |

| Access |          |          |        |          |       |        |               |         |

| Reset  |          |          |        |          |       |        |               |         |

|        |          |          |        |          |       |        |               |         |

| Bit    | 23       | 22       | 21     | 20       | 19    | 18     | 17            | 16      |

|        |          |          | COPEN1 | COPEN0   |       |        | CAPTEN1       | CAPTEN0 |

| Access |          |          | R/W    | R/W      |       |        | R/W           | R/W     |

| Reset  |          |          | 0      | 0        |       |        | 0             | 0       |

|        |          |          |        |          |       |        |               |         |

| Bit    | 15       | 14       | 13     | 12       | 11    | 10     | 9             | 8       |

|        |          |          |        |          | ALOCK | F      | PRESCALER[2:0 | 1       |

| Access |          |          |        |          | R/W   | R/W    | R/W           | R/W     |

| Reset  |          |          |        |          | 0     | 0      | 0             | 0       |

|        |          |          |        |          |       |        |               |         |

| Bit    | 7        | 6        | 5      | 4        | 3     | 2      | 1             | 0       |

|        | ONDEMAND | RUNSTDBY | PRESCS | YNC[1:0] | MOD   | E[1:0] | ENABLE        | SWRST   |

| Access | R/W      | R/W      | R/W    | R/W      | R/W   | R/W    | R/W           | W       |

| Reset  | 0        | 0        | 0      | 0        | 0     | 0      | 0             | 0       |

# Bits 20, 21 – COPENx Capture On Pin x Enable

Bit x of COPEN[1:0] selects the trigger source for capture operation, either events or I/O pin input.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

# Bits 16, 17 – CAPTENx Capture Channel x Enable

Bit x of CAPTEN[1:0] selects whether channel x is a capture or a compare channel.

These bits are not synchronized.

| <b>/</b> alue | Description                           |

|---------------|---------------------------------------|

| )             | CAPTEN disables capture on channel x. |

| 1             | CAPTEN enables capture on channel x.  |

# Bit 11 – ALOCK Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

#### 38.7.2.12 Synchronization Busy

| Name:<br>Offset:<br>Reset:<br>Property: |    | SYNCBUSY<br>0x10<br>0x00000000<br>- |     |       |        |       |        |       |

|-----------------------------------------|----|-------------------------------------|-----|-------|--------|-------|--------|-------|

| Bit                                     | 31 | 30                                  | 29  | 28    | 27     | 26    | 25     | 24    |

|                                         |    |                                     |     |       |        |       |        |       |

| Access                                  |    |                                     |     |       |        |       |        |       |

| Reset                                   |    |                                     |     |       |        |       |        |       |

|                                         |    |                                     |     |       |        |       |        |       |

| Bit                                     | 23 | 22                                  | 21  | 20    | 19     | 18    | 17     | 16    |

|                                         |    |                                     |     |       |        |       |        |       |

| Access                                  |    |                                     |     |       |        |       |        |       |

| Reset                                   |    |                                     |     |       |        |       |        |       |

|                                         |    |                                     |     |       |        |       |        |       |

| Bit                                     | 15 | 14                                  | 13  | 12    | 11     | 10    | 9      | 8     |

|                                         |    |                                     |     |       |        |       |        |       |

| Access                                  |    |                                     |     |       |        |       |        |       |

| Reset                                   |    |                                     |     |       |        |       |        |       |

| Bit                                     | 7  | 6                                   | 5   | 4     | 3      | 2     | 1      | 0     |

| Dit                                     | ,  | CCx                                 | PER | COUNT | STATUS | CTRLB | ENABLE | SWRST |

| Access                                  |    | R                                   | R   | R     | R      | R     | R      | R     |

| Reset                                   |    | 0                                   | 0   | 0     | 0      | 0     | 0      | 0     |

| 110301                                  |    | 0                                   | 0   | 0     | 0      | 0     | 0      | 0     |

**Bit 6 – CCx** Compare/Capture Channel x Synchronization Busy For details on CC channels number, refer to each TC feature list.

This bit is set when the synchronization of CCx between clock domains is started.

This bit is also set when the CCBUFx is written, and cleared on update condition. The bit is automatically cleared when the STATUS.CCBUFx bit is cleared.

#### Bit 5 – PER PER Synchronization Busy

This bit is cleared when the synchronization of PER between the clock domains is complete.

This bit is set when the synchronization of PER between clock domains is started.

This bit is also set when the PER is written, and cleared on update condition. The bit is automatically cleared when the STATUS.PERBUF bit is cleared.

# Bit 4 – COUNT COUNT Synchronization Busy

This bit is cleared when the synchronization of COUNT between the clock domains is complete.

This bit is set when the synchronization of COUNT between clock domains is started.

# Bit 3 – STATUS STATUS Synchronization Busy

This bit is cleared when the synchronization of STATUS between the clock domains is complete.

© 2018 Microchip Technology Inc.

This bit is set when a '1' is written to the Capture Channel Buffer Valid status flags (STATUS.CCBUFVx) and the synchronization of STATUS between clock domains is started.

# **Bit 2 – CTRLB** CTRLB Synchronization Busy

This bit is cleared when the synchronization of CTRLB between the clock domains is complete.

This bit is set when the synchronization of CTRLB between clock domains is started.

# Bit 1 – ENABLE ENABLE Synchronization Busy

This bit is cleared when the synchronization of ENABLE bit between the clock domains is complete.

This bit is set when the synchronization of ENABLE bit between clock domains is started.

# Bit 0 – SWRST SWRST Synchronization Busy

This bit is cleared when the synchronization of SWRST bit between the clock domains is complete.

This bit is set when the synchronization of SWRST bit between clock domains is started.

# 41.8.1 Control A

| Name:     | CTRLA                                    |

|-----------|------------------------------------------|

| Offset:   | 0x00                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7        | 6        | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|----------|----------|---|---|---|---|--------|-------|

|        | ONDEMAND | RUNSTDBY |   |   |   |   | ENABLE | SWRST |

| Access | R/W      | R/W      |   |   |   |   | R/W    | R/W   |

| Reset  | 0        | 0        |   |   |   |   | 0      | 0     |

# Bit 7 - ONDEMAND On Demand Control

The On Demand operation mode allows the ADC to be enabled or disabled, depending on other peripheral requests.

In On Demand operation mode, i.e., if the ONDEMAND bit has been previously set, the ADC will only be running when requested by a peripheral. If there is no peripheral requesting the ADC will be in a disable state.

If On Demand is disabled the ADC will always be running when enabled.

In standby sleep mode, the On Demand operation is still active if the CTRLA.RUNSTDBY bit is '1'. If CTRLA.RUNSTDBY is '0', the ADC is disabled.

This bit is not synchronized.

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | The ADC is always on , if enabled.                                                 |

| 1     | The ADC is enabled, when a peripheral is requesting the ADC conversion. The ADC is |

|       | disabled if no peripheral is requesting it.                                        |

# Bit 6 – RUNSTDBY Run in Standby

This bit controls how the ADC behaves during standby sleep mode.

This bit is not synchronized.

| Value | Description                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The ADC is halted during standby sleep mode.                                                                                                                                                              |

| 1     | The ADC is not stopped in standby sleep mode. If CTRLA.ONDEMAND=1, the ADC will be running when a peripheral is requesting it. If CTRLA.ONDEMAND=0, the ADC will always be running in standby sleep mode. |

# Bit 1 - ENABLE Enable

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the ENABLE bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description          |

|-------|----------------------|

| 0     | The ADC is disabled. |

| 1     | The ADC is enabled.  |

# 41.8.5 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2      | 1       | 0      |

|--------|---|---|---|---|---|--------|---------|--------|

|        |   |   |   |   |   | WINMON | OVERRUN | RESRDY |

| Access |   |   |   |   |   | R/W    | R/W     | R/W    |

| Reset  |   |   |   |   |   | 0      | 0       | 0      |

# **Bit 2 – WINMON** Window Monitor Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Window Monitor Interrupt Enable bit, which disables the corresponding interrupt request.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The window monitor interrupt is disabled.                                                    |

| 1     | The window monitor interrupt is enabled, and an interrupt request will be generated when the |

|       | Window Monitor interrupt flag is set.                                                        |

# **Bit 1 – OVERRUN** Overrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overrun Interrupt Enable bit, which disables the corresponding interrupt request.

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | The Overrun interrupt is disabled.                                                    |

| 1     | The Overrun interrupt is enabled, and an interrupt request will be generated when the |

|       | Overrun interrupt flag is set.                                                        |

# **Bit 0 – RESRDY** Result Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Result Ready Interrupt Enable bit, which disables the corresponding interrupt request.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Result Ready interrupt is disabled.                                                    |

| 1     | The Result Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | Result Ready interrupt flag is set.                                                        |

# SAM L10/L11 Family

# 125°C Electrical Characteristics

| Mode | Conditions | Regulator | PL  | CPU Clock            | Vcc  | Та | Тур. | Max. | Units |

|------|------------|-----------|-----|----------------------|------|----|------|------|-------|

|      |            | BUCK      | PLO | DFLLUP at 8<br>MHz   | 1.8V |    | 28.1 | 72   |       |

|      |            |           |     |                      | 3.3V |    | 18.5 | 47   |       |

|      |            |           |     | OSC 8 MHz            | 1.8V |    | 32.2 | 73   |       |

|      |            |           |     |                      | 3.3V |    | 25.3 | 51   |       |

|      |            |           |     | OSC 4 MHz            | 1.8V |    | 38.4 | 121  |       |

|      |            |           |     |                      | 3.3V |    | 31.9 | 86   |       |

|      |            |           | PL2 | FDPLL96 at<br>32 MHz | 1.8V |    | 41.5 | 55   |       |

|      |            |           |     |                      | 3.3V |    | 24.6 | 34   |       |

|      |            |           |     | DFLLULP at<br>32 MHz | 1.8V |    | 37.1 | 53   |       |

|      |            |           |     |                      | 3.3V |    | 22.0 | 32   |       |

| IDLE |            | LDO       | PL0 | DFLLUP at 8<br>MHz   | 1.8V |    | 16.0 | 81   |       |

|      |            |           |     |                      | 3.3V |    | 16.2 | 82   |       |

|      |            |           |     | OSC 8 MHz            | 1.8V |    | 19.8 | 82   |       |

|      |            |           |     |                      | 3.3V |    | 22.0 | 85   |       |

|      |            |           |     | OSC 4 MHz            | 1.8V |    | 26.2 | 152  |       |

|      |            |           |     |                      | 3.3V |    | 29.2 | 157  |       |

|      |            |           | PL2 | FDPLL96 at<br>32 MHz | 1.8V |    | 20.3 | 54   |       |

|      |            |           |     |                      | 3.3V |    | 20.4 | 54   |       |

|      |            |           |     | DFLLULP at<br>32 MHz | 1.8V |    | 14.3 | 32   |       |

|      |            |           |     |                      | 3.3V |    | 14.4 | 33   |       |

|      |            |           | PLO | DFLLUP at 8<br>MHz   | 1.8V |    | 11.1 | 52   |       |

|      |            |           |     |                      | 3.3V |    | 8.3  | 35   |       |

|      |            |           |     | OSC 8 MHz            | 1.8V |    | 15.5 | 55   |       |

|      |            |           |     |                      | 3.3V |    | 15.2 | 40   |       |

|      |            |           |     | OSC 4 MHz            | 1.8V |    | 21.3 | 100  |       |

|      |            |           |     |                      | 3.3V |    | 21.6 | 73   |       |

|      |            |           | PL2 | FDPLL96 at<br>32 MHz | 1.8V |    | 14.9 | 30   |       |

|      |            |           |     |                      | 3.3V |    | 9.1  | 19   |       |

|      |            |           |     | DFLLULP at<br>32 MHz | 1.8V |    | 10.6 | 24   |       |

|      |            |           |     |                      | 3.3V |    | 6.7  | 15   |       |