#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- HMAC is described in FIPS PUB 198-1.

- The hash used for HMAC is SHA256.

- The output of the HMAC-SHA256 is truncated to obtain an HMAC-SHA256-128 as explained in RFC4868.

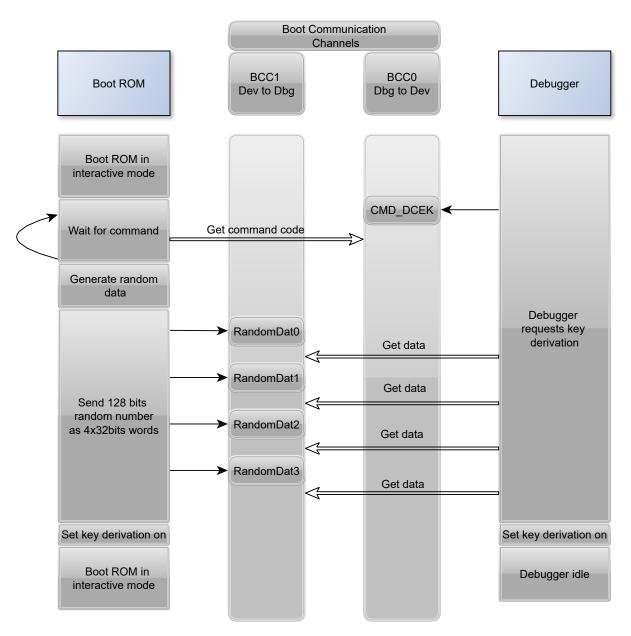

#### 14.4.5.7.1 CMD\_DCEK (SAM L11 only)

#### Figure 14-14. CMD\_DCEK Flow diagram

#### 14.4.5.8 NVM Rows Content Checks (CMD\_RAUX)

The Boot ROM provides a way to check the content of the NVM rows.

When device is secured (DAL0), the fuse configuration can still be read by the debugger using the Read Auxiliary command (CMD\_RAUX).

### 15.5.8 Synchronization

Not applicable.

## 16. DSU - Device Service Unit

### 16.1 Overview

The Device Service Unit (DSU) provides a means to detect debugger probes. This enables the ARM Debug Access Port (DAP) to have control over multiplexed debug pads and CPU reset. The DSU also provides system-level services to debug adapters in an ARM debug system. It implements a CoreSight Debug ROM that provides device identification as well as identification of other debug components within the system. Hence, it complies with the ARM Peripheral Identification specification. The DSU also provides system services to applications that need memory testing, as required for IEC60730 Class B compliance, for example. The DSU can be accessed simultaneously by a debugger and the CPU, as it is connected on the High-Speed Bus Matrix. It implements communication channels between the device and external tools which can be used at boot time to make use of Boot ROM services. For security reasons, some of the DSU features will be limited or unavailable when the Debug Access Level (DAL) is less than 0x2.

#### **Related Links**

30. NVMCTRL - Nonvolatile Memory Controller

### 16.2 Features

- CPU reset extension

- Debugger probe detection (Cold- and Hot-Plugging)

- 32-bit cyclic redundancy check (CRC32) of any memory accessible through the bus matrix

- ARM<sup>®</sup> CoreSight<sup>™</sup> compliant device identification

- Two debug communications channels

- Two Boot communications channels

- · Debug access port security filter

- Onboard memory built-in self-test (MBIST)

## DSU - Device Service Unit

|        | Name:<br>Offset:<br>Reset:<br>Property: | MEMTYPE<br>0x1FCC<br>0x0000000x<br>- |    |    |    |    |    |       |

|--------|-----------------------------------------|--------------------------------------|----|----|----|----|----|-------|

| Bit    | 31                                      | 30                                   | 29 | 28 | 27 | 26 | 25 | 24    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

|        |                                         |                                      |    |    |    |    |    |       |

| Bit    | 23                                      | 22                                   | 21 | 20 | 19 | 18 | 17 | 16    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| D.4    | 45                                      |                                      | 10 | 10 | 44 | 10 | 0  | 0     |

| Bit    | 15                                      | 14                                   | 13 | 12 | 11 | 10 | 9  | 8     |

| A      |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| Bit    | 7                                       | 6                                    | 5  | 4  | 3  | 2  | 1  | 0     |

|        |                                         |                                      |    |    |    |    |    | SMEMP |

| Access |                                         |                                      |    |    |    |    |    | R     |

| Reset  |                                         |                                      |    |    |    |    |    | x     |

|        |                                         |                                      |    |    |    |    |    |       |

#### 16.12.16 CoreSight ROM Table Memory Type

#### Bit 0 - SMEMP System Memory Present

This bit indicates whether system memory is present on the bus that connects to the ROM table.

This bit is set at power-up if the device is not protected, indicating that the system memory is accessible from a debug adapter.

This bit is cleared at power-up if the device is protected, indicating that the system memory is not accessible from a debug adapter.

# 16.12.20 Peripheral Identification 2

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID2<br>0x1FE8<br>0x00000019<br>- |         |    |      |    |              |    |

|--------|-----------------------------------------|-----------------------------------|---------|----|------|----|--------------|----|

| Bit    | 31                                      | 30                                | 29      | 28 | 27   | 26 | 25           | 24 |

|        |                                         |                                   |         |    |      |    |              |    |

| Access |                                         | ·                                 |         |    |      |    |              |    |

| Reset  |                                         |                                   |         |    |      |    |              |    |

|        |                                         |                                   |         |    |      |    |              |    |

| Bit    | 23                                      | 22                                | 21      | 20 | 19   | 18 | 17           | 16 |

|        |                                         |                                   |         |    |      |    |              |    |

| Access |                                         |                                   |         |    |      |    |              |    |

| Reset  |                                         |                                   |         |    |      |    |              |    |

| Dit    | 45                                      | 4.4                               | 10      | 10 | 44   | 10 | 0            | 0  |

| Bit    | 15                                      | 14                                | 13      | 12 | 11   | 10 | 9            | 8  |

| Access |                                         |                                   |         |    |      |    |              |    |

| Reset  |                                         |                                   |         |    |      |    |              |    |

| Nesei  |                                         |                                   |         |    |      |    |              |    |

| Bit    | 7                                       | 6                                 | 5       | 4  | 3    | 2  | 1            | 0  |

|        |                                         |                                   | ON[3:0] |    | JEPU |    | JEPIDCH[2:0] |    |

| Access | R                                       | R                                 | R       | R  | R    | R  | R            | R  |

| Reset  | 0                                       | 0                                 | 0       | 1  | 1    | 0  | 0            | 1  |

|        |                                         |                                   |         |    |      |    |              |    |

#### Bits 7:4 – REVISION[3:0] Revision Number

Revision of the peripheral. Starts at 0x0 and increments by one at both major and minor revisions.

#### Bit 3 – JEPU JEP-106 Identity Code is used

This bit will always return one when read, indicating that JEP-106 code is used.

#### Bits 2:0 – JEPIDCH[2:0] JEP-106 Identity Code High

These bits will always return 0x1 when read, indicating an Atmel device (Atmel JEP-106 identity code is 0x1F).

20.8.9 Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | VALUE<br>0x10<br>0x00000000<br>- |    |       |         |    |    |    |

|--------|-----------------------------------------|----------------------------------|----|-------|---------|----|----|----|

| Bit    | 31                                      | 30                               | 29 | 28    | 27      | 26 | 25 | 24 |

|        |                                         |                                  |    |       |         |    |    |    |

| Access |                                         |                                  |    |       |         |    |    |    |

| Reset  |                                         |                                  |    |       |         |    |    |    |

| Bit    | 23                                      | 22                               | 21 | 20    | 19      | 18 | 17 | 16 |

|        |                                         |                                  |    | VALUE | [23:16] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

| Bit    | 15                                      | 14                               | 13 | 12    | 11      | 10 | 9  | 8  |

|        |                                         |                                  |    | VALUE | E[15:8] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 7                                       | 6                                | 5  | 4     | 3       | 2  | 1  | 0  |

|        |                                         |                                  |    |       | E[7:0]  |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

**Bits 23:0 – VALUE[23:0]** Measurement Value Result from measurement.

#### 24.8.1 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27 | 26      | 25 | 24         |

|--------|----|----|----|----|----|---------|----|------------|

|        |    |    |    |    |    |         |    |            |

| Access |    |    |    |    |    |         |    |            |

| Reset  |    |    |    |    |    |         |    |            |

|        |    |    |    |    |    |         |    |            |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18      | 17 | 16         |

|        |    |    |    |    |    |         |    |            |

| Access |    |    |    |    |    |         |    |            |

| Reset  |    |    |    |    |    |         |    |            |

|        |    |    |    |    |    |         |    |            |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10      | 9  | 8          |

|        |    |    |    |    |    |         |    |            |

| Access |    |    |    |    |    |         |    |            |

| Reset  |    |    |    |    |    |         |    |            |

|        |    |    |    |    |    |         |    |            |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2       | 1  | 0          |

|        |    |    |    |    |    | CLKFAIL |    | XOSC32KRDY |

| Access |    |    |    |    |    | R/W     |    | R/W        |

| Reset  |    |    |    |    |    | 0       |    | 0          |

**Bit 2 – CLKFAIL** XOSC32K Clock Failure Detection Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Clock Failure Interrupt Enable bit, which disables the XOSC32K Clock Failure interrupt.

| Value | Description                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC32K Clock Failure Detection is disabled.                                                                                                       |

| 1     | The XOSC32K Clock Failure Detection is enabled. An interrupt request will be generated when the XOSC32K Clock Failure Detection interrupt flag is set. |

#### Bit 0 – XOSC32KRDY XOSC32K Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Ready Interrupt Enable bit, which disables the XOSC32K Ready interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The XOSC32K Ready interrupt is disabled. |

| 1     | The XOSC32K Ready interrupt is enabled.  |

RTC – Real-Time Counter

Refer to Peripherals Security Attribution for more information.

#### 27.12.7 Debug Control

Name:DBGCTRLOffset:0x0EReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

| Value | e Description                                                                      |

|-------|------------------------------------------------------------------------------------|

| 0     | The RTC is halted when the CPU is halted by an external debugger.                  |

| 1     | The RTC continues normal operation when the CPU is halted by an external debugger. |

| Property: PAC Write-Protection, Enable-Protected |     |     |     |       |          |          |     |     |

|--------------------------------------------------|-----|-----|-----|-------|----------|----------|-----|-----|

|                                                  |     |     |     |       |          |          |     |     |

|                                                  |     |     |     |       |          |          |     |     |

| Bit                                              | 31  | 30  | 29  | 28    | 27       | 26       | 25  | 24  |

|                                                  |     |     |     |       |          |          |     |     |

| Access                                           |     |     |     |       |          |          |     |     |

| Reset                                            |     |     |     |       |          |          |     |     |

|                                                  |     |     |     |       |          |          |     |     |

| Bit                                              | 23  | 22  | 21  | 20    | 19       | 18       | 17  | 16  |

|                                                  |     |     |     |       |          |          |     |     |

| Access                                           |     | ·   |     |       |          | -        |     |     |

| Reset                                            |     |     |     |       |          |          |     |     |

|                                                  |     |     |     |       |          |          |     |     |

| Bit                                              | 15  | 14  | 13  | 12    | 11       | 10       | 9   | 8   |

|                                                  |     |     |     |       | WRBAD    | DR[13:8] |     |     |

| Access                                           |     | ŀ   | R/W | R/W   | R/W      | R/W      | R/W | R/W |

| Reset                                            |     |     | 0   | 0     | 0        | 0        | 0   | 0   |

|                                                  |     |     |     |       |          |          |     |     |

| Bit                                              | 7   | 6   | 5   | 4     | 3        | 2        | 1   | 0   |

|                                                  |     |     |     | WRBAD | DDR[7:0] |          |     |     |

| Access                                           | R/W | R/W | R/W | R/W   | R/W      | R/W      | R/W | R/W |

| Reset                                            | 0   | 0   | 0   | 0     | 0        | 0        | 0   | 0   |

#### 28.8.16 Write-Back Memory Section Base Address

0x38

WRBADDR

0x00000000

Name:

Offset:

Reset:

**Bits 13:0 – WRBADDR[13:0]** Write-Back Memory Base Address These bits store the Write-Back memory base address. The value must be 128-bit aligned. When the USART repetition number reaches the programmed value in CTRLC.MAXITER, the STATUS.ITER bit is set and the internal iteration counter is reset. If the repetition of the character is acknowledged by the receiver before the maximum iteration is reached, the repetitions are stopped and the iteration counter is cleared.

#### **Disable Successive Receive NACK**

The receiver can limit the number of successive NACKs sent back to the remote transmitter. This is programmed by setting the Disable Successive NACK bit (CTRLC.DSNACK). The maximum number of NACKs transmitted is programmed in the CTRLC.MAXITER field. As soon as the maximum is reached, the character is considered as correct, an acknowledge is sent on the line, the STATUS.ITER bit is set and the internal iteration counter is reset.

#### Protocol T=1

When operating in ISO7816 protocol T=1, the transmission is asynchronous (CTRL1.CMODE=0) with one or two stop bits. After the stop bits are sent, the transmitter does not drive the I/O line.

Parity is generated when transmitting and checked when receiving. Parity error detection sets the STATUS.PERR bit, and the erroneous character is written to the receive FIFO. When using T=1 protocol, the receiver does not signal errors on the I/O line and the transmitter does not retransmit.

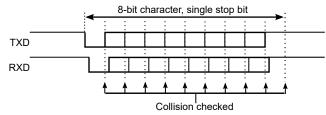

#### 35.6.3.7 Collision Detection

When the receiver and transmitter are connected either through pin configuration or externally, transmit collision can be detected after selecting the Collision Detection Enable bit in the CTRLB register (CTRLB.COLDEN=1). To detect collision, the receiver and transmitter must be enabled (CTRLB.RXEN=1 and CTRLB.TXEN=1).

Collision detection is performed for each bit transmitted by comparing the received value with the transmit value, as shown in the figure below. While the transmitter is idle (no transmission in progress), characters can be received on RxD without triggering a collision.

#### Figure 35-18. Collision Checking

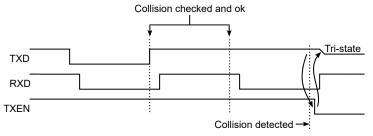

The next figure shows the conditions for a collision detection. In this case, the start bit and the first data bit are received with the same value as transmitted. The second received data bit is found to be different than the transmitted bit at the detection point, which indicates a collision.

#### Figure 35-19. Collision Detected

When a collision is detected, the USART follows this sequence:

#### 35.8.12 Data

|        | Name:<br>Offset:<br>Reset:<br>Property: | DATA<br>0x28<br>0x0000<br>- |     |      |        |     |     |           |

|--------|-----------------------------------------|-----------------------------|-----|------|--------|-----|-----|-----------|

| Bit    | 15                                      | 14                          | 13  | 12   | 11     | 10  | 9   | 8         |

|        |                                         |                             |     |      |        |     |     | DATA[8:8] |

| Access |                                         |                             |     | ·    |        |     |     | R/W       |

| Reset  |                                         |                             |     |      |        |     |     | 0         |

|        |                                         |                             |     |      |        |     |     |           |

| Bit    | 7                                       | 6                           | 5   | 4    | 3      | 2   | 1   | 0         |

|        |                                         |                             |     | DATA | A[7:0] |     |     |           |

| Access | R/W                                     | R/W                         | R/W | R/W  | R/W    | R/W | R/W | R/W       |

| Reset  | 0                                       | 0                           | 0   | 0    | 0      | 0   | 0   | 0         |

#### Bits 8:0 - DATA[8:0] Data

Reading these bits will return the contents of the Receive Data register. The register should be read only when the Receive Complete Interrupt Flag bit in the Interrupt Flag Status and Clear register (INTFLAG.RXC) is set. The status bits in STATUS should be read before reading the DATA value in order to get any corresponding error.

Writing these bits will write the Transmit Data register. This register should be written only when the Data Register Empty Interrupt Flag bit in the Interrupt Flag Status and Clear register (INTFLAG.DRE) is set.

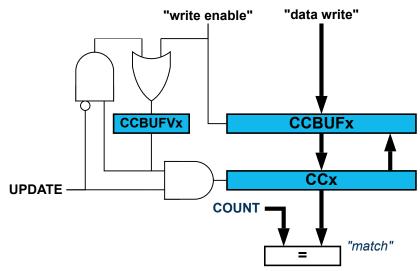

#### Figure 38-7. Compare Channel Double Buffering

Both the registers (PER/CCx) and corresponding buffer registers (PERBUF/CCBUFx) are available in the I/O register map, and the double buffering feature is not mandatory. The double buffering is disabled by writing a '1' to CTRLBSET.LUPD.

**Note:** In NFRQ, MFRQ or PWM down-counting counter mode (CTRLBSET.DIR=1), when double buffering is enabled (CTRLBCLR.LUPD=1), PERBUF register is continously copied into the PER independently of update conditions.

#### Changing the Period

The counter period can be changed by writing a new TOP value to the Period register (PER or CC0, depending on the waveform generation mode), which is available in 8-bit mode. Any period update on registers (PER or CCx) is effective after the synchronization delay.

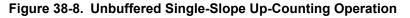

A counter wraparound can occur in any operation mode when up-counting without buffering, see Figure 38-8.

COUNT and TOP are continuously compared, so when a new TOP value that is lower than current COUNT is written to TOP, COUNT will wrap before a compare match.

### Timer/Counter Inputs (TC)

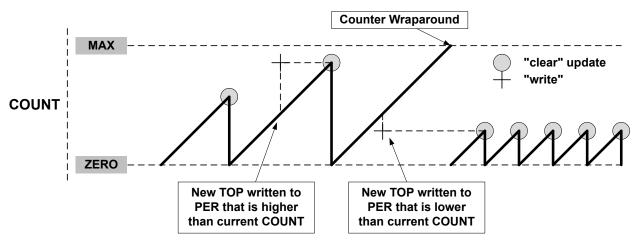

The TC waveform output WO[0] can be used as input source for the LUT (LUTCTRLx.INSELy=TC). Only consecutive instances of the TC, i.e. TCx and the subsequent TC(x+1), are available as default and alternative TC selections (e.g., TC0 and TC1 are sources for LUT0, TC1 and TC2 are sources for LUT1, etc). See the figure below for an example for LUT0. More general, the Timer/Counter selection for each LUT follows the formula:

$IN[N][i] = DefaultTC[N \% TC_Instance_Number]$

$IN[N][i] = AlternativeTC[(N + 1) \% TC_Instance_Number]$

Where N represents the LUT number and i represents the LUT input index (i=0,1,2).

Before selecting the waveform outputs, the TC must be configured first.

#### Figure 40-9. TC Input Selection

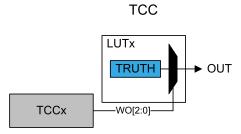

#### Timer/Counter for Control Application Inputs (TCC)

The TCC waveform outputs can be used as input source for the LUT. Only WO[2:0] outputs can be selected and routed to the respective LUT input (i.e., IN0 is connected to WO0, IN1 to WO1, and IN2 to WO2), as shown in the figure below.

Before selecting the waveform outputs, the TCC must be configured first.

#### Figure 40-10. TCC Input Selection

#### Serial Communication Output Transmit Inputs (SERCOM)

The serial engine transmitter output from Serial Communication Interface (SERCOM TX, TXd for USART, MOSI for SPI) can be used as input source for the LUT. The figure below shows an example for LUT0 and LUT1. The SERCOM selection for each LUT follows the formula:

IN[N][i] = SERCOM[N % SERCOM\_Instance\_Number]

With *N* representing the LUT number and *i*=0,1,2 representing the LUT input index.

Before selecting the SERCOM as input source, the SERCOM must be configured first: the SERCOM TX signal must be output on SERCOMn/pad[0], which serves as input pad to the CCL.

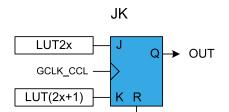

#### Figure 40-15. JK Flip Flop

When the even LUT is disabled (), the flip-flop is asynchronously cleared. The reset command (R) is kept enabled for one APB clock cycle. In all other cases, the flip-flop output (OUT) is refreshed on rising edge of the GCLK\_CCL, as shown in Table 40-3.

#### Table 40-3. JK Characteristics

| R | J | К | Ουτ                    |

|---|---|---|------------------------|

| 1 | Х | Х | Clear                  |

| 0 | 0 | 0 | Hold state (no change) |

| 0 | 0 | 1 | Clear                  |

| 0 | 1 | 0 | Set                    |

| 0 | 1 | 1 | Toggle                 |

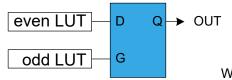

#### Gated D-Latch (DLATCH)

When the DLATCH is selected, the D-input is driven by the even LUT output (), and the G-input is driven by the odd LUT output (), as shown in Figure 40-14.

#### Figure 40-16. D-Latch

When the even LUT is disabled (), the latch output will be cleared.

The G-input is forced enabled for one more APB clock cycle, and the D-input to zero. In all other cases, the latch output (OUT) is refreshed as shown in Table 40-4.

Table 40-4.

D-Latch Characteristics

| G | D | Ουτ                    |

|---|---|------------------------|

| 0 | Х | Hold state (no change) |

| 1 | 0 | Clear                  |

| 1 | 1 | Set                    |

#### **RS Latch (RS)**

When this configuration is selected, the S-input is driven by the even LUT output (), and the R-input is driven by the odd LUT output (), as shown in Figure 40-17.

#### 41.8.16 Offset Correction

| Name:     | OFFSETCORR                               |

|-----------|------------------------------------------|

| Offset:   | 0x14                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15  | 14              | 13  | 12  | 11  | 10               | 9   | 8   |  |  |

|--------|-----|-----------------|-----|-----|-----|------------------|-----|-----|--|--|

|        |     |                 |     |     |     | OFFSETCORR[11:8] |     |     |  |  |

| Access |     |                 |     |     | R/W | R/W              | R/W | R/W |  |  |

| Reset  |     |                 |     |     | 0   | 0                | 0   | 0   |  |  |

|        |     |                 |     |     |     |                  |     |     |  |  |

| Bit    | 7   | 6               | 5   | 4   | 3   | 2                | 1   | 0   |  |  |

|        |     | OFFSETCORR[7:0] |     |     |     |                  |     |     |  |  |

| Access | R/W | R/W             | R/W | R/W | R/W | R/W              | R/W | R/W |  |  |

| Reset  | 0   | 0               | 0   | 0   | 0   | 0                | 0   | 0   |  |  |

Bits 11:0 - OFFSETCORR[11:0] Offset Correction Value

If CTRLC.CORREN=1, these bits define how the ADC conversion result is compensated for offset error before being written to the Result register. This OFFSETCORR value is in two's complement format.

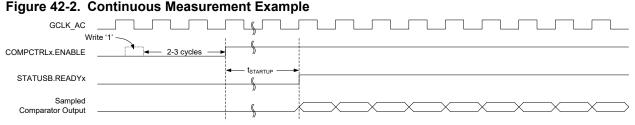

interrupts are also generated. New comparisons are performed continuously until the COMPCTRLx.ENABLE bit is written to zero. The start-up time applies only to the first comparison.

In continuous operation, edge detection of the comparator output for interrupts is done by comparing the current and previous sample. The sampling rate is the GCLK\_AC frequency. An example of continuous measurement is shown in the Figure 42-2.

For low-power operation, comparisons can be performed during sleep modes without a clock. The comparator is enabled continuously, and changes of the comparator state are detected asynchronously. When a toggle occurs, the Power Manager will start GCLK\_AC to register the appropriate peripheral events and interrupts. The GCLK\_AC clock is then disabled again automatically, unless configured to wake up the system from sleep.

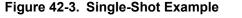

#### 42.6.2.4.2 Single-Shot

Single-shot operation is selected by writing COMPCTRLx.SINGLE to '1'. During single-shot operation, the comparator is normally idle. The user starts a single comparison by writing '1' to the respective Start Comparison bit in the write-only Control B register (CTRLB.STARTx). The comparator is enabled, and after the start-up time has passed, a single comparison is done and STATUSA is updated. Appropriate peripheral events and interrupts are also generated. No new comparisons will be performed.

Writing '1' to CTRLB.STARTx also clears the Comparator x Ready bit in the Status B register (STATUSB.READYx). STATUSB.READYx is set automatically by hardware when the single comparison has completed.

A single-shot measurement can also be triggered by the Event System. Setting the Comparator x Event Input bit in the Event Control Register (EVCTRL.COMPEIx) enables triggering on incoming peripheral events. Each comparator can be triggered independently by separate events. Event-triggered operation is similar to user-triggered operation; the difference is that a peripheral event from another hardware module causes the hardware to automatically start the comparison and clear STATUSB.READYx.

To detect an edge of the comparator output in single-shot operation for the purpose of interrupts, the result of the current measurement is compared with the result of the previous measurement (one sampling period earlier). An example of single-shot operation is shown in Figure 42-3.

For low-power operation, event-triggered measurements can be performed during sleep modes. When the event occurs, the Power Manager will start GCLK\_AC. The comparator is enabled, and after the startup time has passed, a comparison is done and appropriate peripheral events and interrupts are also generated. The comparator and GCLK\_AC are then disabled again automatically, unless configured to wake up the system from sleep.

# SAM L10/L11 Family

DAC – Digital-to-Analog Converter

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Internal DAC output not enabled.                         |

| 1     | Internal DAC output enabled to be used by the AC or ADC. |

Bit 0 – EOEN External Output Enable

| Va | alue | Description                                                                     |

|----|------|---------------------------------------------------------------------------------|

| 0  |      | The DAC output is turned off.                                                   |

| 1  |      | The high-drive output buffer drives the DAC output to the V <sub>OUT</sub> pin. |

# SAM L10/L11 Family

## **Electrical Characteristics**

| Symbol | Parameters                              | Conditions        | Та                   | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------|-------------------|----------------------|------|------|------|------|

| IDD    | DC supply current (Voltage Doubler OFF) | Mode 3,VCC =3.3V  | Max 85°C Typ<br>25°C | -    | 235  | 400  | μA   |

|        |                                         | Mode 2,VCC =3.3V  |                      | -    | 94   | 166  |      |

|        |                                         | Mode 1,VCC =3.3V  |                      | -    | 26   | 47   |      |

|        |                                         | Mode 0 ,VCC =3.3V |                      | -    | 7    | 13   |      |

|        | Voltage Doubler consumption             | VCC =3.3V         |                      | -    | 0.70 | 1.4  |      |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

Table 46-34. Static Characteristics in 1X Gain<sup>(1)</sup>

Table 46-33. Power Consumption<sup>(1)</sup>

| Symbol             | Parameters                          | Conditions | Min. | Тур.      | Max.  | Unit |

|--------------------|-------------------------------------|------------|------|-----------|-------|------|

| G0                 | Open loop gain                      | Mode 3     | -    | 114.5     | -     | dB   |

|                    |                                     | Mode 2     | -    | 117.6     | -     |      |

|                    |                                     | Mode 1     | -    | 116.8     | -     |      |

|                    |                                     | Mode 0     | -    | 108.5     | -     |      |

| GBW                | Gain Bandwidth                      | Mode 3     | -    | 7.1       | -     | MHz  |

|                    |                                     | Mode 2     | -    | 2.8       | -     |      |

|                    |                                     | Mode 1     | -    | 0.85      | -     |      |

|                    |                                     | Mode 0     | -    | 0.2       | -     |      |

| φ <sub>m</sub>     | Phase margin                        | Mode 3     | -    | 71.5      | -     | deg  |

|                    |                                     | Mode 2     | -    | 64        | -     |      |

|                    |                                     | Mode 1     | -    | 56        | -     |      |

|                    |                                     | Mode 0     | -    | 52        | -     |      |

| T <sub>r1</sub>    | Response Time at                    | Mode 3     | -    | 1.3       | -     | μs   |

|                    | 240µV (X1 gain)                     | Mode 2     | -    | 3.3       | -     |      |

|                    |                                     | Mode 1     | -    | 13        | -     |      |

|                    |                                     | Mode 0     | -    | 52        | -     |      |

| ΔT <sub>r1</sub>   | Response Time<br>Variation for 10mV | Mode 3     | -    | 100       | -     | ns   |

| T <sub>start</sub> | Start-up time (Enable               | Mode 3     | -    | 2.7       | -     | μs   |

|                    | to Ready), (Voltage<br>Doubler OFF) | Mode 2     | -    | 6.35      | -     |      |

|                    |                                     | Mode 1     | -    | 21.5      | -     |      |

|                    |                                     | Mode 0     | -    | 88.5      | -     |      |

| Oe                 | Input Offset Voltage                |            | -    | -         | +-3.5 | mV   |

| SR                 | Slew rate                           | Mode 3     | -    | - 2.8/2.6 | -     | V/µs |

|                    |                                     | Mode 2     | -    | -1.2/1.1  | -     |      |

# SAM L10/L11 Family

## **Electrical Characteristics**

| Symbol | Parameter     | Conditions     |     | Min. | Тур. | Max. | Units |

|--------|---------------|----------------|-----|------|------|------|-------|

| tSOSH  | MISO hold     | Slave, VDD>2,7 | 70V | 15   | -    | -    |       |

|        | after SS high | Slave, VDD>1,6 | 62V | 15   | -    | -    |       |

#### Note:

- 1. These values are based on simulation. These values are not covered by test limits in production.

- 2. See I/O Pin Characteristics.

- 3. Where tSLAVE\_OUT is the slave external device output response time, generally tEXT\_SOV +tLINE\_DELAY. <sup>(7)</sup>

- 4. Where tSLAVE\_IN is the slave external device input constraint, generally tEXT\_SIS+tLINE\_DELAY.

- Where tMASTER\_OUT is the master external device output response time, generally tEXT\_MOV +tLINE\_DELAY. <sup>(7)</sup>

- 6. Where tMASTER\_IN is the master external device input constraint, generally tEXT\_MIS +tLINE\_DELAY. <sup>(7)</sup>

- 7. tLINE\_DELAY is the transmission line time delay.

- 8. tEXT\_MIS is the input constraint for the master external device.

- 9. tAPBC is the APB period for SERCOM.

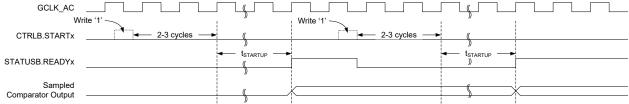

#### Figure 46-5. SPI Timing Requirements in Master Mode

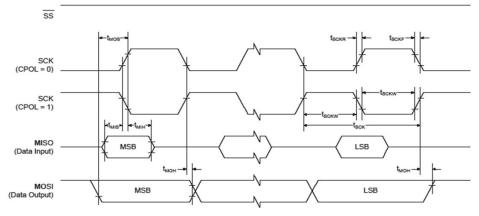

#### Figure 46-6. SPI Timing Requirements in Slave Mode

#### Maximum SPI Frequency