# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 24-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-yf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### SAM L11 Security Features

| Memory Region                | IDAU Region Number for TTx Instructions (IREGION bits) |

|------------------------------|--------------------------------------------------------|

| IOBUS                        | 0x00 (invalid)                                         |

| Others (Reserved, Undefined) | 0x00 (invalid)                                         |

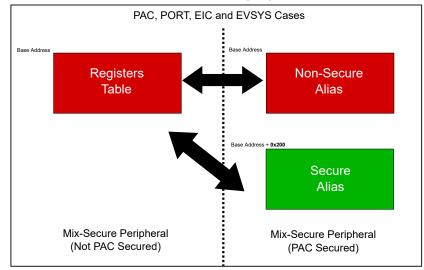

### 13.2.8 Mix-Secure Peripherals

There are five Mix-Secure peripherals that allow internal resources to be shared between the Secure and Non-Secure applications:

- The PAC controller which manages peripherals security attribution (Secure or Non-Secure).

- The Flash memory controller (NVMCTRL) which supports Secure and Non-Secure Flash regions programming.

- The I/O controller (PORT) which allows to individually allocate each I/O to the Secure or Non-Secure applications.

- The External Interrupt Controller (EIC) which allows to individually assign each external interrupt to the Secure or Non-Secure applications.

- The Event System (EVSYS) allows to individually assign each event channel to the Secure or Non-Secure applications.

When a Mix-Secure peripheral is configured as Secure in the PAC, its register map is automatically duplicated in a Secure and Non-Secure alias:

- The Non-Secure alias is at the peripheral base address.

- The Secure alias is located at the peripheral base address:

- + 0x200 offset for the PAC, EIC, PORT and EVSYS peripherals

+ 0x1000 offset for the NVMCTRL peripheral.

## SAM L10/L11 Family Boot ROM

| вооторт      | Verified Areas                               | Verification Method                        |

|--------------|----------------------------------------------|--------------------------------------------|

| 2 or 3       | Flash BS Memory Region<br>+<br>NVM BOCOR row | SHA-256 with BOOTKEY<br>(defined in BOCOR) |

| Other Values | None                                         | -                                          |

If the verification fails, the Boot ROM will report the error to the DSU peripheral and will enter the Boot Interactive mode. This will allow, if a debugger is connected, to put the device in the highest debug level access mode (DAL = 2) by issuing a Chip Erase command. Once in that mode, it is possible for a programming tool to reprogram the different memory regions and/or NVM rows.

When verification fails and no debugger is connected, the part will reset and restart the integrity checks sequences again.

### 14.4.2.3.1 Hash algorithm (SHA-256) Verification Method

The verifications are done using the standard SHA256 hash algorithm.

Both Flash BS region and NVM BOCOR row hashes are computed on the defined memory/row area and compared to their expected reference hash value.

Note: The hash consists of 256 bits, i.e. 32 bytes.

#### SHA256 with BOOTKEY Variant

To prevent unauthorized change of the bootloader code, the hash computation can be slightly modified to require a key to produce a valid hash.

When SHA with BOOTKEY is selected (BOOTOPT=2 or =3), the hash computation (for both Flash BS region and NVM BOCOR row) starts by processing the secure boot key (BOOTKEY) data twice, then proceeds with the rest of data.

This secure boot key (BOOTKEY) is located in the NVM Boot Configuration row (BOCOR) at [0x80C0050:0x80C006F]:

| BOCOR Offset | Bit Position | Name    |

|--------------|--------------|---------|

| 0x50-0x6F    | 895:640      | BOOTKEY |

### 14.4.2.3.2 BS Verification

When BOOTOPT>0, the bootloader authentication starts allowing a secure bootloader code to be protected against inadvertent or malicious changes.

The hash is computed on the Flash Secure BOOT and Flash Non-Secure Callable BOOT (BNSC) regions.

The hash reference value for this area is stored at the end of the Secure BOOT area, just before the Non-Secure Callable BOOT (BNSC) one.

Note: The last 256 bits where the hash is stored are not included in the hash computation.

2. When DAL=1 DAP transfers are always non-secure. The DSU internal address space can only be accessed by secure masters.

Some features not activated by APB transactions are not available when the device is protected:

| Features                     | Availability when DAL equals to |                       |     |  |  |

|------------------------------|---------------------------------|-----------------------|-----|--|--|

|                              | 0x0                             | 0x1<br>(SAM L11 only) | 0x2 |  |  |

| CPU Reset Extension          | Yes                             | Yes                   | Yes |  |  |

| Clear CPU Reset<br>extension | Yes                             | Yes                   | Yes |  |  |

| Debugger Cold-Plugging       | Yes                             | Yes                   | Yes |  |  |

| Debugger Hot-Plugging        | No                              | Yes                   | Yes |  |  |

Table 16-2. Feature Availability Under Protection

### **16.9** Device Identification

Device identification relies on the ARM CoreSight component identification scheme, which allows the chip to be identified as a SAM device implementing a DSU. The DSU contains identification registers to differentiate the device.

### 16.9.1 CoreSight Identification

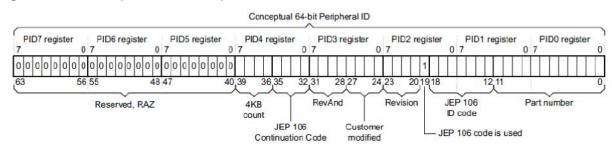

A system-level ARM<sup>®</sup> CoreSight<sup>™</sup> ROM table is present in the device to identify the vendor and the chip identification method. Its address is provided in the MEM-AP BASE register inside the ARM Debug Access Port. The CoreSight ROM implements a 64-bit conceptual ID composed as follows from the PID0 to PID7 CoreSight ROM Table registers:

### Figure 16-5. Conceptual 64-bit Peripheral ID

| Table 16-3. | Conceptual 64-Bit | Peripheral ID Bit | Descriptions |

|-------------|-------------------|-------------------|--------------|

|-------------|-------------------|-------------------|--------------|

| Field           | Size | Description                                          | Location  |

|-----------------|------|------------------------------------------------------|-----------|

| JEP-106 CC code | 4    | Continuation code: 0x0                               | PID4      |

| JEP-106 ID code | 7    | Device ID: 0x1F                                      | PID1+PID2 |

| 4KB count       | 4    | Indicates that the CoreSight component is a ROM: 0x0 | PID4      |

| RevAnd          | 4    | Not used; read as 0                                  | PID3      |

| CUSMOD          | 4    | Not used; read as 0                                  | PID3      |

### DSU - Device Service Unit

|        | Name:<br>Offset:<br>Reset:<br>Property: | MEMTYPE<br>0x1FCC<br>0x0000000x<br>- |    |    |    |    |    |       |

|--------|-----------------------------------------|--------------------------------------|----|----|----|----|----|-------|

| Bit    | 31                                      | 30                                   | 29 | 28 | 27 | 26 | 25 | 24    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

|        |                                         |                                      |    |    |    |    |    |       |

| Bit    | 23                                      | 22                                   | 21 | 20 | 19 | 18 | 17 | 16    |

|        |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| D.4    | 45                                      |                                      | 10 | 10 | 44 | 10 | 0  | 0     |

| Bit    | 15                                      | 14                                   | 13 | 12 | 11 | 10 | 9  | 8     |

| A      |                                         |                                      |    |    |    |    |    |       |

| Access |                                         |                                      |    |    |    |    |    |       |

| Reset  |                                         |                                      |    |    |    |    |    |       |

| Bit    | 7                                       | 6                                    | 5  | 4  | 3  | 2  | 1  | 0     |

|        |                                         |                                      |    |    |    |    |    | SMEMP |

| Access |                                         |                                      |    |    |    |    |    | R     |

| Reset  |                                         |                                      |    |    |    |    |    | x     |

|        |                                         |                                      |    |    |    |    |    |       |

### 16.12.16 CoreSight ROM Table Memory Type

### Bit 0 - SMEMP System Memory Present

This bit indicates whether system memory is present on the bus that connects to the ROM table.

This bit is set at power-up if the device is not protected, indicating that the system memory is accessible from a debug adapter.

This bit is cleared at power-up if the device is protected, indicating that the system memory is not accessible from a debug adapter.

#### 18.8.4 Peripheral Channel Control

| Name:     | PCHCTRLm              |

|-----------|-----------------------|

| Offset:   | 0x80 + m*0x04 [m=020] |

| Reset:    | 0x0000000             |

| Property: | PAC Write-Protection  |

PCHTRLm controls the settings of Peripheral Channel number m (m=0..20).

| Bit    | 31      | 30   | 29 | 28 | 27 | 26  | 25       | 24  |

|--------|---------|------|----|----|----|-----|----------|-----|

|        |         |      |    |    |    |     |          |     |

| Access |         |      | •  |    |    |     |          |     |

| Reset  |         |      |    |    |    |     |          |     |

|        |         |      |    |    |    |     |          |     |

| Bit    | 23      | 22   | 21 | 20 | 19 | 18  | 17       | 16  |

|        |         |      |    |    |    |     |          |     |

| Access |         |      |    |    |    | •   |          |     |

| Reset  |         |      |    |    |    |     |          |     |

|        |         |      |    |    |    |     |          |     |

| Bit    | 15      | 14   | 13 | 12 | 11 | 10  | 9        | 8   |

|        |         |      |    |    |    |     |          |     |

| Access |         |      |    |    |    |     |          |     |

| Reset  |         |      |    |    |    |     |          |     |

|        |         |      |    |    |    |     |          |     |

| Bit    | 7       | 6    | 5  | 4  | 3  | 2   | 1        | 0   |

|        | WRTLOCK | CHEN |    |    |    |     | GEN[2:0] |     |

| Access | R/W     | R/W  | •  |    | •  | R/W | R/W      | R/W |

| Reset  | 0       | 0    |    |    |    | 0   | 0        | 0   |

### Bit 7 – WRTLOCK Write Lock

After this bit is set to '1', further writes to the PCHCTRLm register will be discarded. The control register of the corresponding Generator n (GENCTRLn), as assigned in PCHCTRLm.GEN, will also be locked. It can only be unlocked by a Power Reset.

Note that Generator 0 cannot be locked.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The Peripheral Channel register and the associated Generator register are not locked |

| 1     | The Peripheral Channel register and the associated Generator register are locked     |

### Bit 6 – CHEN Channel Enable

This bit is used to enable and disable a Peripheral Channel.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Peripheral Channel is disabled |

| 1     | The Peripheral Channel is enabled  |

#### Bits 2:0 – GEN[2:0] Generator Selection

This bit field selects the Generator to be used as the source of a peripheral clock, as shown in the table below:

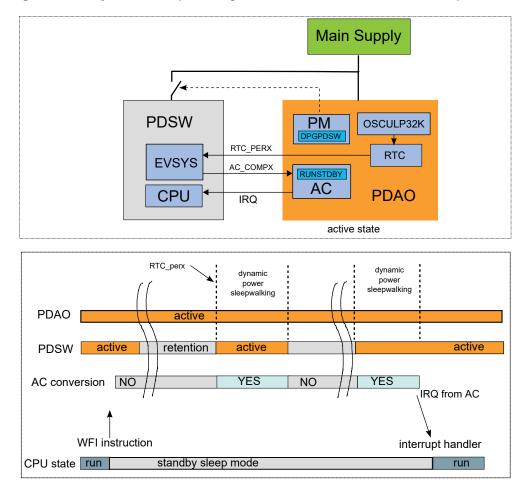

Dynamic SleepWalking based on event is illustrated in the following example:

### Figure 22-8. Dynamic SleepWalking based on Event: AC Periodic Comparison

The Analog Comparator (AC) peripheral is used in single shot mode to monitor voltage levels on input pins. A comparator interrupt, based on the AC peripheral configuration, is generated to wake up the device. In the GCLK module, the AC generic clock (GCLK\_AC) source is routed a 32.768kHz oscillator (for low power applications, OSC32KULP is recommended). RTC and EVSYS modules are configured to generate periodic events to the AC. To make the comparator continue to run in standby sleep mode, the RUNSTDBY bit is written to '1'. To enable the dynamic SleepWalking for PDSW power domain, STDBYCFG.PDSW must be written to '1'.

*Entering standby mode*: The Power Manager sets the PDSW power domain in retention state. The AC comparators, COMPx, are OFF. The GCLK\_AC clock is stopped. The VDDCORE is supplied by the low power regulator.

*Dynamic SleepWalking*: The RTC event (RTC\_PERX) is routed by the Event System to the Analog Comparator to trigger a single-shot measurement. This event is detected by the Power Manager, which sets the PDSW power domain to active state and starts the main voltage regulator.

After enabling the AC comparator and starting the GCLK\_AC, the single-shot measurement can be performed during Sleep mode (sleepwalking task), refer to 42.6.14.2 Single-Shot Measurement during Sleep for details. At the end of the conversion, if conditions to generate an interrupt are not met, the GCLK\_AC clock is stopped again, as well as the AC comparator.

© 2018 Microchip Technology Inc.

Example (fractional mode): assuming  $F_{CKR}$  = 32kHz and  $F_{CK}$  = 48.006MHz, the multiplication ratio is 1500.1875 (1500 + 3/16). Thus LDR is set to 1499 and LDRFRAC to 3.

### **Related Links**

- 18. GCLK Generic Clock Controller

- 24. OSC32KCTRL 32KHz Oscillators Controller

### 23.6.7.1 Basic Operation

### 23.6.7.1.1 Initialization, Enabling, Disabling, and Resetting

The DPLLC is enabled by writing a '1' to the Enable bit in the DPLL Control A register (DPLLCTRLA.ENABLE). The DPLLC is disabled by writing a zero to this bit.

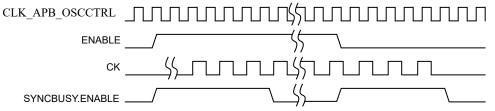

The DPLLSYNCBUSY.ENABLE is set when the DPLLCTRLA.ENABLE bit is modified. It is cleared when the DPLL output clock CK has sampled the bit at the high level after enabling the DPLL. When disabling the DPLL, DPLLSYNCBUSY.ENABLE is cleared when the output clock is no longer running.

### Figure 23-4. Enable Synchronization Busy Operation

The frequency of the DPLL output clock CK is stable when the module is enabled and when the Lock bit in the DPLL Status register is set (DPLLSTATUS.LOCK).

When the Lock Time bit field in the DPLL Control B register (DPLLCTRLB.LTIME) is non-zero, a user defined lock time is used to validate the lock operation. In this case the lock time is constant. If DPLLCTRLB.LTIME=0, the lock signal is linked with the status bit of the DPLL, and the lock time varies depending on the filter selection and the final target frequency.

**Note:** GCLK\_DPLL\_32K is responsible for counting the user defined lock time (LTIME different from 0x0), hence must be enabled.

When the Wake Up Fast bit (DPLLCTRLB.WUF) is set, the wake up fast mode is activated. In this mode the clock gating cell is enabled at the end of the startup time. At this time the final frequency is not stable, as it is still during the acquisition period, but it allows to save several milliseconds. After first acquisition, the Lock Bypass bit (DPLLCTRLB.LBYPASS) indicates if the lock signal is discarded from the control of the clock gater (CG) generating the output clock CLK\_DPLL.

| Table 23-3. | CLK DPLL | Behavior from | Startup to F | First Edge Detection |

|-------------|----------|---------------|--------------|----------------------|

|             |          |               |              |                      |

| WUF | LTIME             | CLK_DPLL Behavior                                                    |

|-----|-------------------|----------------------------------------------------------------------|

| 0   | 0                 | Normal Mode: First Edge when lock is asserted                        |

| 0   | Not Equal To Zero | Lock Timer Timeout mode: First Edge when the timer down-counts to 0. |

| 1   | Х                 | Wake Up Fast Mode: First Edge when CK is active (startup time)       |

### **OSCCTRL – Oscillators Controller**

| Offset | Name          | Bit Pos. |          |          |       |         |           |              |            |        |

|--------|---------------|----------|----------|----------|-------|---------|-----------|--------------|------------|--------|

|        |               | 7:0      |          |          |       |         | DELAY     |              | ENABLE     |        |

|        | DFLLULPSYNCBU | 15:8     |          |          |       |         |           |              |            |        |

| 0x28   | SY            | 23:16    |          |          |       |         |           |              |            |        |

|        |               | 31:24    |          |          |       |         |           |              |            |        |

| 0x2C   | DPLLCTRLA     | 7:0      | ONDEMAND | RUNSTDBY |       |         |           |              | ENABLE     |        |

| 0x2D   |               |          |          |          |       |         |           |              |            |        |

|        | Reserved      |          |          |          |       |         |           |              |            |        |

| 0x2F   |               |          |          |          |       |         |           |              |            |        |

|        |               | 7:0      |          |          |       | LDF     | R[7:0]    |              |            |        |

| 0x30   | DPLLRATIO     | 15:8     |          |          |       |         |           | LDR[11:8]    |            |        |

| 0,50   | DPLLRATIO     | 23:16    |          |          |       |         |           | LDRFRAC[3:0] |            |        |

|        |               | 31:24    |          |          |       |         |           |              |            |        |

|        |               | 7:0      |          |          | REFCL | _K[1:0] | WUF       | LPEN         | FILTE      | R[1:0] |

| 0x34   | DPLLCTRLB     | 15:8     |          |          |       | LBYPASS |           |              | LTIME[2:0] |        |

| 0x34   | DFLLCTRLB     | 23:16    | DIV[7:0] |          |       |         |           |              |            |        |

|        |               | 31:24    |          |          |       |         |           | DIV[10:8]    |            |        |

| 0x38   | DPLLPRESC     | 7:0      |          |          |       |         |           |              | PRES       | C[1:0] |

| 0x39   |               |          |          |          |       |         |           |              |            |        |

|        | Reserved      |          |          |          |       |         |           |              |            |        |

| 0x3B   |               |          |          |          |       |         |           |              |            |        |

| 0x3C   | DPLLSYNCBUSY  | 7:0      |          |          |       |         | DPLLPRESC | DPLLRATIO    | ENABLE     |        |

| 0x3D   |               |          |          |          |       |         |           |              |            |        |

|        | Reserved      |          |          |          |       |         |           |              |            |        |

| 0x3F   |               |          |          |          |       |         |           |              |            |        |

| 0x40   | DPLLSTATUS    | 7:0      |          |          |       |         |           |              | CLKRDY     | LOCK   |

### 23.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Write-protection is denoted by the "PAC Write-Protection" property in each individual register description. Refer to the 23.5.8 Register Access Protection section and the PAC - Peripheral Access Controller chapter for details.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" or "Write-Synchronized" property in each individual register description. Refer to the section on Synchronization for details.

### **OSCCTRL – Oscillators Controller**

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0xE          | 16384                               | 3                              | 500000                              |

| 0xF          | 32768                               | 3                              | 1000000                             |

#### Note:

- 1. Actual startup time is 1 OSCULP32K cycle + 3 XOSC cycles.

- 2. The given time neglects the three XOSC cycles before OSCULP32K cycle.

### Bit 11 – AMPGC Automatic Amplitude Gain Control

**Note:** This bit must be set only after the XOSC has settled, indicated by the XOSC Ready flag in the Status register (STATUS.XOSCRDY).

| Value | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The automatic amplitude gain control is disabled.                                                                                   |

| 1     | The automatic amplitude gain control is enabled. Amplitude gain will be automatically adjusted during Crystal Oscillator operation. |

### Bits 10:8 – GAIN[2:0] Oscillator Gain

These bits select the gain for the oscillator. The listed maximum frequencies are recommendations, and might vary based on capacitive load and crystal characteristics. Those bits must be properly configured even when the Automatic Amplitude Gain Control is active.

| Value   | Recommended Max Frequency [MHz] |

|---------|---------------------------------|

| 0x0     | 2                               |

| 0x1     | 4                               |

| 0x2     | 8                               |

| 0x3     | 16                              |

| 0x4     | 30                              |

| 0x5-0x7 | Reserved                        |

### Bit 7 – ONDEMAND On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled, depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

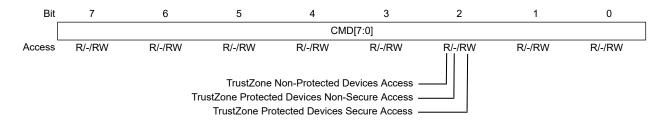

On SAM L11 devices, the Mix-Secure peripheral has different types of registers (Non-Secure, Secure, Write-Secure, Mix-Secure, and Write-Mix-Secure) with different access permissions for each bitfield. Refer to *Mix-Secure Peripherals* for more details. In the following register descriptions, the access permissions are specified as shown in the following figure.

### 33.6 Register Summary

#### Important:

For SAM L11, the EVSYS register map is automatically duplicated in a Secure and Non-Secure alias:

- The Non-Secure alias is at the peripheral base address

- The Secure alias is located at the peripheral base address + 0x200

Refer to *Mix-Secure Peripherals* for more information on register access rights

| Offset | Name        | Bit Pos. |          |          |       |           |           |           |           |

|--------|-------------|----------|----------|----------|-------|-----------|-----------|-----------|-----------|

| 0x00   | CTRLA       | 7:0      |          |          |       |           |           |           | SWRST     |

| 0x01   |             |          |          |          |       |           |           |           |           |

|        | Reserved    |          |          |          |       |           |           |           |           |

| 0x03   |             |          |          |          |       |           |           |           |           |

|        |             | 7:0      |          |          | CHANI | NEL[7:0]  |           |           |           |

| 0x04   | SWEVT       | 15:8     |          |          |       |           |           |           |           |

| 0.04   | SWEVT       | 23:16    |          |          |       |           |           |           |           |

|        |             | 31:24    |          |          |       |           |           |           |           |

| 0x08   | PRICTRL     | 7:0      | RREN     |          |       |           |           | PRI       | [1:0]     |

| 0x09   |             |          |          |          |       |           |           |           |           |

|        | Reserved    |          |          |          |       |           |           |           |           |

| 0x0F   |             |          |          |          |       |           |           |           |           |

| 0x10   | INTPEND     | 7:0      |          |          |       |           |           | ID[       | 1:0]      |

| 0,10   |             | 15:8     | BUSY     | READY    |       |           |           | EVD       | OVR       |

| 0x12   |             |          |          |          |       |           |           |           |           |

|        | Reserved    |          |          |          |       |           |           |           |           |

| 0x13   |             |          |          |          |       |           |           |           |           |

|        |             | 7:0      |          |          |       | CHINT3    | CHINT2    | CHINT1    | CHINT0    |

| 0x14   | INTSTATUS   | 15:8     |          |          |       |           |           |           |           |

| 0,14   |             | 23:16    |          |          |       |           |           |           |           |

|        |             | 31:24    |          |          |       |           |           |           |           |

|        |             | 7:0      |          |          |       | BUSYCHx3  | BUSYCHx2  | BUSYCHx1  | BUSYCHx0  |

| 0x18   | BUSYCH      | 15:8     |          |          |       |           |           |           |           |

| 0210   | BUSTCH      | 23:16    |          |          |       |           |           |           |           |

|        |             | 31:24    |          |          |       |           |           |           |           |

|        |             | 7:0      |          |          |       | READYUSR3 | READYUSR2 | READYUSR1 | READYUSR0 |

| 0.40   |             | 15:8     |          |          |       |           |           |           |           |

| 0x1C   | READYUSR    | 23:16    |          |          |       |           |           |           |           |

|        |             | 31:24    |          |          |       |           |           |           |           |

|        |             | 7:0      |          |          |       | EVGE      | N[5:0]    |           |           |

| 000    |             | 15:8     | ONDEMAND | RUNSTDBY |       | EDGS      |           | PATH      | H[1:0]    |

| 0x20   | CHANNEL0    | 23:16    |          |          |       |           |           |           |           |

|        |             | 31:24    |          |          |       |           |           |           |           |

| 0x24   | CHINTENCLR0 | 7:0      |          |          |       |           |           | EVD       | OVR       |

| 0x25   | CHINTENSET0 | 7:0      |          |          |       |           |           | EVD       | OVR       |

### 35.8.8 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x18    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7     | 6 | 5     | 4     | 3   | 2   | 1   | 0   |

|--------|-------|---|-------|-------|-----|-----|-----|-----|

|        | ERROR |   | RXBRK | CTSIC | RXS | RXC | TXC | DRE |

| Access | R/W   |   | R/W   | R/W   | R/W | R   | R/W | R   |

| Reset  | 0     |   | 0     | 0     | 0   | 0   | 0   | 0   |

### Bit 7 – ERROR Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. Errors that will set this flag are COLL, ISF, BUFOVF, FERR, and PERR.Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

### Bit 5 – RXBRK Receive Break

This flag is cleared by writing '1' to it.

This flag is set when auto-baud is enabled (CTRLA.FORM) and a break character is received.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

### Bit 4 – CTSIC Clear to Send Input Change

This flag is cleared by writing a '1' to it.

This flag is set when a change is detected on the CTS pin.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

### Bit 3 – RXS Receive Start

This flag is cleared by writing '1' to it.

This flag is set when a start condition is detected on the RxD line and start-of-frame detection is enabled (CTRLB.SFDE is '1').

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Start interrupt flag.

#### Bit 2 – RXC Receive Complete

This flag is cleared by reading the Data register (DATA) or by disabling the receiver.

This flag is set when there are unread data in DATA.

Writing '0' to this bit has no effect.

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

### Related Links

15. PAC - Peripheral Access Controller

### 36.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

### 36.5.10 Analog Connections

Not applicable.

### 36.6 Functional Description

### 36.6.1 Principle of Operation

The SPI is a high-speed synchronous data transfer interface It allows high-speed communication between the device and peripheral devices.

The SPI can operate as master or slave. As master, the SPI initiates and controls all data transactions. The SPI is single buffered for transmitting and double buffered for receiving.

When transmitting data, the Data register can be loaded with the next character to be transmitted during the current transmission.

When receiving, the data is transferred to the two-level or four-level receive buffer, and the receiver is ready for a new character.

The SPI transaction format is shown in SPI Transaction Format. Each transaction can contain one or more characters. The character size is configurable, and can be either 8 or 9 bits.

#### Figure 36-2. SPI Transaction Format

|           | •        | Character   | <br>Transaction |             |  |

|-----------|----------|-------------|-----------------|-------------|--|

| MOSI/MISO | $\times$ | Character 0 | Character 1     | Character 2 |  |

| _SS       |          |             |                 |             |  |

### 38.7.1.5 Interrupt Enable Clear

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

| [      |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

**Bit 4 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will clear the corresponding Match or Capture Channel x Interrupt Enable bit, which disables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

### Bit 1 – ERR Error Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

### Bit 0 – OVF Overflow Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

### 38.7.2.4 Event Control

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x06                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15 | 14 | 13    | 12    | 11 | 10  | 9          | 8     |

|--------|----|----|-------|-------|----|-----|------------|-------|

|        |    |    | MCEOx | MCEOx |    |     |            | OVFEO |

| Access |    |    | R/W   | R/W   |    |     |            | R/W   |

| Reset  |    |    | 0     | 0     |    |     |            | 0     |

|        |    |    |       |       |    |     |            |       |

| Bit    | 7  | 6  | 5     | 4     | 3  | 2   | 1          | 0     |

|        |    |    | TCEI  | TCINV |    |     | EVACT[2:0] |       |

| Access |    |    | R/W   | R/W   |    | R/W | R/W        | R/W   |

| Reset  |    |    | 0     | 0     |    | 0   | 0          | 0     |

**Bits 13,12 – MCEOx** Match or Capture Channel x Event Output Enable [x = 1..0] These bits enable the generation of an event for every match or capture on channel x.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Match/Capture event on channel x is disabled and will not be generated.              |

| 1     | Match/Capture event on channel x is enabled and will be generated for every compare/ |

|       | capture.                                                                             |

### Bit 8 - OVFEO Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

### Bit 5 - TCEI TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |  |  |

|-------|-------------------------------|--|--|

| 0     | Incoming events are disabled. |  |  |

| 1     | Incoming events are enabled.  |  |  |

### Bit 4 – TCINV TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Input event source is not inverted. |

| 1     | Input event source is inverted.     |

### Bits 2:0 – EVACT[2:0] Event Action

These bits define the event action the TC will perform on an event.

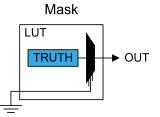

### Figure 40-3. Masked Input Selection

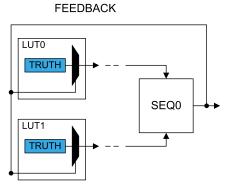

### Internal Feedback Inputs (FEEDBACK)

When selected (LUTCTRLx.INSELy=FEEDBACK), the Sequential (SEQ) output is used as input for the corresponding LUT.

The output from an internal sequential sub-module can be used as input source for the LUT, see figure below for an example for LUT0 and LUT1. The sequential selection for each LUT follows the formula:

IN[2N][i] = SEQ[N]

IN[2N+1][i] = SEQ[N]

With *N* representing the sequencer number and i=0,1,2 representing the LUT input index.

For details, refer to 40.6.2.7 Sequential Logic.

### Figure 40-4. Feedback Input Selection

### Linked LUT (LINK)

When selected (LUTCTRLx.INSELy=LINK), the subsequent LUT output is used as the LUT input (e.g., LUT2 is the input for LUT1), as shown in this figure:

### 41.8.11 Average Control

| Name:     | AVGCTRL                                  |

|-----------|------------------------------------------|

| Offset:   | 0x0C                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7 | 6   | 5           | 4   | 3   | 2      | 1        | 0   |

|--------|---|-----|-------------|-----|-----|--------|----------|-----|

|        |   |     | ADJRES[2:0] |     |     | SAMPLE | NUM[3:0] |     |

| Access |   | R/W | R/W         | R/W | R/W | R/W    | R/W      | R/W |

| Reset  |   | 0   | 0           | 0   | 0   | 0      | 0        | 0   |

**Bits 6:4 – ADJRES[2:0]** Adjusting Result / Division Coefficient These bits define the division coefficient in 2n steps.

### Bits 3:0 - SAMPLENUM[3:0] Number of Samples to be Collected

These bits define how many samples are added together. The result will be available in the Result register (RESULT). Note: if the result width increases, CTRLC.RESSEL must be changed.

| Value | Description  |

|-------|--------------|

| 0x0   | 1 sample     |

| 0x1   | 2 samples    |

| 0x2   | 4 samples    |

| 0x3   | 8 samples    |

| 0x4   | 16 samples   |

| 0x5   | 32 samples   |

| 0x6   | 64 samples   |

| 0x7   | 128 samples  |

| 0x8   | 256 samples  |

| 0x9   | 512 samples  |

| 0xA   | 1024 samples |

| 0xB - | Reserved     |

| 0xF   |              |

### **OPAMP – Operational Amplifier Controller**

| Value | Name   | Description                                       |

|-------|--------|---------------------------------------------------|

| 0x0   | Mode 0 | Minimum current consumption, but the slowest mode |

| 0x1   | Mode 1 | Low current consumption, slow speed               |

| 0x2   | Mode 2 | High current consumption, fast speed              |

| 0x3   | Mode 3 | Maximum current consumption but the fastest mode  |

### Bit 2 – ANAOUT Analog Output

This bit controls a switch connected to the OPAMP output.

| Value | Description                                                      |  |

|-------|------------------------------------------------------------------|--|

| 0     | Switch open. No ADC or AC connection.                            |  |

| 1     | Switch closed. OPAMP output is connected to the ADC or AC input. |  |

### Bit 1 – ENABLE Operational Amplifier Enable

| Value | Description            |  |

|-------|------------------------|--|

| 0     | The OPAMPx is disabled |  |

| 1     | The OPAMPx is enabled  |  |

### **Electrical Characteristics**

| Symbol                            | Description                               | Conditions | Fmax       | Fmax.      |     |

|-----------------------------------|-------------------------------------------|------------|------------|------------|-----|

|                                   |                                           |            | PL0        | PL2        |     |

| f <sub>GCLK_DPLL</sub>            | FDPLL96M Reference clock frequency        | -          | 2          | 2          | MHz |

| f <sub>GCLK_DPLL_32K</sub>        | FDPLL96M 32K clock frequency              | -          | 32.7<br>68 | 32.7<br>68 | kHz |

| f <sub>GCLK_EIC</sub>             | EIC input clock frequency                 | -          | 12         | 48         | MHz |

| f <sub>GCLK_EVSYS_CHANNEL_0</sub> | EVSYS channel 0 input clock frequency     | -          | 12         | 48         | MHz |

| $f_{GCLK\_EVSYS\_CHANNEL\_1}$     | EVSYS channel 1 input clock frequency     | -          |            |            |     |

| f <sub>GCLK_EVSYS_CHANNEL_2</sub> | EVSYS channel 2 input clock frequency     | -          |            |            |     |

| $f_{GCLK\_EVSYS\_CHANNEL\_3}$     | EVSYS channel 3 input clock frequency     | -          |            |            |     |

| f <sub>GCLK_SERCOM0_SLOW</sub>    | Common SERCOM0 slow input clock frequency | -          | 1          | 5          | MHz |

| f <sub>GCLK_SERCOM1_SLOW</sub>    | Common SERCOM1 slow input clock frequency | -          |            |            |     |

| f <sub>GCLK_SERCOM2_SLOW</sub>    | Common SERCOM2 slow input clock frequency | -          |            |            |     |

| fgclk_sercom0_core                | SERCOM0 input clock frequency             | -          | 12         | 48         | MHz |

| fGCLK_SERCOM1_CORE                | SERCOM1 input clock frequency             | -          |            |            |     |

| f <sub>GCLK_SERCOM2_CORE</sub>    | SERCOM2 input clock frequency             | -          |            |            |     |

| f <sub>GCLK_TC0</sub>             | TC0 input clock frequency                 | -          | 12         | 48         | MHz |

| f <sub>GCLK_TC1</sub>             | TC1 input clock frequency                 | -          |            |            |     |

| f <sub>GCLK_TC2</sub>             | TC2 input clock frequency                 | -          |            |            |     |

| f <sub>GCLK_ADC</sub>             | ADC input clock frequency                 | -          | 12         | 48         | MHz |

| f <sub>GCLK_AC</sub>              | AC digital input clock frequency          | -          |            |            |     |

| f <sub>GCLK_DAC</sub>             | DAC input clock frequency                 | -          |            |            |     |

| f <sub>GCLK_FREQM_MSR</sub>       | FREQM measured clock frequency            | -          |            |            |     |

| f <sub>GCLK_FREQM_REF</sub>       | FREQM reference clock frequency           | -          |            |            |     |

| f <sub>GCLK_PTC</sub>             | PTC input clock frequency                 | -          |            |            |     |

| f <sub>GCLK_CCL</sub>             | CCL input clock frequency                 | -          |            |            |     |

| f <sub>GCLKin</sub>               | External GCLK input clock frequency       | -          |            |            |     |

### Note:

1. These values are based on simulation. They are not covered by production test limits or characterization.

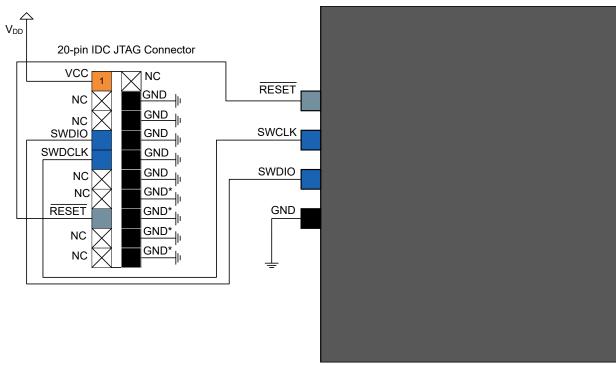

### Figure 50-13. 20-pin IDC JTAG Connector

### Table 50-9. 20-pin IDC JTAG Connector

| Header Signal Name | Description                                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWDCLK             | Serial wire clock pin                                                                                                                                                             |

| SWDIO              | Serial wire bidirectional data pin                                                                                                                                                |

| RESET              | Target device reset pin, active low                                                                                                                                               |

| VCC                | Target voltage sense, should be connected to the device $V_{DD}$                                                                                                                  |

| GND                | Ground                                                                                                                                                                            |

| GND*               | These pins are reserved for firmware extension purposes. They can be left unconnected or connected to GND in normal debug environment. They are not essential for SWD in general. |

### 50.8 Peripherals Considerations

### **ADC Accuracy**

The ADC accuracy may depend on different parameters, such as its input sources, as well as its conversion speed.

Please refer to the *Analog-to-Digital Converter (ADC) Characteristics* section in the *Electrical Characteristics* chapters for more details.