# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 24-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d15a-yu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 13. SAM L11 Security Features

This chapter provides an overview of the SAM L11 security features.

# 13.1 Features

Security features can be split in two main categories.

The first category relates to the ARM TrustZone for Cortex-M technology features:

- Flexible hardware isolation of memories and peripherals:

- Up to six regions for the Flash

- Up to two regions for the Data Flash

- Up to two regions for the SRAM

- Individual security attribution (secure or non-secure) for each peripheral using the Peripheral Access Controller (PAC)

- Mix-secure peripherals which support both secure and non-secure security attributions

- Three debug access levels allowing:

- The highest debug level with no restrictions in term of memory and peripheral accesses

- A restricted debug level with non-secure memory regions access only

- The lowest debug level where no access is authorized except with a debugger using a Boot ROM-specific mode

- Different chip erase support according to security settings

- Security configuration is fully stored in Flash and safely auto-loaded at startup during Boot ROM execution using CRC checks

**Important:** Debug access levels, such as Chip Erase support are described in the Boot ROM chapter.

The second category relates to the extra security features which are not related to ARM TrustZone for Cortex-M technology support:

- Built-in cryptographic accelerator accessible through cryptographic libraries stored in ROM

- Supporting AES-128 encryption/decryption, SHA-256 authentication, GCM encryption and authentication

- Cryptographic libraries are especially designed for side channel and fault injection attacks prevention

- One True Random Generator (TRNG)

- Secure Boot, which performs integrity check on a configurable portion of the Flash (BS memory area)

- Secure Pin Multiplexing to isolate on dedicated SERCOM I/O pins a secured communication with external devices from the non secure application

- Data Flash

- Optimized for secrets storage

- Data Scrambling with user-defined key (optional)

# DSU - Device Service Unit

#### 16.12.21 Peripheral Identification 3

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID3<br>0x1FEC<br>0x00000000<br>- |         |    |    |    |         |    |

|--------|-----------------------------------------|-----------------------------------|---------|----|----|----|---------|----|

| Bit    | 31                                      | 30                                | 29      | 28 | 27 | 26 | 25      | 24 |

|        |                                         |                                   |         |    |    |    |         |    |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

|        |                                         |                                   |         |    |    |    |         |    |

| Bit    | 23                                      | 22                                | 21      | 20 | 19 | 18 | 17      | 16 |

|        |                                         |                                   |         |    |    |    |         |    |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Bit    | 15                                      | 14                                | 13      | 12 | 11 | 10 | 9       | 8  |

| DIL    | 15                                      | 14                                | 13      | 12 | 11 | 10 | 9       | 0  |

| Access |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Reset  |                                         |                                   |         |    |    |    |         |    |

| Bit    | 7                                       | 6                                 | 5       | 4  | 3  | 2  | 1       | 0  |

|        |                                         |                                   | ND[3:0] |    |    |    | DD[3:0] |    |

| Access | R                                       | R                                 | R       | R  | R  | R  | R       | R  |

| Reset  | 0                                       | 0                                 | 0       | 0  | 0  | 0  | 0       | 0  |

|        |                                         |                                   |         |    |    |    |         |    |

**Bits 7:4 – REVAND[3:0]** Revision Number These bits will always return 0x0 when read.

Bits 3:0 – CUSMOD[3:0] ARM CUSMOD

These bits will always return 0x0 when read.

#### 19.8.7 APBA Mask

| Name:     | APBAMASK             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x000007FFF          |

| Property: | PAC Write-Protection |

| Bit    | 31   | 30       | 29         | 28      | 27    | 26   | 25  | 24  |

|--------|------|----------|------------|---------|-------|------|-----|-----|

|        |      |          |            |         |       |      |     |     |

| Access |      |          |            |         |       |      |     |     |

| Reset  |      |          |            |         |       |      |     |     |

|        |      |          |            |         |       |      |     |     |

| Bit    | 23   | 22       | 21         | 20      | 19    | 18   | 17  | 16  |

|        |      |          |            |         |       |      |     |     |

| Access |      |          | I I        |         |       |      |     |     |

| Reset  |      |          |            |         |       |      |     |     |

|        |      |          |            |         |       |      |     |     |

| Bit    | 15   | 14       | 13         | 12      | 11    | 10   | 9   | 8   |

|        |      | Reserved | AC         | PORT    | FREQM | EIC  | RTC | WDT |

| Access |      | R/W      | R/W        | R/W     | R/W   | R/W  | R/W | R/W |

| Reset  |      | 1        | 1          | 1       | 1     | 1    | 1   | 1   |

|        |      |          |            |         |       |      |     |     |

| Bit    | 7    | 6        | 5          | 4       | 3     | 2    | 1   | 0   |

|        | GCLK | SUPC     | OSC32KCTRL | OSCCTRL | RSTC  | MCLK | PM  | PAC |

| Access | R/W  | R/W      | R/W        | R/W     | R/W   | R/W  | R/W | R/W |

| Reset  | 1    | 1        | 1          | 1       | 1     | 1    | 1   | 1   |

#### Bit 14 – Reserved For future use

Reserved bits are unused and reserved for future use. For compatibility with future devices, always write reserved bits to their reset value. If no reset value is given, write 0.

### Bit 13 – AC AC APBA Clock Enable

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The APBA clock for the AC is stopped. |

| 1     | The APBA clock for the AC is enabled. |

#### Bit 12 - PORT PORT APBA Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBA clock for the PORT is stopped. |

| 1     | The APBA clock for the PORT is enabled. |

#### Bit 11 – FREQM FREQM APBA Clock Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The APBA clock for the FREQM is stopped. |

| 1     | The APBA clock for the FREQM is enabled. |

```

23.8.5 Status

```

|        | Name:<br>Offset:<br>Reset:<br>Property: | STATUS<br>0x10<br>0x00000100<br>- |    |           |           |             |             |            |

|--------|-----------------------------------------|-----------------------------------|----|-----------|-----------|-------------|-------------|------------|

| Bit    | 31                                      | 30                                | 29 | 28        | 27        | 26          | 25          | 24         |

|        |                                         |                                   |    |           |           |             |             |            |

| Access |                                         |                                   |    |           |           |             |             |            |

| Reset  |                                         |                                   |    |           |           |             |             |            |

| Dit    | 00                                      | 22                                | 24 | 20        | 10        | 40          | 47          | 40         |

| Bit    | 23                                      | 22                                | 21 | 20        | 19        | 18          | 17          | 16         |

|        |                                         |                                   |    |           | DPLLLDRTO | DPLLLTO     | DPLLLCKF    | DPLLLCKR   |

| Access |                                         |                                   |    |           | R         | R           | R           | R          |

| Reset  |                                         |                                   |    |           | 0         | 0           | 0           | 0          |

|        |                                         |                                   |    |           |           |             |             |            |

| Bit    | 15                                      | 14                                | 13 | 12        | 11        | 10          | 9           | 8          |

|        |                                         |                                   |    |           |           | DFLLULPNOLO | DFLLULPLOCK | DFLLULPRDY |

|        |                                         |                                   |    |           |           | СК          |             |            |

| Access |                                         |                                   |    | 1         |           | R           | R           | R          |

| Reset  |                                         |                                   |    |           |           | 0           | 0           | 1          |

|        |                                         |                                   |    |           |           |             |             |            |

| Bit    | 7                                       | 6                                 | 5  | 4         | 3         | 2           | 1           | 0          |

|        |                                         |                                   |    | OSC16MRDY |           | CLKSW       | CLKFAIL     | XOSCRDY    |

| Access |                                         |                                   |    | R         |           | R           | R           | R          |

| Reset  |                                         |                                   |    | 0         |           | 0           | 0           | 0          |

#### Bit 19 – DPLLLDRTO DPLL Loop Divider Ratio Update Complete

|   | Value | Description                                           |

|---|-------|-------------------------------------------------------|

| ſ | 0     | DPLL Loop Divider Ratio Update Complete not detected. |

|   | 1     | DPLL Loop Divider Ratio Update Complete detected.     |

#### Bit 18 – DPLLLTO DPLL Lock Timeout

| Value | Description                      |

|-------|----------------------------------|

| 0     | DPLL Lock time-out not detected. |

| 1     | DPLL Lock time-out detected.     |

#### Bit 17 – DPLLLCKF DPLL Lock Fall

| Value | Description                       |

|-------|-----------------------------------|

| 0     | DPLL Lock fall edge not detected. |

| 1     | DPLL Lock fall edge detected.     |

Bit 16 – DPLLLCKR DPLL Lock Rise

# SAM L10/L11 Family

# **OSCCTRL – Oscillators Controller**

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the DFLLULP behaves during standby sleep mode, together with the ONDEMAND bit.

This bit is not enabled-protected. This bit is not synchronized

#### Bit 5 – DITHER Tuner Dither Mode

This bit is not synchronized.

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | The dither mode is disabled.                                            |

| 1     | The dither mode is enabled if tuning is enabled (DFLLULPCTRL.TUNE = 1). |

#### Bit 4 – SAFE Tuner Safe Mode

This bit is not synchronized.

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | The clock output is not masked while binary search tuning is ongoing.                 |

| 1     | The clock output is masked while binary search tuning is ongoing (DFLLULPCTRL.BINSE = |

|       | 1).                                                                                   |

#### Bit 3 – BINSE Binary Search Enable

This bit is not synchronized.

| Value | Description                                                                                        |

|-------|----------------------------------------------------------------------------------------------------|

| 0     | Binary search tuning is disabled. Maximum number of reference clock cycles to acquire lock is 256. |

| 1     | Binary search tuning is enabled. Maximum number of reference clock cycles to acquire lock is 8.    |

#### Bit 1 – ENABLE Enable

This bit is not enable-protected.

| Value | Description              |

|-------|--------------------------|

| 0     | The DFLLULP is disabled. |

| 1     | The DFLLULP is enabled.  |

#### 23.8.12 DFLLULP Delay Value

| Name:     | DFLLULPDLY                               |

|-----------|------------------------------------------|

| Offset:   | 0x20                                     |

| Reset:    | 0x0000080                                |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 31  | 30  | 29  | 28   | 27     | 26  | 25  | 24  |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     |      |        |     |     |     |

| Access | R   | R   | R   | R    | R      | R   | R   | R   |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19     | 18  | 17  | 16  |

|        |     |     |     |      |        |     |     |     |

| Access | R   | R   | R   | R    | R      | R   | R   | R   |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|        |     |     |     |      |        |     |     |     |

| Access | R   | R   | R   | R    | R      | R   | R   | R   |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |     |     | DELA | Y[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 1   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 7:0 - DELAY[7:0] Delay Value

Writing a value to this field sets the oscillator delay. A small value will produce a fast clock and a large value will produce a slow clock. If the tuner is enabled, writing to this field will cause the tuner to start tuning from the written value. Reading this value will return the last written delay or the oscillator delay when a synchronization was requested from the DFLLULPRREQ register. Writing a value to this register while a write synchronization or a read request synchronization is on-going will have no effect and produce a PAC error.

The STATUS.VCORERDY bit is set to '1' as soon as the VDDCORE voltage has reached the target voltage. During voltage transition, STATUS.VCORERDY will read '0'. The Voltage Ready interrupt (VCORERDY) can be used to detect a 0-to-1 transition of STATUS.VCORERDY, see also 25.6.4 Interrupts.

When entering the Standby Sleep mode and when no sleepwalking task is requested, the VDDCORE Voltage scaling control is not used.

#### 25.6.1.5 Sleep Mode Operation

In Standby mode, the low-power voltage regulator (LPVREG) is used to supply VDDCORE.

When the Run in Standby bit in the VREG register (VREG.RUNSTDBY) is written to '1', VDDCORE is supplied by the main voltage regulator. Depending on the Standby in PL0 bit in the Voltage Regulator register (VREG.STDBYPL0), the VDDCORE level is either set to the PL0 voltage level, or remains in the current performance level.

| Table 25-1 | VDDCORE | Level in | Standby | / Mode |

|------------|---------|----------|---------|--------|

|------------|---------|----------|---------|--------|

| VREG.RUNSTDBY | VREG.STDBYPL0 | VDDCORE Supply in Standby Mode                       |

|---------------|---------------|------------------------------------------------------|

| 0             | -             | LPVREG                                               |

| 1             | 0             | MAINVREG in current performance level <sup>(1)</sup> |

| 1             | 1             | MAINVREG in PL0                                      |

#### Note:

When the device is in PL0 but VREG.STDBYPL0=0, the MAINVREG is operating in normal power mode. To minimize power consumption, operate MAINVREG in PL0 mode by selecting VREG.STDBYPL0=1.

By writing the Low-Power mode Efficiency bit in the VREG register (VREG.LPEFF) to '1', the efficiency of the regulator in LPVREG can be improved when the application uses a limited VDD range (2.5 to 3.63V). It is also possible to use the BOD33 in order to monitor the VDD and change this LPEFF value on the fly according to VDD level.

#### **Related Links**

22.6.3.3 Sleep Mode Controller

#### 25.6.2 Voltage Reference System Operation

The reference voltages are generated by a functional block DETREF inside of the SUPC. DETREF is providing a fixed-voltage source, BANDGAP=1.1V, and a variable voltage, INTREF.

#### 25.6.2.1 Initialization

The voltage reference output and the temperature sensor are disabled after any Reset.

#### 25.6.2.2 Enabling, Disabling, and Resetting

The voltage reference output is enabled/disabled by setting/clearing the Voltage Reference Output Enable bit in the Voltage Reference register (VREF.VREFOE).

The temperature sensor is enabled/disabled by setting/clearing the Temperature Sensor Enable bit in the Voltage Reference register (VREF.TSEN).

**Note:** When VREF.ONDEMAND=0, it is not recommended to enable both voltage reference output and temperature sensor at the same time - only the voltage reference output will be present at both ADC inputs.

# SAM L10/L11 Family

RTC – Real-Time Counter

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

#### 28.8.21 Channel Interrupt Enable Set

Name:CHINTENSETOffset:0x4DReset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Channel Interrupt Enable Clear (CHINTENCLR) register. This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0    |

|--------|---|---|---|---|---|------|-------|------|

|        |   |   |   |   |   | SUSP | TCMPL | TERR |

| Access |   |   |   |   |   | R/W  | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0    | 0     | 0    |

Bit 2 – SUSP Channel Suspend Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Suspend Interrupt Enable bit, which enables the Channel Suspend interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Channel Suspend interrupt is disabled. |

| 1     | The Channel Suspend interrupt is enabled.  |

Bit 1 – TCMPL Channel Transfer Complete Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Complete Interrupt Enable bit, which enables the Channel Transfer Complete interrupt.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The Channel Transfer Complete interrupt is disabled. |

| 1     | The Channel Transfer Complete interrupt is enabled.  |

Bit 0 – TERR Channel Transfer Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Error Interrupt Enable bit, which enables the Channel Transfer Error interrupt.

|   | /alue | Description                                       |

|---|-------|---------------------------------------------------|

| ( | )     | The Channel Transfer Error interrupt is disabled. |

| - | L     | The Channel Transfer Error interrupt is enabled.  |

#### 30.8.11 Non-Secure Region Unlock Bits

| Name:     | NSULCK                                               |

|-----------|------------------------------------------------------|

| Offset:   | 0x22                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Mix-Secure               |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

| Bit    | 15     | 14     | 13     | 12     | 11      | 10        | 9         | 8         |

|--------|--------|--------|--------|--------|---------|-----------|-----------|-----------|

| [      |        |        |        | NSLK   | EY[7:0] |           |           |           |

| Access | W/W*/W | W/W*/W | W/W*/W | W/W*/W | W/W*/W  | W/W*/W    | W/W*/W    | W/W*/W    |

| Reset  | 0      | 0      | 0      | 0      | 0       | 0         | 0         | 0         |

|        |        |        |        |        |         |           |           |           |

| Bit    | 7      | 6      | 5      | 4      | 3       | 2         | 1         | 0         |

| Γ      |        |        |        |        |         | DNS       | ANS       | BNS       |

| Access |        |        |        |        |         | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  |        |        |        |        |         | x         | x         | x         |

#### Bits 15:8 – NSLKEY[7:0] Non-Secure Unlock Key

When this bit group is written to the key value 0xA5, the write will be performed. If a value different from the key value is tried, the write will be discarded and INTFLAG.KEYE set.

#### Bit 2 – DNS Data Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure Data Flash region corresponds to the entire Data Flash region.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Non-Secure Data Flash region is locked.     |

| 1     | The Non-Secure Data Flash region is not locked. |

#### Bit 1 - ANS Application Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure APPLICATION region corresponds to the entire APPLICATION Flash region.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The Non-Secure APPLICATION region is locked.     |

| 1     | The Non-Secure APPLICATION region is not locked. |

#### Bit 0 - BNS BOOT Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure BOOT region corresponds to the entire BOOT Flash region.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Non-Secure BOOT region is locked.     |

| 1     | The Non-Secure BOOT region is not locked. |

#### 32.8.12 Event Input Control

| Name:     | EVCTRL                       |

|-----------|------------------------------|

| Offset:   | 0x2C                         |

| Reset:    | 0x0000000                    |

| Property: | PAC Write-Protection, Secure |

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to four input event pins for each PORT group. Each byte of this register addresses one Event input pin.

| Bit    | 31      | 30          | 29      | 28      | 27      | 26        | 25      | 24      |

|--------|---------|-------------|---------|---------|---------|-----------|---------|---------|

|        | PORTEIx | EVACTx[1:0] |         |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0           | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |             |         |         |         |           |         |         |

| Bit    | 23      | 22          | 21      | 20      | 19      | 18        | 17      | 16      |

|        | PORTEIX | EVAC        | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0           | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |             |         |         |         |           |         |         |

| Bit    | 15      | 14          | 13      | 12      | 11      | 10        | 9       | 8       |

|        | PORTEIX | EVAC        | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0           | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |             |         |         |         |           |         |         |

| Bit    | 7       | 6           | 5       | 4       | 3       | 2         | 1       | 0       |

|        | PORTEIx | EVAC        | Tx[1:0] |         |         | PIDx[4:0] |         |         |

| Access | RW/-/RW | RW/-/RW     | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW   | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0           | 0       | 0       | 0       | 0         | 0       | 0       |

|        |         |             |         |         |         |           |         |         |

Bits 31,23,15,7 – PORTEIx PORT Event Input Enable x [x = 3..0]

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The event action x (EVACTx) will not be triggered on any incoming event. |

| 1     | The event action x (EVACTx) will be triggered on any incoming event.     |

# Bits 30:29, 22:21,14:13,6:5 – EVACTx PORT Event Action x [x = 3..0]

These bits define the event action the PORT will perform on event input x. See also Table 32-4.

Bits 28:24,20:16,12:8,4:0 – PIDx PORT Event Pin Identifier x [x = 3..0]

These bits define the I/O pin on which the event action will be performed, according to Table 32-5.

Refer to the CTRLA register description for details.

#### 36.6.2.3 Clock Generation

In SPI master operation (CTRLA.MODE=0x3), the serial clock (SCK) is generated internally by the SERCOM baud-rate generator.

In SPI mode, the baud-rate generator is set to synchronous mode. The 8-bit Baud register (BAUD) value is used for generating SCK and clocking the shift register. Refer to *Clock Generation – Baud-Rate Generator* for more details.

In SPI slave operation (CTRLA.MODE is 0x2), the clock is provided by an external master on the SCK pin. This clock is used to directly clock the SPI shift register.

#### **Related Links**

34.6.2.3 Clock Generation – Baud-Rate Generator34.6.2.3.1 Asynchronous Arithmetic Mode BAUD Value Selection

#### 36.6.2.4 Data Register

The SPI Transmit Data register (TxDATA) and SPI Receive Data register (RxDATA) share the same I/O address, referred to as the SPI Data register (DATA). Writing DATA register will update the Transmit Data register. Reading the DATA register will return the contents of the Receive Data register.

#### 36.6.2.5 SPI Transfer Modes

There are four combinations of SCK phase and polarity to transfer serial data. The SPI data transfer modes are shown in SPI Transfer Modes (Table) and SPI Transfer Modes (Figure).

SCK phase is configured by the Clock Phase bit in the CTRLA register (CTRLA.CPHA). SCK polarity is programmed by the Clock Polarity bit in the CTRLA register (CTRLA.CPOL). Data bits are shifted out and latched in on opposite edges of the SCK signal. This ensures sufficient time for the data signals to stabilize.

| Mode | CPOL | СРНА | Leading Edge    | Trailing Edge   |

|------|------|------|-----------------|-----------------|

| 0    | 0    | 0    | Rising, sample  | Falling, setup  |

| 1    | 0    | 1    | Rising, setup   | Falling, sample |

| 2    | 1    | 0    | Falling, sample | Rising, setup   |

| 3    | 1    | 1    | Falling, setup  | Rising, sample  |

#### Table 36-3. SPI Transfer Modes

#### Note:

Leading edge is the first clock edge in a clock cycle.

Trailing edge is the second clock edge in a clock cycle.

#### 38.7.3.9 Waveform Generation Control

Name:WAVEOffset:0x0CReset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | WAVEG | GEN[1:0] |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

#### Bits 1:0 – WAVEGEN[1:0] Waveform Generation Mode

These bits select the waveform generation operation. They affect the top value, as shown in 38.6.2.6.1 Waveform Output Operations. They also control whether frequency or PWM waveform generation should be used. The waveform generation operations are explained in 38.6.2.6.1 Waveform Output Operations.

These bits are not synchronized.

| Value | Name | Operation        | Top Value              | Output<br>Waveform<br>on Match | Output Waveform<br>on Wraparound |

|-------|------|------------------|------------------------|--------------------------------|----------------------------------|

| 0x0   | NFRQ | Normal frequency | PER <sup>1</sup> / Max | Toggle                         | No action                        |

| 0x1   | MFRQ | Match frequency  | CC0                    | Toggle                         | No action                        |

| 0x2   | NPWM | Normal PWM       | PER <sup>1</sup> / Max | Set                            | Clear                            |

| 0x3   | MPWM | Match PWM        | CC0                    | Set                            | Clear                            |

1) This depends on the TC mode: In 8-bit mode, the top value is the Period Value register (PER). In 16and 32-bit mode it is the respective MAX value.

#### 39.8.5 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x0A    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|--------|---|---|---|---|---|---|---|---------|

|        |   |   |   |   |   |   |   | DATARDY |

| Access |   |   |   |   |   |   |   | R/W     |

| Reset  |   |   |   |   |   |   |   | 0       |

#### Bit 0 – DATARDY Data Ready

This flag is set when a new random value is generated, and an interrupt will be generated if INTENCLR/ SET.DATARDY=1.

This flag is cleared by writing a '1' to the flag or by reading the DATA register.

Writing a '0' to this bit has no effect.

# 40. CCL – Configurable Custom Logic

### 40.1 Overview

The Configurable Custom Logic (CCL) is a programmable logic peripheral which can be connected to the device pins, to events, or to other internal peripherals. This allows the user to eliminate logic gates for simple glue logic functions on the PCB.

Each LookUp Table (LUT) consists of three inputs, a truth table, an optional synchronizer/filter, and an optional edge detector. Each LUT can generate an output as a user programmable logic expression with three inputs. Inputs can be individually masked.

The output can be combinatorially generated from the inputs, and can be filtered to remove spikes. Optional sequential logic can be used. The inputs of the sequential module are individually controlled by two independent, adjacent LUT (LUT0/LUT1, LUT2/LUT3 etc.) outputs, enabling complex waveform generation.

### 40.2 Features

- Glue logic for general purpose PCB design

- Up to 2 programmable LookUp Tables (LUTs)

- Combinatorial logic functions: AND, NAND, OR, NOR, XOR, XNOR, NOT

- Sequential logic functions: Gated D Flip-Flop, JK Flip-Flop, gated D Latch, RS Latch

- Flexible LUT inputs selection:

- I/Os

- Events

- Internal peripherals

- Subsequent LUT output

- Output can be connected to the I/O pins or the Event System

- Optional synchronizer, filter, or edge detector available on each LUT output

#### 41.5.1 I/O Lines

Using the ADC's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

#### **Related Links**

32. PORT - I/O Pin Controller

#### 41.5.2 Power Management

The ADC will continue to operate in any Sleep mode where the selected source clock is running. The ADC's interrupts, except the OVERRUN interrupt, can be used to wake up the device from sleep modes, except the OVERRUN interrupt. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

22. PM - Power Manager

#### 41.5.3 Clocks

The ADC bus clock (CLK\_APB\_ADCx) can be enabled in the Main Clock, which also defines the default state.

The ADC requires a generic clock (GCLK\_ADC). This clock must be configured and enabled in the Generic Clock Controller (GCLK) before using the ADC.

A generic clock is asynchronous to the bus clock. Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to *Synchronization* for further details.

#### **Related Links**

41.6.8 Synchronization19.6.2.6 Peripheral Clock Masking18. GCLK - Generic Clock Controller

#### 41.5.4 DMA

The DMA request line is connected to the DMA Controller (DMAC). Using the ADC DMA requests requires the DMA Controller to be configured first.

#### Related Links

28. DMAC - Direct Memory Access Controller

#### 41.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the ADC interrupt requires the interrupt controller to be configured first.

#### 41.5.6 Events

The events are connected to the Event System.

#### **Related Links**

33. EVSYS – Event System

#### 41.5.7 Debug Operation

When the CPU is halted in debug mode the ADC will halt normal operation. The ADC can be forced to continue operation during debugging. Refer to DBGCTRL register for details.

#### 41.8.8 Sequence Status

| Name:     | SEQSTATUS |

|-----------|-----------|

| Offset:   | 0x07      |

| Reset:    | 0x00      |

| Property: | -         |

| Bit    | 7       | 6 | 5 | 4 | 3 | 2             | 1 | 0 |

|--------|---------|---|---|---|---|---------------|---|---|

|        | SEQBUSY |   |   |   |   | SEQSTATE[4:0] |   |   |

| Access | R       |   |   | R | R | R             | R | R |

| Reset  | 0       |   |   | 0 | 0 | 0             | 0 | 0 |

#### Bit 7 – SEQBUSY Sequence busy

This bit is set when the sequence start.

This bit is clear when the last conversion in a sequence is done.

#### Bits 4:0 - SEQSTATE[4:0] Sequence State

These bit fields are the pointer of sequence. This value identifies the last conversion done in the sequence.

#### 42.8.3 Event Control

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 15 | 14 | 13     | 12     | 11 | 10 | 9       | 8       |

|--------|----|----|--------|--------|----|----|---------|---------|

|        |    |    | INVEIx | INVEIx |    |    | COMPEIx | COMPEIx |

| Access |    |    | R/W    | R/W    |    |    | R/W     | R/W     |

| Reset  |    |    | 0      | 0      |    |    | 0       | 0       |

|        |    |    |        |        |    |    |         |         |

| Bit    | 7  | 6  | 5      | 4      | 3  | 2  | 1       | 0       |

|        |    |    |        | WINEO0 |    |    | COMPEOx | COMPEOx |

| Access |    |    |        | R/W    |    |    | R/W     | R/W     |

| Reset  |    |    |        | 0      |    |    | 0       | 0       |

#### Bits 13,12 – INVEIx Inverted Event Input Enable x

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Incoming event is not inverted for comparator x. |

| 1     | Incoming event is inverted for comparator x.     |

#### Bits 9,8 – COMPEIx Comparator x Event Input

Note that several actions can be enabled for incoming events. If several events are connected to the peripheral, the enabled action will be taken for any of the incoming events. There is no way to tell which of the incoming events caused the action.

These bits indicate whether a comparison will start or not on any incoming event.

| Value | Description                                      |  |

|-------|--------------------------------------------------|--|

| 0     | Comparison will not start on any incoming event. |  |

| 1     | Comparison will start on any incoming event.     |  |

#### Bit 4 – WINEO0 Window 0 Event Output Enable

These bits indicate whether the window 0 function can generate a peripheral event or not.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Window 0 Event is disabled. |

| 1     | Window 0 Event is enabled.  |

#### Bits 1,0 – COMPEOx Comparator x Event Output Enable

These bits indicate whether the comparator x output can generate a peripheral event or not.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | COMPx event generation is disabled. |

| 1     | COMPx event generation is enabled.  |

# SAM L10/L11 Family

# **OPAMP – Operational Amplifier Controller**

| Value | OPAMPx  | Name      | Description           |

|-------|---------|-----------|-----------------------|

| 0x2   | x=0     | REFERENCE | REFERENCE[DAC/REFBUF] |

|       | x=1     | OA0OUT    | OPAMP0 output         |

|       | x=2     | OA1OUT    | OPAMP1 output         |

| 0x3   | x=0,1,2 | GND       |                       |

| 0x4   | x=0,1   | RG_CONN   |                       |

|       | x=2     | Reserved  |                       |

#### Bit 9 – RES1EN Resistor 1 Enable

| I | Value | Description                   |  |

|---|-------|-------------------------------|--|

|   | 0     | R1 disconnected from RES1MUX. |  |

|   | 1     | R1 connected to RES1MUX.      |  |

#### Bit 8 – RES2OUT Resistor ladder To Output

| Value | Description    |

|-------|----------------|

| 0     | Swith open.    |

| 1     | Switch closed. |

#### Bit 7 – ONDEMAND On Demand Control

The On Demand operation mode allows the OPAMPx to be enabled or disabled, depending on other peripheral requests.

| Value | Description                                                                                                                                                    |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | The OPAMPx is always on, if enabled.                                                                                                                           |  |

| 1     | The OPAMPx is enabled when a peripheral is requesting the OPAMPx to be used as an input. The OPAMPx is disabled if no peripheral is requesting it as an input. |  |

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the OPAMPx behaves during standby sleep mode:

| Value | Description                                                                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OPAMPx is disabled in standby sleep mode.                                                                                                                                                                                        |

| 1     | The OPAMPx is not stopped in standby sleep mode. If OPAMPCTRLx.ONDEMAND=1, the OPAMPx will be running when a peripheral is requesting it as an input. If OPAMPCTRLx.ONDEMAND=0, OPAMPx will always be running in standby sleep mode. |

#### Bit 5 – RES2VCC Resistor ladder To VCC

| Value | Description    |

|-------|----------------|

| 0     | Swith open.    |

| 1     | Switch closed. |

#### Bits 4:3 - BIAS[1:0] Bias Selection

These bits are used to select the bias mode.

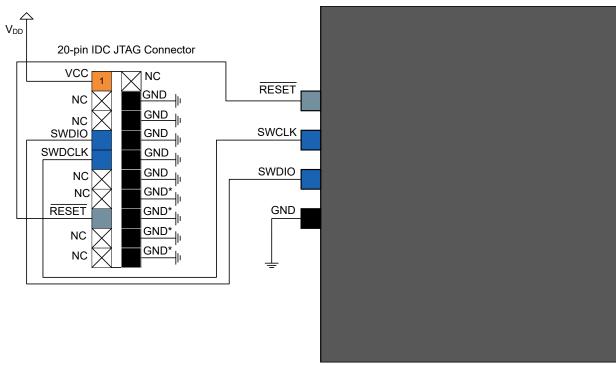

#### Figure 50-13. 20-pin IDC JTAG Connector

#### Table 50-9. 20-pin IDC JTAG Connector

| Header Signal Name | Description                                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWDCLK             | Serial wire clock pin                                                                                                                                                             |

| SWDIO              | Serial wire bidirectional data pin                                                                                                                                                |

| RESET              | Target device reset pin, active low                                                                                                                                               |

| VCC                | Target voltage sense, should be connected to the device $V_{DD}$                                                                                                                  |

| GND                | Ground                                                                                                                                                                            |

| GND*               | These pins are reserved for firmware extension purposes. They can be left unconnected or connected to GND in normal debug environment. They are not essential for SWD in general. |

### 50.8 Peripherals Considerations

#### **ADC Accuracy**

The ADC accuracy may depend on different parameters, such as its input sources, as well as its conversion speed.

Please refer to the *Analog-to-Digital Converter (ADC) Characteristics* section in the *Electrical Characteristics* chapters for more details.