Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d16a-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 23.8.1 Event Control

| Name:     | EVCTRL               |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2       | 1      | 0     |

|--------|---|---|---|---|---|---------|--------|-------|

|        |   |   |   |   |   | TUNEINV | TUNEEI | CFDEO |

| Access |   |   |   |   |   | R/W     | R/W    | R/W   |

| Reset  |   |   |   |   |   | 0       | 0      | 0     |

#### Bit 2 – TUNEINV Tune Event Input Invert

This bit is used to invert the input event of the DFLLULP tuner.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Tune event input source is not inverted. |

| 1     | Tune event input source is inverted.     |

# Bit 1 – TUNEEI Tune Event Input Enable

This bit is used to enable the input event of the DFLLULP tuner.

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | A new closed loop tuning will not be triggered on any incoming event. |

| 1     | A new closed loop tuning will be triggered on any incoming event.     |

# Bit 0 – CFDEO Clock Failure Detector Event Output Enable

This bit indicates whether the Clock Failure detector event output is enabled or not and an output event will be generated when the Clock Failure detector detects a clock failure

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Clock Failure detector event output is disabled and no event will be generated. |

| 1     | Clock Failure detector event output is enabled and an event will be generated.  |

SAM L10/L11 Family

# **OSCCTRL – Oscillators Controller**

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0xE          | 16384                               | 3                              | 500000                              |

| 0xF          | 32768                               | 3                              | 1000000                             |

#### Note:

- 1. Actual startup time is 1 OSCULP32K cycle + 3 XOSC cycles.

- 2. The given time neglects the three XOSC cycles before OSCULP32K cycle.

# Bit 11 – AMPGC Automatic Amplitude Gain Control

**Note:** This bit must be set only after the XOSC has settled, indicated by the XOSC Ready flag in the Status register (STATUS.XOSCRDY).

| Value | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The automatic amplitude gain control is disabled.                                                                                   |

| 1     | The automatic amplitude gain control is enabled. Amplitude gain will be automatically adjusted during Crystal Oscillator operation. |

#### Bits 10:8 – GAIN[2:0] Oscillator Gain

These bits select the gain for the oscillator. The listed maximum frequencies are recommendations, and might vary based on capacitive load and crystal characteristics. Those bits must be properly configured even when the Automatic Amplitude Gain Control is active.

| Value   | Recommended Max Frequency [MHz] |

|---------|---------------------------------|

| 0x0     | 2                               |

| 0x1     | 4                               |

| 0x2     | 8                               |

| 0x3     | 16                              |

| 0x4     | 30                              |

| 0x5-0x7 | Reserved                        |

# Bit 7 – ONDEMAND On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled, depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

# 24.6.6 Real-Time Counter Clock Selection

Before enabling the RTC module, the RTC clock must be selected first. All oscillator outputs are valid as RTC clock. The selection is done in the RTC Control register (RTCCTRL). To ensure a proper operation, it is highly recommended to disable the RTC module first, before the RTC clock source selection is changed.

# **Related Links**

27. RTC - Real-Time Counter

# 24.6.7 Interrupts

The OSC32KCTRL has the following interrupt sources:

- XOSC32KRDY 32KHz Crystal Oscillator Ready: A 0-to-1 transition on the STATUS.XOSC32KRDY bit is detected

- CLKFAIL Clock Failure Detector: A 0-to-1 transition on the STATUS.CLKFAIL bit is detected

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs. Each interrupt can be enabled individually by setting the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the OSC32KCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSC32KCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

# **Related Links**

22. PM - Power Manager

# 24.6.8 Events

The CFD can generate the following output event:

Clock Failure Detector (CLKFAIL): Generated when the Clock Failure Detector status bit is set in the Status register (STATUS.CLKFAIL). The CFD event is not generated when the Clock Switch bit (STATUS.SWBACK) in the Status register is set.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.CFDEO) enables the CFD output event. Writing a '0' to this bit disables the CFD output event. Refer to the Event System chapter for details on configuring the event system.

#### 26.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------|---|---|---|---|---|---|---|-----|

|        |   |   |   |   |   |   |   | EW  |

| Access |   |   |   |   |   |   |   | R/W |

| Reset  |   |   |   |   |   |   |   | 0   |

Bit 0 – EW Early Warning Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Early Warning Interrupt Enable bit, which disables the Early Warning interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Early Warning interrupt is disabled. |

| 1     | The Early Warning interrupt is enabled.  |

# 26.8.8 Clear

| Name:     | CLEAR              |

|-----------|--------------------|

| Offset:   | 0x0C               |

| Reset:    | 0x00               |

| Property: | Write-Synchronized |

| Bit    | 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|--------|---|---|---|------|--------|---|---|---|

|        |   |   |   | CLEA | R[7:0] |   |   |   |

| Access | W | W | W | W    | W      | W | W | W |

| Reset  | 0 | 0 | 0 | 0    | 0      | 0 | 0 | 0 |

# Bits 7:0 – CLEAR[7:0] Watchdog Clear

In Normal mode, writing 0xA5 to this register during the watchdog time-out period will clear the Watchdog Timer and the watchdog time-out period is restarted.

In Window mode, any writing attempt to this register before the time-out period started (i.e., during  $TO_{WDTW}$ ) will issue an immediate system Reset. Writing 0xA5 during the time-out period  $TO_{WDT}$  will clear the Watchdog Timer and the complete time-out sequence (first  $TO_{WDTW}$  then  $TO_{WDT}$ ) is restarted.

In both modes, writing any other value than 0xA5 will issue an immediate system Reset.

# 27.8.10 Counter Value in COUNT32 mode (CTRLA.MODE=0)

| Name:     | COUNT                                                       |

|-----------|-------------------------------------------------------------|

| Offset:   | 0x18                                                        |

| Reset:    | 0x0000000                                                   |

| Property: | PAC Write-Protection, Write-Synchronized, Read-Synchronized |

| Bit    | 31  | 30           | 29  | 28    | 27       | 26  | 25  | 24  |  |

|--------|-----|--------------|-----|-------|----------|-----|-----|-----|--|

|        |     | COUNT[31:24] |     |       |          |     |     |     |  |

| Access | R/W | R/W          | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0   | 0            | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |     |              |     |       |          |     |     |     |  |

| Bit    | 23  | 22           | 21  | 20    | 19       | 18  | 17  | 16  |  |

|        |     |              |     | COUNT | Г[23:16] |     |     |     |  |

| Access | R/W | R/W          | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0   | 0            | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |     |              |     |       |          |     |     |     |  |

| Bit    | 15  | 14           | 13  | 12    | 11       | 10  | 9   | 8   |  |

|        |     |              |     | COUN  | T[15:8]  |     |     |     |  |

| Access | R/W | R/W          | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0   | 0            | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |     |              |     |       |          |     |     |     |  |

| Bit    | 7   | 6            | 5   | 4     | 3        | 2   | 1   | 0   |  |

|        |     |              |     | COUN  | IT[7:0]  |     |     |     |  |

| Access | R/W | R/W          | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0   | 0            | 0   | 0     | 0        | 0   | 0   | 0   |  |

# Bits 31:0 - COUNT[31:0] Counter Value

These bits define the value of the 32-bit RTC counter in mode 0.

RTC – Real-Time Counter

|        | Offset:<br>Reset: | SYNCBUSY<br>0x10<br>0x00000000<br>- |       |     |       |          |        |       |

|--------|-------------------|-------------------------------------|-------|-----|-------|----------|--------|-------|

| Bit    | 31                | 30                                  | 29    | 28  | 27    | 26       | 25     | 24    |

|        |                   |                                     |       |     |       |          |        |       |

| Access |                   |                                     |       |     |       |          |        |       |

| Reset  |                   |                                     |       |     |       |          |        |       |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    | 23                | 22                                  | 21    | 20  | 19    | 18       | 17     | 16    |

|        |                   |                                     |       |     |       |          |        | [1:0] |

| Access |                   |                                     |       |     |       |          | R      | R     |

| Reset  |                   |                                     |       |     |       |          | 0      | 0     |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    |                   | 14                                  | 13    | 12  | 11    | 10       | 9      | 8     |

|        | COUNTSYNC         |                                     |       |     |       |          |        |       |

| Access | R                 |                                     |       |     |       |          |        |       |

| Reset  | 0                 |                                     |       |     |       |          |        |       |

|        |                   |                                     |       |     |       |          |        |       |

| Bit    | 7                 | 6                                   | 5     | 4   | 3     | 2        | 1      | 0     |

|        |                   | COMP1                               | COMP0 | PER | COUNT | FREQCORR | ENABLE | SWRST |

| Access |                   | R/W                                 | R/W   | R   | R     | R        | R      | R     |

| Reset  |                   | 0                                   | 0     | 0   | 0     | 0        | 0      | 0     |

#### 27.10.8 Synchronization Busy in COUNT16 mode (CTRLA.MODE=1)

Bits 17:16 - GPn[1:0] General Purpose n Synchronization Busy Status

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | Write synchronization for GPn register is complete. |

| 1     | Write synchronization for GPn register is ongoing.  |

Bit 15 – COUNTSYNC Count Read Sync Enable Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Write synchronization for CTRLA.COUNTSYNC bit is complete. |

| 1     | Write synchronization for CTRLA.COUNTSYNC bit is ongoing.  |

#### Bits 5, 6 – COMPn Compare n Synchronization Busy Status [n = 1..0]

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Write synchronization for COMPn register is complete. |

| 1     | Write synchronization for COMPn register is ongoing.  |

#### **Bit 4 – PER** Period Synchronization Busy Status

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | Write synchronization for PER register is complete. |

| 1     | Write synchronization for PER register is ongoing.  |

# 27.10.11 Counter Period in COUNT16 mode (CTRLA.MODE=1)

| Name:     | PER                                      |

|-----------|------------------------------------------|

| Offset:   | 0x1C                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | PER[ | [15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |     |     | PER  | [7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

# Bits 15:0 - PER[15:0] Counter Period

These bits define the value of the 16-bit RTC period in COUNT16 mode (CTRLA.MODE=1).

#### 29.8.11 Debouncer Enable

| Name:     | DEBOUNCEN                                          |

|-----------|----------------------------------------------------|

| Offset:   | 0x30                                               |

| Reset:    | 0x0000000                                          |

| Property: | PAC Write-Protection, Enable-Protected, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the external interrupt x (EXTINTx) is set as Non-Secure in the NONSEC register (NONSEC.EXTINTx bit). Some restrictions apply for the Non-Secure accesses to an Enabled-Protected register as it will not be possible for the Non-Secure to configure it once this register is enabled by the Secure application. This will require some veneers to be implemented on Secure side.

| Bit    | 31             | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|        |                |           |           |           |           |           |           |           |

| Access |                |           |           |           |           |           |           |           |

| Reset  |                |           |           |           |           |           |           |           |

|        |                |           |           |           |           |           |           |           |

| Bit    | 23             | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |                |           |           |           |           |           |           |           |

| Access |                |           |           |           |           |           |           |           |

| Reset  |                |           |           |           |           |           |           |           |

|        |                |           |           |           |           |           |           |           |

| Bit    | 15             | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

|        |                |           |           |           |           |           |           |           |

| Access |                |           |           |           |           |           |           |           |

| Reset  |                |           |           |           |           |           |           |           |

|        |                |           |           |           |           |           |           |           |

| Bit    | 7              | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| ſ      | DEBOUNCEN[7:0] |           |           |           |           |           |           |           |

| Access | RW/RW*/RW      | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0              | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

# Bits 7:0 – DEBOUNCEN[7:0] Debouncer Enable

The bit x of DEBOUNCEN set the Debounce mode for the interrupt associated with the EXTINTx pin.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The EXTINT x edge input is not debounced. |

| 1     | The EXTINT x edge input is debounced.     |

The tamper full erase routine operates at the highest priority. If a remanence routine executing when a tamper full erase occurs, the remanence routine is immediately terminated. If the CPU attempts to write a new scramble key at the same time the tamper key erase routine is active, the CPU data is ignored, but no bus error will occur. If a CPU security routine access is requested during a tamper full erase, the CPU transaction will be ignored and treated as a bus error similar to accessing the module during a software reset.

**Important:** In STANDBY low power mode, it is mandatory to enable the dynamic power gating feature (STDBYCFG.DPGPDSW) to ensure TrustRAM erasing when the power domain PDSW is in a retention state.

# 31.6.3 Interrupts

The TRAM has the following interrupt sources:

- Data Remanence Prevention (DRP): Indicates that the data remanence prevention routine has ended.

- Data Read Error (ERR): Indicates when there is a RAM readout error.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TRAM is reset. See 22.8.6 INTFLAG for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

# 31.6.4 Sleep Mode Operation

The TRAM continues to operate during sleep. When it receives events from the Event System, it will request its own clock in order to perform the requested operation.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering an interrupt. In this case, the CPU will continue executing from the instruction following the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *EVSYS – Event System* for more information.

# 31.6.5 Synchronization

Due to the asynchronicity between event sources and CLK\_TRAM\_APB some registers must be synchronized when accessed. A register can require:

Synchronization when written

When the USART repetition number reaches the programmed value in CTRLC.MAXITER, the STATUS.ITER bit is set and the internal iteration counter is reset. If the repetition of the character is acknowledged by the receiver before the maximum iteration is reached, the repetitions are stopped and the iteration counter is cleared.

# **Disable Successive Receive NACK**

The receiver can limit the number of successive NACKs sent back to the remote transmitter. This is programmed by setting the Disable Successive NACK bit (CTRLC.DSNACK). The maximum number of NACKs transmitted is programmed in the CTRLC.MAXITER field. As soon as the maximum is reached, the character is considered as correct, an acknowledge is sent on the line, the STATUS.ITER bit is set and the internal iteration counter is reset.

# Protocol T=1

When operating in ISO7816 protocol T=1, the transmission is asynchronous (CTRL1.CMODE=0) with one or two stop bits. After the stop bits are sent, the transmitter does not drive the I/O line.

Parity is generated when transmitting and checked when receiving. Parity error detection sets the STATUS.PERR bit, and the erroneous character is written to the receive FIFO. When using T=1 protocol, the receiver does not signal errors on the I/O line and the transmitter does not retransmit.

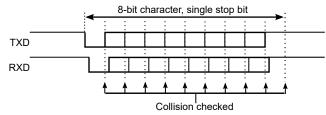

# 35.6.3.7 Collision Detection

When the receiver and transmitter are connected either through pin configuration or externally, transmit collision can be detected after selecting the Collision Detection Enable bit in the CTRLB register (CTRLB.COLDEN=1). To detect collision, the receiver and transmitter must be enabled (CTRLB.RXEN=1 and CTRLB.TXEN=1).

Collision detection is performed for each bit transmitted by comparing the received value with the transmit value, as shown in the figure below. While the transmitter is idle (no transmission in progress), characters can be received on RxD without triggering a collision.

# Figure 35-18. Collision Checking

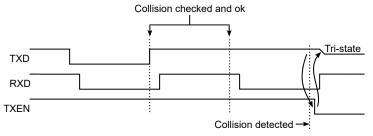

The next figure shows the conditions for a collision detection. In this case, the start bit and the first data bit are received with the same value as transmitted. The second received data bit is found to be different than the transmitted bit at the detection point, which indicates a collision.

# Figure 35-19. Collision Detected

When a collision is detected, the USART follows this sequence:

#### 37.8.3 Interrupt Enable Clear

Name:INTENCLROffset:0x14Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7     | 6 | 5 | 4 | 3 | 2    | 1      | 0    |

|--------|-------|---|---|---|---|------|--------|------|

|        | ERROR |   |   |   |   | DRDY | AMATCH | PREC |

| Access | R/W   |   |   |   |   | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   |   |   | 0    | 0      | 0    |

# Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

# **Bit 2 – DRDY** Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Ready bit, which disables the Data Ready interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Data Ready interrupt is disabled. |

| 1     | The Data Ready interrupt is enabled.  |

# **Bit 1 – AMATCH** Address Match Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Address Match Interrupt Enable bit, which disables the Address Match interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Address Match interrupt is disabled. |

| 1     | The Address Match interrupt is enabled.  |

# Bit 0 – PREC Stop Received Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Stop Received Interrupt Enable bit, which disables the Stop Received interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

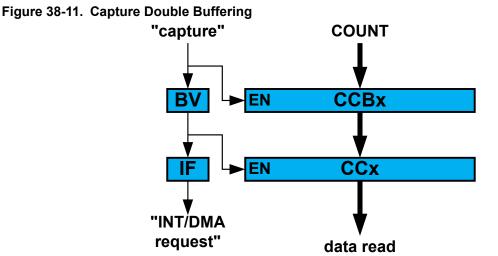

#### 38.6.2.6 Compare Operations

By default, the Compare/Capture channel is configured for compare operations.

When using the TC and the Compare/Capture Value registers (CCx) for compare operations, the counter value is continuously compared to the values in the CCx registers. This can be used for timer or for waveform operation.

The Channel x Compare Buffer (CCBUFx) registers provide double buffer capability. The double buffering synchronizes the update of the CCx register with the buffer value at the UPDATE condition or a forced update command (CTRLBSET.CMD=UPDATE). For further details, refer to 38.6.2.7 Double Buffering. The synchronization prevents the occurrence of odd-length, non-symmetrical pulses and ensures glitch-free output.

#### 38.6.2.6.1 Waveform Output Operations

The compare channels can be used for waveform generation on output port pins. To make the waveform available on the connected pin, the following requirements must be fulfilled:

- 1. Choose a waveform generation mode in the Waveform Generation Operation bit in Waveform register (WAVE.WAVEGEN).

- 2. Optionally invert the waveform output WO[x] by writing the corresponding Output Waveform x Invert Enable bit in the Driver Control register (DRVCTRL.INVENx).

- 3. Configure the pins with the I/O Pin Controller. Refer to PORT I/O Pin Controller for details.

The counter value is continuously compared with each CCx value. On a comparison match, the Match or Capture Channel x bit in the Interrupt Flag Status and Clear register (INTFLAG.MCx) will be set on the next zero-to-one transition of CLK\_TC\_CNT (see Normal Frequency Operation). An interrupt/and or event can be generated on comparison match if enabled. The same condition generates a DMA request.

There are four waveform configurations for the Waveform Generation Operation bit group in the Waveform register (WAVE.WAVEGEN). This will influence how the waveform is generated and impose restrictions on the top value. The configurations are:

- Normal frequency (NFRQ)

- Match frequency (MFRQ)

- Normal pulse-width modulation (NPWM)

- Match pulse-width modulation (MPWM)

When using NPWM or NFRQ configuration, the TOP will be determined by the counter resolution. In 8-bit counter mode, the Period register (PER) is used as TOP, and the TOP can be changed by writing to the PER register. In 16- and 32-bit counter mode, TOP is fixed to the maximum (MAX) value of the counter.

# **Normal Frequency Generation (NFRQ)**

For Normal Frequency Generation, the period time (T) is controlled by the period register (PER) for 8-bit counter mode and MAX for 16- and 32-bit mode. The waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and the corresponding Match or Capture Channel x Interrupt Flag (INTFLAG.MCx) will be set.

• When the channel is counting events from the Event System, write a '1' to the TC Event Input Invert Enable bit in Event Control register (EVCTRL.TCINV).

For input capture, the buffer register and the corresponding CCx act like a FIFO. When CCx is empty or read, any content in CCBUFx is transferred to CCx. The buffer valid flag is passed to set the CCx interrupt flag (IF) and generate the optional interrupt, event or DMA request. The CCBUFx register value can't be read, all captured data must be read from CCx register.

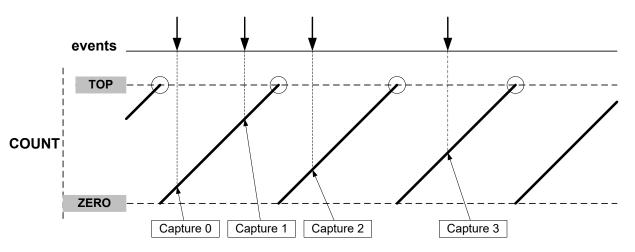

#### 38.6.2.8.1 Event Capture Action

The compare/capture channels can be used as input capture channels to capture events from the Event System and give them a timestamp. The following figure shows four capture events for one capture channel.

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

# 38.6.2.8.2 Period and Pulse-Width (PPW) Capture Action

The TC can perform two input captures and restart the counter on one of the edges. This enables the TC to measure the pulse width and period and to characterize the frequency *f* and duty cycle of an input signal:

This bit has no effect when input capture operation is enabled.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The CCBUFx and PERBUF buffer registers value are copied into CCx and PER registers on  |

|       | hardware update condition.                                                             |

| 1     | The CCBUFx and PERBUF buffer registers value are not copied into CCx and PER registers |

|       | on hardware update condition.                                                          |

#### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

#### 38.7.2.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x0A    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

|        |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

#### **Bit 4 – MCx** Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

#### Bit 1 – ERR Error Interrupt Flag

This flag is set when a new capture occurs on a channel while the corresponding Match or Capture Channel x interrupt flag is set, in which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Error interrupt flag.

#### Bit 0 – OVF Overflow Interrupt Flag

This flag is set on the next CLK\_TC\_CNT cycle after an overflow condition occurs, and will generate an interrupt request if INTENCLR.OVF or INTENSET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

The TRNG interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

22. PM – Power Manager39.6.5 Sleep Mode Operation

# 39.5.3 Clocks

The TRNG bus clock (CLK\_TRNG\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_TRNG\_APB can be found in *Peripheral Clock Masking*.

#### **Related Links**

19.6.2.6 Peripheral Clock Masking

# 39.5.4 DMA

Not applicable.

#### 39.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the TRNG interrupt(s) requires the interrupt controller to be configured first. Refer to NVIC - Nested Interrupt *Nested Vector Interrupt Controller* for details.

#### 39.5.6 Events

TRNG can generate Events that are used by the Event System (EVSYS) and EVSYS users.

TRNG cannot use any Events from other peripherals, as it is not an Event User.

#### **Related Links**

33. EVSYS - Event System

#### 39.5.7 Debug Operation

When the CPU is halted in debug mode the TRNG continues normal operation. If the TRNG is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

# 39.5.8 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following register:

Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

# 39.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 40.5.10 Analog Connections

Not applicable.

# 40.6 Functional Description

#### 40.6.1 Principle of Operation

Configurable Custom Logic (CCL) is a programmable logic block that can use the device port pins, internal peripherals, and the internal Event System as both input and output channels. The CCL can serve as glue logic between the device and external devices. The CCL can eliminate the need for external logic component and can also help the designer overcome challenging real-time constrains by combining core independent peripherals in clever ways to handle the most time critical parts of the application independent of the CPU.

#### 40.6.2 Operation

#### 40.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the corresponding even LUT is disabled (LUTCTRLx.ENABLE=0):

• Sequential Selection bits in the Sequential Control x (SEQCTRLx.SEQSEL) register

The following registers are enable-protected, meaning that they can only be written when the corresponding LUT is disabled (LUTCTRLx.ENABLE=0):

• LUT Control x (LUTCTRLx) register, except the ENABLE bit

Enable-protected bits in the LUTCTRLx registers can be written at the same time as LUTCTRLx.ENABLE is written to '1', but not at the same time as LUTCTRLx.ENABLE is written to '0'.

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 40.6.2.2 Enabling, Disabling, and Resetting

The CCL is enabled by writing a '1' to the Enable bit in the Control register (CTRL.ENABLE). The CCL is disabled by writing a '0' to CTRL.ENABLE.

Each LUT is enabled by writing a '1' to the Enable bit in the LUT Control x register (LUTCTRLx.ENABLE). Each LUT is disabled by writing a '0' to LUTCTRLx.ENABLE.

The CCL is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST). All registers in the CCL will be reset to their initial state, and the CCL will be disabled. Refer to 40.8.1 CTRL for details.

#### 40.6.2.3 Lookup Table Logic

The lookup table in each LUT unit can generate any logic expression OUT as a function of three inputs (IN[2:0]), as shown in Figure 40-2. One or more inputs can be masked. The truth table for the expression is defined by TRUTH bits in LUT Control x register (LUTCTRLx.TRUTH).

The DAC Controller is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the DAC will be reset to their initial state, and the DAC Controller will be disabled. Refer to the CTRLA register for details.

#### 43.6.2.3 Enabling the Output Buffer

To enable the DAC output on the  $V_{OUT}$  pin, the output driver must be enabled by writing a one to the External Output Enable bit in the Control B register (CTRLB.EOEN).

The DAC output buffer provides a high-drive-strength output, and is capable of driving both resistive and capacitive loads. To minimize power consumption, the output buffer should be enabled only when external output is needed.

#### 43.6.2.4 Digital to Analog Conversion

The DAC converts a digital value (stored in the DATA register) into an analog voltage. The conversion range is between GND and the selected DAC voltage reference. The default voltage reference is the internal reference voltage. Other voltage reference options are the analog supply voltage (VDDANA) and the external voltage reference (VREFA). The voltage reference is selected by writing to the Reference Selection bits in the Control B register (CTRLB.REFSEL).

The output voltage from the DAC can be calculated using the following formula:

$$V_{\rm OUT} = \frac{\rm DATA}{0x3\rm FF} \cdot \rm VREF$$

A new conversion starts as soon as a new value is loaded into DATA. DATA can either be loaded via the APB bus during a CPU write operation, using DMA, or from the DATABUF register when a START event occurs. Refer to 43.6.5 Events for details. As there is no automatic indication that a conversion is done, the sampling period must be greater than or equal to the specified conversion time.

# 43.6.3 DMA Operation

The DAC generates the following DMA request:

Data Buffer Empty (EMPTY): The request is set when data is transferred from DATABUF to the internal data buffer of DAC. The request is cleared when DATABUF register is written, or by writing a one to the EMPTY bit in the Interrupt Flag register (INTFLAG.EMPTY).

For each Start Conversion event, DATABUF is transferred into DATA and the conversion starts. When DATABUF is empty, the DAC generates the DMA request for new data. As DATABUF is initially empty, a DMA request is generated whenever the DAC is enabled.

If the CPU accesses the registers that are the source of a DMA request set/clear condition, the DMA request can be lost or the DMA transfer can be corrupted, if enabled.

# 43.6.4 Interrupts

The DAC Controller has the following interrupt sources:

- Data Buffer Empty (EMPTY): Indicates that the internal data buffer of the DAC is empty.

- Underrun (UNDERRUN): Indicates that the internal data buffer of the DAC is empty and a DAC start of conversion event occurred. Refer to 43.6.5 Events for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

#### 43.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | EMPTY | UNDERRUN |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

**Bit 1 – EMPTY** Data Buffer Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Empty Interrupt Enable bit, which disables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

# Bit 0 – UNDERRUN Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Underrun Interrupt Enable bit, which disables the Data Buffer Underrun interrupt.

| Va | lue | Description                                     |

|----|-----|-------------------------------------------------|

| 0  |     | The Data Buffer Underrun interrupt is disabled. |

| 1  |     | The Data Buffer Underrun interrupt is enabled.  |