#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 24-VQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d16a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

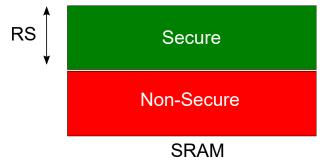

- The Secure SRAM region, with a size defined by the RS fuse from the NVM Boot Configuration Row (BOCOR)

- The Non-Secure (NS) SRAM region

#### Figure 13-4. SAM L11 SRAM Memory Mapping

## 13.2.3 SAM L11 Memory Mapping Configuration Summary

The table below summarizes the mapping of the SAM L11 memory regions.

#### Table 13-2. SAM L11 Memory Regions Mapping

| Memory region                         | Base address                              | Size                                                                |  |  |

|---------------------------------------|-------------------------------------------|---------------------------------------------------------------------|--|--|

| Flash Boot area                       | 0x0000000                                 | BOOTPROT * 256Bytes                                                 |  |  |

| Flash Secure Boot                     | 0x0000000                                 | BS*256Bytes - BNSC*32Bytes                                          |  |  |

| Flash Non-Secure Callable Boot        | Contiguous to Flash Secure Boot           | BNSC * 32Bytes                                                      |  |  |

| Flash Non-Secure Boot (1)             | BS * 256Bytes                             | Flash Boot remaining size (BOOTPROT * 256Bytes -<br>BS*256Bytes)    |  |  |

| Flash Appliation area                 | BOOTPROT * 256Bytes                       | Flash size - BOOTPROT * 256Bytes (Flash Boot area)                  |  |  |

| Flash Secure Application              | BOOTPROT * 256Bytes                       | AS*256Bytes-ANSC*32Bytes                                            |  |  |

| Flash Non-Secure Callable Application | Contiguous to Flash Secure<br>APPLICATION | ANSC * 32Bytes                                                      |  |  |

| Flash Non-Secure Application          | (BOOTPROT+AS) * 256Bytes                  | Flash remaining size (Flash size - BOOTPROT*256Bytes - AS*256Bytes) |  |  |

| Secure Data Flash                     | 0x00400000                                | DS * 256Bytes                                                       |  |  |

| Non-Secure Data Flash                 | Contiguous to Secure Data Flash           | 2KB - Secure Data Flash size                                        |  |  |

| Secure SRAM                           | 0x20000000                                | RS * 128Bytes                                                       |  |  |

| Non-Secure SRAM                       | Contiguous to Secure SRAM                 | SRAM size - Secure SRAM size                                        |  |  |

#### Note:

1. Flash Secure Boot size cannot be null if a Flash Non-Secure Boot size is defined.

Here is a typical configuration for a 64KB of Flash, 2KB of Data Flash and 16KB of SRAM:

- Flash boot area:

- Total Boot area size = 8KB => BOOTPROT = 8192 / 256 = 0x20

- Flash Secure + Non-Secure Callable Boot size = 1KB => BS = 1024 / 256 = 0x4

- Flash Non-Secure Callable Boot size = 32Bytes => BNSC = 32 / 32 = 0x1

- Flash Non-Secure Boot size = 8KB 1KB = 7KB

- Flash Application area:

- Total Application area size = 64 KB 8KB = 56KB

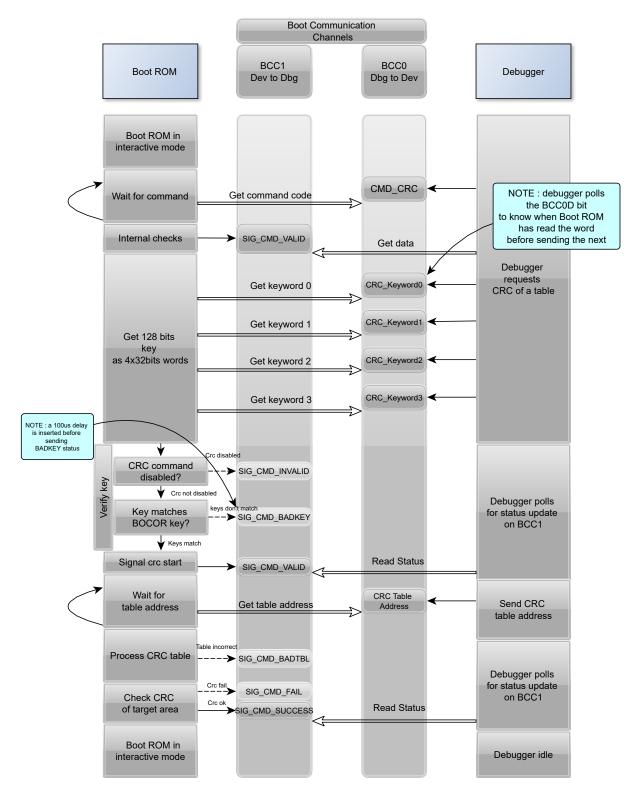

# 14.4.5.6.4 CMD\_CRC

Figure 14-12. CMD\_CRC Flow diagram

# 20.7 Register Summary

| Offset | Name     | Bit Pos. |        |             |  |      |          |  |        |       |

|--------|----------|----------|--------|-------------|--|------|----------|--|--------|-------|

| 0x00   | CTRLA    | 7:0      |        |             |  |      |          |  | ENABLE | SWRST |

| 0x01   | CTRLB    | 7:0      |        |             |  |      |          |  |        | START |

| 000    | 0504     | 7:0      |        | REFNUM[7:0] |  |      |          |  |        |       |

| 0x02   | CFGA     | 15:8     | DIVREF |             |  |      |          |  |        |       |

| 0x04   |          |          |        |             |  |      |          |  |        |       |

|        | Reserved |          |        |             |  |      |          |  |        |       |

| 0x07   |          |          |        |             |  |      |          |  |        |       |

| 0x08   | INTENCLR | 7:0      |        |             |  |      |          |  |        | DONE  |

| 0x09   | INTENSET | 7:0      |        |             |  |      |          |  |        | DONE  |

| 0x0A   | INTFLAG  | 7:0      |        |             |  |      |          |  |        | DONE  |

| 0x0B   | STATUS   | 7:0      |        |             |  |      |          |  | OVF    | BUSY  |

|        |          | 7:0      |        |             |  |      |          |  | ENABLE | SWRST |

| 0x0C   |          | 15:8     |        |             |  |      |          |  |        |       |

| UXUC   | SYNCBUSY | 23:16    |        |             |  |      |          |  |        |       |

|        |          | 31:24    |        |             |  |      |          |  |        |       |

|        |          | 7:0      |        |             |  | VALU | JE[7:0]  |  |        |       |

| 0x10   | VALUE    | 15:8     |        |             |  | VALU | E[15:8]  |  |        |       |

|        | VALUE    | 23:16    |        |             |  | VALU | E[23:16] |  |        |       |

|        |          | 31:24    |        |             |  |      |          |  |        |       |

# 20.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 20.8.3 Configuration A

| Name:     | CFGA                                   |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-protected |

| Bit    | 15     | 14          | 13  | 12  | 11  | 10  | 9   | 8   |

|--------|--------|-------------|-----|-----|-----|-----|-----|-----|

| ĺ      | DIVREF |             |     |     |     |     |     |     |

| Access | R/W    |             |     |     |     |     |     |     |

| Reset  | 0      |             |     |     |     |     |     |     |

| Bit    | 7      | 6           | 5   | 4   | 3   | 2   | 1   | 0   |

|        |        | REFNUM[7:0] |     |     |     |     |     |     |

| Access | R/W    | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0      | 0           | 0   | 0   | 0   | 0   | 0   | 0   |

# Bit 15 – DIVREF Divide Reference Clock

Divides the reference clock by 8

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The reference clock is divided by 1. |

| 1     | The reference clock is divided by 8. |

## Bits 7:0 - REFNUM[7:0] Number of Reference Clock Cycles

Selects the duration of a measurement in number of CLK\_FREQM\_REF cycles. This must be a non-zero value, i.e. 0x01 (one cycle) to 0xFF (255 cycles).

**Bit 8 – VREGRDY** Voltage Regulator Ready Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Voltage Regulator Ready Interrupt Enable bit, which enables the Voltage Regulator Ready interrupt.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | The Voltage Regulator Ready interrupt is disabled.                                          |

| 1     | The Voltage Regulator Ready interrupt is enabled and an interrupt request will be generated |

|       | when the Voltage Regulator Ready Interrupt Flag is set.                                     |

**Bit 2 – B33SRDY** BOD33 Synchronization Ready Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the BOD33 Synchronization Ready Interrupt Enable bit, which enables the BOD33 Synchronization Ready interrupt.

| Value | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Synchronization Ready interrupt is disabled.                                                                                                       |

| 1     | The BOD33 Synchronization Ready interrupt is enabled, and an interrupt request will be generated when the BOD33 Synchronization Ready Interrupt flag is set. |

## Bit 1 – BOD33DET BOD33 Detection Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the BOD33 Detection Interrupt Enable bit, which enables the BOD33 Detection interrupt.

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Detection interrupt is disabled.                                                                                           |

| 1     | The BOD33 Detection interrupt is enabled, and an interrupt request will be generated when the BOD33 Detection Interrupt flag is set. |

#### Bit 0 – BOD33RDY BOD33 Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the BOD33 Ready Interrupt Enable bit, which enables the BOD33 Ready interrupt.

| Value | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Ready interrupt is disabled.                                                                                       |

| 1     | The BOD33 Ready interrupt is enabled, and an interrupt request will be generated when the BOD33 Ready Interrupt flag is set. |

#### 26.8.1 Control A

| Name:     | CTRLA                                                |

|-----------|------------------------------------------------------|

| Offset:   | 0x00                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Synchronized             |

| Bit    | 7        | 6        | 5 | 4 | 3 | 2   | 1      | 0 |

|--------|----------|----------|---|---|---|-----|--------|---|

|        | ALWAYSON | RUNSTDBY |   |   |   | WEN | ENABLE |   |

| Access | R/W      | R/W      |   |   |   | R/W | R/W    |   |

| Reset  | x        | x        |   |   |   | x   | x      |   |

#### Bit 7 – ALWAYSON Always-On

This bit allows the WDT to run continuously. After being set, this bit cannot be written to '0', and the WDT will remain enabled until a power-on Reset is received. When this bit is '1', the Control A register (CTRLA), the Configuration register (CONFIG) and the Early Warning Control register (EWCTRL) will be read-only, and any writes to these registers are not allowed.

Writing a '0' to this bit has no effect.

This bit is not Enable-Protected.

This bit is loaded from NVM User Row at start-up.

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The WDT is enabled and disabled through the ENABLE bit.                |

| 1     | The WDT is enabled and can only be disabled by a power-on reset (POR). |

#### Bit 6 - RUNSTDBY Run in Standby

This bit controls the behavior of the watchdog during standby sleep mode. This bit can only be written when CTRLA.ENABLE is zero or CTRLA.ALWAYSON is one:

- When CTRLA.ALWAYSON=0, this bit is enable-protected by CTRLA.ENABLE.

- When CTRLA.ALWAYSON=1, this bit is not enable-protected by CTRLA.ENABLE.

These bits are loaded from NVM User Row at startup.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The WDT is disabled during standby sleep.                     |

| 1     | The WDT is enabled continues to operate during standby sleep. |

#### **Bit 2 – WEN** Watchdog Timer Window Mode Enable

This bit enables Window mode. It can only be written if the peripheral is disabled unless CTRLA.ALWAYSON=1. The initial value of this bit is loaded from Flash Calibration.

This bit is loaded from NVM User Row at startup.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Window mode is disabled (normal operation). |

| 1     | Window mode is enabled.                     |

# 26.8.8 Clear

| Name:     | CLEAR              |

|-----------|--------------------|

| Offset:   | 0x0C               |

| Reset:    | 0x00               |

| Property: | Write-Synchronized |

| Bit    | 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|--------|---|---|---|------|--------|---|---|---|

|        |   |   |   | CLEA | R[7:0] |   |   |   |

| Access | W | W | W | W    | W      | W | W | W |

| Reset  | 0 | 0 | 0 | 0    | 0      | 0 | 0 | 0 |

#### Bits 7:0 – CLEAR[7:0] Watchdog Clear

In Normal mode, writing 0xA5 to this register during the watchdog time-out period will clear the Watchdog Timer and the watchdog time-out period is restarted.

In Window mode, any writing attempt to this register before the time-out period started (i.e., during  $TO_{WDTW}$ ) will issue an immediate system Reset. Writing 0xA5 during the time-out period  $TO_{WDT}$  will clear the Watchdog Timer and the complete time-out sequence (first  $TO_{WDTW}$  then  $TO_{WDT}$ ) is restarted.

In both modes, writing any other value than 0xA5 will issue an immediate system Reset.

# 27. RTC – Real-Time Counter

# 27.1 Overview

The Real-Time Counter (RTC) is a 32-bit counter with a 10-bit programmable prescaler that typically runs continuously to keep track of time. The RTC can wake up the device from sleep modes using the alarm/ compare wake up, periodic wake up, or overflow wake up mechanisms, or from the wake inputs.

The RTC can generate periodic peripheral events from outputs of the prescaler, as well as alarm/compare interrupts and peripheral events, which can trigger at any counter value. Additionally, the timer can trigger an overflow interrupt and peripheral event, and can be reset on the occurrence of an alarm/compare match. This allows periodic interrupts and peripheral events at very long and accurate intervals.

The 10-bit programmable prescaler can scale down the clock source. By this, a wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the minimum counter tick interval is  $30.5\mu$ s, and time-out periods can range up to 36 hours. For a counter tick interval of 1s, the maximum time-out period is more than 136 years.

# 27.2 Features

- 32-bit counter with 10-bit prescaler

- Multiple clock sources

- 32-bit or 16-bit counter mode

- One 32-bit or two 16-bit compare values

- Clock/Calendar mode

- Time in seconds, minutes, and hours (12/24)

- Date in day of month, month, and year

- Leap year correction

- Digital prescaler correction/tuning for increased accuracy

- Overflow, alarm/compare match and prescaler interrupts and events

- Optional clear on alarm/compare match

- 2 general purpose registers

- Tamper Detection

- Timestamp on event or up to 5 inputs with debouncing

- Active layer protection

#### **Related Links**

33. EVSYS – Event System

#### 27.6.6 Sleep Mode Operation

The RTC will continue to operate in any sleep mode where the source clock is active. The RTC *interrupts* can be used to wake up the device from a sleep mode. RTC *events* can trigger other operations in the system without exiting the sleep mode.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering any interrupt. In this case, the CPU will continue executing right from the first instruction that followed the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *Event System* for more information.

#### 27.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register, CTRLA.SWRST

- Enable bit in Control A register, CTRLA.ENABLE

- Count Read Synchronization bit in Control A register (CTRLA.COUNTSYNC)

- Clock Read Synchronization bit in Control A register (CTRLA.COUNTSYNC)

The following registers are synchronized when written:

- Counter Value register, COUNT

- Clock Value register, CLOCK

- Counter Period register, PER

- Compare n Value registers, COMPn

- Alarm n Value registers, ALARMn

- Frequency Correction register, FREQCORR

- Alarm n Mask register, MASKn

- The General Purpose n registers (GPn)

The following registers are synchronized when read:

- The Counter Value register, COUNT, if the Counter Read Sync Enable bit in CTRLA (CTRLA.COUNTSYNC) is '1'

- The Clock Value register, CLOCK, if the Clock Read Sync Enable bit in CTRLA (CTRLA.CLOCKSYNC) is '1'

- The Timestamp Value register (TIMESTAMP)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

# 27.7 Register Summary - Mode 0 - 32-Bit Counter

| Offset | Name      | Bit Pos. |              |          |           |        |            |          |           |          |

|--------|-----------|----------|--------------|----------|-----------|--------|------------|----------|-----------|----------|

| 0.00   | CTRLA     | 7:0      | MATCHCLR     |          |           |        | MOE        | DE[1:0]  | ENABLE    | SWRST    |

| 0x00   |           | 15:8     | COUNTSYNC    | GPTRST   |           |        |            | PRESCA   | LER[3:0]  | !        |

| 0.00   |           | 7:0      | DMAEN        | RTCOUT   | DEBASYNC  | DEBMAJ |            |          |           | GP0EN    |

| 0x02   | CTRLB     | 15:8     | SEPTO        |          | ACTF[2:0] |        |            |          | DEBF[2:0] |          |

|        |           | 7:0      | PEREO7       | PEREO6   | PEREO5    | PEREO4 | PEREO3     | PEREO2   | PEREO1    | PEREO0   |

| 0.04   | EV (OT DI | 15:8     | OVFEO        | TAMPEREO |           |        |            |          |           | CMPEO0   |

| 0x04   | EVCTRL    | 23:16    |              |          |           |        |            |          |           | TAMPEVEI |

|        |           | 31:24    |              |          |           |        |            |          |           | PERDEO   |

|        |           | 7:0      | PER7         | PER6     | PER5      | PER4   | PER3       | PER2     | PER1      | PER0     |

| 0x08   | INTENCLR  | 15:8     | OVF          | TAMPER   |           |        |            |          |           | CMP0     |

|        |           | 7:0      | PER7         | PER6     | PER5      | PER4   | PER3       | PER2     | PER1      | PER0     |

| 0x0A   | INTENSET  | 15:8     | OVF          | TAMPER   |           |        |            |          |           | CMP0     |

|        |           | 7:0      | PER7         | PER6     | PER5      | PER4   | PER3       | PER2     | PER1      | PER0     |

| 0x0C   | INTFLAG   | 15:8     | OVF          | TAMPER   |           |        |            |          |           | CMP0     |

| 0x0E   | DBGCTRL   | 7:0      |              |          |           |        |            |          |           | DBGRUN   |

| 0x0F   | Reserved  |          |              |          |           |        |            |          |           |          |

|        | SYNCBUSY  | 7:0      |              |          | COMP0     |        | COUNT      | FREQCORR | ENABLE    | SWRST    |

|        |           | 15:8     | COUNTSYNC    |          |           |        |            |          |           |          |

| 0x10   |           | 23:16    |              |          |           |        |            |          | GPr       | n[1:0]   |

|        |           | 31:24    |              |          |           |        |            |          |           |          |

| 0x14   | FREQCORR  | 7:0      | SIGN         |          |           |        | VALUE[6:0] |          |           |          |

| 0x15   |           |          |              |          |           |        |            |          |           |          |

|        | Reserved  |          |              |          |           |        |            |          |           |          |

| 0x17   |           |          |              |          |           |        |            |          |           |          |

|        |           | 7:0      |              |          |           | COUN   | NT[7:0]    |          |           |          |

|        |           | 15:8     |              |          |           | COUN   | T[15:8]    |          |           |          |

| 0x18   | COUNT     | 23:16    | COUNT[23:16] |          |           |        |            |          |           |          |

|        |           | 31:24    |              |          |           | COUNT  | Г[31:24]   |          |           |          |

| 0x1C   |           |          |              |          |           |        |            |          |           |          |

|        | Reserved  |          |              |          |           |        |            |          |           |          |

| 0x1F   |           |          |              |          |           |        |            |          |           |          |

|        |           | 7:0      |              |          |           | COM    | P[7:0]     |          |           |          |

| 0.00   | 00115     | 15:8     |              |          |           | COMF   | P[15:8]    |          |           |          |

| 0x20   | COMP      | 23:16    |              |          |           | COMP   | [23:16]    |          |           |          |

|        |           | 31:24    |              |          |           | COMP   | [31:24]    |          |           |          |

| 0x24   |           |          |              |          |           |        |            |          |           |          |

|        | Reserved  |          |              |          |           |        |            |          |           |          |

| 0x3F   |           |          |              |          |           |        |            |          |           |          |

|        |           | 7:0      |              |          |           | GP     | [7:0]      |          |           |          |

| 0x40   | GP0       | 15:8     |              |          |           | GP[    | 15:8]      |          |           |          |

| 0,40   | GEU       | 23:16    |              |          |           | GP[2   | 3:16]      |          |           |          |

|        |           | 31:24    |              |          |           | GP[3   | 31:24]     |          |           |          |

| 0x44   | GP1       | 7:0      |              |          |           | GP     | [7:0]      |          |           |          |

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 2 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 2 priority. |

#### Bits 19:16 – LVLPRI2[3:0] Level 2 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN2=1) for priority level 2, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 2.

When static arbitration is enabled (PRICTRL0.RRLVLEN2=0) for priority level 2, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN2 written to '0').

#### Bit 15 – RRLVLEN1 Level 1 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to 28.6.2.4 Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 1 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 1 priority. |

## Bits 11:8 – LVLPRI1[3:0] Level 1 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN1=1) for priority level 1, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 1.

When static arbitration is enabled (PRICTRL0.RRLVLEN1=0) for priority level 1, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN1 written to '0').

#### Bit 7 – RRLVLEN0 Level 0 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to 28.6.2.4 Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 0 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 0 priority. |

#### Bits 3:0 – LVLPRI0[3:0] Level 0 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN0=1) for priority level 0, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 0.

When static arbitration is enabled (PRICTRL0.RRLVLEN0=0) for priority level 0, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN0 written to '0').

# SAM L10/L11 Family

TRAM - TrustRAM

| Offset | Name      | Bit Pos. |             |

|--------|-----------|----------|-------------|

|        |           | 7:0      | DATA[7:0]   |

| 0x01A0 | RAM40     | 15:8     | DATA[15:8]  |

| UXUTAU | RAIVI40   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01A4 | RAM41     | 15:8     | DATA[15:8]  |

| 00174  | NAIVI4 I  | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01A8 | RAM42     | 15:8     | DATA[15:8]  |

| UXUTAO | RAIVI42   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01AC | RAM43     | 15:8     | DATA[15:8]  |

| UXUTAC | RAIVI43   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01B0 | DAM44     | 15:8     | DATA[15:8]  |

| UXUTBU | RAM44     | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        | RAM45     | 7:0      | DATA[7:0]   |

| 0x01B4 |           | 15:8     | DATA[15:8]  |

| 0,0104 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01B8 | RAM46     | 15:8     | DATA[15:8]  |

| 0.0100 | KAIVI40   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        | RAM47     | 7:0      | DATA[7:0]   |

| 0x01BC |           | 15:8     | DATA[15:8]  |

| 0,0100 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C0 | RAM48     | 15:8     | DATA[15:8]  |

| 0.0100 |           | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C4 | RAM49     | 15:8     | DATA[15:8]  |

| 0,0104 | 10 101-15 | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

|        |           | 7:0      | DATA[7:0]   |

| 0x01C8 | RAM50     | 15:8     | DATA[15:8]  |

| 0.0100 | 10 1000   | 23:16    | DATA[23:16] |

|        |           | 31:24    | DATA[31:24] |

| 0x01CC | RAM51     | 7:0      | DATA[7:0]   |

| 0.0100 | RAM51     | 15:8     | DATA[15:8]  |

#### 33.7.17 Channel Security Attribution

| Name:     | NONSECCHAN                         |

|-----------|------------------------------------|

| Offset:   | 0x1D8                              |

| Reset:    | 0x0000000                          |

| Property: | PAC Write-Protection, Write-Secure |

This register allows the user to configure one or more channels as secured or non-secured.

|                 | <b>&gt;</b>   | Important: This register is only available for SAM L11 and has no effect for SAM L10. |         |         |         |         |         | AM L10. |  |  |

|-----------------|---------------|---------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--|--|

| Bit             | 31            | 30                                                                                    | 29      | 28      | 27      | 26      | 25      | 24      |  |  |

| [               |               |                                                                                       |         |         |         |         |         |         |  |  |

| Access<br>Reset |               |                                                                                       |         | 1       |         | 1       |         |         |  |  |

| Bit             | 23            | 22                                                                                    | 21      | 20      | 19      | 18      | 17      | 16      |  |  |

| [               |               |                                                                                       |         |         |         |         |         |         |  |  |

| Access<br>Reset |               |                                                                                       |         |         |         |         |         |         |  |  |

| Bit             | 15            | 14                                                                                    | 13      | 12      | 11      | 10      | 9       | 8       |  |  |

|                 |               |                                                                                       |         |         |         |         |         |         |  |  |

| Access          |               |                                                                                       |         |         |         |         |         |         |  |  |

| Reset           |               |                                                                                       |         |         |         |         |         |         |  |  |

| Bit             | 7             | 6                                                                                     | 5       | 4       | 3       | 2       | 1       | 0       |  |  |

|                 | CHANNELn[7:0] |                                                                                       |         |         |         |         |         |         |  |  |

| Access          | RW/R/RW       | RW/R/RW                                                                               | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW |  |  |

| Reset           | 0             | 0                                                                                     | 0       | 0       | 0       | 0       | 0       | 0       |  |  |

**Bits 7:0 – CHANNELn[7:0]** Channel n Security Attribution [n=7..0]The bit n of CHANNEL enables the non-secure mode of CHANNELn. The registers whose CHANNEL bit or bitfield n is set in non-secure mode by NONSECCHAN.CHANNELn are CHANNELn, CHINTENCLRn, CHINTENSETn, CHINTFLAGn and CHSTATUSx registers.

These bits set the security attribution for the individual channels.

| Value | Description                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The corresponding channel is secured. When the module is PAC secured, the configuration and status bits for this channel are only available through the secure alias. Attempts to change the channel configuration through the non-secure alias will be silently ignored and reads will return 0. |

| 1     | The corresponding channel is non-secured. The configuration and status bits for this channel are available through the non-secure alias.                                                                                                                                                          |

#### 33.7.18 Channel Security Attribution Check

| Name:     | NSCHKCHAN            |

|-----------|----------------------|

| Offset:   | 0x1DC                |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to select one or more channels to check their security attribution as non-secured.

|        | >        | Important: | This register is only available for <b>SAM L11</b> and has no effect for <b>SAM L10</b> . |          |          |          |          |          |

|--------|----------|------------|-------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

|        |          |            |                                                                                           |          |          |          |          |          |

| Bit    | 31       | 30         | 29                                                                                        | 28       | 27       | 26       | 25       | 24       |

|        |          |            |                                                                                           |          |          |          |          |          |

| Access |          |            | 1                                                                                         | 1        |          |          |          |          |

| Reset  |          |            |                                                                                           |          |          |          |          |          |

|        |          |            |                                                                                           |          |          |          |          |          |

| Bit    | 23       | 22         | 21                                                                                        | 20       | 19       | 18       | 17       | 16       |

|        |          |            |                                                                                           |          |          |          |          |          |

| Access |          |            |                                                                                           |          |          |          |          |          |

| Reset  |          |            |                                                                                           |          |          |          |          |          |

| Bit    | 15       | 14         | 13                                                                                        | 12       | 11       | 10       | 9        | 8        |

| DIL    | 15       | 14         | 13                                                                                        | 12       | 11       | 10       | 9        | 0        |

| Access |          |            |                                                                                           |          |          |          |          |          |

| Reset  |          |            |                                                                                           |          |          |          |          |          |

| 10000  |          |            |                                                                                           |          |          |          |          |          |

| Bit    | 7        | 6          | 5                                                                                         | 4        | 3        | 2        | 1        | 0        |

|        |          |            |                                                                                           | CHANN    | ELn[7:0] |          |          |          |

| Access | RW/RW/RW | RW/RW/RW   | RW/RW/RW                                                                                  | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW |

| Reset  | 0        | 0          | 0                                                                                         | 0        | 0        | 0        | 0        | 0        |

|        |          |            |                                                                                           |          |          |          |          |          |

#### Bits 7:0 – CHANNELn[7:0] Channel n Selection [n=7..0]

These bits selects the individual channels for security attribution check. If any channel selected in NSCHKCHAN has the corresponding bit in NONSECCHAN set to the opposite value, then the NSCHK interrupt flag will be set.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | 0-to-1 transition will be detected on corresponding NONSECCHAN bit. |

| 1     | 1-to-0 transition will be detected on corresponding NONSECCHAN bit. |

TC – Timer/Counter

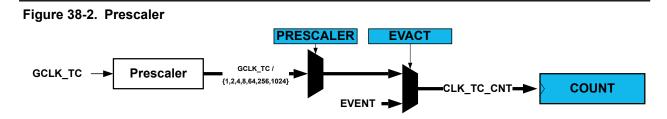

#### 38.6.2.4 Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period Value and Period Buffer Value registers (PER and PERBUF).

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

- COUNT32: This mode is achieved by pairing two 16-bit TC peripherals. TCn is paired with TCn+1. TC2 does not support 32-bit resolution.

When paired, the TC peripherals are configured using the registers of the even-numbered TC. The odd-numbered partner will act as a slave, and the Slave bit in the Status register (STATUS.SLAVE) will be set. The register values of a slave will not reflect the registers of the 32-bit counter. Writing to any of the slave registers will not affect the 32-bit counter. Normal access to the slave COUNT and CCx registers is not allowed.

#### 38.6.2.5 Counter Operations

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TC clock input (CLK\_TC\_CNT). A counter clear or reload marks the end of the current counter cycle and the start of a new one.

The counting direction is set by the Direction bit in the Control B register (CTRLB.DIR). If this bit is zero the counter is counting up, and counting down if CTRLB.DIR=1. The counter will count up or down for each tick (clock or event) until it reaches TOP or ZERO. When it is counting up and TOP is reached, the counter will be set to zero at the next tick (overflow) and the Overflow Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF) will be set. When it is counting down, the counter is reloaded with the TOP value when ZERO is reached (underflow), and INTFLAG.OVF is set.

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e., a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. When starting the TC, the COUNT value will be either ZERO or TOP (depending on the counting direction set by CTRLBSET.DIR or CTRLBCLR.DIR), unless a different value has been written to it, or the TC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed when the counter is running. See also the following figure.

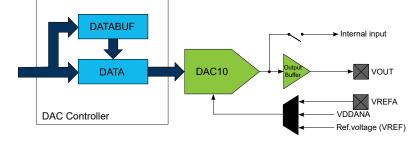

# 43. DAC – Digital-to-Analog Converter

# 43.1 Overview

The Digital-to-Analog Converter (DAC) converts a digital value to a voltage. The DAC has one channel with 10-bit resolution, and it is capable of converting up to 350,000 samples per second (350ksps).

# 43.2 Features

- DAC with 10-bit resolution

- Up to 350ksps conversion rate

- Hardware support for 14-bit using dithering

- Multiple trigger sources

- High-drive capabilities

- Output can be used as input to the Analog Comparator (AC), ADC

- DMA support

# 43.3 Block Diagram

## Figure 43-1. DAC Block Diagram

# 43.4 Signal Description

| Signal Name | Туре          | Description        |

|-------------|---------------|--------------------|

| VOUT        | Analog output | DAC output         |

| VREFA       | Analog input  | External reference |

# 43.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 43.5.1 I/O Lines

Using the DAC Controller's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

#### **Related Links**

- Interrupt Flag Status and Clear (INTFLAG) register

- Data Buffer (DATABUF) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger

#### Related Links

15. PAC - Peripheral Access Controller

#### 43.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 43.5.10 Analog Connections

The DAC has one output pin (VOUT) and one analog input pin (VREFA) that must be configured first.

When internal input is used, it must be enabled before DAC Controller is enabled.

# 43.6 Functional Description

#### 43.6.1 Principle of Operation

The DAC converts the digital value located in the Data register (DATA) into an analog voltage on the DAC output (VOUT).

A conversion is started when new data is written to the Data register. The resulting voltage is available on the DAC output after the conversion time. A conversion can also be started by input events from the Event System.

#### 43.6.2 Basic Operation

#### 43.6.2.1 Initialization

The following registers are enable-protected, meaning they can only be written when the DAC is disabled (CTRLA.ENABLE is zero):

- Control B register (CTRLB)

- Event Control register (EVCTRL)

Enable-protection is denoted by the Enable-Protected property in the register description.

Before enabling the DAC, it must be configured by selecting the voltage reference using the Reference Selection bits in the Control B register (CTRLB.REFSEL).

#### 43.6.2.2 Enabling, Disabling and Resetting

The DAC Controller is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The DAC Controller is disabled by writing a '0' to CTRLA.ENABLE.

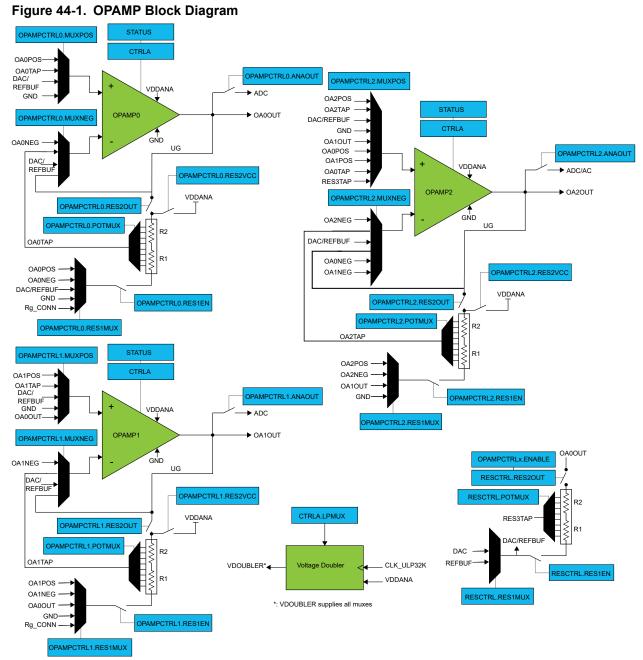

# 44.3 Block Diagram

# 44.4 Signal Description

| Signal | Description           | Туре         |

|--------|-----------------------|--------------|

| OA0POS | OPAMP0 positive input | Analog input |

| OA0NEG | OPAMP0 negative input | Analog input |

| OA1POS | OPAMP1 positive input | Analog input |

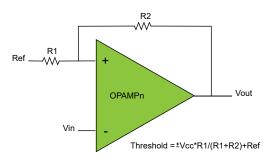

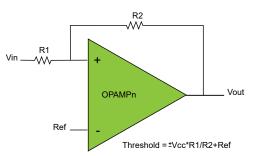

## Figure 44-11. Inverting comparator with programmable hysteresis

To configure an OPAMP as a non-inverting comparator with programmable hysteresis, the OPAMPCTRLx register can be configured as follows:

Table 44-17. Configuration of Input Multiplexes for OPAMP0 and OPAMP1 (Example: Vth = 1/3\*Vcc, Ref = Gnd)

|        | MUXPOS | MUXNEG | RES1MUX | ΡΟΤΜUΧ | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| OPAMP1 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| OPAMP2 | 0001   | 010    | 000     | 100    | 0       | 1       | 1      | 0      |

| Value | R1  | R2  | Threshold = Vcc * R1 / R2 |

|-------|-----|-----|---------------------------|

| 0x0   | 14R | 2R  | Vcc * 7 (unused)          |

| 0x1   | 12R | 4R  | Vcc * 3 (unused)          |

| 0x2   | 8R  | 8R  | Vcc (unused)              |

| 0x3   | 6R  | 10R | 0.6* Vcc                  |

| 0x4   | 4R  | 12R | 1/3 * Vcc                 |

| 0x5   | 3R  | 13R | 3/13 *Vcc                 |

| 0x6   | 2R  | 14R | 1/7 * Vcc                 |

| 0x7   | R   | 15R | 1/15 * Vcc                |

# Figure 44-12. Non-Inverting comparator with programmable hysteresis

# SAM L10/L11 Family

# 125°C Electrical Characteristics

| Symbol                           | Parameter        | Conditions       | Min. | Тур. | Max.       | Units |

|----------------------------------|------------------|------------------|------|------|------------|-------|

|                                  |                  | Slave, VDD>1,62V | 13.4 | -    | -          |       |

| tSOSS MISO setup<br>after SS low |                  | Slave, VDD>2,70V |      | -    | 1*<br>tSCK |       |

|                                  |                  | Slave, VDD>1,62V |      | -    | 1*<br>tSCK |       |

| tSOSH MISO hold                  | Slave, VDD>2,70V | 8.7              | -    | -    |            |       |

|                                  | after SS high    | Slave, VDD>1,62V | 8.7  | -    | -          |       |

#### Note:

- 1. These values are based on simulation. These values are not covered by test limits in production.

- 2. See I/O Pin Characteristics.

- 3. Where tSLAVE\_OUT is the slave external device output response time, generally tEXT\_SOV +tLINE\_DELAY (See Note 7).

- 4. Where tSLAVE\_IN is the slave external device input constraint, generally tEXT\_SIS+tLINE\_DELAY (See Note 7).

- 5. Where tMASTER\_OUT is the master external device output response time, generally tEXT\_MOV +tLINE\_DELAY (See Note 7).

- 6. Where tMASTER\_IN is the master external device input constraint, generally tEXT\_MIS +tLINE\_DELAY (See Note 7).

- 7. tLINE\_DELAY is the transmission line time delay.

- 8. tEXT\_MIS is the input constraint for the master external device.

- 9. tAPBC is the APB period for SERCOM.

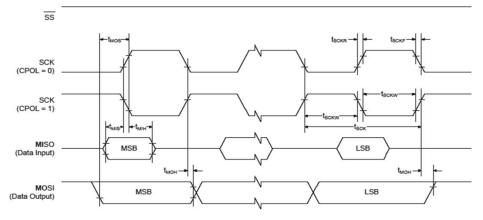

#### Figure 47-4. SPI Timing Requirements in Master Mode