# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 24-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d16a-yu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **DSU - Device Service Unit**

#### 16.12.24 Component Identification 2

|        | Name:<br>Offset:<br>Reset:<br>Property: | CID2<br>0x1FF8<br>0x00000005<br>- |    |        |           |    |    |    |

|--------|-----------------------------------------|-----------------------------------|----|--------|-----------|----|----|----|

| Bit    | 31                                      | 30                                | 29 | 28     | 27        | 26 | 25 | 24 |

|        |                                         |                                   |    |        |           |    |    |    |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

| Bit    | 23                                      | 22                                | 21 | 20     | 19        | 18 | 17 | 16 |

|        |                                         |                                   |    |        |           |    |    |    |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

| Bit    | 15                                      | 14                                | 13 | 12     | 11        | 10 | 9  | 8  |

|        |                                         |                                   |    |        |           |    |    |    |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

| Bit    | 7                                       | 6                                 | 5  | 4      | 3         | 2  | 1  | 0  |

|        |                                         |                                   |    | PREAMB | LEB2[7:0] |    |    |    |

| Access |                                         | R                                 | R  | R      | R         | R  | R  | R  |

| Reset  | 0                                       | 0                                 | 0  | 0      | 0         | 1  | 0  | 1  |

**Bits 7:0 – PREAMBLEB2[7:0]** Preamble Byte 2 These bits will always return 0x00000005 when read. A clock source selected as input to a Generator can either be used directly, or it can be prescaled in the Generator. A generator output is used by one or more Peripheral Channels to provide a peripheral generic clock signal (GCLK\_PERIPH) to the peripherals.

#### 18.6.2 Basic Operation

#### 18.6.2.1 Initialization

Before a Generator is enabled, the corresponding clock source should be enabled. The Peripheral clock must be configured as outlined by the following steps:

- The Generator must be enabled (GENCTRLn.GENEN=1) and the division factor must be set (GENTRLn.DIVSEL and GENCTRLn.DIV) by performing a single 32-bit write to the Generator Control register (GENCTRLn).

- 2. The Generic Clock for a peripheral must be configured by writing to the respective Peripheral Channel Control register (PCHCTRLm). The Generator used as the source for the Peripheral Clock must be written to the GEN bit field in the Peripheral Channel Control register (PCHCTRLm.GEN).

- Note: Each Generator n is configured by one dedicated register GENCTRLn.

**Note:** Each Peripheral Channel m is configured by one dedicated register PCHCTRLm.

#### 18.6.2.2 Enabling, Disabling, and Resetting

The GCLK module has no enable/disable bit to enable or disable the whole module.

The GCLK is reset by setting the Software Reset bit in the Control A register (CTRLA.SWRST) to 1. All registers in the GCLK will be reset to their initial state, except for Peripheral Channels and associated Generators that have their Write Lock bit set to 1 (PCHCTRLm.WRTLOCK). For further details, refer to 18.6.3.4 Configuration Lock.

#### 18.6.2.3 Generic Clock Generator

Each Generator (GCLK\_GEN) can be set to run from one of eight different clock sources except GCLK\_GEN[1], which can be set to run from one of seven sources. GCLK\_GEN[1] is the only Generator that can be selected as source to others Generators.

Each generator GCLK\_GEN[x] can be connected to one specific pin GCLK\_IO[x]. A pin GCLK\_IO[x] can be set either to act as source to GCLK\_GEN[x] or to output the clock signal generated by GCLK\_GEN[x].

The selected source can be divided. Each Generator can be enabled or disabled independently.

Each GCLK\_GEN clock signal can then be used as clock source for Peripheral Channels. Each Generator output is allocated to one or several Peripherals.

GCLK\_GEN[0] is used as GCLK\_MAIN for the synchronous clock controller inside the Main Clock Controller. Refer to the Main Clock Controller description for details on the synchronous clock generation.

#### 20.8.4 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x08                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|---|---|---|---|---|---|---|------|

|        |   |   |   |   |   |   |   | DONE |

| Access |   |   |   |   |   |   |   | R/W  |

| Reset  |   |   |   |   |   |   |   | 0    |

Bit 0 – DONE Measurement Done Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Measurement Done Interrupt Enable bit, which disables the Measurement Done interrupt.

| I | Value | Description                                 |

|---|-------|---------------------------------------------|

|   | 0     | The Measurement Done interrupt is disabled. |

|   | 1     | The Measurement Done interrupt is enabled.  |

| Name:     | STATUS |

|-----------|--------|

| Offset:   | 0x0B   |

| Reset:    | 0x00   |

| Property: | -      |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0    |

|--------|---|---|---|---|---|---|-----|------|

|        |   |   |   |   |   |   | OVF | BUSY |

| Access |   |   |   |   |   |   | R/W | R    |

| Reset  |   |   |   |   |   |   | 0   | 0    |

**Bit 1 – OVF** Sticky Count Value Overflow This bit is cleared by writing a '1' to it.

This bit is set when an overflow condition occurs to the value counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the OVF status.

#### Bit 0 – BUSY FREQM Status

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No ongoing frequency measurement. |

| 1     | Frequency measurement is ongoing. |

## SAM L10/L11 Family

#### **OSCCTRL – Oscillators Controller**

| Offset | Name          | Bit Pos. |          |          |       |         |              |           |            |        |  |

|--------|---------------|----------|----------|----------|-------|---------|--------------|-----------|------------|--------|--|

|        |               | 7:0      |          |          |       |         | DELAY        |           | ENABLE     |        |  |

|        | DFLLULPSYNCBU | 15:8     |          |          |       |         |              |           |            |        |  |

| 0x28   | SY            | 23:16    |          |          |       |         |              |           |            |        |  |

|        |               | 31:24    |          |          |       |         |              |           |            |        |  |

| 0x2C   | DPLLCTRLA     | 7:0      | ONDEMAND | RUNSTDBY |       |         |              |           | ENABLE     |        |  |

| 0x2D   |               |          |          |          |       |         |              |           |            |        |  |

|        | Reserved      |          |          |          |       |         |              |           |            |        |  |

| 0x2F   |               |          |          |          |       |         |              |           |            |        |  |

|        |               | 7:0      |          |          |       | LDF     | R[7:0]       |           |            |        |  |

| 0x30   | DPLLRATIO     | 15:8     |          |          |       |         |              | LDR[11:8] |            |        |  |

| 0,50   | DELLATIO      | 23:16    |          |          |       |         | LDRFRAC[3:0] |           |            |        |  |

|        |               | 31:24    |          |          |       |         |              |           |            |        |  |

|        |               | 7:0      |          |          | REFCL | _K[1:0] | WUF          | LPEN      | FILTE      | R[1:0] |  |

| 0x34   | DPLLCTRLB     | 15:8     |          |          |       | LBYPASS |              |           | LTIME[2:0] |        |  |

| 0x34   | DFLLCTRLB     | 23:16    | DIV[7:0] |          |       |         |              |           |            |        |  |

|        |               | 31:24    |          |          |       |         |              | DIV[10:8] |            |        |  |

| 0x38   | DPLLPRESC     | 7:0      |          |          |       |         |              |           | PRES       | C[1:0] |  |

| 0x39   |               |          |          |          |       |         |              |           |            |        |  |

|        | Reserved      |          |          |          |       |         |              |           |            |        |  |

| 0x3B   |               |          |          |          |       |         |              |           |            |        |  |

| 0x3C   | DPLLSYNCBUSY  | 7:0      |          |          |       |         | DPLLPRESC    | DPLLRATIO | ENABLE     |        |  |

| 0x3D   |               |          |          |          |       |         |              |           |            |        |  |

|        | Reserved      |          |          |          |       |         |              |           |            |        |  |

| 0x3F   |               |          |          |          |       |         |              |           |            |        |  |

| 0x40   | DPLLSTATUS    | 7:0      |          |          |       |         |              |           | CLKRDY     | LOCK   |  |

#### 23.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Write-protection is denoted by the "PAC Write-Protection" property in each individual register description. Refer to the 23.5.8 Register Access Protection section and the PAC - Peripheral Access Controller chapter for details.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" or "Write-Synchronized" property in each individual register description. Refer to the section on Synchronization for details.

#### 25.6.3.4 1.2V Brown-Out Detector (BOD12)

The BOD12 is calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration must not be changed to assure the correct behavior of the BOD12. The BOD12 generates a reset when 1.2V crosses below the preset brown-out level. The BOD12 is always disabled in Standby Sleep mode.

#### 25.6.3.5 Continuous Mode

Continuous mode is the default mode for BOD33.

The BOD33 is continuously monitoring the VDD supply voltage if it is enabled (BOD33.ENABLE=1) and if the BOD33 Configuration bit in the BOD33 register is cleared (BOD33.ACTCFG=0 for active mode, BOD33.STDBYCFG=0 for standby mode).

#### 25.6.3.6 Sampling Mode

The Sampling Mode is a low-power mode where the BOD33 is being repeatedly enabled on a sampling clock's ticks. The BOD33 will monitor the supply voltage for a short period of time and then go to a low-power disabled state until the next sampling clock tick.

Sampling mode is enabled in Active mode for BOD33 by writing the ACTCFG bit (BOD33.ACTCFG=1). Sampling mode is enabled in Standby mode by writing to the STDBYCFG bit (BOD33.STBYCFG=1). The frequency of the clock ticks (F<sub>clksampling</sub>) is controlled by the Prescaler Select bit groups in the BOD33 register (BOD33.PSEL).

$$F_{clksampling} = \frac{F_{clkprescaler}}{2^{(PSEL+1)}}$$

The prescaler signal ( $F_{clkprescaler}$ ) is a 1KHz clock, output by the 32KHz Ultra Low Power Oscillator OSCULP32K.

As the sampling clock is different from the APB clock domain, synchronization among the clocks is necessary. See also 25.6.6 Synchronization.

#### 25.6.3.7 Hysteresis

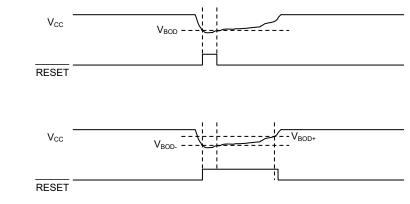

A hysteresis on the trigger threshold of a BOD will reduce the sensitivity to ripples on the monitored voltage: instead of switching  $\overrightarrow{\text{RESET}}$  at each crossing of V<sub>BOD</sub>, the thresholds for switching  $\overrightarrow{\text{RESET}}$  on and off are separated (V<sub>BOD</sub>, and V<sub>BOD</sub>, respectively).

#### Figure 25-2. BOD Hysteresis Principle

Hysteresis OFF:

Hysteresis ON:

Enabling the BOD33 hysteresis by writing the Hysteresis bit in the BOD33 register (BOD33.HYST) to '1' will add hysteresis to the BOD33 threshold level.

## 27. RTC – Real-Time Counter

#### 27.1 Overview

The Real-Time Counter (RTC) is a 32-bit counter with a 10-bit programmable prescaler that typically runs continuously to keep track of time. The RTC can wake up the device from sleep modes using the alarm/ compare wake up, periodic wake up, or overflow wake up mechanisms, or from the wake inputs.

The RTC can generate periodic peripheral events from outputs of the prescaler, as well as alarm/compare interrupts and peripheral events, which can trigger at any counter value. Additionally, the timer can trigger an overflow interrupt and peripheral event, and can be reset on the occurrence of an alarm/compare match. This allows periodic interrupts and peripheral events at very long and accurate intervals.

The 10-bit programmable prescaler can scale down the clock source. By this, a wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the minimum counter tick interval is  $30.5\mu$ s, and time-out periods can range up to 36 hours. For a counter tick interval of 1s, the maximum time-out period is more than 136 years.

#### 27.2 Features

- 32-bit counter with 10-bit prescaler

- Multiple clock sources

- 32-bit or 16-bit counter mode

- One 32-bit or two 16-bit compare values

- Clock/Calendar mode

- Time in seconds, minutes, and hours (12/24)

- Date in day of month, month, and year

- Leap year correction

- Digital prescaler correction/tuning for increased accuracy

- Overflow, alarm/compare match and prescaler interrupts and events

- Optional clear on alarm/compare match

- 2 general purpose registers

- Tamper Detection

- Timestamp on event or up to 5 inputs with debouncing

- Active layer protection

#### 27.8.10 Counter Value in COUNT32 mode (CTRLA.MODE=0)

| Name:     | COUNT                                                       |

|-----------|-------------------------------------------------------------|

| Offset:   | 0x18                                                        |

| Reset:    | 0x0000000                                                   |

| Property: | PAC Write-Protection, Write-Synchronized, Read-Synchronized |

| Bit    | 31                                   | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |  |  |  |  |

|--------|--------------------------------------|-----|-----|-------|----------|-----|-----|-----|--|--|--|--|--|

|        | COUNT[31:24]                         |     |     |       |          |     |     |     |  |  |  |  |  |

| Access | cess R/W R/W R/W R/W R/W R/W R/W R/W |     |     |       |          |     |     |     |  |  |  |  |  |

| Reset  | 0                                    | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |  |

|        |                                      |     |     |       |          |     |     |     |  |  |  |  |  |

| Bit    | 23                                   | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |  |  |  |  |

|        |                                      |     |     | COUNT | Г[23:16] |     |     |     |  |  |  |  |  |

| Access | R/W                                  | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |  |

| Reset  | 0                                    | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |  |

|        |                                      |     |     |       |          |     |     |     |  |  |  |  |  |

| Bit    | 15                                   | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |  |  |  |  |

|        |                                      |     |     | COUN  | T[15:8]  |     |     |     |  |  |  |  |  |

| Access | R/W                                  | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |  |

| Reset  | 0                                    | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |  |

|        |                                      |     |     |       |          |     |     |     |  |  |  |  |  |

| Bit    | 7                                    | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |  |  |  |  |

|        |                                      |     |     | COUN  | IT[7:0]  |     |     |     |  |  |  |  |  |

| Access | R/W                                  | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |  |

| Reset  | 0                                    | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |  |

#### Bits 31:0 - COUNT[31:0] Counter Value

These bits define the value of the 32-bit RTC counter in mode 0.

## 27.11 Register Summary - Mode 2 - Clock/Calendar

| Offset | Name     | Bit Pos. |           |          |           |        |             |          |           |           |  |

|--------|----------|----------|-----------|----------|-----------|--------|-------------|----------|-----------|-----------|--|

| 0.00   |          | 7:0      | MATCHCLR  | CLKREP   |           |        | MOD         | E[1:0]   | ENABLE    | SWRST     |  |

| 0x00   | CTRLA    | 15:8     | CLOCKSYNC | GPTRST   |           |        |             | PRESCA   | LER[3:0]  |           |  |

|        |          | 7:0      | DMAEN     | RTCOUT   | DEBASYNC  | DEBMAJ |             |          |           | GP0EN     |  |

| 0x02   | CTRLB    | 15:8     | SEPTO     |          | ACTF[2:0] |        |             |          | DEBF[2:0] |           |  |

|        |          | 7:0      | PEREO7    | PEREO6   | PEREO5    | PEREO4 | PEREO3      | PEREO2   | PEREO1    | PEREO0    |  |

| 0.04   |          | 15:8     | OVFEO     | TAMPEREO |           |        |             |          |           | ALARMEO   |  |

| 0x04   | EVCTRL   | 23:16    |           |          |           |        |             |          |           | TAMPEVEI  |  |

|        |          | 31:24    |           |          |           |        |             |          |           | PERDEO    |  |

|        |          | 7:0      | PER7      | PER6     | PER5      | PER4   | PER3        | PER2     | PER1      | PER0      |  |

| 0x08   | INTENCLR | 15:8     | OVF       | TAMPER   |           |        |             |          |           | ALARM0    |  |

|        |          | 7:0      | PER7      | PER6     | PER5      | PER4   | PER3        | PER2     | PER1      | PER0      |  |

| 0x0A   | INTENSET | 15:8     | OVF       | TAMPER   |           |        |             |          |           | ALARM0    |  |

|        |          | 7:0      | PER7      | PER6     | PER5      | PER4   | PER3        | PER2     | PER1      | PER0      |  |

| 0x0C   | INTFLAG  | 15:8     | OVF       | TAMPER   |           |        |             |          |           | ALARM0    |  |

| 0x0E   | DBGCTRL  | 7:0      |           |          |           |        |             |          |           | DBGRUN    |  |

| 0x0F   | Reserved |          |           |          |           |        |             |          |           |           |  |

|        |          | 7:0      |           |          | ALARM0    |        | CLOCK       | FREQCORR | ENABLE    | SWRST     |  |

|        |          | 15:8     | CLOCKSYNC |          |           |        | MASK0       |          |           |           |  |

| 0x10   | SYNCBUSY | 23:16    |           |          |           |        |             |          | GPr       | n[1:0]    |  |

|        |          | 31:24    |           |          |           |        |             |          |           |           |  |

| 0x14   | FREQCORR | 7:0      | SIGN      |          |           |        | VALUE[6:0]  |          |           |           |  |

| 0x15   |          |          |           |          |           |        |             |          |           |           |  |

|        | Reserved |          |           |          |           |        |             |          |           |           |  |

| 0x17   |          |          |           |          |           |        |             |          |           |           |  |

|        |          | 7:0      | MINUT     | FE[1:0]  |           |        | SECO        | ND[5:0]  |           |           |  |

|        |          | 15:8     |           | HOU      | R[3:0]    |        | MINUTE[5:2] |          |           |           |  |

| 0x18   | CLOCK    | 23:16    | MONT      | H[1:0]   | DAY[4:0]  |        |             |          | HOUR[4:4] |           |  |

|        |          | 31:24    |           |          | YEAF      | R[5:0] |             |          | MON       | TH[3:2]   |  |

| 0x1C   |          |          |           |          |           |        |             |          |           |           |  |

|        | Reserved |          |           |          |           |        |             |          |           |           |  |

| 0x1F   |          |          |           |          |           |        |             |          |           |           |  |

|        |          | 7:0      | MINUT     | FE[1:0]  |           |        | SECO        | ND[5:0]  |           |           |  |

|        |          | 15:8     |           | HOU      | R[3:0]    |        |             | MINUT    | E[5:2]    |           |  |

| 0x20   | ALARM    | 23:16    | MONT      | H[1:0]   |           |        | DAY[4:0]    |          |           | HOUR[4:4] |  |

|        |          | 31:24    |           |          | YEAF      | R[5:0] |             |          | MON       | TH[3:2]   |  |

| 0x24   | MASK     | 7:0      |           |          |           |        |             |          | SEL[2:0]  |           |  |

| 0x25   |          |          |           |          |           |        |             |          |           |           |  |

|        | Reserved |          |           |          |           |        |             |          |           |           |  |

| 0x3F   |          |          |           |          |           |        |             |          |           |           |  |

|        |          | 7:0      |           |          |           | GP     | [7:0]       |          |           |           |  |

| 0.40   | 053      | 15:8     |           |          |           | GP[    | 15:8]       |          |           |           |  |

| 0x40   | GP0      | 23:16    |           |          |           | GP[2   | 3:16]       |          |           |           |  |

|        |          | 31:24    |           |          |           |        | 31:24]      |          |           |           |  |

This bit will always read as zero.

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | The lower 16 pins of the PORT group will be configured. |

| 1     | The upper 16 pins of the PORT group will be configured. |

#### Bit 30 – WRPINCFG Write PINCFG

This bit determines whether the atomic write operation will update the Pin Configuration register (PINCFGy) or not for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits.

Writing '0' to this bit has no effect.

Writing '1' to this bit updates the configuration of the selected pins with the written WRCONFIG.DRVSTR, WRCONFIG.PULLEN, WRCONFIG.INEN, WRCONFIG.PMUXEN, and WRCONFIG.PINMASK values.

This bit will always read as zero.

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | The PINCFGy registers of the selected pins will not be updated. |

| 1     | The PINCFGy registers of the selected pins will be updated.     |

#### Bit 28 - WRPMUX Write PMUX

This bit determines whether the atomic write operation will update the Peripheral Multiplexing register (PMUXn) or not for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits.

Writing '0' to this bit has no effect.

Writing '1' to this bit updates the pin multiplexer configuration of the selected pins with the written WRCONFIG. PMUX value.

This bit will always read as zero.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The PMUXn registers of the selected pins will not be updated. |

| 1     | The PMUXn registers of the selected pins will be updated.     |

#### Bits 27:24 – PMUX[3:0] Peripheral Multiplexing

These bits determine the new value written to the Peripheral Multiplexing register (PMUXn) for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPMUX bit is set.

These bits will always read as zero.

#### Bit 22 - DRVSTR Output Driver Strength Selection

This bit determines the new value written to PINCFGy.DRVSTR for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 18 – PULLEN Pull Enable

This bit determines the new value written to PINCFGy.PULLEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### 32.8.18 Security Attribution

| Name:     | NONSEC                             |

|-----------|------------------------------------|

| Offset:   | 0x6C                               |

| Reset:    | 0x0000000                          |

| Property: | PAC Write-Protection, Write-Secure |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

This register allows the user to configure one or more I/O pins as secured or non-secured.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31            | 30      | 29      | 28      | 27       | 26      | 25      | 24      |

|--------|---------------|---------|---------|---------|----------|---------|---------|---------|

|        | NONSEC[31:24] |         |         |         |          |         |         |         |

| Access | RW/R/RW       | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW  | RW/R/RW | RW/R/RW | RW/R/RW |

| Reset  | 0             | 0       | 0       | 0       | 0        | 0       | 0       | 0       |

|        |               |         |         |         |          |         |         |         |

| Bit    | 23            | 22      | 21      | 20      | 19       | 18      | 17      | 16      |

|        |               |         |         | NONSE   | C[23:16] |         |         |         |

| Access | RW/R/RW       | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW  | RW/R/RW | RW/R/RW | RW/R/RW |

| Reset  | 0             | 0       | 0       | 0       | 0        | 0       | 0       | 0       |

|        |               |         |         |         |          |         |         |         |

| Bit    | 15            | 14      | 13      | 12      | 11       | 10      | 9       | 8       |

|        |               |         |         | NONSE   | C[15:8]  |         |         |         |

| Access | RW/R/RW       | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW  | RW/R/RW | RW/R/RW | RW/R/RW |

| Reset  | 0             | 0       | 0       | 0       | 0        | 0       | 0       | 0       |

|        |               |         |         |         |          |         |         |         |

| Bit    | 7             | 6       | 5       | 4       | 3        | 2       | 1       | 0       |

|        | NONSEC[7:0]   |         |         |         |          |         |         |         |

| Access | RW/R/RW       | RW/R/RW | RW/R/RW | RW/R/RW | RW/R/RW  | RW/R/RW | RW/R/RW | RW/R/RW |

| Reset  | 0             | 0       | 0       | 0       | 0        | 0       | 0       | 0       |

#### Bits 31:0 - NONSEC[31:0] Port Security Attribution

These bits set the security attribution for the individual I/O pins in the PORT group.

| Value | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| C     | The corresponding I/O pin in the PORT group is configured as secured. When module is            |

|       | PAC secured, the configuration for this pin is only available through the secure alias. Attempt |

The receiver consists of a one-level (I<sup>2</sup>C), two-level or four-level (USART, SPI) receive buffer and a shift register.

The baud-rate generator is capable of running on the GCLK\_SERCOMx\_CORE clock or an external clock.

Address matching logic is included for SPI and I<sup>2</sup>C operation.

#### 34.6.2 Basic Operation

#### 34.6.2.1 Initialization

The SERCOM must be configured to the desired mode by writing the Operating Mode bits in the Control A register (CTRLA.MODE). Refer to table SERCOM Modes for details.

| CTRLA.MODE | Description                       |

|------------|-----------------------------------|

| 0x0        | USART with external clock         |

| 0x1        | USART with internal clock         |

| 0x2        | SPI in slave operation            |

| 0x3        | SPI in master operation           |

| 0x4        | I <sup>2</sup> C slave operation  |

| 0x5        | I <sup>2</sup> C master operation |

| 0x6-0x7    | Reserved                          |

#### Table 34-1. SERCOM Modes

For further initialization information, see the respective SERCOM mode chapters:

#### **Related Links**

- 35. SERCOM USART SERCOM Synchronous and Asynchronous Receiver and Transmitter

- 36. SERCOM SPI SERCOM Serial Peripheral Interface

- 37. SERCOM I2C SERCOM Inter-Integrated Circuit

#### 34.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

Refer to the CTRLA register description for details.

#### 34.6.2.3 Clock Generation – Baud-Rate Generator

The baud-rate generator, as shown in Figure 34-3, generates internal clocks for asynchronous and synchronous communication. The output frequency ( $f_{BAUD}$ ) is determined by the Baud register (BAUD) setting and the baud reference frequency ( $f_{ref}$ ). The baud reference clock is the serial engine clock, and it can be internal or external.

For asynchronous communication, the /16 (divide-by-16) output is used when transmitting, whereas the /1 (divide-by-1) output is used while receiving.

For synchronous communication, the /2 (divide-by-2) output is used.

#### Bit 7 – CLKHOLD Clock Hold

The slave Clock Hold bit (STATUS.CLKHOLD) is set when the slave is holding the SCL line low, stretching the I2C clock. Software should consider this bit a read-only status flag that is set when INTFLAG.DRDY or INTFLAG.AMATCH is set.

This bit is automatically cleared when the corresponding interrupt is also cleared.

#### Bit 6 – LOWTOUT SCL Low Time-out

This bit is set if an SCL low time-out occurs.

This bit is cleared automatically if responding to a new start condition with ACK or NACK (write 3 to CTRLB.CMD) or when INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No SCL low time-out has occurred. |

| 1     | SCL low time-out has occurred.    |

#### Bit 4 – SR Repeated Start

When INTFLAG.AMATCH is raised due to an address match, SR indicates a repeated start or start condition.

This flag is only valid while the INTFLAG.AMATCH flag is one.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Start condition on last address match          |

| 1     | Repeated start condition on last address match |

#### Bit 3 – DIR Read / Write Direction

The Read/Write Direction (STATUS.DIR) bit stores the direction of the last address packet received from a master.

| Value | Description                            |

|-------|----------------------------------------|

| 0     | Master write operation is in progress. |

| 1     | Master read operation is in progress.  |

#### Bit 2 – RXNACK Received Not Acknowledge

This bit indicates whether the last data packet sent was acknowledged or not.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Master responded with ACK.  |

| 1     | Master responded with NACK. |

#### Bit 1 – COLL Transmit Collision

If set, the I2C slave was not able to transmit a high data or NACK bit, the I2C slave will immediately release the SDA and SCL lines and wait for the next packet addressed to it.

This flag is intended for the SMBus address resolution protocol (ARP). A detected collision in non-ARP situations indicates that there has been a protocol violation, and should be treated as a bus error.

#### 38.6.2.6 Compare Operations

By default, the Compare/Capture channel is configured for compare operations.

When using the TC and the Compare/Capture Value registers (CCx) for compare operations, the counter value is continuously compared to the values in the CCx registers. This can be used for timer or for waveform operation.

The Channel x Compare Buffer (CCBUFx) registers provide double buffer capability. The double buffering synchronizes the update of the CCx register with the buffer value at the UPDATE condition or a forced update command (CTRLBSET.CMD=UPDATE). For further details, refer to 38.6.2.7 Double Buffering. The synchronization prevents the occurrence of odd-length, non-symmetrical pulses and ensures glitch-free output.

#### 38.6.2.6.1 Waveform Output Operations

The compare channels can be used for waveform generation on output port pins. To make the waveform available on the connected pin, the following requirements must be fulfilled:

- 1. Choose a waveform generation mode in the Waveform Generation Operation bit in Waveform register (WAVE.WAVEGEN).

- 2. Optionally invert the waveform output WO[x] by writing the corresponding Output Waveform x Invert Enable bit in the Driver Control register (DRVCTRL.INVENx).

- 3. Configure the pins with the I/O Pin Controller. Refer to PORT I/O Pin Controller for details.

The counter value is continuously compared with each CCx value. On a comparison match, the Match or Capture Channel x bit in the Interrupt Flag Status and Clear register (INTFLAG.MCx) will be set on the next zero-to-one transition of CLK\_TC\_CNT (see Normal Frequency Operation). An interrupt/and or event can be generated on comparison match if enabled. The same condition generates a DMA request.

There are four waveform configurations for the Waveform Generation Operation bit group in the Waveform register (WAVE.WAVEGEN). This will influence how the waveform is generated and impose restrictions on the top value. The configurations are:

- Normal frequency (NFRQ)

- Match frequency (MFRQ)

- Normal pulse-width modulation (NPWM)

- Match pulse-width modulation (MPWM)

When using NPWM or NFRQ configuration, the TOP will be determined by the counter resolution. In 8-bit counter mode, the Period register (PER) is used as TOP, and the TOP can be changed by writing to the PER register. In 16- and 32-bit counter mode, TOP is fixed to the maximum (MAX) value of the counter.

#### **Normal Frequency Generation (NFRQ)**

For Normal Frequency Generation, the period time (T) is controlled by the period register (PER) for 8-bit counter mode and MAX for 16- and 32-bit mode. The waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and the corresponding Match or Capture Channel x Interrupt Flag (INTFLAG.MCx) will be set.

#### 38.7.1.15 Channel x Compare/Capture Value, 8-bit Mode

Name:CCxOffset:0x1C + x\*0x01 [x=0..1]Reset:0x00Property:Write-Synchronized, Read-Synchronized

| Bit    | 7       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|---------|-----|-----|-----|-----|-----|-----|-----|

|        | CC[7:0] |     |     |     |     |     |     |     |

| Access | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Bits 7:0 - CC[7:0] Channel x Compare/Capture Value

These bits contain the compare/capture value in 8-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (WAVE.WAVEGEN), the CC0 register is used as a period register.

SAM L10/L11 Family

#### ADC – Analog-to-Digital Converter

| CTRLA.RUNSTDBY | CTRLA.ONDEMAND | CTRLA.ENABLE | Description                        |

|----------------|----------------|--------------|------------------------------------|

| 1              | 0              | 1            | Run in all sleep modes.            |

| 1              | 1              | 1            | Run in all sleep modes on request. |

#### 41.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

The following registers are synchronized when written:

- Input Control register (INPUTCTRL)

- Control C register (CTRLC)

- Average control register (AVGCTRL)

- Sampling time control register (SAMPCTRL)

- Window Monitor Lower Threshold register (WINLT)

- Window Monitor Upper Threshold register (WINUT)

- Gain correction register (GAINCORR)

- Offset Correction register (OFFSETCORR)

- Software Trigger register (SWTRIG)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

## SAM L10/L11 Family

## **Electrical Characteristics**

| Symbol                                 | Parameter                                 | Conditions        |                                               | Min.                                   | Тур.      | Max.       | Units |

|----------------------------------------|-------------------------------------------|-------------------|-----------------------------------------------|----------------------------------------|-----------|------------|-------|

|                                        |                                           | Master, VDD       | ⊳1,62V                                        | 0                                      | -         | -          |       |

| tMOV MOSI output<br>valid after<br>SCK | Master, VDD                               | >2,70V            | -                                             | -                                      | 34.5      | ns         |       |

|                                        | Master, VDD>1,62V                         |                   | -                                             | -                                      | 38.6      |            |       |

| tMOH MOSI hold<br>after SCK            |                                           | Master, VDD>2,70V |                                               | 9.7                                    | -         | -          |       |

|                                        | after SCK                                 | Master, VDD>1,62V |                                               | 9.7                                    | -         | -          |       |

| Period whe                             | Slave SCK<br>Period when<br>tMIS=0 on the | Slave             | Reception                                     | 2*(tSIS<br>+tMASTER_OUT)               | -         | -          |       |

|                                        | master side                               | Slave             | Transmission                                  | 2*(tSOV<br>+tMASTER_IN) <sup>(6)</sup> | -         | -          |       |

| tSSCKW                                 | SCK high/low width                        | Slave             |                                               | -                                      | 0,5*tSCK  | -          |       |

| tSSCKR                                 | SCK rise<br>time <sup>(2)</sup>           | Slave             |                                               | -                                      | 0,25*tSCK | -          |       |

| tSSCKF                                 | SCK fall<br>time <sup>(2)</sup>           | Slave             |                                               | -                                      | 0,25*tSCK | -          |       |

|                                        | MOSI setup to                             | Slave, VDD>       | •2,70V                                        | 25.6                                   | -         | -          | ns    |

|                                        | SCK                                       | Slave, VDD>1,62V  |                                               | 26.2                                   | -         | -          |       |

| tSIH MOSI hold<br>after SCK            |                                           | Slave, VDD>2,70V  |                                               | 13.2                                   | -         | -          |       |

|                                        | Slave, VDD>1,62V                          |                   | 13.9                                          | -                                      | -         |            |       |

| tSSS SS setup to<br>SCK                | Slave                                     | PRELOADEN=1       | tSOSS+tEXT_MIS<br>+2*tAPBC <sup>(8) (9)</sup> | -                                      | -         |            |       |

|                                        |                                           |                   | PRELOADEN=0                                   | tSOSS+tEXT_MIS                         | -         | -          |       |

| tSSH                                   | SS hold after<br>SCK                      | Slave             |                                               | 0.5*tSSCK                              | -         | -          |       |

| tSOV MISO output<br>valid after<br>SCK | MISO output                               | Slave, VDD>2,70V  |                                               | -                                      | -         | 69         |       |

|                                        |                                           | Slave, VDD>1,62V  |                                               | -                                      | -         | 78.4       |       |

| tSOH MISO hold<br>after SCK            | MISO hold                                 | Slave, VDD>2,70V  |                                               | 20.2                                   | -         | -          |       |

|                                        | after SCK                                 | Slave, VDD>1,62V  |                                               | 20.2                                   | -         | -          |       |

|                                        | MISO setup<br>after SS low                | Slave, VDD>       | 2,70V                                         | -                                      | -         | 1*<br>tSCK |       |

|                                        |                                           | Slave, VDD>       | •1,62V                                        | -                                      | -         | 1*<br>tSCK |       |

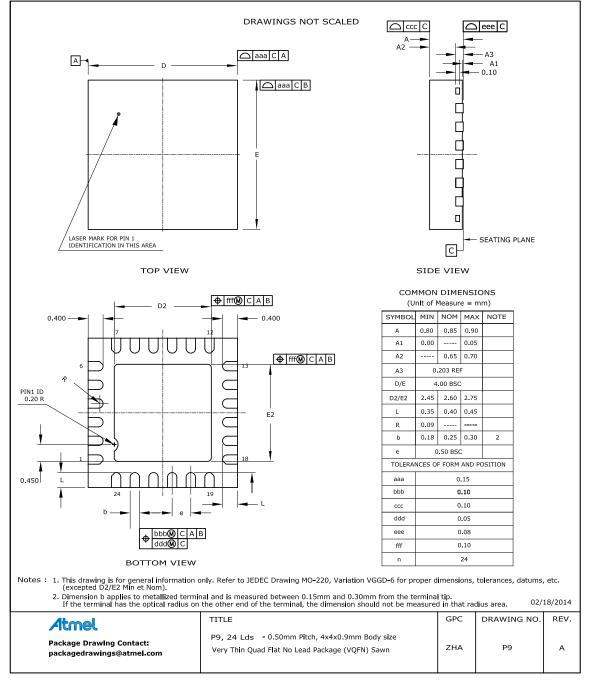

## SAM L10/L11 Family Packaging Information

| Table 49-3. Package Reference |        |  |  |

|-------------------------------|--------|--|--|

| JEDEC Drawing Reference       | MS-026 |  |  |

| JESD97 Classification         | E3     |  |  |

#### 49.2.2 24-pin VQFN

#### Table 49-4. Device and Package Maximum Weight

mg

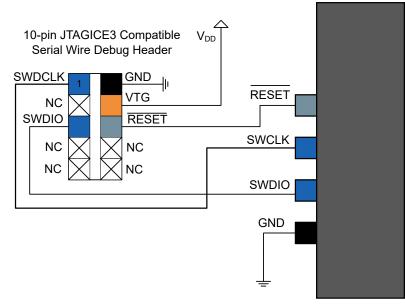

JTAGICE3 and SAM L10/L11. The following figure describes how to connect a 10-pin header that support connecting the JTAGICE3 directly to the SAM L10/L11 without the need for a squid cable. This can also be used for the Atmel-ICE AVR connector port.

The JTAGICE3 squid cable or the JTACICE3 50mil cable can be used to connect the JTAGICE3 programmer and debugger to the SAM L10/L11. The figure illustrates the correct pinout for the JTAGICE3 50 mil, and details are given in the following table.

#### Table 50-8. 10-pin JTAGICE3 Compatible Serial Wire Debug Interface

| Header Signal Name | Description                                                      |  |

|--------------------|------------------------------------------------------------------|--|

| SWDCLK             | Serial wire clock pin                                            |  |

| SWDIO              | Serial wire bidirectional data pin                               |  |

| RESET              | Target device reset pin, active low                              |  |

| VTG                | Target voltage sense, should be connected to the device $V_{DD}$ |  |

| GND                | Ground                                                           |  |

#### 50.7.3 20-pin IDC JTAG Connector

For debuggers and/or programmers that support the 20-pin IDC JTAG Connector, e.g., the SAM-ICE, the signals should be connected, as shown in the following figure, with details described in the following table.

### 53. Datasheet Revision History

**Note:** The datasheet revision is independent of the die revision (Revision bit in the Device Identification register of the Device Service Unit, DSU.DID.REVISION) and the device variant (last letter of the ordering number).

#### 53.1 Rev A - 09/2017

This is the initial released version of the document.

### 53.2 Rev B - 6/2018

Added new documentation for Electrical Characteristics -125°C.