# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 24-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11d16a-yut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The following areas are accessible:

#### Table 14-8. Accessible Memory Range by Read Auxiliary Row Command

| Area                           | Start address | End address |

|--------------------------------|---------------|-------------|

| User row (UROW)                | 0x00804000    | 0x0080401F  |

| Software Calibration row       | 0x00806020    | 0x0080602F  |

| Temperature Log row            | 0x00806038    | 0x0080603F  |

| Boot Configuration row (BOCOR) | 0x0080C000    | 0x0080C0FF  |

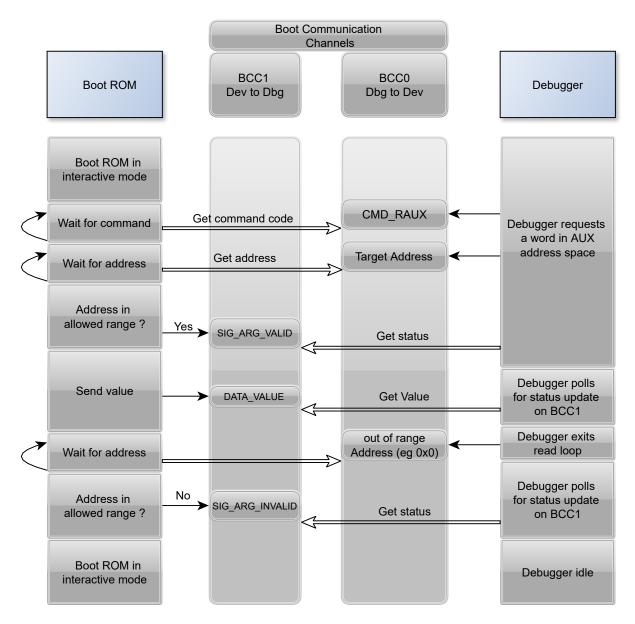

#### 14.4.5.8.1 CMD\_RAUX

#### Figure 14-15. CMD\_RAUX Flow diagram

Note: After the CMD\_RAUX is sent, the debugger can read multiple data, the read loop is exit when an out of range address is sent.

### 16.12.15 CoreSight ROM Table End

| Name:     | END        |

|-----------|------------|

| Offset:   | 0x1008     |

| Reset:    | 0x00000000 |

| Property: | -          |

| R  |

|----|

| 0  |

|    |

| 16 |

|    |

| R  |

| 0  |

|    |

| 8  |

|    |

| R  |

| 0  |

|    |

| 0  |

|    |

| R  |

| 0  |

|    |

Bits 31:0 - END[31:0] End Marker

Indicates the end of the CoreSight ROM table entries.

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID0<br>0x1FE0<br>0x00000000<br>- |    |    |          |    |    |    |

|--------|-----------------------------------------|-----------------------------------|----|----|----------|----|----|----|

| Bit    | 31                                      | 30                                | 29 | 28 | 27       | 26 | 25 | 24 |

|        |                                         |                                   |    |    |          |    |    |    |

| Access |                                         |                                   |    |    |          |    |    |    |

| Reset  |                                         |                                   |    |    |          |    |    |    |

| Bit    | 23                                      | 22                                | 21 | 20 | 19       | 18 | 17 | 16 |

| Access |                                         |                                   |    |    |          |    |    |    |

| Reset  |                                         |                                   |    |    |          |    |    |    |

| Reset  |                                         |                                   |    |    |          |    |    |    |

| Bit    | 15                                      | 14                                | 13 | 12 | 11       | 10 | 9  | 8  |

|        |                                         |                                   |    |    |          |    |    |    |

| Access |                                         |                                   |    |    |          |    |    |    |

| Reset  |                                         |                                   |    |    |          |    |    |    |

|        |                                         |                                   |    |    |          |    |    |    |

| Bit    | 7                                       | 6                                 | 5  | 4  | 3        | 2  | 1  | 0  |

|        |                                         |                                   |    |    | IBL[7:0] |    |    |    |

| Access |                                         | R                                 | R  | R  | R        | R  | R  | R  |

| Reset  | 0                                       | 0                                 | 0  | 0  | 0        | 0  | 0  | 0  |

### 16.12.18 Peripheral Identification 0

#### Bits 7:0 – PARTNBL[7:0] Part Number Low

These bits will always return 0xD0 when read, indicating that this device implements a DSU module instance.

**Note:** After power-up, the MAINVREG low power mode takes some time to stabilize. Once stabilized, the SUPC->STATUS.ULPVREFRDY bit is set. Before entering Standby, software must ensure that the SUPC->STATUS.ULPVREFRDY bit is set.

| Table 22-1. | Sleep Mode | Entry and | Exit Table |

|-------------|------------|-----------|------------|

|-------------|------------|-----------|------------|

| Mode    | Mode Entry                      | Wake-Up Sources                                                    |

|---------|---------------------------------|--------------------------------------------------------------------|

| IDLE    | SLEEPCFG.SLEEPMODE = IDLE<br>_n | Synchronous <sup>(2)</sup> (APB, AHB), asynchronous <sup>(1)</sup> |

| STANDBY | SLEEPCFG.SLEEPMODE =<br>STANDBY | Synchronous <sup>(3)</sup> , Asynchronous                          |

| OFF     | SLEEPCFG.SLEEPMODE = OFF        | External Reset                                                     |

#### Note:

- 1. Asynchronous: interrupt generated on generic clock, external clock, or external event.

- 2. Synchronous: interrupt generated on the APB clock.

- 3. Synchronous interrupt only for peripherals configured to run in standby.

**Note:** The type of wake-up sources (synchronous or asynchronous) is given in each module interrupt section.

The sleep modes (idle, standby, and off) and their effect on the clocks activity, the regulator and the NVM state are described in the table and the sections below. Refer to Power Domain Controller for the power domain gating effect.

| Mode    | Main                | CPU  | AHBx and            | GCLK                | Oscillators                       |                  | Regulator                        | NVM              |

|---------|---------------------|------|---------------------|---------------------|-----------------------------------|------------------|----------------------------------|------------------|

|         | clock               |      | APBx clock          | clocks              | ONDEMAND = 0                      | ONDEMAND = 1     |                                  |                  |

| Active  | Run                 | Run  | Run                 | Run <sup>(3)</sup>  | Run                               | Run if requested | MAINVREG                         | active           |

| IDLE    | Run                 | Stop | Stop <sup>(1)</sup> | Run <sup>(3)</sup>  | Run                               | Run if requested | MAINVREG                         | active           |

| STANDBY | Stop <sup>(1)</sup> | Stop | Stop <sup>(1)</sup> | Stop <sup>(1)</sup> | Run if requested or<br>RUNSTDBY=1 | Run if requested | MAINVREG<br>in low power<br>mode | Ultra Low- power |

| OFF     | Stop                | Stop | Stop                | OFF                 | OFF                               | OFF              | OFF                              | OFF              |

#### Table 22-2. Sleep Mode Overview

#### Note:

- 1. Running if requested by peripheral during SleepWalking.

- 2. Running during SleepWalking.

- 3. Following On-Demand Clock Request principle.

#### 22.6.3.3.1 IDLE Mode

IDLE mode allows power optimization with the fastest wake-up time.

The CPU is stopped, and peripherals are still working. As in Active mode, the AHBx and APBx clocks for peripheral are still provided if requested. As the main clock source is still running, wake-up time is very fast.

• Entering Idle mode: The Idle mode is entered by executing the WFI instruction. Additionally, if the SLEEPONEXIT bit in the Cortex System Control register (SCR) is set, the Idle mode will be entered when the CPU exits the lowest priority ISR (Interrupt Service Routine, refer to the ARM Cortex

#### 23.8.8 16MHz Internal Oscillator (OSC16M) Control

| Name:     | OSC16MCTRL           |

|-----------|----------------------|

| Offset:   | 0x18                 |

| Reset:    | 0x82                 |

| Property: | PAC Write-Protection |

| Bit    | 7        | 6        | 5 | 4 | 3    | 2      | 1      | 0 |

|--------|----------|----------|---|---|------|--------|--------|---|

|        | ONDEMAND | RUNSTDBY |   |   | FSEL | .[1:0] | ENABLE |   |

| Access | R/W      | R/W      |   |   | R/W  | R/W    | R/W    |   |

| Reset  | 1        | 0        |   |   | 0    | 0      | 1      |   |

#### Bit 7 - ONDEMAND On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the OSC16M behaves during standby sleep mode.

| Value | Description                                                                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OSC16M is disabled in standby sleep mode if no peripheral requests the clock.                                                                                                                                   |

| 1     | The OSC16M is not stopped in standby sleep mode. If ONDEMAND=1, the OSC16M will be running when a peripheral is requesting the clock. If ONDEMAND=0, the clock source will always be running in standby sleep mode. |

#### Bits 3:2 – FSEL[1:0] Oscillator Frequency Selection

These bits control the oscillator frequency range.

| Value | Description |

|-------|-------------|

| 0x00  | 4MHz        |

| 0x01  | 8MHz        |

| 0x10  | 12MHz       |

| 0x11  | 16MHz       |

Bit 1 – ENABLE Oscillator Enable

# SAM L10/L11 Family

### SUPC – Supply Controller

| Value | Name     | Description           |

|-------|----------|-----------------------|

| 0xA   | DIV2048  | Divide clock by 2048  |

| 0xB   | DIV4096  | Divide clock by 4096  |

| 0xC   | DIV8192  | Divide clock by 8192  |

| 0xD   | DIV16384 | Divide clock by 16384 |

| 0xE   | DIV32768 | Divide clock by 32768 |

| 0xF   | DIV65536 | Divide clock by 65536 |

**Bit 11 – VREFSEL** BOD33 Voltage Reference Selection This bit is not synchronized.

| ſ | Value | Description                    |

|---|-------|--------------------------------|

| Γ | 0     | Selects VREF for the BOD33.    |

|   | 1     | Selects ULPVREF for the BOD33. |

**Bit 8 – ACTCFG** BOD33 Configuration in Active Sleep Mode

This bit is not synchronized.

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | In active mode, the BOD33 operates in continuous mode. |

| 1     | In active mode, the BOD33 operates in sampling mode.   |

#### Bit 6 – RUNSTDBY Run in Standby

This bit is not synchronized.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | In standby sleep mode, the BOD33 is disabled. |

| 1     | In standby sleep mode, the BOD33 is enabled.  |

#### **Bit 5 – STDBYCFG** BOD33 Configuration in Standby Sleep Mode

If the RUNSTDBY bit is set to '1', the STDBYCFG bit sets the BOD33 configuration in standby sleep mode.

This bit is not synchronized.

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | In standby sleep mode, the BOD33 is enabled and configured in continuous mode. |

| 1     | In standby sleep mode, the BOD33 is enabled and configured in sampling mode.   |

#### Bits 4:3 – ACTION[1:0] BOD33 Action

These bits are used to select the BOD33 action when the supply voltage crosses below the BOD33 threshold.

These bits are loaded from NVM User Row at start-up.

This bit field is not synchronized.

| Value | Name  | Description                 |  |

|-------|-------|-----------------------------|--|

| 0x0   | NONE  | No action                   |  |

| 0x1   | RESET | The BOD33 generates a reset |  |

# SAM L10/L11 Family

RTC – Real-Time Counter

#### 27.8.6 Interrupt Flag Status and Clear in COUNT32 mode (CTRLA.MODE=0)

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x0C<br>0x0000<br>- |      |      |      |      |      |      |

|--------|-----------------------------------------|--------------------------------|------|------|------|------|------|------|

| Bit    | 15                                      | 14                             | 13   | 12   | 11   | 10   | 9    | 8    |

|        | OVF                                     | TAMPER                         |      |      |      |      |      | CMP0 |

| Access | R/W                                     | R/W                            | •    |      |      |      |      | R/W  |

| Reset  | 0                                       | 0                              |      |      |      |      |      | 0    |

|        |                                         |                                |      |      |      |      |      |      |

| Bit    | 7                                       | 6                              | 5    | 4    | 3    | 2    | 1    | 0    |

|        | PER7                                    | PER6                           | PER5 | PER4 | PER3 | PER2 | PER1 | PER0 |

| Access | R/W                                     | R/W                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                              | 0    | 0    | 0    | 0    | 0    | 0    |

#### Bit 15 - OVF Overflow

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after an overflow condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

#### Bit 14 – TAMPER Tamper event

This flag is set after a damper condition occurs, and an interrupt request will be generated if INTENCLR.TAMPER/INTENSET.TAMPER is '1'. Writing a '0' to this bit has no effect. Writing a '1' to this bit clears the Tamper interrupt flag.

#### Bit 8 – CMP0 Compare 0

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with the compare condition, and an interrupt request will be generated if INTENCLR/SET.COMP0 is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Compare 0 interrupt flag.

### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PERn Periodic Interval n [n = 7..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the 0-to-1 transition of prescaler bit [n+2], and an interrupt request will be generated if INTENCLR/SET.PERn is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Periodic Interval n interrupt flag.

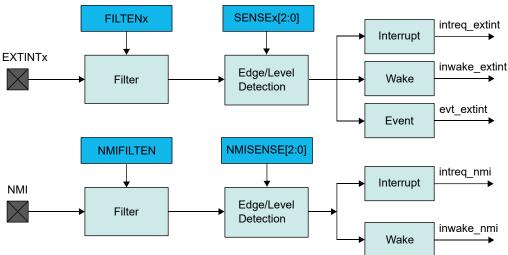

# 29. EIC – External Interrupt Controller

#### 29.1 Overview

The External Interrupt Controller (EIC) allows external pins to be configured as interrupt lines. Each interrupt line can be individually masked and can generate an interrupt on rising, falling, or both edges, or on high or low levels. Each external pin has a configurable filter to remove spikes. Each external pin can also be configured to be asynchronous in order to wake up the device from sleep modes where all clocks have been disabled. External pins can also generate an event. Each external pin can be defined as secured or non-secured, where secured pins can only be handled by secure accesses.

A separate non-maskable interrupt (NMI) is also supported. It has properties similar to the other external interrupts, but is connected to the NMI request of the CPU, enabling it to interrupt any other interrupt mode.

### 29.2 Features

- Up to 8 external pins (EXTINTx), plus one non-maskable pin (NMI)

- Dedicated, individually maskable interrupt for each pin

- Interrupt on rising, falling, or both edges

- Synchronous or asynchronous edge detection mode

- Interrupt pin debouncing

- Interrupt on high or low levels

- Asynchronous interrupts for sleep modes without clock

- Filtering of external pins

- Event generation from EXTINTx

- Selectable secured or non-secured attribution for each individual external pin (SAM L11)

### 29.3 Block Diagram

#### Figure 29-1. EIC Block Diagram

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | No programming of any locked lock region has happened since this bit was last cleared.       |

| 1     | Programming of at least one locked lock region has happened since this bit was last cleared. |

#### Bit 1 – PROGE Programming Error

This flag is set on the occurrence of a PROGE error.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | No invalid commands or bad keywords were written in the NVM Command register since this bit was last cleared.         |

| 1     | An invalid command and/or a bad keyword was/were written in the NVM Command register since this bit was last cleared. |

#### Bit 0 – DONE NVM Command Done

This bit can be cleared by writing a one to its bit location

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | The NVM controller has not completed any commands since the last clear. |

| 1     | At least one command has completed since the last clear.                |

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 31.6 Functional Description

#### 31.6.1 Principle of Operation

System bus transactions from the CPU to the security RAM undergoes a scrambling routine. Both address and data buses information are modified through an algorithm determined by a scrambling key. This is performed on both write and read transactions.

#### 31.6.2 Basic Operation

#### 31.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the TRAM is disabled (CTRLA.ENABLE is zero):

- Tamper Erase bit in the Control A register (CTRLA.TAMPERS)

- Data Remanence Protection bit in the Control A register (CTRLA.DRP)

- Silent Access bit in the Control A register (CTRLA.SILACC)

The following register is enable-protected:

• Data Scramble Control register (DSCC)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to one, but not at the same time as CTRLA.ENABLE is written to zero.

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 31.6.2.2 Enabling, Disabling and Resetting

The TRAM is enabled by writing a one to the Enable bit in the Control A register (CTRLA.ENABLE). The TRAM is disabled by writing a zero to CTRLA.ENABLE.

The TRAM is reset by writing a one to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TRAM will be reset to their initial state, and the TRAM will be disabled. All data in the secure RAM will be cleared to '0'.

#### 31.6.2.3 Scrambling

The Data Scramble Control (DSCC) must be configured before the CTRLA.ENABLE is set. These settings cannot be changed while the module is enabled.

The scrambling logic is enabled by writing one to the enable bit in the Data Scramble Control register (DSCC.DSCEN). Scrambling is disabled by writing a zero to DSCC.DSCEN. Writing a zero to CTRLA.ENABLE will also disable the scrambling, but will not clear the DSCC.DSCEN bit.

#### 31.6.2.4 Silent Access

Silent access bit (CTRLA.SILACC) must be configured before CTRLA.ENABLE is set. This setting cannot be changed while the module is enabled. When this mode is enabled, only 128 bytes of the security RAM are accessible since the other 128 bytes are reserved to store the 1's complement (bitwise invert) values. The physical access to the RAM is now twice as wide compared to the bus access. Therefore, only 8-bit

The flag will only be set when using a synchronous or resynchronized path. In the case of asynchronous path, the CHINTFLAGn.EVD is always zero.

#### 33.5.2.11 Channel Status

The Channel Status register (CHSTATUS) shows the status of the channels when using a synchronous or resynchronized path. There are two different status bits in CHSTATUS for each of the available channels:

- The CHSTATUSn.BUSYCH bit will be set when an event on the corresponding channel n has not been handled by all event users connected to that channel.

- The CHSTATUSn.RDYUSR bit will be set when all event users connected to the corresponding channel are ready to handle incoming events on that channel.

#### 33.5.2.12 Software Event

A software event can be initiated on a channel by writing a '1' to the Software Event bit in the Channel register (CHANNELm.SWEVT). Then the software event can be serviced as any event generator; i.e., when the bit is set to '1', an event will be generated on the respective channel.

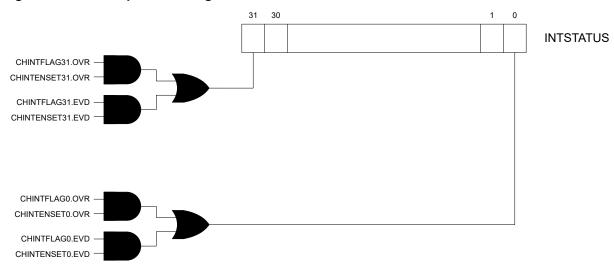

#### 33.5.2.13 Interrupt Status and Interrupts Arbitration

The Interrupt Status register stores all channels with pending interrupts, as shown below.

#### Figure 33-2. Interrupt Status Register

The Event System can arbitrate between all channels with pending interrupts. The arbiter can be configured to prioritize statically or dynamically the incoming events. The priority is evaluated each time a new channel has an interrupt pending, or an interrupt has been cleared. The Channel Pending Interrupt register (INTPEND) will provide the channel number with the highest interrupt priority, and the corresponding channel interrupt flags and status bits.

By default, static arbitration is enabled (PRICTRL.RRENx is '0'), the arbiter will prioritize a low channel number over a high channel number as shown below. When using the status scheme, there is a risk of high channel numbers never being granted access by the arbiter. This can be avoided using a dynamic arbitration scheme.

# SAM L10/L11 Family

# EVSYS – Event System

| Value     | Event Generator | Description           |

|-----------|-----------------|-----------------------|

| 0x19-0x1C | DMAC_CH         | DMAC channel          |

| 0x1D      | TC0_OVF         | TC0 overflow          |

| 0x1E-0x1F | TC0_MCX         | TC0 match/compare     |

| 0x20      | TC1_OVF         | TC1 overflow          |

| 0x21-0x22 | TC1_MCX         | TC1 match/compare     |

| 0x23      | TC2_OVF         | TC2 overflow          |

| 0x24-0x25 | TC2_MCX         | TC2 match/compare     |

| 0x26      | ADC_RESRDY      | ADC resolution ready  |

| 0x27      | ADC_WINMON      | ADC window monitor    |

| 0x28-0x29 | AC_COMP         | AC comparator         |

| 0x2A      | AC_WIN          | AC window             |

| 0x2B      | DAC_EMPTY       | DAC empty             |

| 0x2C      | PTC_EOC         | PTC end of conversion |

| 0x2D      | PTC_WCOMP       | PTC window comparator |

| 0x2E      | TRNG_READY      | Data ready            |

| 0x2F-0x30 | CCL_LUTOUT      | CCL output            |

| 0x31      | PAC_ERR         | PAC access error      |

#### 33.7.13 Event User m

| Name:     | USERm                            |

|-----------|----------------------------------|

| Offset:   | 0x0120 + m*0x01 [m=022]          |

| Reset:    | 0x0                              |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding event user (USERx) is set as Non-Secured in the NONSECUSER register.

| Bit    | 7 | 6 | 5 | 4 | 3            | 2          | 1          | 0          |

|--------|---|---|---|---|--------------|------------|------------|------------|

|        |   |   |   |   | CHANNEL[3:0] |            |            |            |

| Access |   |   |   |   | R/W/RW*/RW   | R/W/RW*/RW | R/W/RW*/RW | R/W/RW*/RW |

| Reset  |   |   |   |   | 0            | 0          | 0          | 0          |

#### Bits 3:0 – CHANNEL[3:0] Channel Event Selection

These bits select channel n to connect to the event user m.

**Note:** A value x of this bit field selects channel n = x-1.

| USERm  | User Multiplexer | Description          | Path Type |

|--------|------------------|----------------------|-----------|

| m=0    | OSCCTRL_TUNE     | DFLLULP Tune         | A         |

| m=1    | RTC_TAMPER       | RTC Tamper           | A         |

| m=2    | NWMCTRL_PAGEW    | NVMCTRL Auto-Write   | A,S,R     |

| m=36   | PORT_EV[03]      | Port Event 03        | A         |

| m=710  | DMAC_CH[03]      | Channel 03           | S,R       |

| m=11   | TC0_EVU          | TC0 EVU              | A,S,R     |

| m=12   | TC1_EVU          | TC1 EVU              | A,S,R     |

| m=13   | TC2_EVU          | TC2 EVU              | A,S,R     |

| m=14   | ADC_START        | ADC Start Conversion | A,S,R     |

| m=15   | ADC_SYNC         | Flush ADC            | A,S,R     |

| m=1617 | AC_COMP[01]      | Start Comparator 01  | A         |

| m=18   | DAC_START        | DAC Start Conversion | A         |

| m=19   | PTC_STCONV       | PTC Start Conversion | A,S,R     |

| m=20   | PTC_DSEQR        | PTC Sequencing       | A,S,R     |

| m=2122 | CCL_LUTIN[01]    | CCL Input 01         | A         |

#### Table 33-3. User Multiplexer Number m

1) A = Asynchronous path, S = Synchronous path, R = Resynchronized path

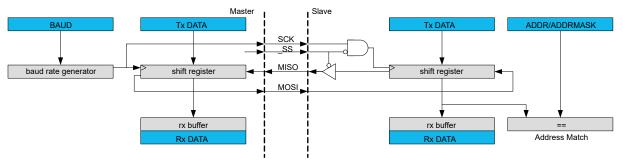

#### 36.3 Block Diagram

Figure 36-1. Full-Duplex SPI Master Slave Interconnection

### 36.4 Signal Description

#### Table 36-1. SERCOM SPI Signals

| Signal Name | Туре        | Description         |

|-------------|-------------|---------------------|

| PAD[3:0]    | Digital I/O | General SERCOM pins |

One signal can be mapped to one of several pins.

#### 36.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 36.5.1 I/O Lines

In order to use the SERCOM's I/O lines, the I/O pins must be configured using the IO Pin Controller (PORT).

When the SERCOM is configured for SPI operation, the SERCOM controls the direction and value of the I/O pins according to the table below. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver is disabled, the data input pin can be used for other purposes. In master mode, the slave select line ( $\overline{SS}$ ) is hardware controlled when the Master Slave Select Enable bit in the Control B register (CTRLB.MSSEN) is '1'.

#### Table 36-2. SPI Pin Configuration

| Pin  | Master SPI             | Slave SPI |

|------|------------------------|-----------|

| MOSI | Output                 | Input     |

| MISO | Input                  | Output    |

| SCK  | Output                 | Input     |

| SS   | Output (CTRLB.MSSEN=1) | Input     |

The combined configuration of PORT, the Data In Pinout and the Data Out Pinout bit groups in the Control A register (CTRLA.DIPO and CTRLA.DOPO) define the physical position of the SPI signals in the table above.

#### **Related Links**

**Note:** The  $I^2C$  standard *Fm*+ (Fast-mode plus) requires a nominal high to low SCL ratio of 1:2, and BAUD should be set accordingly. At a minimum, BAUD.BAUD and/or BAUD.BAUDLOW must be non-zero.

**Startup Timing** The minimum time between SDA transition and SCL rising edge is 6 APB cycles when the DATA register is written in smart mode. If a greater startup time is required due to long rise times, the time between DATA write and IF clear must be controlled by software.

**Note:** When timing is controlled by user, the Smart Mode cannot be enabled.

#### Master Clock Generation (High-Speed Mode)

For I<sup>2</sup>C *Hs* transfers, there is no SCL synchronization. Instead, the SCL frequency is determined by the GCLK\_SERCOMx\_CORE frequency ( $f_{GCLK}$ ) and the High-Speed Baud setting in the Baud register (BAUD.HSBAUD). When BAUD.HSBAUDLOW=0, the HSBAUD value will determine both SCL high and SCL low. In this case the following formula determines the SCL frequency.

$$f_{\rm SCL} = \frac{f_{\rm GCLK}}{2 + 2 \cdot HS \, BAUD}$$

When HSBAUDLOW is non-zero, the following formula determines the SCL frequency.

$$f_{\rm SCL} = \frac{f_{\rm GCLK}}{2 + HS\,BAUD + HSBAUDLOW}$$

**Note:** The I<sup>2</sup>C standard *Hs* (High-speed) requires a nominal high to low SCL ratio of 1:2, and HSBAUD should be set accordingly. At a minimum, BAUD.HSBAUD and/or BAUD.HSBAUDLOW must be non-zero.

#### 37.6.2.4.2 Transmitting Address Packets

The I<sup>2</sup>C master starts a bus transaction by writing the I<sup>2</sup>C slave address to ADDR.ADDR and the direction bit, as described in 37.6.1 Principle of Operation. If the bus is busy, the I<sup>2</sup>C master will wait until the bus becomes idle before continuing the operation. When the bus is idle, the I<sup>2</sup>C master will issue a start condition on the bus. The I<sup>2</sup>C master will then transmit an address packet using the address written to ADDR.ADDR. After the address packet has been transmitted by the I<sup>2</sup>C master, one of four cases will arise according to arbitration and transfer direction.

#### Case 1: Arbitration lost or bus error during address packet transmission

If arbitration was lost during transmission of the address packet, the Master on Bus bit in the Interrupt Flag Status and Clear register (INTFLAG.MB) and the Arbitration Lost bit in the Status register (STATUS.ARBLOST) are both set. Serial data output to SDA is disabled, and the SCL is released, which disables clock stretching. In effect the I<sup>2</sup>C master is no longer allowed to execute any operation on the bus until the bus is idle again. A bus error will behave similarly to the arbitration lost condition. In this case, the MB interrupt flag and Master Bus Error bit in the Status register (STATUS.BUSERR) are both set in addition to STATUS.ARBLOST.

The Master Received Not Acknowledge bit in the Status register (STATUS.RXNACK) will always contain the last successfully received acknowledge or not acknowledge indication.

In this case, software will typically inform the application code of the condition and then clear the interrupt flag before exiting the interrupt routine. No other flags have to be cleared at this moment, because all flags will be cleared automatically the next time the ADDR.ADDR register is written.

#### Case 2: Address packet transmit complete – No ACK received

If there is no I<sup>2</sup>C slave device responding to the address packet, then the INTFLAG.MB interrupt flag and STATUS.RXNACK will be set. The clock hold is active at this point, preventing further activity on the bus.

#### 38.7.2.1 Control A

| Name:     | CTRLA                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x00                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Write-Synchronized, Enable-Protected |

| Bit    | 31       | 30       | 29     | 28       | 27        | 26  | 25            | 24      |

|--------|----------|----------|--------|----------|-----------|-----|---------------|---------|

|        |          |          |        |          |           |     |               |         |

| Access |          |          |        |          |           |     |               |         |

| Reset  |          |          |        |          |           |     |               |         |

|        |          |          |        |          |           |     |               |         |

| Bit    | 23       | 22       | 21     | 20       | 19        | 18  | 17            | 16      |

|        |          |          | COPEN1 | COPEN0   |           |     | CAPTEN1       | CAPTEN0 |

| Access |          |          | R/W    | R/W      |           |     | R/W           | R/W     |

| Reset  |          |          | 0      | 0        |           |     | 0             | 0       |

|        |          |          |        |          |           |     |               |         |

| Bit    | 15       | 14       | 13     | 12       | 11        | 10  | 9             | 8       |

|        |          |          |        |          | ALOCK     | F   | PRESCALER[2:0 | 1       |

| Access |          |          |        |          | R/W       | R/W | R/W           | R/W     |

| Reset  |          |          |        |          | 0         | 0   | 0             | 0       |

|        |          |          |        |          |           |     |               |         |

| Bit    | 7        | 6        | 5      | 4        | 3         | 2   | 1             | 0       |

|        | ONDEMAND | RUNSTDBY | PRESCS | YNC[1:0] | MODE[1:0] |     | ENABLE        | SWRST   |

| Access | R/W      | R/W      | R/W    | R/W      | R/W       | R/W | R/W           | W       |

| Reset  | 0        | 0        | 0      | 0        | 0         | 0   | 0             | 0       |

#### Bits 20, 21 – COPENx Capture On Pin x Enable

Bit x of COPEN[1:0] selects the trigger source for capture operation, either events or I/O pin input.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

#### Bits 16, 17 – CAPTENx Capture Channel x Enable

Bit x of CAPTEN[1:0] selects whether channel x is a capture or a compare channel.

These bits are not synchronized.

| <b>/</b> alue | Description                           |

|---------------|---------------------------------------|

| )             | CAPTEN disables capture on channel x. |

| 1             | CAPTEN enables capture on channel x.  |

#### Bit 11 – ALOCK Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

#### 38.7.3.9 Waveform Generation Control

Name:WAVEOffset:0x0CReset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | WAVEG | GEN[1:0] |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

#### Bits 1:0 – WAVEGEN[1:0] Waveform Generation Mode

These bits select the waveform generation operation. They affect the top value, as shown in 38.6.2.6.1 Waveform Output Operations. They also control whether frequency or PWM waveform generation should be used. The waveform generation operations are explained in 38.6.2.6.1 Waveform Output Operations.

These bits are not synchronized.

| Value | Name | Operation        | Top Value              | Output<br>Waveform<br>on Match | Output Waveform<br>on Wraparound |

|-------|------|------------------|------------------------|--------------------------------|----------------------------------|

| 0x0   | NFRQ | Normal frequency | PER <sup>1</sup> / Max | Toggle                         | No action                        |

| 0x1   | MFRQ | Match frequency  | CC0                    | Toggle                         | No action                        |

| 0x2   | NPWM | Normal PWM       | PER <sup>1</sup> / Max | Set                            | Clear                            |

| 0x3   | MPWM | Match PWM        | CC0                    | Set                            | Clear                            |

1) This depends on the TC mode: In 8-bit mode, the top value is the Period Value register (PER). In 16and 32-bit mode it is the respective MAX value.

# SAM L10/L11 Family

## **Electrical Characteristics**

| Symbol                 | Parameters                        | Conditions      | Min | Тур | Мах      | Unit |

|------------------------|-----------------------------------|-----------------|-----|-----|----------|------|

| Vin                    | Input channel range               | -               | 0   | -   | VDDANA   | V    |

| Vcmin                  | Input common mode voltage         | For Vref > 1.0V | 0.7 | -   | Vref-0.7 | V    |

|                        |                                   | For Vref=1.0V   | 0.3 | -   | Vref-0.3 | V    |

| CSAMPLE <sup>(1)</sup> | Input sampling capacitance        |                 | -   | 2.8 | 3.2      | pF   |

| RSAMPLE <sup>(1)</sup> | Input sampling on-resistance      |                 | -   | -   | 1715     | Ω    |

| Rref <sup>(1)</sup>    | Reference input source resistance | REFCOMP = 1     | -   | -   | 5        | kΩ   |

#### Note:

1. These values are based on simulation. They are not covered by production test limits or characterization.

#### Table 46-24. Differential Mode <sup>(1)</sup>

| Symb   | Parameters                     | Conditions                                 |                                           | Measurements |              |              | 11::4 |

|--------|--------------------------------|--------------------------------------------|-------------------------------------------|--------------|--------------|--------------|-------|

| ol     |                                |                                            |                                           | Min          | Тур          | Max          | Unit  |

| ENOB   | Effective<br>Number of<br>bits | Fadc = 1Msps                               | Vref=2.0V Vddana=3.0V                     | 9.1          | 10.2         | 10.8         | bits  |

|        |                                |                                            | Vref=1.0V Vddana=1.6V<br>to 3.6V          | 9.0          | 10.1         | 10.6         |       |

|        |                                |                                            | Vref=Vddana=1.6V to<br>3.6V               | 8.9          | 9.9          | 11.0         |       |

|        |                                |                                            | Bandgap Reference,<br>Vddana=1.6V to 3.6V | 9.0          | 9.8          | 10.6         |       |

| TUE    | Total<br>Unadjusted<br>Error   | without offset<br>and gain<br>compensation | Vref=Vddana=1.6V to<br>3.6V               | -            | 7            | 32           | LSB   |

| INL    | Integral Non<br>Linearity      | without offset<br>and gain<br>compensation | Vref=Vddana=1.6V to<br>3.6V               | -            | +/-1.9       | +/-4         | -     |

| DNL    | Differential<br>Non Linearity  | without offset<br>and gain<br>compensation | Vref=Vddana=1.6V to<br>3.6V               | -            | +0.94/-<br>1 | +1.85/<br>-1 |       |

| Gain   | Gain Error                     | without gain<br>compensation               | Vref=1V Vddana=1.6V to<br>3.6V            | -            | +/-0.38      | +/-1.9       | %     |

|        |                                |                                            | Vref=3V Vddana=1.6V to<br>3.6V            | -            | +/-0.14      | +/-0.9       |       |

|        |                                |                                            | Bandgap Reference                         | -            | +/-0.64      | +/-5.4       |       |

|        |                                |                                            | Vref=Vddana=1.6V to<br>3.6V               | -            | +/-0.15      | +/-0.9       |       |

| Offset | Offset Error                   | without offset compensation                | Vref=1V Vddana=1.6V to<br>3.6V            | -            | +/-0.13      | +/-15.<br>8  | mV    |

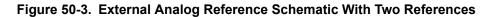

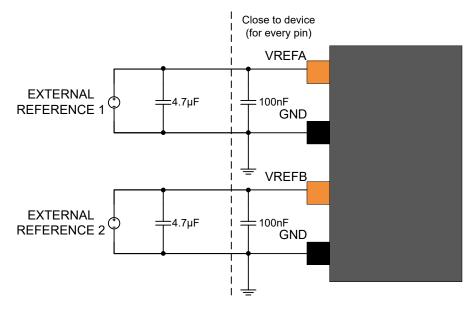

#### Figure 50-4. External Analog Reference Schematic With One Reference

#### Table 50-2. External Analog Reference Connections

| Signal Name | Recommended Pin Connection                                                                                                                                           | Description                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| VREFx       | 1.0V to $(V_{DDANA} - 0.6V)$ for ADC<br>1.0V to $(V_{DDANA} - 0.15V)$ for DAC<br>Decoupling/filtering capacitors<br>100nF <sup>(1)(2)</sup> and 4.7µF <sup>(1)</sup> | External reference VREFx for the analog port |

| GND         |                                                                                                                                                                      | Ground                                       |

1. These values are only given as a typical example.

analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.