Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e14a-aft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

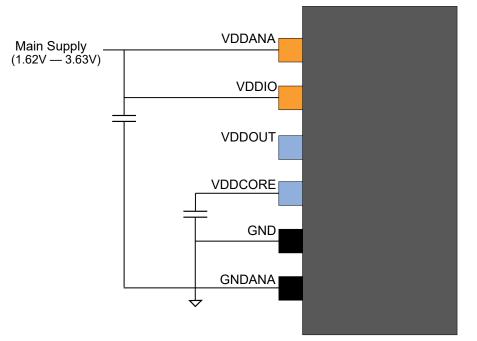

Figure 6-2. Power Supply Connections for Linear (LDO) Mode Only

Note: Refer to "Schematic Checklist" chapter for additional information.

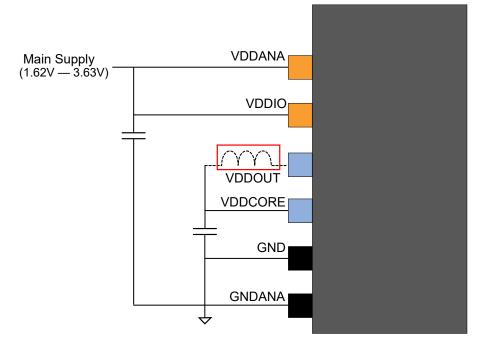

Figure 6-3. Power Supply Connections for Switching (BUCK) / Linear (LDO) Modes

**Note:** Refer to "Schematic Checklist" chapter for additional information.

#### 14.4.2.1.3 CRC Computation and Programming

The CRCs needs to be recalculated and updated in their respective NVM row as soon as a data from any of the checked regions is changed.

**Important:** USERCRC and BOCORCRC CRCs programming must be done by any programming tool supporting the SAM L11 devices.

The algorithm is a CRC-32 module embedded in the DSU peripheral and that uses for both CRC calculation with the following parameters:

- Width = 32 bits

- Polynomial = 0x04C11DB7 (Poly)

- Initial Value = 0xFFFFFFFF (Init)

- Input Data is reflected (RefIn)

- Output Data is reflected (RefOut)

- No XOR is performed on the output CRC (XorOut)

Example: the DSU CRC of 0x31, 0x32, 0x33, 0x34, 0x35, 0x36, 0x37, 0x38, 0x39 is 0x340BC6D9

#### 14.4.2.2 Memories and Peripherals Configurations Initialization

For SAM L11 devices, memories and peripherals security attributions are done by reading the different fuses values from the NVM User (UROW) and Boot Configuration (BOCOR) rows.

The Boot ROM is responsible for setting these attributions on the different concerned memory and peripheral controllers:

- Set memory security attribution according to AS, ANSC, DS, RS, BS, BSNC and BOOTPROT fuses

- Set peripherals security attribution according to NONSECA, NONSECB and NONSECC fuses

**Important:** The Boot ROM does not perform any consistency checks on the configured memory attributions (e.g setting BS>BOOTPROT will not trigger any errors during Boot ROM execution).

#### 14.4.2.3 Secure Boot

Depending on the BOOTOPT fuse value (from BOCOR NVM row), the following secure boot integrity checks will be performed on:

- The Flash BS memory area which is composed by:

- The Flash Secure BOOT memory region

- The Flash Non-Secure Callable BOOT memory region

- And the NVM Boot Configuration row (BOCOR)

#### Table 14-4. Secure Boot Options

| вооторт | Verified Areas         | Verification Method |  |

|---------|------------------------|---------------------|--|

| 0       | None                   | -                   |  |

| 1       | Flash BS Memory Region | SHA-256             |  |

|         | +                      |                     |  |

|         | NVM BOCOR row          |                     |  |

PAC - Peripheral Access Controller

Bits 1, 2, 3 – SERCOM Interrupt Flag for SERCOMn [n = 2..0]

Bit 0 – EVSYS Interrupt Flag for EVSYS

Two Boot Communication Channel status bits in the Status B registers (STATUS.BCCDx) indicate whether a new value has been written in BCC0 or BCC1. These bits, BCC0D and BCC1D, are located in the STATUSB registers. They are automatically set on write and cleared on read.

**Note:** The DCC0 and DCC1 registers are shared with the BCC0 and BCC1 registers therefore using DCC is not recommended while the Boot ROM is being executed.

## 16.10.6 Testing of On-Board Memories MBIST

The DSU implements a feature for automatic testing of memory also known as MBIST (memory built-in self test). This is primarily intended for production test of on-board memories. MBIST cannot be operated from the external address range when DAL<0x2. If an MBIST command is issued when the device is protected, it is filtered-out, a protection error is reported in the Protection Error bit in the Status A register (STATUSA.PERR) and STATUSA.DONE don't rise.

## 1. Algorithm

The algorithm used for testing is a type of March algorithm called "March LR". This algorithm is able to detect a wide range of memory defects, while still keeping a linear run time. The algorithm is:

- 1.1. Write entire memory to '0', in any order.

- 1.2. Bit for bit read '0', write '1', in descending order.

- 1.3. Bit for bit read '1', write '0', read '0', write '1', in ascending order.

- 1.4. Bit for bit read '1', write '0', in ascending order.

- 1.5. Bit for bit read '0', write '1', read '1', write '0', in ascending order.

- 1.6. Read '0' from entire memory, in ascending order.

The specific implementation used has a run time which depends on the CPU clock frequency and the number of bytes tested in the RAM. The detected faults are:

- Address decoder faults

- Stuck-at faults

- Transition faults

- Coupling faults

- Linked Coupling faults

- 2. Starting MBIST

To test a memory, you need to write the start address of the memory to the ADDR.ADDR bit field, and the size of the memory into the Length register.

For best test coverage, an entire physical memory block should be tested at once. It is possible to test only a subset of a memory, but the test coverage will then be somewhat lower.

The actual test is started by writing a '1' to CTRL.MBIST. A running MBIST operation can be canceled by writing a '1' to CTRL.SWRST.

3. Interpreting the Results

The tester should monitor the STATUSA register. When the operation is completed, STATUSA.DONE is set. There are two different modes:

ADDR.AMOD=0: exit-on-error (default)

In this mode, the algorithm terminates either when a fault is detected or on successful completion. In both cases, STATUSA.DONE is set. If an error was detected, STATUSA.FAIL will be set. User then can read the DATA and ADDR registers to locate the fault.

ADDR.AMOD=1: pause-on-error

### Bit 1 – PM PM APBA Clock Enable

| Value | Description                           |

|-------|---------------------------------------|

| C     | The APBA clock for the PM is stopped. |

| 1     | The APBA clock for the PM is enabled. |

## Bit 0 – PAC PAC APBA Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBA clock for the PAC is stopped. |

| 1     | The APBA clock for the PAC is enabled. |

### 20.6.2.2 Enabling, Disabling and Resetting

The FREQM is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The peripheral is disabled by writing CTRLA.ENABLE=0.

The FREQM is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). On software reset, all registers in the FREQM will be reset to their initial state, and the FREQM will be disabled.

Then ENABLE and SWRST bits are write-synchronized.

## **Related Links**

20.6.7 Synchronization

### 20.6.2.3 Measurement

In the Configuration A register, the Number of Reference Clock Cycles field (CFGA.REFNUM) selects the duration of the measurement. The measurement is given in number of GCLK\_FREQM\_REF periods. **Note:** The REFNUM field must be written before the FREQM is enabled.

After the FREQM is enabled, writing a '1' to the START bit in the Control B register (CTRLB.START) starts the measurement. The BUSY bit in Status register (STATUS.BUSY) is set when the measurement starts, and cleared when the measurement is complete.

There is also an interrupt request for Measurement Done: When the Measurement Done bit in Interrupt Enable Set register (INTENSET.DONE) is '1' and a measurement is finished, the Measurement Done bit in the Interrupt Flag Status and Clear register (INTFLAG.DONE) will be set and an interrupt request is generated.

The result of the measurement can be read from the Value register (VALUE.VALUE). The frequency of the measured clock GCLK\_FREQM\_MSR is then:

$$f_{\text{CLK}_{\text{MSR}}} = \left(\frac{\text{VALUE}}{\text{REFNUM}}\right) f_{\text{CLK}_{\text{REF}}}$$

**Note:** In order to make sure the measurement result (VALUE.VALUE[23:0]) is valid, the overflow status (STATUS.OVF) should be checked.

In case an overflow condition occurred, indicated by the Overflow bit in the STATUS register (STATUS.OVF), either the number of reference clock cycles must be reduced (CFGA.REFNUM), or a faster reference clock must be configured. Once the configuration is adjusted, clear the overflow status by writing a '1' to STATUS.OVF. Then another measurement can be started by writing a '1' to CTRLB.START.

## 20.6.3 DMA Operation

Not applicable.

## 20.6.4 Interrupts

The FREQM has one interrupt source:

• DONE: A frequency measurement is done.

The interrupt flag in the Interrupt Flag Status and Clear (20.8.6 INTFLAG) register is set when the interrupt condition occurs. The interrupt can be enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (20.8.5 INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (20.8.4 INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the

© 2018 Microchip Technology Inc.

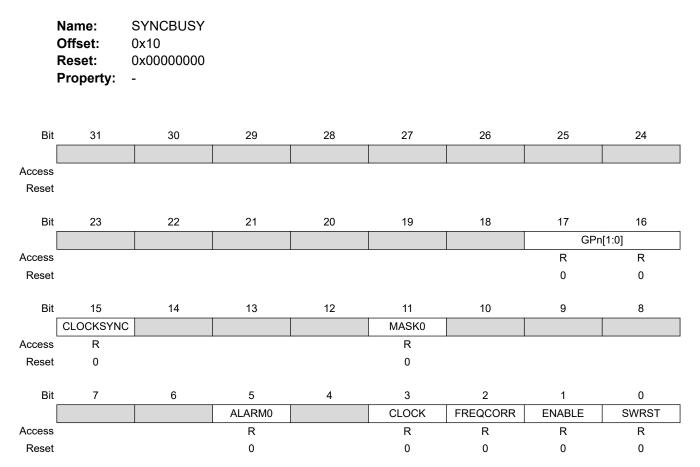

RTC – Real-Time Counter

## 27.12.8 Synchronization Busy in Clock/Calendar mode (CTRLA.MODE=2)

## Bits 17:16 - GPn[1:0] General Purpose n Synchronization Busy Status

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | Write synchronization for GPn register is complete. |

| 1     | Write synchronization for GPn register is ongoing.  |

#### Bit 15 - CLOCKSYNC Clock Read Sync Enable Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Write synchronization for CTRLA.CLOCKSYNC bit is complete. |

| 1     | Write synchronization for CTRLA.CLOCKSYNC bit is ongoing.  |

#### Bit 11 - MASK0 Mask 0 Synchronization Busy Status

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Write synchronization for MASK0 register is complete. |

| 1     | Write synchronization for MASK0 register is ongoing.  |

### Bit 5 – ALARMO Alarm 0 Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for ALARM0 register is complete. |

| 1     | Write synchronization for ALARM0 register is ongoing.  |

# 29.4 Signal Description

| Signal Name | Туре          | Description                |  |  |

|-------------|---------------|----------------------------|--|--|

| EXTINT[70]  | Digital Input | External interrupt pin     |  |  |

| NMI         | Digital Input | Non-maskable interrupt pin |  |  |

One signal may be available on several pins.

## 29.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 29.5.1 I/O Lines

Using the EIC's I/O lines requires the I/O pins to be configured.

## **Related Links**

32. PORT - I/O Pin Controller

### 29.5.2 Power Management

All interrupts are available down to STANDBY sleep mode, but the EIC can be configured to automatically mask some interrupts in order to prevent device wake-up.

The EIC will continue to operate in any sleep mode where the selected source clock is running. The EIC's interrupts can be used to wake up the device from sleep modes. Events connected to the Event System can trigger other operations in the system without exiting sleep modes.

## **Related Links**

22. PM – Power Manager

## 29.5.3 Clocks

The EIC bus clock (CLK\_EIC\_APB) can be enabled and disabled by the Main Clock Controller, the default state of CLK\_EIC\_APB can be found in the Peripheral Clock Masking section.

Some optional functions need a peripheral clock, which can either be a generic clock (GCLK\_EIC, for wider frequency selection) or a Ultra Low-Power 32 KHz clock (CLK\_ULP32K, for highest power efficiency). One of the clock sources must be configured and enabled before using the peripheral:

GCLK\_EIC is configured and enabled in the Generic Clock Controller.

CLK\_ULP32K is provided by the internal Ultra Low-Power (OSCULP32K) Oscillator in the OSC32KCTRL module.

Both GCLK\_EIC and CLK\_ULP32K are asynchronous to the user interface clock (CLK\_EIC\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

## **Related Links**

19. MCLK – Main Clock

19.6.2.6 Peripheral Clock Masking

- 18. GCLK Generic Clock Controller

- 24. OSC32KCTRL 32KHz Oscillators Controller

### 30.8.10 Secure Region Unlock Bits

| Name:     | SULCK                                                |

|-----------|------------------------------------------------------|

| Offset:   | 0x20                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Secure                   |

| >      |       | Important: | This register i | s only availab | ble for SAM L | 11 and has no | o effect for <b>S</b> A | M L10.  |

|--------|-------|------------|-----------------|----------------|---------------|---------------|-------------------------|---------|

| Bit    | 15    | 14         | 13              | 12             | 11            | 10            | 9                       | 8       |

|        |       |            |                 | SLKE           | Y[7:0]        |               |                         |         |

| Access | W/-/W | W/-/W      | W/-/W           | W/-/W          | W/-/W         | W/-/W         | W/-/W                   | W/-/W   |

| Reset  | 0     | 0          | 0               | 0              | 0             | 0             | 0                       | 0       |

|        |       |            |                 |                |               |               |                         |         |

| Bit    | 7     | 6          | 5               | 4              | 3             | 2             | 1                       | 0       |

|        |       |            |                 |                |               | DS            | AS                      | BS      |

| Access |       | ·          | ·               |                |               | RW/R/RW       | RW/R/RW                 | RW/R/RW |

| Reset  |       |            |                 |                |               | x             | x                       | х       |

### Bits 15:8 – SLKEY[7:0] Secure Unlock Key

When this bit group is written to the key value 0xA5, the write will be performed. If a value different from the key value is tried, the write will be discarded and INTFLAG.KEYE set.

#### Bit 2 – DS DATA Secure Unlock Bit

Default state after erase will be unlocked (0x1).

| Value | Description                  |

|-------|------------------------------|

| 0     | The DS region is locked.     |

| 1     | The DS region is not locked. |

# Bit 1 – AS Application Secure Unlock Bit

Default state after erase will be unlocked (0x1).

| Value | Description                  |

|-------|------------------------------|

| 0     | The AS region is locked.     |

| 1     | The AS region is not locked. |

#### Bit 0 - BS BOOT Secure Unlock Bit

Default state after erase will be unlocked (0x1).

| Value | Description                  |

|-------|------------------------------|

| 0     | The BS region is locked.     |

| 1     | The BS region is not locked. |

#### 30.8.11 Non-Secure Region Unlock Bits

| Name:     | NSULCK                                               |

|-----------|------------------------------------------------------|

| Offset:   | 0x22                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | PAC Write-Protection, Write-Mix-Secure               |

**Important:** For **SAM L11 Non-Secure** accesses, write accesses (W\*) are allowed only if Non-Secure Write is set in the NONSEC register.

| Bit    | 15     | 14          | 13     | 12     | 11     | 10        | 9         | 8         |  |

|--------|--------|-------------|--------|--------|--------|-----------|-----------|-----------|--|

| [      |        | NSLKEY[7:0] |        |        |        |           |           |           |  |

| Access | W/W*/W | W/W*/W      | W/W*/W | W/W*/W | W/W*/W | W/W*/W    | W/W*/W    | W/W*/W    |  |

| Reset  | 0      | 0           | 0      | 0      | 0      | 0         | 0         | 0         |  |

|        |        |             |        |        |        |           |           |           |  |

| Bit    | 7      | 6           | 5      | 4      | 3      | 2         | 1         | 0         |  |

| Γ      |        |             |        |        |        | DNS       | ANS       | BNS       |  |

| Access |        |             |        |        |        | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |

| Reset  |        |             |        |        |        | x         | x         | x         |  |

## Bits 15:8 – NSLKEY[7:0] Non-Secure Unlock Key

When this bit group is written to the key value 0xA5, the write will be performed. If a value different from the key value is tried, the write will be discarded and INTFLAG.KEYE set.

## Bit 2 – DNS Data Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure Data Flash region corresponds to the entire Data Flash region.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Non-Secure Data Flash region is locked.     |

| 1     | The Non-Secure Data Flash region is not locked. |

#### Bit 1 - ANS Application Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure APPLICATION region corresponds to the entire APPLICATION Flash region.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The Non-Secure APPLICATION region is locked.     |

| 1     | The Non-Secure APPLICATION region is not locked. |

## Bit 0 - BNS BOOT Non-Secure Unlock Bit

**Note:** For **SAM L10** devices, the Non-Secure BOOT region corresponds to the entire BOOT Flash region.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Non-Secure BOOT region is locked.     |

| 1     | The Non-Secure BOOT region is not locked. |

#### 32.8.2 Data Direction Clear

| Name:     | DIRCLR                           |

|-----------|----------------------------------|

| Offset:   | 0x04                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

This register allows the user to set one or more I/O pins as an input, without doing a read-modify-write operation. Changes in this register will also be reflected in the Data Direction (DIR), Data Direction Toggle (DIRTGL) and Data Direction Set (DIRSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31           | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|--------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Dir (  | 01           |           | 20        |           | R[31:24]  | 20        | 20        |           |

| l      |              |           |           |           |           |           |           |           |

| Access | RW/RW*/RW    | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |              |           |           |           |           |           |           |           |

| Bit    | 23           | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |              |           |           | DIRCLE    | R[23:16]  |           |           |           |

| Access | RW/RW*/RW    | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |              |           |           |           |           |           |           |           |

| Bit    | 15           | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

| [      | DIRCLR[15:8] |           |           |           |           |           |           |           |

| Access | RW/RW*/RW    | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |              |           |           |           |           |           |           |           |

| Bit    | 7            | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| [      |              |           |           | DIRCI     | .R[7:0]   |           |           |           |

| l      |              |           |           |           |           |           |           |           |

| Access | RW/RW*/RW    | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

## Bits 31:0 - DIRCLR[31:0] Port Data Direction Clear

Writing a '0' to a bit has no effect.

## 35.8.13 DBGCTRL

#### 35.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 35.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 35.5.10 Analog Connections

Not applicable.

## **35.6 Functional Description**

#### 35.6.1 Principle of Operation

The USART uses the following lines for data transfer:

- RxD for receiving

- TxD for transmitting

- XCK for the transmission clock in synchronous operation

USART data transfer is frame based. A serial frame consists of:

- 1 start bit

- From 5 to 9 data bits (MSB or LSB first)

- No, even or odd parity bit

- 1 or 2 stop bits

A frame starts with the start bit followed by one character of data bits. If enabled, the parity bit is inserted after the data bits and before the first stop bit. After the stop bit(s) of a frame, either the next frame can

### 36.8.8 Synchronization Busy

|        | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x1C<br>0x00000000<br>- |    |    |    |       |        |       |

|--------|-----------------------------------------|-------------------------------------|----|----|----|-------|--------|-------|

| Bit    | 31                                      | 30                                  | 29 | 28 | 27 | 26    | 25     | 24    |

|        |                                         |                                     |    |    |    |       |        |       |

| Access |                                         |                                     |    |    |    |       |        |       |

| Reset  |                                         |                                     |    |    |    |       |        |       |

|        |                                         |                                     |    |    |    |       |        |       |

| Bit    | 23                                      | 22                                  | 21 | 20 | 19 | 18    | 17     | 16    |

|        |                                         |                                     |    |    |    |       |        |       |

| Access |                                         |                                     |    |    |    |       |        |       |

| Reset  |                                         |                                     |    |    |    |       |        |       |

| -      |                                         |                                     | 10 | 10 |    |       |        |       |

| Bit    | 15                                      | 14                                  | 13 | 12 | 11 | 10    | 9      | 8     |

|        |                                         |                                     |    |    |    |       |        |       |

| Access |                                         |                                     |    |    |    |       |        |       |

| Reset  |                                         |                                     |    |    |    |       |        |       |

| Bit    | 7                                       | 6                                   | 5  | 4  | 3  | 2     | 1      | 0     |

| Dit    | ,                                       | Ū                                   | 3  | •  | 5  | CTRLB | ENABLE | SWRST |

| Access |                                         |                                     |    |    |    | R     | R      | R     |

| Reset  |                                         |                                     |    |    |    | 0     | 0      | 0     |

## Bit 2 – CTRLB CTRLB Synchronization Busy

Writing to the CTRLB when the SERCOM is enabled requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.CTRLB=1 until synchronization is complete. If CTRLB is written while SYNCBUSY.CTRLB=1, an APB error will be generated.

| Value | Description                        |

|-------|------------------------------------|

| 0     | CTRLB synchronization is not busy. |

| 1     | CTRLB synchronization is busy.     |

## **Bit 1 – ENABLE** SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.ENABLE=1 until synchronization is complete.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

## Bit 0 – SWRST Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.SWRST=1 until synchronization is complete.

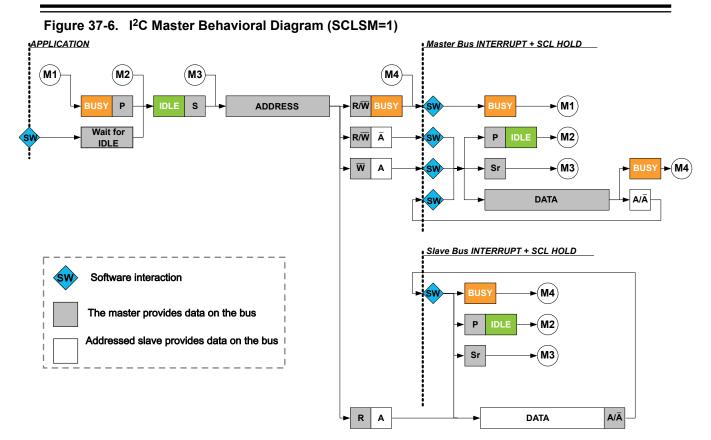

# SAM L10/L11 Family SERCOM I2C – SERCOM Inter-Integrated Circ...

## 37.6.2.4.1 Master Clock Generation

The SERCOM peripheral supports several I<sup>2</sup>C bidirectional modes:

- Standard mode (*Sm*) up to 100 kHz

- Fast mode (*Fm*) up to 400 kHz

- Fast mode Plus (*Fm*+) up to 1 MHz

- High-speed mode (Hs) up to 3.4 MHz

The Master clock configuration for *Sm*, *Fm*, and *Fm*+ are described in Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus). For *Hs*, refer to Master Clock Generation (High-Speed Mode).

## Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus)

In I<sup>2</sup>C *Sm, Fm*, and *Fm*+ mode, the Master clock (SCL) frequency is determined as described in this section:

The low (T<sub>LOW</sub>) and high (T<sub>HIGH</sub>) times are determined by the Baud Rate register (BAUD), while the rise (T<sub>RISE</sub>) and fall (T<sub>FALL</sub>) times are determined by the bus topology. Because of the wired-AND logic of the bus, T<sub>FALL</sub> will be considered as part of T<sub>LOW</sub>. Likewise, T<sub>RISE</sub> will be in a state between T<sub>LOW</sub> and T<sub>HIGH</sub> until a high state has been detected.

### 37.8.8 Address

| Name:     | ADDR                                   |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31       | 30  | 29  | 28            | 27  | 26            | 25        | 24     |  |

|--------|----------|-----|-----|---------------|-----|---------------|-----------|--------|--|

|        |          |     |     |               |     | ADDRMASK[9:7] |           |        |  |

| Access |          |     |     | •             |     | R/W           | R/W       | R/W    |  |

| Reset  |          |     |     |               |     | 0             | 0         | 0      |  |

|        |          |     |     |               |     |               |           |        |  |

| Bit    | 23       | 22  | 21  | 20            | 19  | 18            | 17        | 16     |  |

|        |          |     |     | ADDRMASK[6:0] |     |               |           |        |  |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W           | R/W       |        |  |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0             | 0         |        |  |

|        |          |     |     |               |     |               |           |        |  |

| Bit    | 15       | 14  | 13  | 12            | 11  | 10            | 9         | 8      |  |

|        | TENBITEN |     |     |               |     |               | ADDR[9:7] |        |  |

| Access | R/W      |     |     |               |     | R/W           | R/W       | R/W    |  |

| Reset  | 0        |     |     |               |     | 0             | 0         | 0      |  |

|        |          |     |     |               |     |               |           |        |  |

| Bit    | 7        | 6   | 5   | 4             | 3   | 2             | 1         | 0      |  |

|        |          |     |     | ADDR[6:0]     |     |               |           | GENCEN |  |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W           | R/W       | R/W    |  |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0             | 0         | 0      |  |

|        |          |     |     |               |     |               |           |        |  |

## Bits 26:17 – ADDRMASK[9:0] Address Mask

These bits act as a second address match register, an address mask register or the lower limit of an address range, depending on the CTRLB.AMODE setting.

#### **Bit 15 – TENBITEN** Ten Bit Addressing Enable

| Value | Description                          |

|-------|--------------------------------------|

| 0     | 10-bit address recognition disabled. |

| 1     | 10-bit address recognition enabled.  |

#### Bits 10:1 - ADDR[9:0] Address

These bits contain the I<sup>2</sup>C slave address used by the slave address match logic to determine if a master has addressed the slave.

When using 7-bit addressing, the slave address is represented by ADDR[6:0].

When using 10-bit addressing (ADDR.TENBITEN=1), the slave address is represented by ADDR[9:0]

When the address match logic detects a match, INTFLAG.AMATCH is set and STATUS.DIR is updated to indicate whether it is a read or a write transaction.

#### Bit 0 – GENCEN General Call Address Enable

A general call address is an address consisting of all-zeroes, including the direction bit (master write).

© 2018 Microchip Technology Inc.

#### 37.10.4 Interrupt Enable Clear

Name:INTENCLROffset:0x14Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7     | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|-------|---|---|---|---|---|-----|-----|

|        | ERROR |   |   |   |   |   | SB  | MB  |

| Access | R/W   |   |   |   |   |   | R/W | R/W |

| Reset  | 0     |   |   |   |   |   | 0   | 0   |

## Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

**Bit 1 – SB** Slave on Bus Interrupt Enable Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Slave on Bus Interrupt Enable bit, which disables the Slave on Bus interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Slave on Bus interrupt is disabled. |

| 1     | The Slave on Bus interrupt is enabled.  |

Bit 0 – MB Master on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Master on Bus Interrupt Enable bit, which disables the Master on Bus interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Master on Bus interrupt is disabled. |

| 1     | The Master on Bus interrupt is enabled.  |

#### 38.7.3.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x0A    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

|        |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

#### **Bit 4 – MCx** Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

#### Bit 1 – ERR Error Interrupt Flag

This flag is set when a new capture occurs on a channel while the corresponding Match or Capture Channel x interrupt flag is set, in which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Error interrupt flag.

#### Bit 0 – OVF Overflow Interrupt Flag

This flag is set on the next CLK\_TC\_CNT cycle after an overflow condition occurs, and will generate an interrupt request if INTENCLR.OVF or INTENSET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

### 41.8.3 Reference Control

| Name:     | REFCTRL                                |

|-----------|----------------------------------------|

| Offset:   | 0x02                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 7       | 6 | 5 | 4 | 3   | 2     | 1       | 0   |

|--------|---------|---|---|---|-----|-------|---------|-----|

|        | REFCOMP |   |   |   |     | REFSE | EL[3:0] |     |

| Access | R/W     |   |   |   | R/W | R/W   | R/W     | R/W |

| Reset  | 0       |   |   |   | 0   | 0     | 0       | 0   |

#### Bit 7 – REFCOMP Reference Buffer Offset Compensation Enable

The gain error can be reduced by enabling the reference buffer offset compensation. This will increase the start-up time of the reference.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Reference buffer offset compensation is disabled. |

| 1     | Reference buffer offset compensation is enabled.  |

## Bits 3:0 - REFSEL[3:0] Reference Selection

These bits select the reference for the ADC.

| Value | Name    | Description                                                                                      |

|-------|---------|--------------------------------------------------------------------------------------------------|

| 0x0   | INTREF  | Internal variable reference voltage, refer to the SUPC.VREF register for voltage reference value |

| x01   | INTVCC0 | 1/1.6 VDDANA                                                                                     |

| 0x2   | INTVCC1 | 1/2 VDDANA (only for VDDANA > 2.0V)                                                              |

| 0x3   | VREFA   | External reference                                                                               |

| 0x4   | VREFB   | External reference                                                                               |

| 0x5   | INTVCC2 | VDDANA                                                                                           |

| 0x6 - |         | Reserved                                                                                         |

| 0xF   |         |                                                                                                  |

# SAM L10/L11 Family

# **OPAMP – Operational Amplifier Controller**

| Value | OPAMPx  | Name      | Description                 |

|-------|---------|-----------|-----------------------------|

| 0x0   | x=0,1,2 | OAxPOS    | OPAMPx Positive Input       |

| 0x1   | x=0,1,2 | OAxTAP    | OPAMPx Resistor Ladder Taps |

| 0x2   | x=0,1,2 | REFERENCE | REFERENCE[DAC/REFBUF]       |

| 0x3   | x=0,1,2 | GND       | Ground                      |

| 0x4   | x=0     | Reserved  |                             |

|       | x=1     | OA0OUT    | OPAMP0 output               |

|       | x=2     | OA1OUT    | OPAMP1 output               |

| 0x5   | x=0,1   | Reserved  |                             |

|       | x=2     | OA0POS    | OPAMP0 Positive Input       |

| 0x6   | x=0,1   | Reserved  |                             |

|       | x=2     | OA1POS    | OPAMP1 Positive Input       |

| 0x7   | x=0,1   | Reserved  |                             |

|       | x=2     | OA0TAP    | OPAMP0 Resistor Ladder Taps |

| 0x8   | x=0,1   | Reserved  |                             |

|       | x=2     | RES3TAP   |                             |

## Bits 15:13 – POTMUX[2:0] Potentiometer selection

Resistor selection bits control a numeric potentiometer with eight fixed values.

| Value | R1  | R2  |

|-------|-----|-----|

| 0x0   | 14R | 2R  |

| 0x1   | 12R | 4R  |

| 0x2   | 8R  | 8R  |

| 0x3   | 6R  | 10R |

| 0x4   | 4R  | 12R |

| 0x5   | 3R  | 13R |

| 0x6   | 2R  | 14R |

| 0x7   | R   | 15R |

## Bits 12:10 – RES1MUX[2:0] Resistor 1 Mux

These bits select the connection of R1 resistor of the potentiometer.

| Value | OPAMPx  | Name   | Description           |

|-------|---------|--------|-----------------------|

| 0x0   | x=0,1,2 | OAxPOS | OPAMPx Positive Input |

| 0x1   | x=0,1,2 | OAxNEG | OPAMPx Negative Input |

# SAM L10/L11 Family

# Acronyms and Abbreviations

| Abbreviation       | Description                                                            |

|--------------------|------------------------------------------------------------------------|

| SWD                | Serial Wire Debug                                                      |

| тс                 | Timer/Counter                                                          |

| TRNG               | True Random Number Generator                                           |

| ТХ                 | Transmitter/Transmit                                                   |

| ULP                | Ultra Low-Power                                                        |

| USART              | Universal Synchronous and Asynchronous Serial Receiver and Transmitter |

| V <sub>DD</sub>    | Common voltage to be applied to VDDIO and VDDANA                       |

| V <sub>DDIO</sub>  | Digital Supply Voltage                                                 |

| V <sub>DDANA</sub> | Analog Supply Voltage                                                  |

| VREF               | Voltage Reference                                                      |

| WDT                | Watchdog Timer                                                         |

| XOSC               | Crystal Oscillator                                                     |