#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e14a-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

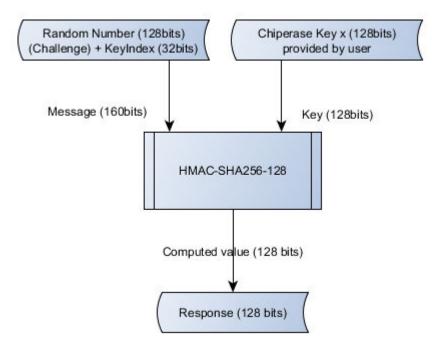

### 14.4.5.7 Random Session Key Generation (CMD\_DCEK) - SAM L11 only

This command allows using a challenge-response scheme to prevent exposure of the keys in clear text on the debugger communication lines.

The different keys sent by the debugger during the Boot ROM for Chip Erase (CMD\_CEx) and CRC (CMD\_CRC) commands execution are:

- CRCKEY for CMD\_CRC command

- CEKEYx for CMD\_CEx commands

**Note:** The CMD\_DCEK command has no effect on the SAM L10, the key derivation will not be enabled.

The random challenge value is generated using the TRNG of the device. It is generated once the CMD\_DCEK is received and communicated to the debugger.

The next CMD\_CEx or CMD\_CRC commands will expect the key value to be replaced by the computed response corresponding to the challenge.

The challenge value is valid only for the next CMD\_CEx/ CMD\_CRC command.

Before sending a new CMD\_CEx/ CMD\_CRC command, a CMD\_DCEK shall be used to re-enable the challenge-response scheme a get a new challenge value.

On the debugger side, the response shall be computed using the following algorithm:

### Figure 14-13. Debugger Algorithm

Where KeyIndex is:

- 0 for ChipErase\_NS

- 1 for ChipErase\_S

- 2 for ChipErase\_ALL

- 3 for CRC Command

### Note:

### 18.6.3.3 Selecting the Clock Source for a Peripheral

When changing a peripheral clock source by writing to PCHCTRLm.GEN, the peripheral clock must be disabled before re-enabling it with the new clock source setting. This prevents glitches during the transition:

- 1. Disable the Peripheral Channel by writing PCHCTRLm.CHEN=0

- 2. Assert that PCHCTRLm.CHEN reads '0'

- 3. Change the source of the Peripheral Channel by writing PCHCTRLm.GEN

- 4. Re-enable the Peripheral Channel by writing PCHCTRLm.CHEN=1

# Related Links 18.8.4 PCHCTRLm

### 18.6.3.4 Configuration Lock

The peripheral clock configuration can be locked for further write accesses by setting the Write Lock bit in the Peripheral Channel Control register PCHCTRLm.WRTLOCK=1). All writing to the PCHCTRLm register will be ignored. It can only be unlocked by a Power Reset.

The Generator source of a locked Peripheral Channel will be locked, too: The corresponding GENCTRLn register is locked, and can be unlocked only by a Power Reset.

There is one exception concerning the Generator 0. As it is used as GCLK\_MAIN, it cannot be locked. It is reset by any Reset and will start up in a known configuration. The software reset (CTRLA.SWRST) can not unlock the registers.

In case of an external Reset, the Generator source will be disabled. Even if the WRTLOCK bit is written to '1' the peripheral channels are disabled (PCHCTRLm.CHEN set to '0') until the Generator source is enabled again. Then, the PCHCTRLm.CHEN are set to '1' again.

# **Related Links**

18.8.1 CTRLA

### 18.6.4 Additional Features

### 18.6.4.1 Peripheral Clock Enable after Reset

The Generic Clock Controller must be able to provide a generic clock to some specific peripherals after a Reset. That means that the configuration of the Generators and Peripheral Channels after Reset is device-dependent.

Refer to GENCTRLn.SRC for details on GENCTRLn reset.

Refer to PCHCTRLm.SRC for details on PCHCTRLm reset.

### 18.6.5 Sleep Mode Operation

### 18.6.5.1 SleepWalking

The GCLK module supports the SleepWalking feature.

If the system is in a sleep mode where the Generic Clocks are stopped, a peripheral that needs its clock in order to execute a process must request it from the Generic Clock Controller.

The Generic Clock Controller receives this request, determines which Generic Clock Generator is involved and which clock source needs to be awakened. It then wakes up the respective clock source, enables the Generator and Peripheral Channel stages successively, and delivers the clock to the peripheral.

© 2018 Microchip Technology Inc.

The low-power regulator starts again and the PDSW power domain is set back to retention state by the PM. During this dynamic SleepWalking period, the CPU is still sleeping.

*Exiting standby mode*: during the dynamic SleepWalking sequence, if conditions are met, the AC module generates an interrupt to wake up the device.

### **Related Links**

27. RTC – Real-Time Counter

33. EVSYS – Event System

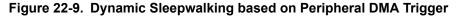

### 22.6.6.2 Dynamic SleepWalking Based on Peripheral DMA Trigger

To enable this advanced feature, the Dynamic Power Gating for Power Domain SW bit in the Standby Configuration register (STDBYCFG.DPGPDSW) have to be written to '1'.

When in retention state, the power domain PDSW (containing the DMAC) can be automatically set to active state if the PM detects a valid DMA trigger that is coming from a peripheral located in PDAO. A peripheral DMA trigger is valid if the corresponding DMA channel is enabled and its Run in Standby bit (RUNSTDBY) is written to '1'.

This is illustrated in the following example:

# SAM L10/L11 Family OSCCTRL – Oscillators Controller

### 23.8.6 External Multipurpose Crystal Oscillator (XOSC) Control

| Name:     | XOSCCTRL             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x0080               |

| Property: | PAC Write-Protection |

| Bit    | 15       | 14       | 13      | 12     | 11    | 10     | 9         | 8   |

|--------|----------|----------|---------|--------|-------|--------|-----------|-----|

|        |          | START    | UP[3:0] |        | AMPGC |        | GAIN[2:0] |     |

| Access | R/W      | R/W      | R/W     | R/W    | R/W   | R/W    | R/W       | R/W |

| Reset  | 0        | 0        | 0       | 0      | 0     | 0      | 0         | 0   |

|        |          |          |         |        |       |        |           |     |

| Bit    | 7        | 6        | 5       | 4      | 3     | 2      | 1         | 0   |

|        | ONDEMAND | RUNSTDBY |         | SWBACK | CFDEN | XTALEN | ENABLE    |     |

| Access | R/W      | R/W      | •       | R/W    | R/W   | R/W    | R/W       |     |

| Reset  | 1        | 0        |         | 0      | 0     | 0      | 0         |     |

### Bits 15:12 - STARTUP[3:0] Start-Up Time

These bits select start-up time for the oscillator.

The OSCULP32K oscillator is used to clock the start-up counter.

### Table 23-5. Start-Up Time for External Multipurpose Crystal Oscillator

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0x0          | 1                                   | 3                              | 31                                  |

| 0x1          | 2                                   | 3                              | 61                                  |

| 0x2          | 4                                   | 3                              | 122                                 |

| 0x3          | 8                                   | 3                              | 244                                 |

| 0x4          | 16                                  | 3                              | 488                                 |

| 0x5          | 32                                  | 3                              | 977                                 |

| 0x6          | 64                                  | 3                              | 1953                                |

| 0x7          | 128                                 | 3                              | 3906                                |

| 0x8          | 256                                 | 3                              | 7813                                |

| 0x9          | 512                                 | 3                              | 15625                               |

| 0xA          | 1024                                | 3                              | 31250                               |

| 0xB          | 2048                                | 3                              | 62500µs                             |

| 0xC          | 4096                                | 3                              | 125000                              |

| 0xD          | 8192                                | 3                              | 250000                              |

#### 25.8.2 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x04                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 31 | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|----|----|----|----|------------|----------|----------|----------|

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 23 | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 15 | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |    |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |    |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |    |    |    |    | 0          | 0        |          | 0        |

|        |    |    |    |    |            |          |          |          |

| Bit    | 7  | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |    |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access |    |    |    |    |            | R/W      | R/W      | R/W      |

| Reset  |    |    |    |    |            | 0        | 0        | 0        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit is set on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY).

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Low Power Ready interrupt is disabled.                                                                                     |

| 1     | The Low Power Ready interrupt is enabled and an interrupt request will be generated when the ULPVREFRDY Interrupt Flag is set. |

Bit 10 – VCORERDY VDDCORE Voltage Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the VDDCORE Ready Interrupt Enable bit, which enables the VDDCORE Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The VDDCORE Ready interrupt is disabled.                                                                                   |

| 1     | The VDDCORE Ready interrupt is enabled and an interrupt request will be generated when the VCORERDY Interrupt Flag is set. |

### 25.8.3 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x08Reset:x initially determined from NVM User Row after resetProperty:-

| Bit    | 31      | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|---------|----|----|----|------------|----------|----------|----------|

|        |         |    |    |    |            |          |          |          |

| Access |         |    |    |    |            |          |          |          |

| Reset  |         |    |    |    |            |          |          |          |

|        |         |    |    |    |            |          |          |          |

| Bit    | 23      | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |         |    |    |    |            |          |          |          |

| Access |         |    |    |    |            |          |          |          |

| Reset  |         |    |    |    |            |          |          |          |

|        |         |    |    |    |            |          |          |          |

| Bit    | 15      | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |         |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |         |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |         |    |    |    | 0          | 0        |          | 1        |

|        |         |    |    |    |            |          |          |          |

| Bit    | 7       | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |         |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access | <u></u> | •  | •  |    | •          | R/W      | R/W      | R/W      |

| Reset  |         |    |    |    |            | 0        | 0        | x        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit will clear on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY) and will generate an interrupt request if INTENSET.ULPVREFRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the ULPVREFRDY interrupt flag.

Bit 10 – VCORERDY VDDCORE Voltage Ready

This flag is cleared by writing a '1 to it.

This flag is set on a zero-to-one transition of the VDDCORE Ready bit in the Status register (STATUS.VCORERDY) and will generate an interrupt request if INTENSET.VCORERDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the VCORERDY interrupt flag.

Bit 8 – VREGRDY Voltage Regulator Ready

This flag is cleared by writing a '1' to it.

© 2018 Microchip Technology Inc.

# RTC – Real-Time Counter

# Bit 14 – TAMPEREO Tamper Event Output Enable

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Tamper event output is disabled, and will not be generated                    |

| 1     | Tamper event output is enabled, and will be generated for every tamper input. |

### Bit 8 – ALARMEO Alarm 0 Event Output Enable

| Valu | e Description                                                           |

|------|-------------------------------------------------------------------------|

| 0    | Alarm 0 event is disabled and will not be generated.                    |

| 1    | Alarm 0 event is enabled and will be generated for every compare match. |

### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PEREOn Periodic Interval n Event Output Enable [n = 7..0]

| Value | Description                                                      |

|-------|------------------------------------------------------------------|

| 0     | Periodic Interval n event is disabled and will not be generated. |

| 1     | Periodic Interval n event is enabled and will be generated.      |

# SAM L10/L11 Family

# PORT - I/O Pin Controller

|                | <b>,</b> |        |        |                       |

|----------------|----------|--------|--------|-----------------------|

| EVACT0         | EVACT1   | EVACT2 | EVACT3 | Executed Event Action |

| SET            | SET      | SET    | SET    | SET                   |

| CLR            | CLR      | CLR    | CLR    | CLR                   |

| All Other Comb | inations | TGL    |        |                       |

Table 32-3. Priority on Simultaneous SET/CLR/TGL Event Actions

Be careful when the event is output to pin. Due to the fact the events are received asynchronously, the I/O pin may have unpredictable levels, depending on the timing of when the events are received. When several events are output to the same pin, the lowest event line will get the access. All other events will be ignored.

### **Related Links**

33. EVSYS - Event System

## 32.6.6 PORT Access Priority

The PORT is accessed by different systems:

- The ARM<sup>®</sup> CPU through the ARM<sup>®</sup> single-cycle I/O port (IOBUS)

- The ARM<sup>®</sup> CPU through the high-speed matrix and the AHB/APB bridge (APB)

- EVSYS through four asynchronous input events

The following priority is adopted:

- 1. ARM<sup>®</sup> CPU IOBUS (No wait tolerated)

- 2. APB

- 3. EVSYS input events

For input events that require different actions on the same I/O pin, refer to 32.6.5 Events.

Important: Only EVSYS channel 0 to 3 can be configured as synchronous or resynchronized.

### **Related Links**

19.6.2.6 Peripheral Clock Masking18. GCLK - Generic Clock Controller

### 33.4.4 DMA

Not applicable.

### 33.4.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the EVSYS interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

### 33.4.6 Events

Not applicable.

### 33.4.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging.

### 33.4.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except for the following:

- Channel Pending Interrupt (INTPEND)

- Channel n Interrupt Flag Status and Clear (CHINTFLAGn)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

Write-protection does not apply for accesses through an external debugger.

### 33.4.9 SAM L11 TrustZone Specific Register Access Protection

When the EVSYS is not PAC secured, non-secure and secure code can both access all functionalities. When the EVSYS is PAC secured, all registers are by default available in the secure alias only.

A PAC secured EVSYS can open up individual event channels and event users for non-secure access. This is done using the NONSECCHAN and NONSECUSER registers. When a channel or event user has been configured as non-secure, it can be handled from non-secure code using the EVSYS module non-secure alias. Since only Secured code has the rights to modify the NONSECCHAN and NONSECUSER registers, an interrupt-based mechanism has been added to let Non Secured code know when these registers have been changed by Secured code. A single flag called NSCHK in the INTFLAG register will rise should changes, conditioned by the NSCHKCHAN and NSCHKUSER registers, occur in the NONSECCHAN and NONSECUSER registers.

Note: Refer to the Mix-Secure Peripherals section in the SAM L11 Security Features chapter.

### 33.4.10 Analog Connections

Not applicable.

# 33.7.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection , Secure

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | SWRST |

| Access |   |   |   |   |   |   |   | W/-/W |

| Reset  |   |   |   |   |   |   |   | 0     |

### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the EVSYS to their initial state.

**Note:** Before applying a Software Reset it is recommended to disable the event generators.

# 35. SERCOM USART - SERCOM Synchronous and Asynchronous Receiver and Transmitter

# 35.1 Overview

The Universal Synchronous and Asynchronous Receiver and Transmitter (USART) is one of the available modes in the Serial Communication Interface (SERCOM).

The USART uses the SERCOM transmitter and receiver, see 35.3 Block Diagram. Labels in uppercase letters are synchronous to CLK\_SERCOMx\_APB and accessible for CPU. Labels in lowercase letters can be programmed to run on the internal generic clock or an external clock.

The transmitter consists of a single write buffer, a shift register, and control logic for different frame formats. The write buffer support data transmission without any delay between frames. The receiver consists of a two-level or four-level receive buffer and a shift register. Status information of the received data is available for error checking. Data and clock recovery units ensure robust synchronization and noise filtering during asynchronous data reception.

### **Related Links**

34. SERCOM - Serial Communication Interface

# 35.2 USART Features

- Full-duplex operation

- Asynchronous (with clock reconstruction) or synchronous operation

- Internal or external clock source for asynchronous and synchronous operation

- Baud-rate generator

- Supports serial frames with 5, 6, 7, 8 or 9 data bits and 1 or 2 stop bits

- Odd or even parity generation and parity check

- Selectable LSB- or MSB-first data transfer

- Buffer overflow and frame error detection

- Noise filtering, including false start-bit detection and digital low-pass filter

- Collision detection

- Can operate in all sleep modes

- Operation at speeds up to half the system clock for internally generated clocks

- Operation at speeds up to the system clock for externally generated clocks

- RTS and CTS flow control

- IrDA modulation and demodulation up to 115.2kbps

- LIN slave support

- Auto-baud and break character detection

- ISO 7816 T=0 or T=1 protocols for Smart Card interfacing

- RS485 Support

- Start-of-frame detection

- Two- or Four-Level Receive Buffer

- Can work with DMA

### 35.8.4 Baud

| Name:     | BAUD                                   |

|-----------|----------------------------------------|

| Offset:   | 0x0C                                   |

| Reset:    | 0x0000                                 |

| Property: | Enable-Protected, PAC Write-Protection |

| Bit    | 15         | 14  | 13  | 12  | 11  | 10  | 9   | 8   |  |  |  |

|--------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

|        | BAUD[15:8] |     |     |     |     |     |     |     |  |  |  |

| Access | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Reset  | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

|        |            |     |     |     |     |     |     |     |  |  |  |

| Bit    | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|        | BAUD[7:0]  |     |     |     |     |     |     |     |  |  |  |

| Access | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Reset  | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

### Bits 15:0 - BAUD[15:0] Baud Value

Arithmetic Baud Rate Generation (CTRLA.SAMPR[0]=0):

These bits control the clock generation, as described in the SERCOM Baud Rate section.

If Fractional Baud Rate Generation (CTRLA.SAMPR[0]=1) bit positions 15 to 13 are replaced by FP[2:0] Fractional Part:

### • Bits 15:13 - FP[2:0]: Fractional Part

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

### • Bits 12:0 - BAUD[12:0]: Baud Value

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

# **Related Links**

34.6.2.3 Clock Generation – Baud-Rate Generator34.6.2.3.1 Asynchronous Arithmetic Mode BAUD Value Selection

# SAM L10/L11 Family

# SERCOM SPI – SERCOM Serial Peripheral Interface

| AMODE[1:0] | Name    | Description                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------|

| 0x0        | MASK    | ADDRMASK is used as a mask to the ADDR register                                                               |

| 0x1        | 2_ADDRS | The slave responds to the two unique addresses in ADDR and ADDRMASK                                           |

| 0x2        | RANGE   | The slave responds to the range of addresses between and including ADDR and ADDRMASK. ADDR is the upper limit |

| 0x3        | -       | Reserved                                                                                                      |

# Bit 13 – MSSEN Master Slave Select Enable

This bit enables hardware slave select  $(\overline{SS})$  control.

| Value | Description                      |

|-------|----------------------------------|

| 0     | Hardware SS control is disabled. |

| 1     | Hardware SS control is enabled.  |

# Bit 9 – SSDE Slave Select Low Detect Enable

This bit enables wake up when the slave select  $(\overline{SS})$  pin transitions from high to low.

| Value | Description                  |

|-------|------------------------------|

| 0     | SS low detector is disabled. |

| 1     | SS low detector is enabled.  |

## Bit 6 – PLOADEN Slave Data Preload Enable

Setting this bit will enable preloading of the slave shift register when there is no transfer in progress. If the SS line is high when DATA is written, it will be transferred immediately to the shift register.

### Bits 2:0 – CHSIZE[2:0] Character Size

| CHSIZE[2:0] | Name | Description |

|-------------|------|-------------|

| 0x0         | 8BIT | 8 bits      |

| 0x1         | 9BIT | 9 bits      |

| 0x2-0x7     | -    | Reserved    |

## 36.8.9 Address

| Name:     | ADDR                                   |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31  | 30  | 29  | 28    | 27       | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|----------|-----|-----|-----|

|        |     |     |     |       |          |     |     |     |

| Access |     |     |     |       |          |     |     |     |

| Reset  |     |     |     |       |          |     |     |     |

|        |     |     |     |       |          |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19       | 18  | 17  | 16  |

|        |     |     |     | ADDRM | ASK[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

|        |     |     |     |       |          |     |     |     |

| Access |     |     |     |       |          |     |     |     |

| Reset  |     |     |     |       |          |     |     |     |

|        |     |     |     |       |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

|        |     |     |     | ADD   | R[7:0]   |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

# Bits 23:16 – ADDRMASK[7:0] Address Mask

These bits hold the address mask when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

### Bits 7:0 – ADDR[7:0] Address

These bits hold the address when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

# SAM L10/L11 Family

# SERCOM I2C – SERCOM Inter-Integrated Circ...

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Automatic transfer length disabled. |

| 1     | Automatic transfer length enabled.  |

### Bits 10:0 – ADDR[10:0] Address

When ADDR is written, the consecutive operation will depend on the bus state:

UNKNOWN: INTFLAG.MB and STATUS.BUSERR are set, and the operation is terminated.

BUSY: The I<sup>2</sup>C master will await further operation until the bus becomes IDLE.

IDLE: The I<sup>2</sup>C master will issue a start condition followed by the address written in ADDR. If the address is acknowledged, SCL is forced and held low, and STATUS.CLKHOLD and INTFLAG.MB are set.

OWNER: A repeated start sequence will be performed. If the previous transaction was a read, the acknowledge action is sent before the repeated start bus condition is issued on the bus. Writing ADDR to issue a repeated start is performed while INTFLAG.MB or INTFLAG.SB is set.

STATUS.BUSERR, STATUS.ARBLOST, INTFLAG.MB and INTFLAG.SB will be cleared when ADDR is written.

The ADDR register can be read at any time without interfering with ongoing bus activity, as a read access does not trigger the master logic to perform any bus protocol related operations.

The I<sup>2</sup>C master control logic uses bit 0 of ADDR as the bus protocol's read/write flag (R/W); 0 for write and 1 for read.

### 38.7.1.2 Control B Clear

Name:CTRLBCLROffset:0x04Reset:0x00Property:PAC Write-Protection, Read-Synchronized, Write-Synchronized

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

| Bit    | 7   | 6        | 5   | 4 | 3 | 2       | 1    | 0   |

|--------|-----|----------|-----|---|---|---------|------|-----|

|        |     | CMD[2:0] |     |   |   | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W |   |   | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   |   |   | 0       | 0    | 0   |

### Bits 7:5 – CMD[2:0] Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a '1' to any of these bits will clear the pending command.

## Bit 2 – ONESHOT One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will disable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

### Bit 1 – LUPD Lock Update

This bit controls the update operation of the TC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

This bit has no effect when input capture operation is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the LUPD bit.

| Value | Description                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------|

| 0     | The CCBUFx and PERBUF buffer registers value are copied into CCx and PER registers on                                |

|       | hardware update condition.                                                                                           |

| 1     | The CCBUFx and PERBUF buffer registers value are not copied into CCx and PER registers on hardware update condition. |

## Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

### 38.7.2.9 Waveform Generation Control

Name:WAVEOffset:0x0CReset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1            | 0   |

|--------|---|---|---|---|---|---|--------------|-----|

|        |   |   |   |   |   |   | WAVEGEN[1:0] |     |

| Access |   |   |   |   |   |   | R/W          | R/W |

| Reset  |   |   |   |   |   |   | 0            | 0   |

### Bits 1:0 – WAVEGEN[1:0] Waveform Generation Mode

These bits select the waveform generation operation. They affect the top value, as shown in 38.6.2.6.1 Waveform Output Operations. They also control whether frequency or PWM waveform generation should be used. The waveform generation operations are explained in 38.6.2.6.1 Waveform Output Operations.

These bits are not synchronized.

| Value | Name | Operation        | Top Value              | Output<br>Waveform<br>on Match | Output Waveform<br>on Wraparound |

|-------|------|------------------|------------------------|--------------------------------|----------------------------------|

| 0x0   | NFRQ | Normal frequency | PER <sup>1</sup> / Max | Toggle                         | No action                        |

| 0x1   | MFRQ | Match frequency  | CC0                    | Toggle                         | No action                        |

| 0x2   | NPWM | Normal PWM       | PER <sup>1</sup> / Max | Set                            | Clear                            |

| 0x3   | MPWM | Match PWM        | CC0                    | Set                            | Clear                            |

1) This depends on the TC mode: In 8-bit mode, the top value is the Period Value register (PER). In 16and 32-bit mode it is the respective MAX value.

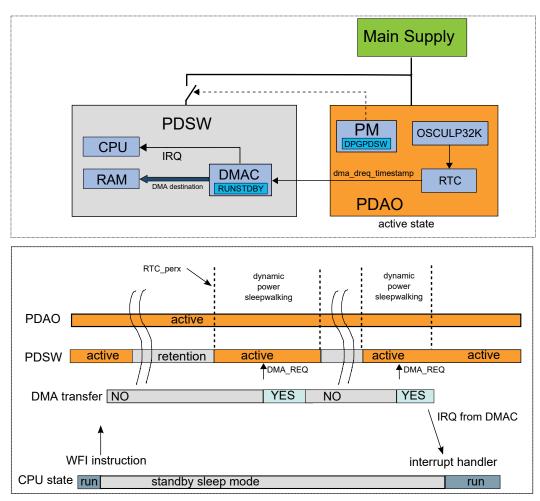

### Figure 40-5. Linked LUT Input Selection

### Internal Events Inputs Selection (EVENT)

Asynchronous events from the Event System can be used as input selection, as shown in Figure 40-6. For each LUT, one event input line is available and can be selected on each LUT input. Before enabling the event selection by writing LUTCTRLx.INSELy=EVENT, the Event System must be configured first.

By default CCL includes an edge detector. When the event is received, an internal strobe is generated when a rising edge is detected. The pulse duration is one GCLK\_CCL clock cycle. Writing the LUTCTRLx.INSELy=ASYNCEVENT will disable the edge detector. In this case, it is possible to combine an asynchronous event input with any other input source. This is typically useful with event levels inputs (external IO pin events, as example). The following steps ensure proper operation:

- 1. Enable the GCLK\_CCL clock.

- 2. Configure the Event System to route the event asynchronously.

- 3. Select the event input type (LUTCTRLx.INSEL).

- 4. If a strobe must be generated on the event input falling edge, write a '1' to the Inverted Event Input Enable bit in LUT Control register (LUTCTRLx.INVEI).

- 5. Enable the event input by writing the Event Input Enable bit in LUT Control register (LUTCTRLx.LUTEI) to '1'.

# SAM L10/L11 Family

# 125°C Electrical Characteristics

| Symbol                              | Parameter                                     | Conditions                                                                               | Min.  | Тур.  | Max.  | Units |  |  |  |

|-------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

|                                     |                                               | Calibrated against a 4/8/12/16 MHz reference                                             |       | 8.00  | 8.08  |       |  |  |  |

|                                     |                                               |                                                                                          |       | 12.00 | 12.12 |       |  |  |  |

|                                     |                                               |                                                                                          | 15.84 | 16.00 | 16.16 |       |  |  |  |

| TempDrift                           | Freq vs. temperature drift                    | VDD=3.3V over temperature<br>[-40°C-125°C], versus calibration<br>reference at 25°C      | -5    |       | 5     | %     |  |  |  |

| SupplyDrift                         | Freq vs. supply drift                         | Temperature =25°C over voltage<br>[1.62V-3.63V], versus calibration<br>reference at 3.3V | -1.5  |       | 1.5   |       |  |  |  |

| T <sub>WUP</sub> <sup>(2)</sup>     | Wake up time - 1st clock edge<br>after enable | F <sub>OUT</sub> = 4MHz                                                                  | -     | 0.13  | 0.32  | μs    |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 8MHz                                                                  | -     | 0.13  | 0.31  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 12MHz                                                                 | -     | 0.13  | 0.31  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 16MHz                                                                 | -     | 0.13  | 0.31  |       |  |  |  |

| T <sub>STARTUP</sub> <sup>(2)</sup> | Startup time                                  | F <sub>OUT</sub> = 4MHz                                                                  | -     | 1.16  | 2.96  | μs    |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 8MHz                                                                  | -     | 1.29  | 2.74  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 12MHz                                                                 | -     | 1.34  | 2.95  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 16MHz                                                                 | -     | 1.39  | 3.11  |       |  |  |  |

| Duty <sup>(1)</sup>                 | Duty Cycle                                    | -                                                                                        | 45    | 50    | 55    | %     |  |  |  |

### Note:

- 1. These values are based on simulation. They are not covered by production test limits or characterization.

- 2. These values are based on characterization. These values are not covered in test limits in production.

# Table 47-22. Power Consumption

| Symbol          | Parameter   | Conditions                                        | Та                    | Min. | Тур. | Max. | Units |

|-----------------|-------------|---------------------------------------------------|-----------------------|------|------|------|-------|

| I <sub>DD</sub> | consumption | F <sub>out</sub> =4MHz,<br>V <sub>CC</sub> =3.3V  | Max.125°C<br>Typ.25°C | -    | 73   | 370  | μΑ    |

|                 |             | F <sub>out</sub> =8MHz,<br>V <sub>CC</sub> =3.3V  |                       | -    | 106  | 400  |       |

|                 |             | F <sub>out</sub> =12MHz,<br>V <sub>CC</sub> =3.3V |                       | -    | 135  | 425  |       |

|                 |             | F <sub>out</sub> =16MHz,<br>V <sub>CC</sub> =3.3V |                       | -    | 166  | 455  |       |