# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e14a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Peripherals Configuration Summary

| Peripheral Base<br>name address |            | IRQ line                                                                                                                                                                        | IRQ line AHB o |                     | AHB clock APB clo |                     | Generic<br>Clock                     | P/    | AC                              | Events                    |                                |                  | DMA                        | Power<br>domain |

|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|-------------------|---------------------|--------------------------------------|-------|---------------------------------|---------------------------|--------------------------------|------------------|----------------------------|-----------------|

|                                 |            |                                                                                                                                                                                 | Index          | Enabled at<br>Reset | Index             | Enabled at<br>Reset | Index                                | Index | Write<br>Protection<br>at Reset | User                      | Generator                      | Sleep<br>Walking | Index                      | Name            |

| AHB-APB<br>Bridge B             | 0x41000000 | -                                                                                                                                                                               | 1              | Y                   | -                 | -                   | -                                    | _     | -                               | -                         | _                              | N/A              | -                          | PDSW            |

| DSU                             | 0x41002000 | -                                                                                                                                                                               | 4              | Y                   | 1                 | Y                   | -                                    | 1     | Y                               | -                         | -                              | N/A              | 2-3:<br>DCC0-1             | PDSW            |

| NVMCTRL                         | 0x41004000 | 9: DONE,<br>PROGE,<br>LOCKE,<br>NVME,<br>KEYE,<br>NSCHK                                                                                                                         | 7              | Y                   | 2                 | Y                   | -                                    | 2     | N                               | 2: AUTOW                  | _                              | Y                | -                          | PDSW            |

| DMAC                            | 0x41006000 | 11: SUSP0,<br>TERR0,<br>TCMPL0<br>12: SUSP1,<br>TERR1,<br>TCMPL1<br>13: SUSP2,<br>TERR2,<br>TCMPL2<br>14: SUSP3,<br>TERR3,<br>TCMPL3<br>15:<br>SUSP4-7,<br>TERR4-7,<br>TCMPL4-7 | 3              | Y                   | _                 | _                   | _                                    | 3     | _                               | 7-10: CH0-3               | 25-28:<br>CH0-3                | Y                | _                          | PDSW            |

| HMATRIXH<br>S                   | 0x41008000 | -                                                                                                                                                                               | 5              | Y                   | -                 | -                   | -                                    | 4     | N                               | -                         | -                              | N/A              | -                          | PDSW            |

| AHB-APB<br>Bridge C             | 0x42000000 | —                                                                                                                                                                               | 2              | Y                   | _                 | -                   | -                                    | _     | -                               | -                         | _                              | N/A              | -                          | PDSW            |

| EVSYS                           | 0x42000000 | 16: EVD0,<br>OVR0<br>17: EVD1,<br>OVR1<br>18: EVD2,<br>OVR2<br>19: EVD3,<br>OVR3<br>20: NSCHK                                                                                   | _              | _                   | 0                 | Y                   | 6: CH0<br>7: CH1<br>8: CH2<br>9: CH3 | 0     | Ν                               | _                         | _                              | N/A              | _                          | PDSW            |

| SERCOM0                         | 0x42000400 | 22: bit 0<br>23: bit 1<br>24: bit 2<br>25: bit 3-6                                                                                                                              | _              | -                   | 1                 | Y                   | 11: CORE<br>10: SLOW                 | 1     | N                               | _                         | _                              | N/A              | 4: RX<br>5: TX             | PDSW            |

| SERCOM1                         | 0x42000800 | 26: bit 0<br>27: bit 1<br>28: bit 2<br>29: bit 3-6                                                                                                                              | _              | -                   | 2                 | Y                   | 12: CORE<br>10: SLOW                 | 2     | N                               | _                         | -                              | N/A              | 6: RX<br>7: TX             | PDSW            |

| SERCOM2                         | 0x42000C00 | 30: bit 0<br>31: bit 1<br>32: bit 2<br>33: bit 3-6                                                                                                                              | _              | -                   | 3                 | Y                   | 13: CORE<br>10: SLOW                 | 3     | N                               | -                         | _                              | N/A              | 8: RX<br>9: TX             | PDSW            |

| TC0                             | 0x42001000 | 34: ERR,<br>MC0, MC1,<br>OVF                                                                                                                                                    | -              | -                   | 4                 | Y                   | 14                                   | 4     | N                               | 11: EVU                   | 29: OVF<br>30-31:<br>MC0-1     | Y                | 10: OVF<br>11-12:<br>MC0-1 | PDSW            |

| TC1                             | 0x42001400 | 35: ERR,<br>MC0, MC1,<br>OVF                                                                                                                                                    | -              | -                   | 5                 | Y                   | 14                                   | 5     | N                               | 12: EVU                   | 32: OVF<br>33-34:<br>MC0-1     | Y                | 13: OVF<br>14-15:<br>MC0-1 | PDSW            |

| TC2                             | 0x42001800 | 36: ERR,<br>MC0, MC1,<br>OVF                                                                                                                                                    | —              | —                   | 6                 | Y                   | 15                                   | 6     | N                               | 13: EVU                   | 35: OVF<br>36-37:<br>MC0-1     | Y                | 16: OVF<br>17-18:<br>MC0-1 | PDSW            |

| ADC                             | 0x42001C00 | 37:<br>OVERRUN,<br>WINMON<br>38:RESRD<br>Y                                                                                                                                      | -              | -                   | 7                 | Y                   | 16                                   | 7     | N                               | 14: START<br>15<br>: SYNC | 38:<br>RESRDY<br>39:<br>WINMON | Y                | 19:<br>RESRDY              | PDSW            |

| DAC                             | 0x42002000 | 40:<br>UNDERRU                                                                                                                                                                  | -              | -                   | 8                 | Y                   | 18                                   | 8     | N                               | 18: START                 | 43: EMPTY                      | Y                | 20: EMPTY                  | PDSW            |

#### 15.7.12 Peripheral Non-Secure Status - Bridge A

| Name:     | NONSECA                                              |

|-----------|------------------------------------------------------|

| Offset:   | 0x54                                                 |

| Reset:    | x initially determined from NVM User Row after reset |

| Property: | Write-Secure                                         |

Important: This register is only available for SAM L11 and has no effect for SAM L10.

#### Reading NONSEC register returns peripheral security attribution status:

|                 | Value |       | Descriptio | n         |         |       |       |       |       |

|-----------------|-------|-------|------------|-----------|---------|-------|-------|-------|-------|

|                 | 0     |       | Peripheral | is secure | ed.     |       |       |       |       |

|                 | 1     |       | Peripheral | is non-se | cured.  |       |       |       |       |

| Bit             | 31    | 30    | 29         | )         | 28      | 27    | 26    | 25    | 24    |

| Access          |       |       |            |           |         |       |       |       |       |

| Reset           |       |       |            |           |         |       |       |       |       |

| Bit             | 23    | 22    | 2'         |           | 20      | 19    | 18    | 17    | 16    |

| Dit             | 25    |       | 2          |           | 20      | 15    | 10    | 17    | 10    |

| Access<br>Reset |       |       |            |           |         |       |       |       |       |

| Bit             | 15    | 14    | 13         | 5         | 12      | 11    | 10    | 9     | 8     |

|                 |       |       | A          | ;         | PORT    | FREQM | EIC   | RTC   | WDT   |

| Access          |       |       | R/R        | /R        | R/R/R   | R/R/R | R/R/R | R/R/R | R/R/R |

| Reset           |       |       | х          |           | x       | х     | х     | Х     | x     |

| Bit             | 7     | 6     | 5          |           | 4       | 3     | 2     | 1     | 0     |

|                 | GCLK  | SUPC  | COSC32     | CTRL C    | DSCCTRL | RSTC  | MCLK  | PM    | PAC   |

| Access          | R/R/R | R/R/F | R R/R      | /R        | R/R/R   | R/R/R | R/R/R | R/R/R | R/R/R |

| Reset           | x     | х     | х          |           | х       | x     | x     | x     | 0     |

#### Bit 13 – AC Peripheral AC Non-Secure

- Bit 12 PORT Peripheral PORT Non-Secure

- **Bit 11 FREQM** Peripheral FREQM Non-Secure

- Bit 10 EIC Peripheral EIC Non-Secure

- Bit 9 RTC Peripheral RTC Non-Secure

## **DSU - Device Service Unit**

| Offset | Name | Bit Pos. |      |          |        |               |  |  |  |

|--------|------|----------|------|----------|--------|---------------|--|--|--|

|        |      | 7:0      | CCLA | ASS[3:0] |        | PREAMBLE[3:0] |  |  |  |

| 0x1FF4 | CID1 | 15:8     |      |          |        |               |  |  |  |

| UXIFF4 | CID1 | 23:16    |      |          |        |               |  |  |  |

|        |      | 31:24    |      |          |        |               |  |  |  |

|        | CID2 | 7:0      |      |          | PREAME | BLEB2[7:0]    |  |  |  |

| 0x1FF8 |      | 15:8     |      |          |        |               |  |  |  |

| UXIFFO |      | 23:16    |      |          |        |               |  |  |  |

|        |      | 31:24    |      |          |        |               |  |  |  |

|        |      | 7:0      |      |          | PREAME | BLEB3[7:0]    |  |  |  |

| 0x1FFC | CID3 | 15:8     |      |          |        |               |  |  |  |

| UXIFFC | CIDS | 23:16    |      |          |        |               |  |  |  |

|        |      | 31:24    |      |          |        |               |  |  |  |

### 16.12 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 16.5.7 Register Access Protection.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 16.12.3 Status B

| Name:     | STATUSB              |

|-----------|----------------------|

| Offset:   | 0x0002               |

| Reset:    | 0xX                  |

| Property: | PAC Write-Protection |

| Bit    | 7     | 6     | 5     | 4     | 3   | 2       | 1   | 0     |

|--------|-------|-------|-------|-------|-----|---------|-----|-------|

|        | BCCDx | BCCDx | DCCDx | DCCDx | HPE | DBGPRES | DAL | [1:0] |

| Access | R     | R     | R     | R     | R   | R       | R   | R     |

| Reset  | 0     | 0     | 0     | 0     | 1   | 0       | 0   | x     |

**Bits 7,6 – BCCDx** BOOT Communication Channel x Dirty [x=1..0] Writing a '0' to this bit has no effect.

Writing a '1' to this bit has no effect.

This bit is set when BCCx is written.

This bit is cleared when BCCx is read.

# **Bits 5,4 – DCCDx** Debug Communication Channel x Dirty [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit has no effect.

This bit is set when DCCx is written.

This bit is cleared when DCCx is read.

#### Bit 3 – HPE Hot-Plugging Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit has no effect.

This bit is set when Hot-Plugging is enabled.

This bit is cleared when Hot-Plugging is disabled. This is the case when the SWCLK function is changed. Only a power-reset or a external reset can set it again.

#### Bit 2 – DBGPRES Debugger Present

Writing a '0' to this bit has no effect.

Writing a '1' to this bit has no effect.

This bit is set when a debugger probe is detected.

This bit is never cleared.

#### Bits 1:0 – DAL[1:0] Debugger Access Level

Indicates the debugger access level:

- 0x0: Debugger can only access the DSU external address space.

- 0x1: Debugger can access only Non-Secure regions (SAM L11 only).

- 0x2: Debugger can access secure and Non-Secure regions.

#### 21.8.1 Reset Cause

Name:RCAUSEOffset:0x00Property:-

When a Reset occurs, the bit corresponding to the Reset source is set to '1' and all other bits are written to '0'.

| Bit    | 7 | 6    | 5   | 4   | 3 | 2     | 1     | 0   |

|--------|---|------|-----|-----|---|-------|-------|-----|

|        |   | SYST | WDT | EXT |   | BOD33 | BOD12 | POR |

| Access |   | R    | R   | R   |   | R     | R     | R   |

| Reset  |   | х    | х   | х   |   | х     | х     | х   |

Bit 6 - SYST System Reset Request

This bit is set if a System Reset Request has occurred. Refer to the Cortex processor documentation for more details.

**Bit 5 – WDT** Watchdog Reset This bit is set if a Watchdog Timer Reset has occurred.

Bit 4 – EXT External Reset

This bit is set if an external Reset has occurred.

**Bit 2 – BOD33** Brown Out 33 Detector Reset This bit is set if a BOD33 Reset has occurred.

**Bit 1 – BOD12** Brown Out 12 Detector Reset This bit is set if a BOD12 Reset has occurred.

**Bit 0 – POR** Power On Reset This bit is set if a POR has occurred.

### **OSCCTRL – Oscillators Controller**

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0xE          | 16384                               | 3                              | 500000                              |

| 0xF          | 32768                               | 3                              | 1000000                             |

#### Note:

- 1. Actual startup time is 1 OSCULP32K cycle + 3 XOSC cycles.

- 2. The given time neglects the three XOSC cycles before OSCULP32K cycle.

#### Bit 11 – AMPGC Automatic Amplitude Gain Control

**Note:** This bit must be set only after the XOSC has settled, indicated by the XOSC Ready flag in the Status register (STATUS.XOSCRDY).

| Value | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The automatic amplitude gain control is disabled.                                                                                   |

| 1     | The automatic amplitude gain control is enabled. Amplitude gain will be automatically adjusted during Crystal Oscillator operation. |

#### Bits 10:8 – GAIN[2:0] Oscillator Gain

These bits select the gain for the oscillator. The listed maximum frequencies are recommendations, and might vary based on capacitive load and crystal characteristics. Those bits must be properly configured even when the Automatic Amplitude Gain Control is active.

| Value   | Recommended Max Frequency [MHz] |

|---------|---------------------------------|

| 0x0     | 2                               |

| 0x1     | 4                               |

| 0x2     | 8                               |

| 0x3     | 16                              |

| 0x4     | 30                              |

| 0x5-0x7 | Reserved                        |

#### Bit 7 – ONDEMAND On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled, depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

The Write-Synchronization of the Enable bit is triggered by writing a '1' to the Enable bit of the BOD33 Control register. The Synchronization Ready bit (STATUS.B33SRDY) in the STATUS register will be cleared when the Write-Synchronization starts, and set again when the Write-Synchronization is complete. Writing to the same register while the Write-Synchronization is ongoing (STATUS.B33SRDY is '0') will generate a PAC error without stalling the APB bus.

#### 25.6.7 Low Power VREF in Active Mode

During active functional mode, the brownout detector BOD33 and the main voltage regulator (VREG) can reduce their power consumption by using the low power voltage reference (ULPVREF).

The low power voltage reference is ready and can be selected when ULPVREFRDY bit in STATUS register is high. The ULPVREF Ready (ULPVREFRDY) interrupt can also be used to detect a zero-to-one transition of the STATUS.ULPVREFRDY bit.

Writing the VREF bit in the BOD33 register to '1' selects ULPVREF as voltage reference for the BOD33.

If the chip operated in PL0 ((PM->PLCFG.PLSEL=0) or Performance Level is disabled (PM->PLCFG.PLDIS=1), writing the VREFSEL bit in the VREG register to '1' selects ULPVREF as voltage reference for the main voltage regulator.

#### 26.6.6 Sleep Mode Operation

The Run-In-Standby bit in Control A (CTRLA.RUNSTDBY) control the behavior of the WDT during standby sleep mode. When the bit is zero, the watchdog is disabled during sleep, but maintains its current configuration. When CTRLA.RUNSTDBY is '1', the WDT continues to operate during sleep.

#### **Related Links**

26.8.1 CTRLA

#### 26.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following registers are synchronized when written:

- Enable bit in Control A register (CTRLA.ENABLE)

- Window Enable bit in Control A register (CTRLA.WEN)

- Run-In-Standby bit in Control A register (CTRLA.RUNSTDBY)

- Always-On bit in control Control A (CTRLA.ALWAYSON)

- Watchdog Clear register (CLEAR)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

#### 26.6.8 Additional Features

#### 26.6.8.1 Always-On Mode

The Always-On mode is enabled by setting the Always-On bit in the Control A register (CTRLA.ALWAYSON=1). When the Always-On mode is enabled, the WDT runs continuously, regardless of the state of CTRLA.ENABLE. Once written, the Always-On bit can only be cleared by a power-on reset. The Configuration (CONFIG) and Early Warning Control (EWCTRL) registers are read-only registers while the CTRLA.ALWAYSON bit is set. Thus, the time period configuration bits (CONFIG.PER, CONFIG.WINDOW, EWCTRL.EWOFFSET) of the WDT cannot be changed.

Enabling or disabling Window mode operation by writing the Window Enable bit (CTRLA.WEN) is allowed while in Always-On mode, but note that CONFIG.PER cannot be changed.

The Interrupt Clear and Interrupt Set registers are accessible in the Always-On mode. The Early Warning interrupt can still be enabled or disabled while in the Always-On mode, but note that EWCTRL.EWOFFSET cannot be changed.

Table WDT Operating Modes With Always-On shows the operation of the WDT for CTRLA.ALWAYSON=1.

| V | VEN | Interrupt Enable | Mode                                                   |

|---|-----|------------------|--------------------------------------------------------|

| 0 | )   | 0                | Always-on and normal mode                              |

| 0 | )   | 1                | Always-on and normal mode with Early Warning interrupt |

#### Table 26-2. WDT Operating Modes With Always-On

### 28.8.6 Debug Control

| Name:     | DBGCTRL              |

|-----------|----------------------|

| Offset:   | 0x0D                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

| <b>/</b> alue | Description                                                                         |

|---------------|-------------------------------------------------------------------------------------|

| C             | The DMAC is halted when the CPU is halted by an external debugger.                  |

| 1             | The DMAC continues normal operation when the CPU is halted by an external debugger. |

(ASYNCH.ASYNCH[x]). The EIC edge detection is operated synchronously when the Asynchronous Control Mode bit (ASYNCH.ASYNCH[x]) is '0' (default value). It is operated asynchronously when ASYNCH.ASYNCH[x] is written to '1'.

In *Synchronous Edge Detection Mode*, the external interrupt (EXTINT) or the non-maskable interrupt (NMI) pins are sampled using the EIC clock as defined by the Clock Selection bit in the Control A register (CTRLA.CKSEL). The External Interrupt flag (INTFLAG.EXTINT[x]) or Non-Maskable Interrupt flag (NMIFLAG.NMI) is set when the last sampled state of the pin differs from the previously sampled state. In this mode, the EIC clock is required.

The Synchronous Edge Detection Mode can be used in Idle and Standby sleep modes.

In *Asynchronous Edge Detection Mode*, the external interrupt (EXTINT) pins or the non-maskable interrupt (NMI) pins set the External Interrupt flag or Non-Maskable Interrupt flag (INTFLAG.EXTINT[x] or NMIFLAG) directly. In this mode, the EIC clock is not requested.

The asynchronous edge detection mode can be used in Idle and Standby sleep modes.

#### 29.6.4.3 Interrupt Pin Debouncing

The external interrupt pin (EXTINT) edge detection can use a debouncer to improve input noise immunity. When selected, the debouncer can work in the synchronous mode or the asynchronous mode, depending on the configuration of the ASYNCH.ASYNCH[x] bit for the pin. The debouncer uses the EIC clock as defined by the bit CTRLA.CKSEL to clock the debouncing circuitry. The debouncing time frame is set with the debouncer prescaler DPRESCALER.DPRESCALERn, which provides the *low frequency clock* tick that is used to reject higher frequency signals.

The debouncing mode for pin EXTINT x can be selected only if the Sense bits in the Configuration y register (CONFIGy.SENSEx) are set to RISE, FALL or BOTH. If the debouncing mode for pin EXTINT x is selected, the filter mode for that pin (CONFIGy.FILTENx) can not be selected.

The debouncer manages an internal "valid pin state" that depends on the external interrupt (EXTINT) pin transitions, the debouncing mode and the debouncer prescaler frequency. The valid pin state reflects the pin value after debouncing. The external interrupt pin (EXTINT) is sampled continously on EIC clock. The sampled value is evaluated on each *low frequency clock* tick to detect a transitional edge when the sampled value is different of the current valid pin state. The sampled value is evaluated on each EIC clock when DPRESCALER.TICKON=0 or on each *low frequency clock* tick when DPRESCALER.TICKON=1, to detect a bounce when the sampled value is equal to the current valid pin state. Transitional edge detection increments the transition counter of the EXTINT pin, while bounce detection resets the transition counter. The transition counter must exceed the transition count threshold as defined by the DPRESCALER.STATESn bitfield. In the synchronous mode the threshold is 4 when DPRESCALER.STATESn=0 or 8 when DPRESCALER.STATESn=1. In the asynchronous mode the threshold is 4.

The valid pin state for the pins can be accessed by reading the register PINSTATE for both synchronous or asynchronous debouncing mode.

**Synchronous edge detection** In this mode the external interrupt (EXTINT) pin is sampled continously on EIC clock.

- 1. A pin edge transition will be validated when the sampled value is consistently different of the current valid pin state for 4 (or 8 depending on bit DPRESCALER.STATESn) consecutive ticks of the low frequency clock.

- 2. Any pin sample, at the *low frequency clock* tick rate, with a value opposite to the current valid pin state will increment the transition counter.

## NVMCTRL – Nonvolatile Memory Controller

| or .   |          |          |              |           |        |          |          |            |         |  |  |

|--------|----------|----------|--------------|-----------|--------|----------|----------|------------|---------|--|--|

| Offset | Name     | Bit Pos. |              |           |        |          |          |            |         |  |  |

|        |          | 15:8     |              |           | SLKE   | Y[7:0]   | -        |            |         |  |  |

| 0x22   | NSULCK   | 7:0      |              |           |        |          | DNS      | ANS        | BNS     |  |  |

| 0,22   | NOOLOK   | 15:8     |              |           | NSLKI  | EY[7:0]  |          |            |         |  |  |

|        |          | 7:0      | FLASHP[7:0]  |           |        |          |          |            |         |  |  |

| 0x24   | PARAM    | 15:8     | FLASHP[15:8] |           |        |          |          |            |         |  |  |

| 0724   | PARAM    | 23:16    | DFL          | ASHP[3:0] |        |          |          | PSZ[2:0]   |         |  |  |

|        |          | 31:24    |              |           | DFLASI | HP[11:4] |          |            |         |  |  |

| 0x28   |          |          |              |           |        |          |          |            |         |  |  |

|        | Reserved |          |              |           |        |          |          |            |         |  |  |

| 0x2F   |          |          |              |           |        |          |          |            |         |  |  |

|        |          | 7:0      |              |           | DSCK   | EY[7:0]  |          |            |         |  |  |

| 0x30   | DSCC     | 15:8     |              |           | DSCKE  | Y[15:8]  |          |            |         |  |  |

| 0,30   | DSCC     | 23:16    |              |           | DSCKE  | Y[23:16] |          |            |         |  |  |

|        |          | 31:24    |              |           |        | DSCKE    | Y[29:24] |            |         |  |  |

|        | SECCTRL  | 7:0      | DXN          |           |        | DSCEN    | SILACC   |            | TAMPEEN |  |  |

| 0x34   |          | 15:8     |              |           |        |          |          | TEROW[2:0] |         |  |  |

| 0x34   |          | 23:16    |              |           |        |          |          |            |         |  |  |

|        |          | 31:24    |              |           | KEY    | [7:0]    |          |            | 1       |  |  |

|        |          | 7:0      |              |           |        |          |          | BCWEN      | BCREN   |  |  |

| 020    | 00500    | 15:8     |              |           |        |          |          |            |         |  |  |

| 0x38   | SCFGB    | 23:16    |              |           |        |          |          |            |         |  |  |

|        |          | 31:24    |              |           |        |          |          |            |         |  |  |

|        |          | 7:0      |              |           |        |          |          |            | URWEN   |  |  |

|        | 005015   | 15:8     |              |           |        |          |          |            |         |  |  |

| 0x3C   | SCFGAD   | 23:16    |              |           |        |          |          |            |         |  |  |

|        |          | 31:24    |              |           |        |          |          |            |         |  |  |

|        |          | 7:0      |              |           |        |          |          |            | WRITE   |  |  |

|        |          | 15:8     |              |           |        |          |          |            |         |  |  |

| 0x40   | NONSEC   | 23:16    |              |           |        |          |          |            |         |  |  |

|        |          | 31:24    |              |           |        |          |          |            |         |  |  |

|        |          | 7:0      |              |           |        |          |          |            | WRITE   |  |  |

|        |          | 15:8     |              |           |        |          |          |            |         |  |  |

| 0x44   | NSCHK    | 23:16    |              |           |        |          |          |            |         |  |  |

|        |          | 31:24    |              |           |        |          |          |            |         |  |  |

#### 30.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

© 2018 Microchip Technology Inc.

#### Bit 11 – FWUP Cache Disable

This bit is used to disable the cache.

| Value | Description                |

|-------|----------------------------|

| 0     | Fast wake-up is turned off |

| 1     | Fast wake-up is turned on  |

# Bits 9:8 – SLEEPPRM[1:0] Power Reduction Mode during Sleep

Indicates the Power Reduction Mode during sleep.

| Value | Name          | Description                                          |

|-------|---------------|------------------------------------------------------|

| 0x0   | WAKEUPACCESS  | NVM block enters low-power mode when entering sleep. |

|       |               | NVM block exits low-power mode upon first access.    |

| 0x1   | WAKEUPINSTANT | NVM block enters low-power mode when entering sleep. |

|       |               | NVM block exits low-power mode when exiting sleep.   |

| 0x2   | Reserved      |                                                      |

| 0x3   | DISABLED      | Auto power reduction disabled.                       |

#### Bits 4:1 - RWS[3:0] NVM Read Wait States

These bits control the number of wait states for a read operation. '0' indicates zero wait states, '1' indicates one wait state, etc., up to 15 wait states.

This register is initialized to 0 wait states. Software can change this value based on the NVM access time and system frequency.

# SAM L10/L11 Family PORT - I/O Pin Controller

Writing a '1' to a bit will clear the corresponding bit in the DIR register, which configures the I/O pin as an input.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration. |

| 1     | The corresponding I/O pin in the PORT group is configured as input.      |

#### 35.8.13 DBGCTRL

#### 35.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 35.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 35.5.10 Analog Connections

Not applicable.

#### **35.6 Functional Description**

#### 35.6.1 Principle of Operation

The USART uses the following lines for data transfer:

- RxD for receiving

- TxD for transmitting

- XCK for the transmission clock in synchronous operation

USART data transfer is frame based. A serial frame consists of:

- 1 start bit

- From 5 to 9 data bits (MSB or LSB first)

- No, even or odd parity bit

- 1 or 2 stop bits

A frame starts with the start bit followed by one character of data bits. If enabled, the parity bit is inserted after the data bits and before the first stop bit. After the stop bit(s) of a frame, either the next frame can

#### 35.8.2 Control B

| Name:     | CTRLB                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x04                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Enable-Protected, Write-Synchronized |

| Bit    | 31 | 30     | 29    | 28 | 27 | 26  | 25          | 24     |

|--------|----|--------|-------|----|----|-----|-------------|--------|

|        |    |        |       |    |    |     |             |        |

| Access |    |        |       |    |    |     |             |        |

| Reset  |    |        |       |    |    |     |             |        |

|        |    |        |       |    |    |     |             |        |

| Bit    | 23 | 22     | 21    | 20 | 19 | 18  | 17          | 16     |

|        |    |        |       |    |    |     | RXEN        | TXEN   |

| Access |    |        |       |    |    |     | R/W         | R/W    |

| Reset  |    |        |       |    |    |     | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 15 | 14     | 13    | 12 | 11 | 10  | 9           | 8      |

|        |    |        | PMODE |    |    | ENC | SFDE        | COLDEN |

| Access |    |        | R/W   |    |    | R/W | R/W         | R/W    |

| Reset  |    |        | 0     |    |    | 0   | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 7  | 6      | 5     | 4  | 3  | 2   | 1           | 0      |

|        |    | SBMODE |       |    |    |     | CHSIZE[2:0] |        |

| Access | -  | R/W    | ·     |    |    | R/W | R/W         | R/W    |

| Reset  |    | 0      |       |    |    | 0   | 0           | 0      |

#### Bit 17 - RXEN Receiver Enable

Writing '0' to this bit will disable the USART receiver. Disabling the receiver will flush the receive buffer and clear the FERR, PERR and BUFOVF bits in the STATUS register.

Writing '1' to CTRLB.RXEN when the USART is disabled will set CTRLB.RXEN immediately. When the USART is enabled, CTRLB.RXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled, CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the USART is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                            |

| 1     | The receiver is enabled or will be enabled when the USART is enabled. |

#### Bit 16 – TXEN Transmitter Enable

Writing '0' to this bit will disable the USART transmitter. Disabling the transmitter will not become effective until ongoing and pending transmissions are completed.

Writing '1' to CTRLB.TXEN when the USART is disabled will set CTRLB.TXEN immediately. When the USART is enabled, CTRLB.TXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the transmitter is enabled. When the transmitter is enabled, CTRLB.TXEN will read back as '1'.

© 2018 Microchip Technology Inc.

### 40.7 Register Summary

| Offset | Name      | Bit Pos. |             |            |         |         |             |       |         |       |

|--------|-----------|----------|-------------|------------|---------|---------|-------------|-------|---------|-------|

| 0x00   | CTRL      | 7:0      |             | RUNSTDBY   |         |         |             |       | ENABLE  | SWRST |

| 0x01   |           |          |             |            |         |         |             |       |         |       |

|        | Reserved  |          |             |            |         |         |             |       |         |       |

| 0x03   |           |          |             |            |         |         |             |       |         |       |

| 0x04   | SEQCTRL0  | 7:0      |             |            |         |         |             | SEQS  | EL[3:0] |       |

| 0x05   |           |          |             |            |         |         |             |       |         |       |

|        | Reserved  |          |             |            |         |         |             |       |         |       |

| 0x07   |           |          |             |            |         |         |             |       |         |       |

|        |           | 7:0      | EDGESEL     |            | FILTSI  | EL[1:0] |             |       | ENABLE  |       |

| 0x08   | LUTCTRL0  | 15:8     | INSELx[3:0] |            |         |         | INSELx[3:0] |       |         |       |

| 0.00   | LOTOTIKED | 23:16    |             | LUTEO      | LUTEI   | INVEI   |             | INSEL | _x[3:0] |       |

|        |           | 31:24    |             | TRUTH[7:0] |         |         |             |       |         |       |

|        |           | 7:0      | EDGESEL     |            | FILTSI  | EL[1:0] |             |       | ENABLE  |       |

| 0x0C   | LUTCTRL1  | 15:8     |             | INSEL      | _x[3:0] |         | INSELx[3:0] |       |         |       |

| UNUC   | LUTCIKLI  | 23:16    |             | LUTEO      | LUTEI   | INVEI   |             | INSEL | _x[3:0] |       |

|        |           | 31:24    |             |            |         | TRUT    | H[7:0]      |       |         |       |

### 40.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 40.5.8 Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

- Gain Correction (GAINCORR)

- Offset Correction (OFFSETCORR)

When one of these registers is written, the data is stored in the corresponding buffer as long as the current conversion is not impacted, and the corresponding busy status will be set in the Synchronization Busy register (SYNCBUSY). When a new RESULT is available, data stored in the buffer registers will be transfered to the ADC and a new conversion can start.

#### 41.6.3.2 Device Temperature Measurement

#### Principle

The device has an integrated temperature sensor which is part of the Supply Controller (SUPC). The analog signal of that sensor can be converted into a digital value by the ADC. The digital value can be converted into a temperature in °C by following the steps in this section.

#### **Configuration and Conditions**

In order to conduct temperature measurements, configure the device according to these steps.

- 1. Configure the clocks and device frequencies according to the Electrical Characteristics chapters.

- 2. Configure the Voltage References System of the Supply Controller (SUPC):

- 2.1. Enable the temperature sensor by writing a '1' to the Temperature Sensor Enable bit in the VREF Control register (SUPC.VREF.TSEN).

- 2.2. Select the required voltage for the internal voltage reference INTREF by writing to the Voltage Reference Selection bits (SUPC.VREF.SEL). The required value can be found in the Electrical Characteristics chapters.

- 2.3. Enable routing INTREF to the ADC by writing a '1' to the Voltage Reference Output Enable bit (SUPC.VREF.VREFOE).

- 3. Configure the ADC:

- 3.1. Select the internal voltage reference INTREF as ADC reference voltage by writing to the Reference Control register (ADC.REFCTRL.REFSEL).

- 3.2. Select the temperature sensor vs. internal GND as input by writing TEMP and GND to the positive and negative MUX Input Selection bit fields (ADC.INPUTCTRL.MUXNEG and .MUXPOS, respectively).

- 3.3. Configure the remaining ADC parameters according to the Electrical Characteristics chapters.

- 3.4. Enable the ADC and acquire a value, ADC<sub>m</sub>.

#### **Calculation Parameter Values**

The temperature sensor behavior is linear, but it is sensitive to several parameters such as the internal voltage reference - which itself depends on the temperature. To take this into account, each device contains a Temperature Log row with individual calibration data measured and written during the production tests. These calibration values are read by software to infer the most accurate temperature readings possible.

The Temperature Log Row basically contains the following parameter set for two different temperatures ("ROOM" and "HOT"):

- Calibration temperatures in °C. One at room temperature *temp*<sub>R</sub>, one at a higher temperature *temp*<sub>H</sub>:

- ROOM\_TEMP\_VAL\_INT and ROOM\_TEMP\_VAL\_DEC contain the measured temperature at room insertion, *temp*<sub>R</sub>, in °C, separated in integer and decimal value.

Equations 3 is a coarse value, because we assumed that  $INT1V_c=1V$ . To achieve a more accurate result, we replace  $INT1V_c$  with an interpolated value  $INT1V_m$ . We use the two data pairs (*temp*<sub>R</sub>,  $INT1V_R$ ) and (*temp*<sub>H</sub>,  $INT1V_H$ ) and yield:

$$(\frac{\text{INT1V}_m - \text{INT1V}_R}{temp_m - temp_R}) = (\frac{\text{INT1V}_H - \text{INT1VV}_R}{temp_H - temp_R})$$

Using the coarse temperature value  $temp_c$ , we can infer a more precise INT1V<sub>m</sub> value during the ADC conversion as:

#### [Equation 4]

$$INT1V_m = INT1V_R + \left(\frac{(INT1V_H - INT1V_R) \cdot (temp_C - temp_R)}{(temp_H - temp_R)}\right)$$

Back to Equation 3, we replace the simple  $INT1V_c=1V$  by the more precise  $INT1V_m$  of Equation 4, and find a more accurate temperature value *temp*<sub>f</sub>:

#### [Equation 5]

$$temp_{f} = temp_{R} + \left[\frac{\{ADC_{m} \cdot \text{INT1V}_{m} - (ADC_{R} \cdot \text{INT1V}_{R})\} \cdot (temp_{H} - temp_{R})}{\{(ADC_{H} \cdot \text{INT1V}_{H}) - (ADC_{R} \cdot \text{INT1V}_{R})\}}\right]$$

#### 41.6.4 DMA Operation

The ADC generates the following DMA request:

• Result Conversion Ready (RESRDY): the request is set when a conversion result is available and cleared when the RESULT register is read. When the averaging operation is enabled, the DMA request is set when the averaging is completed and result is available.

#### 41.6.5 Interrupts

The ADC has the following interrupt sources:

- Result Conversion Ready: RESRDY

- Window Monitor: WINMON

- Overrun: OVERRUN

These interrupts, except the OVERRUN interrupt, are asynchronous wake-up sources. See *Sleep Mode Controller* for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a one to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the ADC is reset. See INTFLAG register for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to *Nested Vector Interrupt Controller* for details. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

22.6.3.3 Sleep Mode Controller

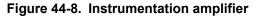

**OPAMP – Operational Amplifier Controller**

| OPAMPCTRL0.POTMUX | OPAMPCTRL2.POTMUX | GAIN     |  |

|-------------------|-------------------|----------|--|

| 0x7               | Reserved          | Reserved |  |

| 0x6               | 0x0               | 1/7      |  |

| 0x5               | Reserved          | Reserved |  |

| 0x4               | 0x1               | 1/3      |  |

| 0x3               | Reserved          | Reserved |  |

| 0x2               | 0x2               | 1        |  |

| 0x1               | 0x4               | 3        |  |

| 0x0               | 0x6               | 7        |  |

#### Table 44-10. Instrumentation Amplifier Gain Selection

**Note:** Either the DAC or GND must be the reference, selected by the OPAMPCTRL0.RES1MUX bits. Refer to the OPAMP Control 'x' register (44.8.3 OPAMPCTRL) for details.

#### 44.6.10.8 High Gain Instrumentation Amplifier

In this mode, OPAMP0 and OPAMP1 are configured as non inverting amplifiers [Stage 1]. OPAMP2 is configured as difference amplifier[Stage 2]. Total gain of the instrumentation amplifier is product of gains of stage 1 and stage 2. The OPAMPCTRLx and RESCTRL registers can be configured as follows:

125°C Electrical Characteristics

| Mode | Conditions                                                                 | Regulator Mode                                 | Vcc  | Та    | Тур.   | Max.    | Units |  |

|------|----------------------------------------------------------------------------|------------------------------------------------|------|-------|--------|---------|-------|--|

|      |                                                                            |                                                |      | 125°C | 15.5   | 33.2    |       |  |

|      | 4kB RAM retained,PDSW<br>domain in retention                               | LPEFF Disable                                  | 1,8V | 25°C  | 0.5    | 0.9     | -     |  |

|      |                                                                            |                                                |      | 125°C | 22.0   | 58.9    |       |  |

|      |                                                                            | LPEFF Enable                                   | 3,3V | 25°C  | 0.5    | 0.9     |       |  |

|      |                                                                            |                                                |      | 125°C | 18.7   | 41.5    |       |  |

|      |                                                                            | BUCK in standby PL0<br>(VREG.RUNSTDBY=1<br>and | 1,8V | 25°C  | 0.7    | 1.0     |       |  |

|      |                                                                            |                                                |      | 125°C | 18.4   | 42.7    | μΑ    |  |

|      |                                                                            | VREG.STDBYPL0=1)                               | 3,3V | 25°C  | 0.8    | 1.5     |       |  |

|      |                                                                            |                                                |      | 125°C | 14.6   | 31.0    |       |  |

|      | 4kB RAM retained,PDSW<br>domain in retention and<br>RTC running on XOSC32k | LPEFF Disable                                  | 1,8V | 25°C  | 0.9    | 1.3     |       |  |

|      |                                                                            |                                                |      | 125°C | 22.6   | 59.8    |       |  |

|      |                                                                            | LPEFF Enable                                   | 3,3V | 25°C  | 0.8    | 1.2     |       |  |

|      |                                                                            |                                                |      | 125°C | 19.3   | 42.1    |       |  |

|      |                                                                            | BUCK in standby PL0<br>(VREG.RUNSTDBY=1<br>and | 1,8V | 25°C  | 1.0    | 1.3     |       |  |

|      |                                                                            |                                                |      | 125°C | 19.0   | 43.3    |       |  |

|      |                                                                            | VREG.STDBYPL0=1)                               | 3,3V | 25°C  | 1.1    | 1.7     |       |  |

|      |                                                                            |                                                |      | 125°C | 15.2   | 31.6    |       |  |

| OFF  |                                                                            |                                                | 1,8V | 25°C  | 34.6   | 54.4    | nA    |  |

|      |                                                                            |                                                |      | 125°C | 4385.0 | 8291.5  |       |  |

|      |                                                                            |                                                | 3,3V | 25°C  | 61.2   | 89.1    |       |  |

|      |                                                                            |                                                |      | 125°C | 5489.5 | 10564.7 |       |  |

# 47.4 Analog Characteristics

# 47.4.1 Brown-Out Detectors (BOD) Characteristics

#### Table 47-4. BOD33 Characteristics with BOD33.VREFSEL = 0

| Symbol | Parameters                 | Conditions          | Min. | Тур. | Max. | Unit |  |

|--------|----------------------------|---------------------|------|------|------|------|--|

|        | BOD33 high threshold level | BOD33.LEVEL<br>= 6  | 1.66 | 1.68 | 1.70 | V    |  |

|        |                            | BOD33.LEVEL<br>= 7  | 1.70 | 1.72 | 1.74 |      |  |

|        |                            | BOD33.LEVEL<br>= 39 | 2.79 | 2.84 | 2.89 |      |  |