# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-VQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e14a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PAC - Peripheral Access Controller**

#### 15.7.5 AHB Slave Bus Interrupt Flag Status and Clear

| Name:     | INTFLAGAHB |

|-----------|------------|

| Offset:   | 0x10       |

| Reset:    | 0x000000   |

| Property: | Secure     |

This flag is cleared by writing a '1' to the flag.

This flag is set when an access error is detected by the SLAVE n, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the corresponding INTFLAGAHB interrupt flag.

| Bit    | 31      | 30       | 29        | 28       | 27      | 26      | 25      | 24      |

|--------|---------|----------|-----------|----------|---------|---------|---------|---------|

|        |         |          |           |          |         |         |         |         |

| Access |         |          |           |          |         |         |         |         |

| Reset  |         |          |           |          |         |         |         |         |

|        |         |          |           |          |         |         |         |         |

| Bit    | 23      | 22       | 21        | 20       | 19      | 18      | 17      | 16      |

|        |         |          |           |          |         |         |         |         |

| Access |         |          |           |          |         |         |         |         |

| Reset  |         |          |           |          |         |         |         |         |

|        |         |          |           |          |         |         |         |         |

| Bit    | 15      | 14       | 13        | 12       | 11      | 10      | 9       | 8       |

|        |         |          |           |          |         |         |         |         |

| Access |         |          |           |          |         |         |         |         |

| Reset  |         |          |           |          |         |         |         |         |

|        |         |          |           |          |         |         |         |         |

| Bit    | 7       | 6        | 5         | 4        | 3       | 2       | 1       | 0       |

|        | BROM    | HSRAMDSU | HSRAMDMAC | HSRAMCPU | HPB2    | HPB1    | HPB0    | FLASH   |

| Access | RW/-/RW | RW/-/RW  | RW/-/RW   | RW/-/RW  | RW/-/RW | RW/-/RW | RW/-/RW | RW/-/RW |

| Reset  | 0       | 0        | 0         | 0        | 0       | 0       | 0       | 0       |

|        |         |          |           |          |         |         |         |         |

Bit 7 – BROM Interrupt Flag for Boot ROM

Bit 6 – HSRAMDSU Interrupt Flag for SLAVE HS SRAM Port 2 - DSU Access

Bit 5 – HSRAMDMAC Interrupt Flag for SLAVE HS SRAM Port 1 - DMAC Access

- Bit 4 HSRAMCPU Interrupt Flag for SLAVE HS SRAM Port 0 CPU Access

- Bit 3 HPB2 Interrupt Flag for SLAVE AHB-APB Bridge C

- Bit 2 HPB1 Interrupt Flag for SLAVE AHB-APB Bridge B

- Bit 1 HPB0 Interrupt Flag for SLAVE AHB-APB Bridge A

- Bit 0 FLASH Interrupt Flag for SLAVE FLASH

# SAM L10/L11 Family

# **DSU - Device Service Unit**

| Offset | Name  | Bit Pos. |             |  |        |               |  |  |  |

|--------|-------|----------|-------------|--|--------|---------------|--|--|--|

|        | 015.4 | 7:0      | CCLASS[3:0] |  |        | PREAMBLE[3:0] |  |  |  |

|        |       | 15:8     |             |  |        |               |  |  |  |

| 0x1FF4 | CID1  | 23:16    |             |  |        |               |  |  |  |

|        |       | 31:24    |             |  |        |               |  |  |  |

| 0x1FF8 | CID2  | 7:0      |             |  | PREAME | BLEB2[7:0]    |  |  |  |

|        |       | 15:8     |             |  |        |               |  |  |  |

|        |       | 23:16    |             |  |        |               |  |  |  |

|        |       | 31:24    |             |  |        |               |  |  |  |

|        | CID3  | 7:0      |             |  | PREAME | BLEB3[7:0]    |  |  |  |

| 0x1FFC |       | 15:8     |             |  |        |               |  |  |  |

| UXTEFC |       | 23:16    |             |  |        |               |  |  |  |

|        |       | 31:24    |             |  |        |               |  |  |  |

## 16.12 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 16.5.7 Register Access Protection.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

documentation for details). This mechanism can be useful for applications that only require the processor to run when an interrupt occurs. Before entering the Idle mode, the user must select the Idle Sleep mode in the Sleep Configuration register (SLEEPCFG.SLEEPMODE=IDLE).

• Exiting Idle mode: The processor wakes the system up when it detects any non-masked interrupt with sufficient priority to cause exception entry. The system goes back to the Active mode. The CPU and affected modules are restarted.

GCLK clocks, regulators and RAM are not affected by the Idle Sleep mode and operate in normal mode.

#### 22.6.3.3.2 STANDBY Mode

The Standby mode is the lowest power configuration while keeping the state of the logic and the content of the RAM.

In this mode, all clocks are stopped except those configured to be running sleepwalking tasks. The clocks can also be active on request or at all times, depending on their on-demand and run-in-standby settings. Either synchronous (CLK\_APBx or CLK\_AHBx) or generic (GCLK\_x) clocks or both can be involved in sleepwalking tasks. This is the case when for example the SERCOM RUNSTDBY bit is written to '1'.

- Entering Standby mode: This mode is entered by executing the WFI instruction after writing the Sleep Mode bit in the Sleep Configuration register (SLEEPCFG.SLEEPMODE=STANDBY). The SLEEPONEXIT feature is also available as in Idle mode.

- Exiting Standby mode: Any peripheral able to generate an asynchronous interrupt can wake up the system. For example, a peripheral running on a GCLK clock can trigger an interrupt. When the enabled asynchronous wake-up event occurs and the system is woken up, the device will either execute the interrupt service routine or continue the normal program execution according to the Priority Mask Register (PRIMASK) configuration of the CPU.

Refer to 22.6.3.5 Power Domain Controller for the RAM state.

The regulator operates in Low-Power mode by default and switches automatically to the normal mode in case of a sleepwalking task requiring more power. It returns automatically to low power mode when the sleepwalking task is completed.

#### 22.6.3.3.3 OFF Mode

In Off mode, the device is entirely powered-off.

- Entering Off mode: This mode is entered by selecting the Off mode in the Sleep Configuration register by writing the Sleep Mode bits (SLEEPCFG.SLEEPMODE=OFF), and subsequent execution of the WFI instruction.

- Exiting Off mode: This mode is left by pulling the RESET pin low, or when a power Reset is done.

#### 22.6.3.4 Performance Level

The application can change the performance level on the fly writing to the by Performance Level Select bit in the Performance Level Configuration register (PLCFG.PLSEL).

When changing to a lower performance level, the bus frequency must be reduced before writing PLCFG.PLSEL in order to avoid exceeding the limit of the target performance level.

When changing to a higher performance level, the bus frequency can be increased only after the Performance Level Ready flag in the Interrupt Flag Status and Clear (INTFLAG.PLRDY) bit set to '1', indicating that the performance level transition is complete.

After a reset, the device starts in the lowest PL (lowest power consumption and lowest max frequency). The application can then switch to another PL at anytime without any stop in the code execution. As shown in Figure 22-3, performance level transition is possible only when the device is in active mode.

CTRLA.ENABLE=0 and check whether the write synchronization has finished, then change the desired bit field value. Enable-protected bits in CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

The RTC prescaler divides the source clock for the RTC counter.

**Note:** In Clock/Calendar mode, the prescaler must be configured to provide a 1Hz clock to the counter for correct operation.

The frequency of the RTC clock (CLK\_RTC\_CNT) is given by the following formula:

$$f_{\text{CLK}_\text{RTC}_\text{CNT}} = \frac{f_{\text{CLK}_\text{RTC}_\text{OSC}}}{2^{\text{PRESCALER}}}$$

The frequency of the oscillator clock, CLK\_RTC\_OSC, is given by  $f_{CLK_RTC_OSC}$ , and  $f_{CLK_RTC_CNT}$  is the frequency of the internal prescaled RTC clock, CLK\_RTC\_CNT.

#### 27.6.2.2 Enabling, Disabling, and Resetting

The RTC is enabled by setting the Enable bit in the Control A register (CTRLA.ENABLE=1). The RTC is disabled by writing CTRLA.ENABLE=0.

The RTC is reset by setting the Software Reset bit in the Control A register (CTRLA.SWRST=1). All registers in the RTC, except DEBUG, will be reset to their initial state, and the RTC will be disabled. The RTC must be disabled before resetting it.

#### 27.6.2.3 32-Bit Counter (Mode 0)

When the RTC Operating Mode bits in the Control A register (CTRLA.MODE) are written to 0x0, the counter operates in 32-bit Counter mode. The block diagram of this mode is shown in Figure 27-1. When the RTC is enabled, the counter will increment on every 0-to-1 transition of CLK\_RTC\_CNT. The counter will increment until it reaches the top value of 0xFFFFFFFF, and then wrap to 0x00000000. This sets the Overflow Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF).

The RTC counter value can be read from or written to the Counter Value register (COUNT) in 32-bit format.

The counter value is continuously compared with the 32-bit Compare register (COMP0). When a compare match occurs, the Compare 0 Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next 0-to-1 transition of CLK\_RTC\_CNT.

If the Clear on Match bit in the Control A register (CTRLA.MATCHCLR) is '1', the counter is cleared on the next counter cycle when a compare match with COMP0 occurs. This allows the RTC to generate periodic interrupts or events with longer periods than the prescaler events. Note that when CTRLA.MATCHCLR is '1', INTFLAG.CMP0 and INTFLAG.OVF will both be set simultaneously on a compare match with COMP0.

#### 27.6.2.4 16-Bit Counter (Mode 1)

When the RTC Operating Mode bits in the Control A register (CTRLA.MODE) are written to 0x1, the counter operates in 16-bit Counter mode as shown in Figure 27-2. When the RTC is enabled, the counter will increment on every 0-to-1 transition of CLK\_RTC\_CNT. In 16-bit Counter mode, the 16-bit Period register (PER) holds the maximum value of the counter. The counter will increment until it reaches the PER value, and then wrap to 0x0000. This sets the Overflow Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF).

The RTC counter value can be read from or written to the Counter Value register (COUNT) in 16-bit format.

© 2018 Microchip Technology Inc.

# SAM L10/L11 Family

## RTC – Real-Time Counter

| Value   | Name    | Description                 |

|---------|---------|-----------------------------|

| 0xB     | DIV1024 | CLK_RTC_CNT = GCLK_RTC/1024 |

| 0xC-0xF | -       | Reserved                    |

#### Bit 7 – MATCHCLR Clear on Match

This bit is valid only in Mode 0 (COUNT32) and Mode 2 (CLOCK). This bit can be written only when the peripheral is disabled. This bit is not synchronized.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The counter is not cleared on a Compare/Alarm 0 match |

| 1     | The counter is cleared on a Compare/Alarm 0 match     |

#### Bit 6 – CLKREP Clock Representation

This bit is valid only in Mode 2 and determines how the hours are represented in the Clock Value (CLOCK) register. This bit can be written only when the peripheral is disabled. This bit is not synchronized.

| Value | Description     |

|-------|-----------------|

| 0     | 24 Hour         |

| 1     | 12 Hour (AM/PM) |

#### Bits 3:2 - MODE[1:0] Operating Mode

This field defines the operating mode of the RTC. This bit is not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT32 | Mode 0: 32-bit counter |

| 0x1   | COUNT16 | Mode 1: 16-bit counter |

| 0x2   | CLOCK   | Mode 2: Clock/calendar |

| 0x3   | -       | Reserved               |

#### Bit 1 – ENABLE Enable

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                |

|-------|----------------------------|

| 0     | The peripheral is disabled |

| 1     | The peripheral is enabled  |

#### Bit 0 - SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the RTC, except DBGCTRL, to their initial state, and the RTC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST will be cleared when the reset is complete.

- Up to 8 channels

- Enable 8 independent transfers

- Automatic descriptor fetch for each channel

- Suspend/resume operation support for each channel

- Flexible arbitration scheme

- 4 configurable priority levels for each channel

- Fixed or round-robin priority scheme within each priority level

- From 1 to 256KB data transfer in a single block transfer

- Multiple addressing modes

- Static

- Configurable increment scheme

- Optional interrupt generation

- On block transfer complete

- On error detection

- On channel suspend

- 4 event inputs

- One event input for each of the 4 least significant DMA channels

- Can be selected to trigger normal transfers, periodic transfers or conditional transfers

- Can be selected to suspend or resume channel operation

- 4 event outputs

- One output event for each of the 4 least significant DMA channels

- Selectable generation on AHB, block, or transaction transfer complete

- Error management supported by write-back function

- Dedicated Write-Back memory section for each channel to store ongoing descriptor transfer

- CRC polynomial software selectable to

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE<sup>®</sup> 802.3)

# SAM L10/L11 Family DMAC – Direct Memory Access Controller

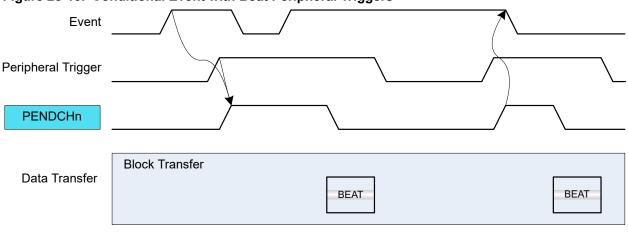

#### **Conditional Transfer**

The event input is used to trigger a conditional transfer on peripherals with pending transfer requests. As example, this type of event can be used for peripheral-to-peripheral transfers, where one peripheral is the source of event and the second peripheral is the source of the trigger.

Each peripheral trigger is stored internally when the event is received. When the peripheral trigger is stored internally, the Channel Pending status bit is set (CHSTATUS.PEND), the respective Pending Channel n Bit in the Pending Channels register is set (28.8.13 PENDCH.PENDCHn), and the event is acknowledged. A software trigger will now trigger a transfer.

The figure below shows an example where conditional event is enabled with peripheral beat trigger requests.

#### **Conditional Block Transfer**

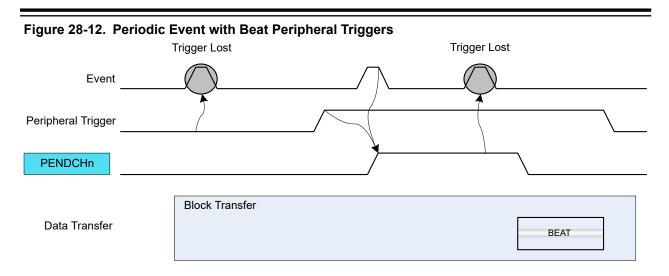

The event input is used to trigger a conditional block transfer on peripherals.

Before starting transfers within a block, an event must be received. When received, the event is acknowledged when the block transfer is completed. A software trigger will trigger a transfer.

The figure below shows an example where conditional event block transfer is started with peripheral beat trigger requests.

© 2018 Microchip Technology Inc.

#### 28.8.23 Channel Status

| Name:     | CHSTATUS |

|-----------|----------|

| Offset:   | 0x4F     |

| Reset:    | 0x00     |

| Property: | -        |

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|--------|---|---|---|---|---|------|------|------|

|        |   |   |   |   |   | FERR | BUSY | PEND |

| Access |   | • |   |   |   | R    | R    | R    |

| Reset  |   |   |   |   |   | 0    | 0    | 0    |

#### Bit 2 – FERR Channel Fetch Error

This bit is cleared when a software resume command is executed.

This bit is set when an invalid descriptor is fetched.

#### Bit 1 – BUSY Channel Busy

This bit is cleared when the channel trigger action is completed, when a bus error is detected or when the channel is disabled.

This bit is set when the DMA channel starts a DMA transfer.

#### Bit 0 – PEND Channel Pending

This bit is cleared when the channel trigger action is started, when a bus error is detected or when the channel is disabled. For details on trigger action settings, refer to CHCTRLB.TRIGACT.

This bit is set when a transfer is pending on the DMA channel, as soon as the transfer request is received.

(ASYNCH.ASYNCH[x]). The EIC edge detection is operated synchronously when the Asynchronous Control Mode bit (ASYNCH.ASYNCH[x]) is '0' (default value). It is operated asynchronously when ASYNCH.ASYNCH[x] is written to '1'.

In *Synchronous Edge Detection Mode*, the external interrupt (EXTINT) or the non-maskable interrupt (NMI) pins are sampled using the EIC clock as defined by the Clock Selection bit in the Control A register (CTRLA.CKSEL). The External Interrupt flag (INTFLAG.EXTINT[x]) or Non-Maskable Interrupt flag (NMIFLAG.NMI) is set when the last sampled state of the pin differs from the previously sampled state. In this mode, the EIC clock is required.

The Synchronous Edge Detection Mode can be used in Idle and Standby sleep modes.

In *Asynchronous Edge Detection Mode*, the external interrupt (EXTINT) pins or the non-maskable interrupt (NMI) pins set the External Interrupt flag or Non-Maskable Interrupt flag (INTFLAG.EXTINT[x] or NMIFLAG) directly. In this mode, the EIC clock is not requested.

The asynchronous edge detection mode can be used in Idle and Standby sleep modes.

#### 29.6.4.3 Interrupt Pin Debouncing

The external interrupt pin (EXTINT) edge detection can use a debouncer to improve input noise immunity. When selected, the debouncer can work in the synchronous mode or the asynchronous mode, depending on the configuration of the ASYNCH.ASYNCH[x] bit for the pin. The debouncer uses the EIC clock as defined by the bit CTRLA.CKSEL to clock the debouncing circuitry. The debouncing time frame is set with the debouncer prescaler DPRESCALER.DPRESCALERn, which provides the *low frequency clock* tick that is used to reject higher frequency signals.

The debouncing mode for pin EXTINT x can be selected only if the Sense bits in the Configuration y register (CONFIGy.SENSEx) are set to RISE, FALL or BOTH. If the debouncing mode for pin EXTINT x is selected, the filter mode for that pin (CONFIGy.FILTENx) can not be selected.

The debouncer manages an internal "valid pin state" that depends on the external interrupt (EXTINT) pin transitions, the debouncing mode and the debouncer prescaler frequency. The valid pin state reflects the pin value after debouncing. The external interrupt pin (EXTINT) is sampled continously on EIC clock. The sampled value is evaluated on each *low frequency clock* tick to detect a transitional edge when the sampled value is different of the current valid pin state. The sampled value is evaluated on each EIC clock when DPRESCALER.TICKON=0 or on each *low frequency clock* tick when DPRESCALER.TICKON=1, to detect a bounce when the sampled value is equal to the current valid pin state. Transitional edge detection increments the transition counter of the EXTINT pin, while bounce detection resets the transition counter. The transition counter must exceed the transition count threshold as defined by the DPRESCALER.STATESn bitfield. In the synchronous mode the threshold is 4 when DPRESCALER.STATESn=0 or 8 when DPRESCALER.STATESn=1. In the asynchronous mode the threshold is 4.

The valid pin state for the pins can be accessed by reading the register PINSTATE for both synchronous or asynchronous debouncing mode.

**Synchronous edge detection** In this mode the external interrupt (EXTINT) pin is sampled continously on EIC clock.

- 1. A pin edge transition will be validated when the sampled value is consistently different of the current valid pin state for 4 (or 8 depending on bit DPRESCALER.STATESn) consecutive ticks of the low frequency clock.

- 2. Any pin sample, at the *low frequency clock* tick rate, with a value opposite to the current valid pin state will increment the transition counter.

#### 32.8.2 Data Direction Clear

| Name:     | DIRCLR                           |

|-----------|----------------------------------|

| Offset:   | 0x04                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

This register allows the user to set one or more I/O pins as an input, without doing a read-modify-write operation. Changes in this register will also be reflected in the Data Direction (DIR), Data Direction Toggle (DIRTGL) and Data Direction Set (DIRSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31            | 30        | 29        | 28        | 27        | 26        | 25        | 24        |  |  |  |  |

|--------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|--|

| Dir (  | DIRCLR[31:24] |           |           |           |           |           |           |           |  |  |  |  |

| l      |               |           |           |           |           |           |           |           |  |  |  |  |

| Access | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |  |

| Reset  | 0             | 0         | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |  |

|        |               |           |           |           |           |           |           |           |  |  |  |  |

| Bit    | 23            | 22        | 21        | 20        | 19        | 18        | 17        | 16        |  |  |  |  |

|        |               |           |           | DIRCLE    | R[23:16]  |           |           |           |  |  |  |  |

| Access | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |  |

| Reset  | 0             | 0         | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |  |

|        |               |           |           |           |           |           |           |           |  |  |  |  |

| Bit    | 15            | 14        | 13        | 12        | 11        | 10        | 9         | 8         |  |  |  |  |

| [      |               |           |           | DIRCL     | R[15:8]   |           |           |           |  |  |  |  |

| Access | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |  |

| Reset  | 0             | 0         | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |  |

|        |               |           |           |           |           |           |           |           |  |  |  |  |

| Bit    | 7             | 6         | 5         | 4         | 3         | 2         | 1         | 0         |  |  |  |  |

| [      |               |           |           | DIRCI     | .R[7:0]   |           |           |           |  |  |  |  |

| l      |               |           |           |           |           |           |           |           |  |  |  |  |

| Access | RW/RW*/RW     | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |  |  |  |  |

| Reset  | 0             | 0         | 0         | 0         | 0         | 0         | 0         | 0         |  |  |  |  |

#### Bits 31:0 - DIRCLR[31:0] Port Data Direction Clear

Writing a '0' to a bit has no effect.

#### 33.7.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection , Secure

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | SWRST |

| Access |   |   |   |   |   |   |   | W/-/W |

| Reset  |   |   |   |   |   |   |   | 0     |

#### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the EVSYS to their initial state.

**Note:** Before applying a Software Reset it is recommended to disable the event generators.

#### 33.7.4 Channel Pending Interrupt

| Name:     | INTPEND |

|-----------|---------|

| Offset:   | 0x10    |

| Reset:    | 0x4000  |

| Property: | Secure  |

An interrupt that handles several channels should consult the INTPEND register to find out which channel number has priority (ignoring/filtering each channel that has its own interrupt line). An interrupt dedicated to only one channel must not use the INTPEND register.

| Bit    | 15    | 14    | 13 | 12 | 11 | 10 | 9       | 8       |  |

|--------|-------|-------|----|----|----|----|---------|---------|--|

|        | BUSY  | READY |    |    |    |    | EVD     | OVR     |  |

| Access | R/-/R | R/-/R |    |    |    |    | RW/-/RW | RW/-/RW |  |

| Reset  | 0     | 1     |    |    |    |    | 0       | 0       |  |

|        |       |       |    |    |    |    |         |         |  |

| Bit    | 7     | 6     | 5  | 4  | 3  | 2  | 1       | 0       |  |

|        |       |       |    |    |    |    | ID[1:0] |         |  |

| Access |       |       |    |    |    |    | RW/-/RW | RW/-/RW |  |

| Reset  |       |       |    |    |    |    | 0       | 0       |  |

#### Bit 15 - BUSY Busy

This bit is read '1' when the event on a channel selected by Channel ID field (ID) has not been handled by all the event users connected to this channel.

#### Bit 14 – READY Ready

This bit is read '1' when all event users connected to the channel selected by Channel ID field (ID) are ready to handle incoming events on this channel.

#### Bit 9 - EVD Channel Event Detected

This flag is set on the next CLK\_EVSYS\_APB cycle when an event is being propagated through the channel, and an interrupt request will be generated if CHINTENCLR/SET.EVD is '1'.

When the event channel path is asynchronous, the EVD bit will not be set.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear it. It will also clear the corresponding flag in the Channel n Interrupt Flag Status and Clear register (CHINTFLAGn) of this peripheral, where n is determined by the Channel ID bit field (ID) in this register.

#### Bit 8 – OVR Channel Overrun

This flag is set on the next CLK\_EVSYS cycle after an overrun channel condition occurs, and an interrupt request will be generated if CHINTENCLR/SET.OVRx is '1'.

There are two possible overrun channel conditions:

- One or more of the event users on channel selected by Channel ID field (ID) are not ready when a new event occurs

- An event happens when the previous event on channel selected by Channel ID field (ID) has not yet been handled by all event users

#### 33.7.18 Channel Security Attribution Check

| Name:     | NSCHKCHAN            |

|-----------|----------------------|

| Offset:   | 0x1DC                |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to select one or more channels to check their security attribution as non-secured.

|        | >        | Important: This register is only available for SAM L11 and has no effect for SAM L10. |          |          |          |          |          | <b>\M L10</b> . |

|--------|----------|---------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------------|

|        |          |                                                                                       |          |          |          |          |          |                 |

| Bit    | 31       | 30                                                                                    | 29       | 28       | 27       | 26       | 25       | 24              |

|        |          |                                                                                       |          |          |          |          |          |                 |

| Access |          |                                                                                       | 1        | 1        |          |          |          |                 |

| Reset  |          |                                                                                       |          |          |          |          |          |                 |

|        |          |                                                                                       |          |          |          |          |          |                 |

| Bit    | 23       | 22                                                                                    | 21       | 20       | 19       | 18       | 17       | 16              |

|        |          |                                                                                       |          |          |          |          |          |                 |

| Access |          |                                                                                       |          |          |          |          |          |                 |

| Reset  |          |                                                                                       |          |          |          |          |          |                 |

| Bit    | 15       | 14                                                                                    | 13       | 12       | 11       | 10       | 9        | 8               |

| DIL    | 15       | 14                                                                                    | 13       | 12       | 11       | 10       | 9        | °               |

| Access |          |                                                                                       |          |          |          |          |          |                 |

| Reset  |          |                                                                                       |          |          |          |          |          |                 |

| 10000  |          |                                                                                       |          |          |          |          |          |                 |

| Bit    | 7        | 6                                                                                     | 5        | 4        | 3        | 2        | 1        | 0               |

|        |          |                                                                                       |          | CHANN    | ELn[7:0] |          |          |                 |

| Access | RW/RW/RW | RW/RW/RW                                                                              | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW | RW/RW/RW        |

| Reset  | 0        | 0                                                                                     | 0        | 0        | 0        | 0        | 0        | 0               |

|        |          |                                                                                       |          |          |          |          |          |                 |

#### Bits 7:0 – CHANNELn[7:0] Channel n Selection [n=7..0]

These bits selects the individual channels for security attribution check. If any channel selected in NSCHKCHAN has the corresponding bit in NONSECCHAN set to the opposite value, then the NSCHK interrupt flag will be set.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | 0-to-1 transition will be detected on corresponding NONSECCHAN bit. |

| 1     | 1-to-0 transition will be detected on corresponding NONSECCHAN bit. |

# SAM L10/L11 Family

SERCOM USART - SERCOM Synchronous and Asyn...

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | NACK is transmitted when a parity error is received.     |

| 1     | NACK is not transmitted when a parity error is received. |

#### Bits 2:0 - GTIME[2:0] Guard Time

These bits define the guard time when using RS485 mode (CTRLA.FORM=0x0 or CTRLA.FORM=0x1, and CTRLA.TXPO=0x3) or ISO7816 mode (CTRLA.FORM=0x7).

For RS485 mode, the guard time is programmable from 0-7 bit times and defines the time that the transmit enable pin (TE) remains high after the last stop bit is transmitted and there is no remaining data to be transmitted.

For ISO7816 T=0 mode, the guard time is programmable from 2-9 bit times and defines the guard time between each transmitted byte.

# 36.8.11 Debug Control

|        | Name:<br>Offset:<br>Reset:<br>Property: | DBGCTRL<br>0x30<br>0x00<br>PAC Write-Protection |   |   |   |   |   |         |

|--------|-----------------------------------------|-------------------------------------------------|---|---|---|---|---|---------|

| Bit    | 7                                       | 6                                               | 5 | 4 | 3 | 2 | 1 | 0       |

|        |                                         |                                                 |   |   |   |   |   | DBGSTOP |

| Access |                                         |                                                 |   |   |   |   |   | R/W     |

| Reset  |                                         |                                                 |   |   |   |   |   | 0       |

#### Bit 0 – DBGSTOP Debug Stop Mode

This bit controls the functionality when the CPU is halted by an external debugger.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The baud-rate generator continues normal operation when the CPU is halted by an external |

|       | debugger.                                                                                |

| 1     | The baud-rate generator is halted when the CPU is halted by an external debugger.        |

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to 37.6.6 Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to *Peripherals Security Attribution* for more information.

#### 38.7.2.11 Debug Control

| Name:     | DBGCTRL              |

|-----------|----------------------|

| Offset:   | 0x0F                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

|           |                      |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN Run in Debug Mode

This bit is not affected by a software Reset, and should not be changed by software while the TC is enabled.

|   | Value | Description                                                                |

|---|-------|----------------------------------------------------------------------------|

| ſ | 0     | The TC is halted when the device is halted in debug mode.                  |

|   | 1     | The TC continues normal operation when the device is halted in debug mode. |

#### 39.8.3 Interrupt Enable Clear

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 7   | 6 | 5 | 4 | 3   | 2 | 1 | 0       |

|--------|-----|---|---|---|-----|---|---|---------|

|        |     |   |   |   |     |   |   | DATARDY |

| Access | ess |   |   |   | R/W |   |   |         |

| Reset  |     |   |   |   |     |   |   | 0       |

#### **Bit 0 – DATARDY** Data Ready Interrupt Enable

Writing a '1' to this bit will clear the Data Ready Interrupt Enable bit, which disables the corresponding interrupt request.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The DATARDY interrupt is disabled. |

| 1     | The DATARDY interrupt is enabled.  |

#### 39.8.4 Interrupt Enable Set

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0       |

|--------|---|---|---|-----|---|---|---|---------|

|        |   |   |   |     |   |   |   | DATARDY |

| Access |   |   |   | R/W |   |   |   |         |

| Reset  |   |   |   |     |   |   |   | 0       |

#### **Bit 0 – DATARDY** Data Ready Interrupt Enable

Writing a '1' to this bit will set the Data Ready Interrupt Enable bit, which enables the corresponding interrupt request.

|   | /alue | Description                        |

|---|-------|------------------------------------|

| ( | )     | The DATARDY interrupt is disabled. |

| - | L     | The DATARDY interrupt is enabled.  |

# 46.5 Supply Characteristics

### Table 46-4. Supply Characteristics

| Symbol             | Voltage |      |       |  |

|--------------------|---------|------|-------|--|

|                    | Min.    | Max. | Units |  |

| V <sub>DDIO</sub>  | 1.62    | 3.63 | V     |  |

| V <sub>DDANA</sub> | 1.62    | 3.63 | V     |  |

#### Table 46-5. Supply Slew Rates<sup>(1)</sup>

| Symbol             | Fall Rate | Rise Rate | Units |  |

|--------------------|-----------|-----------|-------|--|

|                    | Max.      | Max.      |       |  |

| V <sub>DDIO</sub>  | 0.05      | 0.1       | V/µs  |  |

| V <sub>DDANA</sub> | 0.05      | 0.1       | V/µs  |  |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

# 46.6 Maximum Clock Frequencies

# Table 46-6. Maximum GCLK Generator Output Frequencies<sup>(1)</sup>

| Symbol                     | Description                     | Conditions | Fmax |     | Units |  |

|----------------------------|---------------------------------|------------|------|-----|-------|--|

|                            |                                 |            | PL0  | PL2 | -     |  |

| F <sub>gclkgen</sub> [0:2] | GCLK Generator output Frequency | -          | 24   | 96  | MHz   |  |

| F <sub>gclkgen</sub> [3:4] |                                 | -          | 12   | 48  | MHz   |  |

#### Note:

1. These values are based on simulation. They are not covered by production test limits or characterization.

#### Table 46-7. Maximum Peripheral Clock Frequencies<sup>(1)</sup>

| Symbol                    | Description                       | Conditions | Fmax |     | Units |

|---------------------------|-----------------------------------|------------|------|-----|-------|

|                           |                                   |            | PL0  | PL2 |       |

| f <sub>CPU</sub>          | CPU clock frequency               | -          | 8    | 32  | MHz   |

| f <sub>AHB</sub>          | AHB clock frequency               | -          | 8    | 32  | MHz   |

| f <sub>APBA</sub>         | APBA clock frequency              | -          | 8    | 32  | MHz   |

| f <sub>APBB</sub>         | APBB clock frequency              | -          |      |     |       |

| f <sub>APBC</sub>         | APBC clock frequency              | -          |      |     |       |

| f <sub>GCLK_DFLLULP</sub> | DFLLULP Reference clock frequency | -          | 1    | 4   | MHz   |