# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e14a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

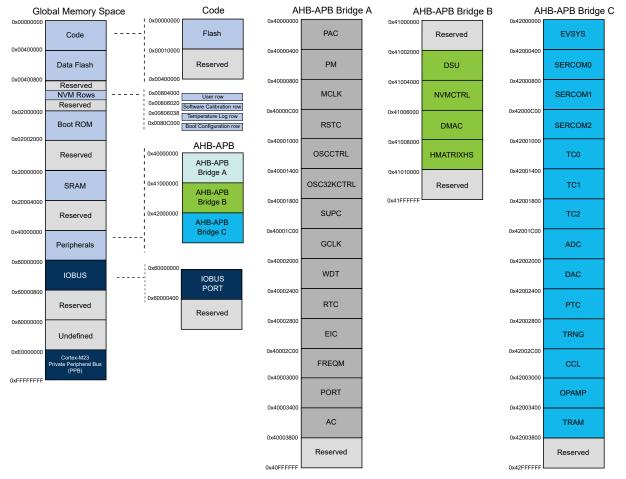

## 9. Product Mapping

Figure 9-1. SAM L10 Product Mapping

## 16.12.14 CoreSight ROM Table Entry 1

| Name:     | ENTRY1               |

|-----------|----------------------|

| Offset:   | 0x1004               |

| Reset:    | 0xXXXXX00X           |

| Property: | PAC Write-Protection |

|           |                      |

| Bit    | 31            | 30   | 29      | 28   | 27       | 26 | 25  | 24    |  |  |  |

|--------|---------------|------|---------|------|----------|----|-----|-------|--|--|--|

|        | ADDOFF[19:12] |      |         |      |          |    |     |       |  |  |  |

| Access | R             | R    | R       | R    | R        | R  | R   | R     |  |  |  |

| Reset  | x             | х    | x       | x    | х        | x  | x   | x     |  |  |  |

|        |               |      |         |      |          |    |     |       |  |  |  |

| Bit    | 23            | 22   | 21      | 20   | 19       | 18 | 17  | 16    |  |  |  |

|        |               |      |         | ADDO | FF[11:4] |    |     |       |  |  |  |

| Access | R             | R    | R       | R    | R        | R  | R   | R     |  |  |  |

| Reset  | x             | х    | x       | х    | х        | х  | х   | x     |  |  |  |

|        |               |      |         |      |          |    |     |       |  |  |  |

| Bit    | 15            | 14   | 13      | 12   | 11       | 10 | 9   | 8     |  |  |  |

|        |               | ADDO | FF[3:0] |      |          |    |     |       |  |  |  |

| Access | R             | R    | R       | R    |          |    |     |       |  |  |  |

| Reset  | x             | x    | x       | x    |          |    |     |       |  |  |  |

|        |               |      |         |      |          |    |     |       |  |  |  |

| Bit    | 7             | 6    | 5       | 4    | 3        | 2  | 1   | 0     |  |  |  |

|        |               |      |         |      |          |    | FMT | EPRES |  |  |  |

| Access |               |      |         |      |          |    | R   | R     |  |  |  |

| Reset  |               |      |         |      |          |    | 1   | x     |  |  |  |

#### Bits 31:12 - ADDOFF[19:0] Address Offset

The base address of the component, relative to the base address of this ROM table.

#### Bit 1 – FMT Format

Always read as '1', indicating a 32-bit ROM table.

#### Bit 0 – EPRES Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

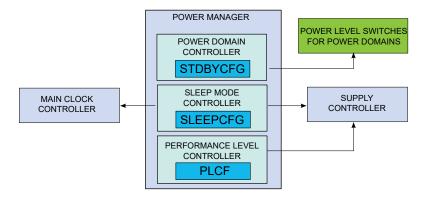

## 22.3 Block Diagram

Figure 22-1. PM Block Diagram

## 22.4 Signal Description

Not applicable.

## 22.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 22.5.1 I/O Lines

Not applicable.

## 22.5.2 Clocks

The PM bus clock (CLK\_PM\_APB) can be enabled and disabled in the Main Clock module. If this clock is disabled, it can only be re-enabled by a system reset.

## 22.5.3 DMA

Not applicable.

## 22.5.4 Interrupts

The interrupt request line is connected to the interrupt controller. Using the PM interrupt requires the interrupt controller to be configured first.

## 22.5.5 Events

Not applicable.

## 22.5.6 Debug Operation

When the CPU is halted in debug mode, the PM continues normal operation. If standby sleep mode is requested by the system while in debug mode, the power domains are not turned off. As a consequence, power measurements while in debug mode are not relevant.

If OFF sleep mode is requested by the system while in debug mode, the core domains are kept on, and the debug modules are kept running to allow the debugger to access internal registers. When exiting the OFF mode upon a reset condition, the core domains are reset except the debug logic, allowing users to keep using their current debug session.

© 2018 Microchip Technology Inc.

## 22.8.1 Sleep Configuration

| Name:     | SLEEPCFG             |

|-----------|----------------------|

| Offset:   | 0x01                 |

| Reset:    | 0x2                  |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1             | 0   |

|--------|---|---|---|---|---|-----|---------------|-----|

|        |   |   |   |   |   | 5   | SLEEPMODE[2:0 | )]  |

| Access |   |   |   |   |   | R/W | R/W           | R/W |

| Reset  |   |   |   |   |   | 0   | 0             | 0   |

## Bits 2:0 – SLEEPMODE[2:0] Sleep Mode

**Note:** A small latency happens between the store instruction and actual writing of the SLEEPCFG register due to bridges. Software has to make sure the SLEEPCFG register reads the wanted value before issuing WFI instruction.

| Value | Name     | Definition                                                      |

|-------|----------|-----------------------------------------------------------------|

| 0x0   | Reserved | Reserved                                                        |

| 0x1   | Reserved | Reserved                                                        |

| 0x2   | IDLE     | CPU, AHBx, and APBx clocks are OFF                              |

| 0x3   | Reserved | Reserved                                                        |

| 0x4   | STANDBY  | ALL clocks are OFF, unless requested by sleepwalking peripheral |

| 0x5   | Reserved | Reserved                                                        |

| 0x6   | OFF      | All power domains are powered OFF                               |

| 0x7   | Reserved | Reserved                                                        |

#### 25.8.1 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|----|----|----|----|------------|----------|----------|----------|

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 23 | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 15 | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |    |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |    |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |    |    |    |    | 0          | 0        |          | 0        |

|        |    |    |    |    |            |          |          |          |

| Bit    | 7  | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |    |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access | -  |    |    |    |            | R/W      | R/W      | R/W      |

| Reset  |    |    |    |    |            | 0        | 0        | 0        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit will clear on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY).

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Low Power Ready interrupt is disabled.                                                                                     |

| 1     | The Low Power Ready interrupt is enabled and an interrupt request will be generated when the ULPVREFRDY Interrupt Flag is set. |

Bit 10 – VCORERDY VDDCORE Voltage Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the VDDCORE Ready Interrupt Enable bit, which disables the VDDCORE Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The VDDCORE Ready interrupt is disabled.                                                                                   |

| 1     | The VDDCORE Ready interrupt is enabled and an interrupt request will be generated when the VCORERDY Interrupt Flag is set. |

## 25.8.4 Status

| Name:     | STATUS                                                 |

|-----------|--------------------------------------------------------|

| Offset:   | 0x0C                                                   |

| Reset:    | x,y initially determined from NVM User Row after reset |

| Property: | -                                                      |

| Bit    | 31 | 30 | 29 | 28         | 27 | 26       | 25       | 24       |

|--------|----|----|----|------------|----|----------|----------|----------|

|        |    |    |    |            |    |          |          |          |

| Access |    |    |    |            |    |          |          |          |

| Reset  |    |    |    |            |    |          |          |          |

|        |    |    |    |            |    |          |          |          |

| Bit    | 23 | 22 | 21 | 20         | 19 | 18       | 17       | 16       |

|        |    |    |    |            |    |          |          |          |

| Access |    |    |    |            |    |          |          |          |

| Reset  |    |    |    |            |    |          |          |          |

|        |    |    |    |            |    |          |          |          |

| Bit    | 15 | 14 | 13 | 12         | 11 | 10       | 9        | 8        |

|        |    |    |    | ULPVREFRDY |    | VCORERDY |          | VREGRDY  |

| Access |    |    |    | R          |    | R        |          | R        |

| Reset  |    |    |    | х          |    | 1        |          | 1        |

|        |    |    |    |            |    |          |          |          |

| Bit    | 7  | 6  | 5  | 4          | 3  | 2        | 1        | 0        |

|        |    |    |    |            |    | B33SRDY  | BOD33DET | BOD33RDY |

| Access |    | •  | •  | •          |    | R        | R        | R        |

| Reset  |    |    |    |            |    | 0        | 0        | У        |

## Bit 12 – ULPVREFRDY Low Power Voltage Reference Ready

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The ULPVREF voltage is not as expected.    |

| 1     | The ULPVREF voltage is the target voltage. |

## Bit 10 - VCORERDY VDDCORE Voltage Ready

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The VDDCORE voltage is not as expected.    |

| 1     | The VDDCORE voltage is the target voltage. |

### Bit 8 – VREGRDY Voltage Regulator Ready

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The selected voltage regulator in VREG.SEL is not ready.                               |

| 1     | The voltage regulator selected in VREG.SEL is ready and the core domain is supplied by |

|       | this voltage regulator.                                                                |

## Bit 2 – B33SRDY BOD33 Synchronization Ready

## 27.10.12 Compare n Value in COUNT16 mode (CTRLA.MODE=1)

| Name:     | COMP                                     |

|-----------|------------------------------------------|

| Offset:   | 0x20 + n*0x02 [n=01]                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15         | 14  | 13  | 12  | 11  | 10  | 9   | 8   |  |  |  |  |

|--------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

|        | COMP[15:8] |     |     |     |     |     |     |     |  |  |  |  |

| Access | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

|        |            |     |     |     |     |     |     |     |  |  |  |  |

| Bit    | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|        | COMP[7:0]  |     |     |     |     |     |     |     |  |  |  |  |

| Access | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

## Bits 15:0 - COMP[15:0] Compare Value

The 16-bit value of COMPn is continuously compared with the 16-bit COUNT value. When a match occurs, the Compare n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMPn) is set on the next counter cycle.

## SAM L10/L11 Family

DMAC – Direct Memory Access Controller

| Value | Description                  |

|-------|------------------------------|

| 0     | The descriptor is not valid. |

| 1     | The descriptor is valid.     |

### 28.10.2 Block Transfer Count

Name: BTCNT Offset: 0x02 Property: -

The BTCNT register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 15 | 14          | 13 | 12   | 11      | 10 | 9 | 8 |  |  |  |  |  |

|--------|----|-------------|----|------|---------|----|---|---|--|--|--|--|--|

|        |    | BTCNT[15:8] |    |      |         |    |   |   |  |  |  |  |  |

| Access |    |             |    |      |         |    |   |   |  |  |  |  |  |

| Reset  |    |             |    |      |         |    |   |   |  |  |  |  |  |

|        |    |             |    |      |         |    |   |   |  |  |  |  |  |

| Bit    | 7  | 6           | 5  | 4    | 3       | 2  | 1 | 0 |  |  |  |  |  |

|        |    |             |    | BTCN | IT[7:0] |    |   |   |  |  |  |  |  |

| Access |    |             |    |      |         |    |   |   |  |  |  |  |  |

Reset

Bits 15:0 – BTCNT[15:0] Block Transfer Count

This bit group holds the 16-bit block transfer count.

During a transfer, the internal counter value is decremented by one after each beat transfer. The internal counter is written to the corresponding write-back memory section for the DMA channel when the DMA channel loses priority, is suspended or gets disabled. The DMA channel can be disabled by a complete transfer, a transfer error or by software.

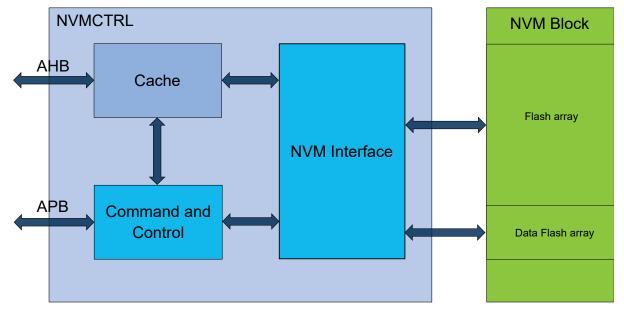

## 30. NVMCTRL – Nonvolatile Memory Controller

## 30.1 Overview

Non-Volatile Memory (NVM) is a reprogrammable Flash memory that retains program and data storage even with power off. It embeds three separate arrays namely FLASH, Data FLASH and AUX FLASH. The Data FLASH array can be programmed while reading the FLASH array. It is intended to store data while executing from the FLASH without stalling. AUX FLASH stores data needed during the device startup such as calibration and system configuration. The NVM Controller (NVMCTRL) connects to the AHB and APB bus interfaces for system access to the NVM block. The AHB interface is used for reads and writes to the NVM block, while the APB interface is used for commands and configuration.

## 30.2 Features

- 32-bit AHB interface for reads and writes

- Write-While-Read (WWR) Data Flash

- All NVM Sections are Memory Mapped to the AHB, Including Calibration and System Configuration

- 32-bit APB Interface for Commands and Control

- Programmable Wait States for Read Optimization

- 6 Regions can be Individually Protected or Unprotected

- Additional Protection for Bootloader

- Interface to Power Manager for Power-Down of Flash Blocks in Sleep Modes

- Can Optionally Wake-up on Exit from Sleep or on First Access

- Direct-mapped Cache

- TrustZone Support (SAM L11)

**Note:** A register with property "Enable-Protected" may contain bits that are *not* enable-protected.

## 30.3 Block Diagram

Figure 30-1. Block Diagram

## 30.4 Signal Description

Not applicable.

## 30.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described in the following sections.

## 30.5.1 Power Management

The NVMCTRL will continue to operate in any sleep mode where the selected source clock is running. The NVMCTRL interrupts can be used to wake up the device from sleep modes.

The Power Manager will automatically put the NVM block into a low-power state when entering sleep mode. This is based on the Control B register (CTRLB) SLEEPPRM bit setting. Refer to the 30.8.2 CTRLB.SLEEPPRM register description for more details. The NVM block goes into low-power mode automatically when the device enters STANDBY mode regardless of SLEEPPRM. The NVM Page Buffer is lost when the NVM goes into low power mode therefore a write command must be issued prior entering the NVM low power mode. NVMCTRL SLEEPPRM can be disabled to avoid such loss when the CPU goes into sleep except if the device goes into STANDBY mode for which there is no way to retain the Page Buffer.

## **Related Links**

22. PM – Power Manager

## 30.5.2 Clocks

Two synchronous clocks are used by the NVMCTRL. One is provided by the AHB bus (CLK\_NVMCTRL\_AHB) and the other is provided by the APB bus (CLK\_NVMCTRL\_APB). For higher

### 31.8.2 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x004                |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|---|---|---|---|---|---|-----|-----|

|        |   |   |   |   |   |   | DRP | ERR |

| Access |   |   |   |   |   |   | R/W | R/W |

| Reset  |   |   |   |   |   |   | 0   | 0   |

**Bit 1 – DRP** Data Remanence Prevention Complete Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Data Remanence Prevention Complete Interrupt Enable bit, which disables the data remanence prevention complete interrupt.

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | Data remanence prevention complete interrupt is disabled. |

| 1     | Data remanence prevention complete interrupt is enabled.  |

Bit 0 – ERR TrustRAM Read Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the TrustRAM Read Error Interrupt Enable bit, which disables the TrustRAM read error interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | TrustRAM read error interrupt is disabled. |

| 1     | TrustRAM read error interrupt is enabled.  |

## SAM L10/L11 Family

## EVSYS – Event System

| _      |             |          |          |          |  |     |          |        |        |

|--------|-------------|----------|----------|----------|--|-----|----------|--------|--------|

| Offset | Name        | Bit Pos. |          |          |  |     |          |        |        |

| 0x26   | CHINTFLAG0  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x27   | CHSTATUS0   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0x28   | CHANNEL1    | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| UNEO   | OF # HILLET | 23:16    |          |          |  |     |          |        |        |

|        |             | 31:24    |          |          |  |     |          |        |        |

| 0x2C   | CHINTENCLR1 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2D   | CHINTENSET1 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2E   | CHINTFLAG1  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x2F   | CHSTATUS1   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0x30   | CHANNEL2    | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| 0,00   | CHANNELZ    | 23:16    |          |          |  |     |          |        |        |

|        |             | 31:24    |          |          |  |     |          |        |        |

| 0x34   | CHINTENCLR2 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x35   | CHINTENSET2 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x36   | CHINTFLAG2  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x37   | CHSTATUS2   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 0.20   | CHANNEL3    | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| 0x38   |             | 23:16    |          |          |  |     |          |        |        |

|        |             | 31:24    |          |          |  |     |          |        |        |

| 0x3C   | CHINTENCLR3 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3D   | CHINTENSET3 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3E   | CHINTFLAG3  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x3F   | CHSTATUS3   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        | 1      |

| 040    |             | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATH   | H[1:0] |

| 0x40   | CHANNEL4    | 23:16    |          |          |  |     |          |        |        |

|        |             | 31:24    |          |          |  |     |          |        |        |

| 0x44   | CHINTENCLR4 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x45   | CHINTENSET4 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x46   | CHINTFLAG4  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x47   | CHSTATUS4   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        |        |

| 010    |             | 15:8     | ONDEMAND | RUNSTDBY |  | EDG | SEL[1:0] | PATI   | H[1:0] |

| 0x48   | CHANNEL5    | 23:16    |          |          |  |     |          |        |        |

|        |             | 31:24    |          |          |  |     |          |        |        |

| 0x4C   | CHINTENCLR5 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4D   | CHINTENSET5 | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4E   | CHINTFLAG5  | 7:0      |          |          |  |     |          | EVD    | OVR    |

| 0x4F   | CHSTATUS5   | 7:0      |          |          |  |     |          | BUSYCH | RDYUSR |

|        |             | 7:0      |          |          |  | EVG | EN[5:0]  |        | 1      |

| a ==   |             | 15:8     | ONDEMAND | RUNSTDBY |  |     | SEL[1:0] | PATH   | H[1:0] |

| 0x50   | CHANNEL6    | 00.40    |          |          |  |     |          |        |        |

|        |             | 23:16    |          |          |  |     |          |        |        |

## Bit 2 – RXC Receive Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

**Bit 1 – TXC** Transmit Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Transmit Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

Bit 0 – DRE Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

### Related Links

15. PAC - Peripheral Access Controller

## 36.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

### 36.5.10 Analog Connections

Not applicable.

## 36.6 Functional Description

## 36.6.1 Principle of Operation

The SPI is a high-speed synchronous data transfer interface It allows high-speed communication between the device and peripheral devices.

The SPI can operate as master or slave. As master, the SPI initiates and controls all data transactions. The SPI is single buffered for transmitting and double buffered for receiving.

When transmitting data, the Data register can be loaded with the next character to be transmitted during the current transmission.

When receiving, the data is transferred to the two-level or four-level receive buffer, and the receiver is ready for a new character.

The SPI transaction format is shown in SPI Transaction Format. Each transaction can contain one or more characters. The character size is configurable, and can be either 8 or 9 bits.

#### Figure 36-2. SPI Transaction Format

|           | •        | Character   | <br>Transaction |             |  |

|-----------|----------|-------------|-----------------|-------------|--|

| MOSI/MISO | $\times$ | Character 0 | Character 1     | Character 2 |  |

| _SS       |          |             |                 |             |  |

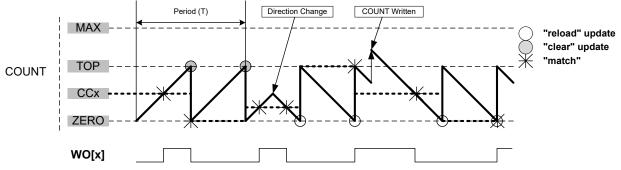

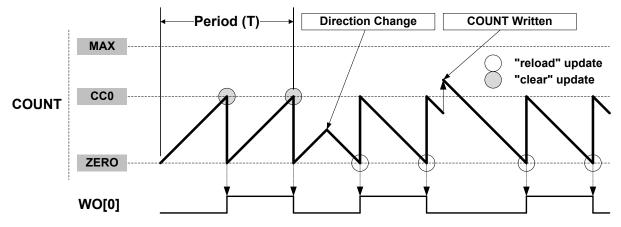

## Match Frequency Generation (MFRQ)

For Match Frequency Generation, the period time (T) is controlled by the CC0 register instead of PER or MAX. WO[0] toggles on each update condition.

Figure 38-5. Match Frequency Operation

## Normal Pulse-Width Modulation Operation (NPWM)

NPWM uses single-slope PWM generation.

For single-slope PWM generation, the period time (T) is controlled by the TOP value, and CCx controls the duty cycle of the generated waveform output. When up-counting, the WO[x] is set at start or compare match between the COUNT and TOP values, and cleared on compare match between COUNT and CCx register values. When down-counting, the WO[x] is cleared at start or compare match between the COUNT and ZERO values, and set on compare match between COUNT and CCx register values.

The following equation calculates the exact resolution for a single-slope PWM ( $R_{PWM SS}$ ) waveform:

$$R_{\rm PWM\_SS} = \frac{\log(\rm TOP+1)}{\log(2)}$$

The PWM frequency ( $f_{PWM_SS}$ ) depends on TOP value and the peripheral clock frequency ( $f_{GCLK_TC}$ ), and can be calculated by the following equation:

$$f_{\rm PWM\_SS} = \frac{f_{\rm GCLK\_TC}}{\rm N(TOP+1)}$$

Where N represents the prescaler divider used (1, 2, 4, 8, 16, 64, 256, 1024).

## Match Pulse-Width Modulation Operation (MPWM)

In MPWM, the output of WO[1] is depending on CC1 as shown in the figure below. On every overflow/ underflow, a one-TC-clock-cycle negative pulse is put out on WO[0] (not shown in the figure).

## 38.7.1.14 Period Value, 8-bit Mode

Name:PEROffset:0x1BReset:0xFFProperty:Write-Synchronized

| Bit    | 7        | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|----------|-----|-----|-----|-----|-----|-----|-----|--|--|

|        | PER[7:0] |     |     |     |     |     |     |     |  |  |

| Access | R/W      | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 1   |  |  |

## Bits 7:0 – PER[7:0] Period Value

These bits hold the value of the Period Buffer register PERBUF. The value is copied to PER register on UPDATE condition.

## 38.7.3.10 Driver Control

| Name:     | DRVCTRL                                |

|-----------|----------------------------------------|

| Offset:   | 0x0D                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | INVENx |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

## Bit 0 – INVENx Output Waveform x Invert Enable

Bit x of INVEN[1:0] selects inversion of the output or capture trigger input of channel x.

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Disable inversion of the WO[x] output and IO input pin. |

| 1     | Enable inversion of the WO[x] output and IO input pin.  |

## SAM L10/L11 Family

AC – Analog Comparators

## 42.7 Register Summary

| Offset           | Name      | Bit Pos. |      |          |             |           |           |         |             |         |

|------------------|-----------|----------|------|----------|-------------|-----------|-----------|---------|-------------|---------|

| 0x00             | CTRLA     | 7:0      |      |          |             |           |           |         | ENABLE      | SWRST   |

| 0x01             | CTRLB     | 7:0      |      |          |             |           |           |         | STARTx      | STARTx  |

| 0x02             | EVCTRL    | 7:0      |      |          |             | WINEO0    |           |         | COMPEOx     | COMPEOx |

| 0x02             | EVCIRE    | 15:8     |      |          | INVEIx      | INVEIx    |           |         | COMPEIx     | COMPEIx |

| 0x04             | INTENCLR  | 7:0      |      |          |             | WIN0      |           |         | COMPx       | COMPx   |

| 0x05             | INTENSET  | 7:0      |      |          |             | WIN0      |           |         | COMPx       | COMPx   |

| 0x06             | INTFLAG   | 7:0      |      |          |             | WIN0      |           |         | COMPx       | COMPx   |

| 0x07             | STATUSA   | 7:0      |      |          | WSTAT       | E0[1:0]   |           |         | STATEx      | STATEx  |

| 0x08             | STATUSB   | 7:0      |      |          |             |           |           |         | READYx      | READYx  |

| 0x09             | DBGCTRL   | 7:0      |      |          |             |           |           |         |             | DBGRUN  |

| 0x0A             | WINCTRL   | 7:0      |      |          |             |           |           | WINTS   | EL0[1:0]    | WEN0    |

| 0x0B             | Reserved  |          |      |          |             |           |           |         |             |         |

| 0x0C             | SCALER0   | 7:0      |      |          |             | 1         | VALU      | E[5:0]  | 1           | 1       |

| 0x0D             | SCALER1   | 7:0      |      |          |             |           | VALU      | E[5:0]  |             |         |

| 0x0E<br><br>0x0F | Reserved  |          |      |          |             |           |           |         |             |         |

|                  |           | 7:0      |      | RUNSTDBY |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 010              | COMPCTRL0 | 15:8     | SWAP |          | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x10             | COMPCTRLU | 23:16    |      |          | HYS.        | T[1:0]    | HYSTEN    |         | SPEE        | D[1:0]  |

|                  |           | 31:24    |      |          | OUT         | [1:0]     |           |         | FLEN[2:0]   |         |

|                  |           | 7:0      |      | RUNSTDBY |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0.14             |           | 15:8     | SWAP |          | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x14             | COMPCTRL1 | 23:16    |      |          | HYS.        | T[1:0]    | HYSTEN    |         | SPEE        | D[1:0]  |

|                  |           | 31:24    |      |          | Ουτ         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x18             |           |          |      |          |             |           |           |         |             |         |

| <br>0x1F         | Reserved  |          |      |          |             |           |           |         |             |         |

|                  |           | 7:0      |      |          |             | COMPCTRLx | COMPCTRLx | WINCTRL | ENABLE      | SWRST   |

| 0.00             | OVNODU OV | 15:8     |      |          |             |           |           |         |             |         |

| 0x20             | SYNCBUSY  | 23:16    |      |          |             |           |           |         |             |         |

|                  |           | 31:24    |      |          |             |           |           |         |             |         |

## 42.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the DAC is reset. See INTFLAG register for details on how to clear interrupt flags.

All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated..

## 43.6.5 Events

The DAC Controller can generate the following output events:

• Data Buffer Empty (EMPTY): Generated when the internal data buffer of the DAC is empty. Refer to DMA Operation for details.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.EMPTYEO) enables the corresponding output event. Writing a '0' to this bit disables the corresponding output event.

The DAC can take the following action on an input event:

Start Conversion (START): DATABUF value is transferred into DATA as soon as the DAC is ready for the next conversion, and then conversion is started. START is considered as asynchronous to GCLK\_DAC thus it is resynchronized in DAC Controller. Refer to 43.6.2.4 Digital to Analog Conversion for details.

Writing a '1' to an Event Input bit in the Event Control register (EVCTRL.STARTEI) enables the corresponding action on an input event. Writing a '0' to this bit disables the corresponding action on input event.

**Note:** When several events are connected to the DAC Controller, the enabled action will be taken on any of the incoming events.

By default, DAC Controller detects rising edge events. Falling edge detection can be enabled by writing a '1' to EVCTRL.INVEIx.

## **Related Links**

33. EVSYS – Event System

## 43.6.6 Sleep Mode Operation

The generic clock for the DAC is running in idle sleep mode. If the Run In Standby bit in the Control A register (CTRLA.RUNSTDBY) is one, the DAC output buffer will keep its value in standby sleep mode. If CTRLA.RUNSTDBY is zero, the DAC output buffer will be disabled in standby sleep mode.

## 43.6.7 Synchronization

Due to the asynchronicity between main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read. A register can require:

- Synchronization when written

- Synchronization when read

- Synchronization when written and read

- No synchronization

When executing an operation that requires synchronization, the corresponding status bit in the Synchronization Busy register (SYNCBUSY) will be set immediately, and cleared when synchronization is complete.