# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M23                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e15a-mft |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5. Signal Descriptions List

The following table provides details on signal names classified by peripherals.

### Table 5-1. Signal Descriptions List

| Signal Name                         | Function                                                         | Туре                                                                |  |  |

|-------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Generic Clock Generator - GCLK      |                                                                  |                                                                     |  |  |

| GCLK_IO[4:0]                        | Generators Clock Source (Input) or Generic Clock Signal (Output) | Digital I/O                                                         |  |  |

| Oscillators Control - OSCCTRL       |                                                                  |                                                                     |  |  |

| XIN                                 | Crystal Oscillator or External Clock Input                       | Analog Input (Crystal Oscillator)/Digital Input (External Clock)    |  |  |

| XOUT                                | Crystal Oscillator Output                                        | Analog Output                                                       |  |  |

| 32 kHz Oscillators Control - OSC32K | CTRL                                                             |                                                                     |  |  |

| XIN32                               | 32.768 kHz Crystal Oscillator or External Clock Input            | Analog Input (Crystal Oscillator)/Digital Input<br>(External Clock) |  |  |

| XOUT32                              | 32.768 kHz Crystal Oscillator Output                             | Analog Output                                                       |  |  |

| Serial Communication Interface - SE | RCOMx                                                            |                                                                     |  |  |

| PAD[3:0]                            | General SERCOM Pins                                              | Digital I/O                                                         |  |  |

| Timer Counter - TCx                 |                                                                  |                                                                     |  |  |

| WO[1:0]                             | Capture Inputs or Waveform Outputs                               | Digital I/O                                                         |  |  |

| Real Timer Clock - RTC              |                                                                  |                                                                     |  |  |

| IN[3:0]                             | Tamper Detection Inputs                                          | Digital Input                                                       |  |  |

| OUT[3:0]                            | Tamper Detection Outputs                                         | Digital Output                                                      |  |  |

| Analog Comparators - AC             |                                                                  |                                                                     |  |  |

| AIN[3:0]                            | AC Comparator Inputs                                             | Analog Input                                                        |  |  |

| CMP[1:0]                            | AC Comparator Outputs                                            | Digital Output                                                      |  |  |

| Analog Digital Converter - ADC      |                                                                  |                                                                     |  |  |

| AIN[9:0]                            | ADC Input Channels                                               | Analog Input                                                        |  |  |

| VREFA <sup>(1)</sup>                | ADC External Reference Voltage A                                 | Analog Input                                                        |  |  |

| VREFB                               | ADC External Reference Voltage B                                 | Analog Input                                                        |  |  |

| Digital Analog Converter - DAC      |                                                                  |                                                                     |  |  |

| VOUT                                | DAC Voltage Output                                               | Analog Output                                                       |  |  |

| VREFA <sup>(1)</sup>                | DAC External Reference Voltage A                                 | Analog Input                                                        |  |  |

| Operational Amplifier - OPAMP       |                                                                  |                                                                     |  |  |

| OA[2:0]NEG                          | OPAMP Negative Inputs                                            | Analog Input                                                        |  |  |

| OA[2:0]POS                          | OPAMP Positive Inputs                                            | Analog Input                                                        |  |  |

| OA0OUT / OA2OUT                     | OPAMP Outputs                                                    | Analog Output                                                       |  |  |

| Peripheral Touch Controller - PTC   |                                                                  |                                                                     |  |  |

| XY[19:0]                            | X-lines and Y-lines                                              | Digital Output (X-line) /Analog I/O (Y-line)                        |  |  |

| Custom Control Logic - CCL          |                                                                  |                                                                     |  |  |

| IN[5:0]                             | Inputs to lookup table                                           | Digital Output                                                      |  |  |

| OUT[1:0]                            | Outputs from lookup table                                        | Digital Input                                                       |  |  |

# 16.12.5 Length

| LENGTH               |

|----------------------|

| 0x0008               |

| 0x0000000            |

| PAC Write-Protection |

|                      |

| Bit    | 31          | 30            | 29  | 28    | 27       | 26  | 25  | 24  |  |  |  |  |

|--------|-------------|---------------|-----|-------|----------|-----|-----|-----|--|--|--|--|

|        |             | LENGTH[29:22] |     |       |          |     |     |     |  |  |  |  |

| Access | R/W         | R/W           | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0           | 0             | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |             |               |     |       |          |     |     |     |  |  |  |  |

| Bit    | 23          | 22            | 21  | 20    | 19       | 18  | 17  | 16  |  |  |  |  |

|        |             |               |     | LENGT | H[21:14] |     |     |     |  |  |  |  |

| Access | R/W         | R/W           | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0           | 0             | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |             |               |     |       |          |     |     |     |  |  |  |  |

| Bit    | 15          | 14            | 13  | 12    | 11       | 10  | 9   | 8   |  |  |  |  |

|        |             |               |     | LENGT | H[13:6]  |     |     |     |  |  |  |  |

| Access | R/W         | R/W           | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0           | 0             | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |  |

|        |             |               |     |       |          |     |     |     |  |  |  |  |

| Bit    | 7           | 6             | 5   | 4     | 3        | 2   | 1   | 0   |  |  |  |  |

|        | LENGTH[5:0] |               |     |       |          |     |     |     |  |  |  |  |

| Access | R/W         | R/W           | R/W | R/W   | R/W      | R/W |     |     |  |  |  |  |

| Reset  | 0           | 0             | 0   | 0     | 0        | 0   |     |     |  |  |  |  |

## Bits 31:2 - LENGTH[29:0] Length

Length in words needed for memory operations.

# SUPC – Supply Controller

| Value | Name | Description                      |

|-------|------|----------------------------------|

| 0x2   | INT  | The BOD33 generates an interrupt |

| 0x3   | -    | Reserved                         |

#### Bit 2 – HYST Hysteresis

This bit indicates whether hysteresis is enabled for the BOD33 threshold voltage.

This bit is loaded from NVM User Row at start-up.

This bit is not synchronized.

| Value | Description         |

|-------|---------------------|

| 0     | No hysteresis.      |

| 1     | Hysteresis enabled. |

### Bit 1 - ENABLE Enable

This bit is loaded from NVM User Row at start-up.

This bit is not enable-protected.

| V | alue | Description        |

|---|------|--------------------|

| 0 |      | BOD33 is disabled. |

| 1 |      | BOD33 is enabled.  |

constantly running timer that is configured to a predefined time-out period. Before the end of the time-out period, the WDT should be set back, or else, a system Reset is issued.

The WDT has two modes of operation, Normal mode and Window mode. Both modes offer the option of Early Warning interrupt generation. The description for each of the basic modes is given below. The settings in the Control A register (CTRLA) and the Interrupt Enable register (handled by INTENCLR/INTENSET) determine the mode of operation:

#### Table 26-1. WDT Operating Modes

| CTRLA.ENABLE | CTRLA.WEN | Interrupt Enable | Mode                                     |

|--------------|-----------|------------------|------------------------------------------|

| 0            | x         | x                | Stopped                                  |

| 1            | 0         | 0                | Normal mode                              |

| 1            | 0         | 1                | Normal mode with Early Warning interrupt |

| 1            | 1         | 0                | Window mode                              |

| 1            | 1         | 1                | Window mode with Early Warning interrupt |

#### 26.6.2 Basic Operation

#### 26.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the WDT is disabled (CTRLA.ENABLE=0):

- Control A register (CTRLA), except the Enable bit (CTRLA.ENABLE)

- Configuration register (CONFIG)

- Early Warning Interrupt Control register (EWCTRL)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'.

The WDT can be configured only while the WDT is disabled. The WDT is configured by defining the required Time-Out Period bits in the Configuration register (CONFIG.PER). If Window mode operation is desired, the Window Enable bit in the Control A register must be set (CTRLA.WEN=1) and the Window Period bits in the Configuration register (CONFIG.WINDOW) must be defined.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

#### 26.6.2.2 Configurable Reset Values

After a Power-on Reset, some registers will be loaded with initial values from the NVM User Row.

This includes the following bits and bit groups:

- Enable bit in the Control A register, CTRLA.ENABLE

- Always-On bit in the Control A register, CTRLA.ALWAYSON

- Run In Standby Enable bit in the Control A register (CTRLA.RUNSTDBY)

- Watchdog Timer Windows Mode Enable bit in the Control A register, CTRLA.WEN

- Watchdog Timer Windows Mode Time-Out Period bits in the Configuration register, CONFIG.WINDOW

- Time-Out Period bits in the Configuration register, CONFIG.PER

- Early Warning Interrupt Time Offset bits in the Early Warning Interrupt Control register, EWCTRL.EWOFFSET

#### 28.8.11 Interrupt Status

| Name:<br>Offset:<br>Reset:<br>Property: |    | INTSTATUS<br>0x24<br>0x00000000<br>- |    |    |             |    |    |    |

|-----------------------------------------|----|--------------------------------------|----|----|-------------|----|----|----|

| Bit                                     | 31 | 30                                   | 29 | 28 | 27          | 26 | 25 | 24 |

|                                         |    |                                      |    |    |             |    |    |    |

| Access                                  |    |                                      |    |    |             |    |    |    |

| Reset                                   |    |                                      |    |    |             |    |    |    |

|                                         |    |                                      |    |    |             |    |    |    |

| Bit                                     | 23 | 22                                   | 21 | 20 | 19          | 18 | 17 | 16 |

|                                         |    |                                      |    |    |             |    |    |    |

| Access                                  |    |                                      |    |    |             |    |    |    |

| Reset                                   |    |                                      |    |    |             |    |    |    |

| 5.4                                     | 45 |                                      | 10 | 10 |             | 40 | 0  | 2  |

| Bit                                     | 15 | 14                                   | 13 | 12 | 11          | 10 | 9  | 8  |

| A                                       |    |                                      |    |    |             |    |    |    |

| Access<br>Reset                         |    |                                      |    |    |             |    |    |    |

| Reset                                   |    |                                      |    |    |             |    |    |    |

| Bit                                     | 7  | 6                                    | 5  | 4  | 3           | 2  | 1  | 0  |

|                                         |    | -                                    | -  |    | CHINTn[6:0] |    |    | -  |

| Access                                  |    | R                                    | R  | R  | R           | R  | R  | R  |

| Reset                                   |    | 0                                    | 0  | 0  | 0           | 0  | 0  | 0  |

|                                         |    | -                                    | -  | -  | -           | -  | -  | -  |

Bits 6:0 – CHINTn[6:0] Channel n Pending Interrupt [n=7..0]

This bit is set when Channel n has a pending interrupt/the interrupt request is received.

This bit is cleared when the corresponding Channel n interrupts are disabled or the interrupts sources are cleared.

#### 29.8.8 Interrupt Flag Status and Clear

| Name:     | INTFLAG    |

|-----------|------------|

| Offset:   | 0x14       |

| Reset:    | 0x00000000 |

| Property: | Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the external interrupt x (EXTINTx) is set as Non-Secure in the NONSEC register (NONSEC.EXTINTx bit).

| Bit    | 31        | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|        | NSCHK     |           |           |           |           |           |           |           |

| Access | RW/RW/RW  | •         |           |           | •         | •         | •         |           |

| Reset  | 0         |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |           |           |           |           |           |           |           |           |

| Access |           |           |           |           |           |           | ·         |           |

| Reset  |           |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 15        | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

|        |           |           |           |           |           |           |           |           |

| Access |           |           | 1         |           |           |           | •         |           |

| Reset  |           |           |           |           |           |           |           |           |

|        |           |           |           |           |           |           |           |           |

| Bit    | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|        |           |           |           | EXTIN     | IT[7:0]   |           |           |           |

| Access | RW/RW*/RW |

| Reset  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

#### Bit 31 – NSCHK Non-secure Check Interrupt

The flag is cleared by writing a '1' to it. This flag is set when write to either NONSEC and NSCHK register and if the related bit of NSCHK is enabled and the related bit of NONSEC is zero.

#### Bits 7:0 – EXTINT[7:0] External Interrupt

The flag bit x is cleared by writing a '1' to it.

This flag is set when EXTINTx pin matches the external interrupt sense configuration and will generate an interrupt request if 29.8.6 INTENCLR.EXTINT[x] or 29.8.7 INTENSET.EXTINT[x] is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the External Interrupt x flag.

# NVMCTRL – Nonvolatile Memory Controller

| or .   |          |          |     |              |        |          |          |            |         |  |

|--------|----------|----------|-----|--------------|--------|----------|----------|------------|---------|--|

| Offset | Name     | Bit Pos. |     |              |        |          |          |            |         |  |

|        |          | 15:8     |     |              | SLKE   | Y[7:0]   | -        |            |         |  |

| 0x22   | NSULCK   | 7:0      |     |              |        |          | DNS      | ANS        | BNS     |  |

| 0,22   | NOOLOK   | 15:8     |     |              | NSLKI  | EY[7:0]  |          |            |         |  |

|        |          | 7:0      |     |              | FLASH  | HP[7:0]  |          |            |         |  |

| 0x24   | PARAM    | 15:8     |     | FLASHP[15:8] |        |          |          |            |         |  |

| 0724   |          | 23:16    | DFL | ASHP[3:0]    |        |          |          | PSZ[2:0]   |         |  |

|        |          | 31:24    |     |              | DFLASI | HP[11:4] |          |            |         |  |

| 0x28   |          |          |     |              |        |          |          |            |         |  |

|        | Reserved |          |     |              |        |          |          |            |         |  |

| 0x2F   |          |          |     |              |        |          |          |            |         |  |

|        |          | 7:0      |     |              | DSCK   | EY[7:0]  |          |            |         |  |

| 0x30   | DSCC     | 15:8     |     |              | DSCKE  | Y[15:8]  |          |            |         |  |

| 0,30   | DSCC     | 23:16    |     |              | DSCKE  | Y[23:16] |          |            |         |  |

|        |          |          |     |              |        | DSCKE    | Y[29:24] |            |         |  |

|        | SECCTRL  | 7:0      | DXN |              |        | DSCEN    | SILACC   |            | TAMPEEN |  |

| 0x34   |          | 15:8     |     |              |        |          |          | TEROW[2:0] |         |  |

| 0x34   |          | 23:16    |     |              |        |          |          |            |         |  |

|        |          | 31:24    |     |              | KEY    | [7:0]    |          |            | 1       |  |

|        |          | 7:0      |     |              |        |          |          | BCWEN      | BCREN   |  |

| 020    | 00500    | 15:8     |     |              |        |          |          |            |         |  |

| 0x38   | SCFGB    | 23:16    |     |              |        |          |          |            |         |  |

|        |          | 31:24    |     |              |        |          |          |            |         |  |

|        |          | 7:0      |     |              |        |          |          |            | URWEN   |  |

|        | 005015   | 15:8     |     |              |        |          |          |            |         |  |

| 0x3C   | SCFGAD   | 23:16    |     |              |        |          |          |            |         |  |

|        |          | 31:24    |     |              |        |          |          |            |         |  |

|        |          | 7:0      |     |              |        |          |          |            | WRITE   |  |

|        |          | 15:8     |     |              |        |          |          |            |         |  |

| 0x40   | NONSEC   | 23:16    |     |              |        |          |          |            |         |  |

|        |          | 31:24    |     |              |        |          |          |            |         |  |

|        |          | 7:0      |     |              |        |          |          |            | WRITE   |  |

|        |          | 15:8     |     |              |        |          |          |            |         |  |

| 0x44   | NSCHK    | 23:16    |     |              |        |          |          |            |         |  |

|        |          | 31:24    |     |              |        |          |          |            |         |  |

### 30.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

© 2018 Microchip Technology Inc.

TRAM - TrustRAM

| Offset | Name   | Bit Pos. |             |

|--------|--------|----------|-------------|

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01D0 | RAM52  | 15:8     | DATA[15:8]  |

| 0.0100 | INAWJZ | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01D4 | RAM53  | 15:8     | DATA[15:8]  |

| 0,0121 |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01D8 | RAM54  | 15:8     | DATA[15:8]  |

| 0.0120 |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01DC | RAM55  | 15:8     | DATA[15:8]  |

| 0,0120 | RAM55  | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01E0 | RAM56  | 15:8     | DATA[15:8]  |

| UXUILU |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01E4 | RAM57  | 15:8     | DATA[15:8]  |

|        | RAIMST | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01E8 | RAM58  | 15:8     | DATA[15:8]  |

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01EC | RAM59  | 15:8     | DATA[15:8]  |

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01F0 | RAM60  | 15:8     | DATA[15:8]  |

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01F4 | RAM61  | 15:8     | DATA[15:8]  |

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

|        |        | 7:0      | DATA[7:0]   |

| 0x01F8 | RAM62  | 15:8     | DATA[15:8]  |

|        |        | 23:16    | DATA[23:16] |

|        |        | 31:24    | DATA[31:24] |

# PORT - I/O Pin Controller

|                | <b>,</b> |        |        |                       |

|----------------|----------|--------|--------|-----------------------|

| EVACT0         | EVACT1   | EVACT2 | EVACT3 | Executed Event Action |

| SET            | SET      | SET    | SET    | SET                   |

| CLR            | CLR      | CLR    | CLR    | CLR                   |

| All Other Comb | inations | TGL    |        |                       |

Table 32-3. Priority on Simultaneous SET/CLR/TGL Event Actions

Be careful when the event is output to pin. Due to the fact the events are received asynchronously, the I/O pin may have unpredictable levels, depending on the timing of when the events are received. When several events are output to the same pin, the lowest event line will get the access. All other events will be ignored.

#### **Related Links**

33. EVSYS - Event System

#### 32.6.6 PORT Access Priority

The PORT is accessed by different systems:

- The ARM<sup>®</sup> CPU through the ARM<sup>®</sup> single-cycle I/O port (IOBUS)

- The ARM<sup>®</sup> CPU through the high-speed matrix and the AHB/APB bridge (APB)

- EVSYS through four asynchronous input events

The following priority is adopted:

- 1. ARM<sup>®</sup> CPU IOBUS (No wait tolerated)

- 2. APB

- 3. EVSYS input events

For input events that require different actions on the same I/O pin, refer to 32.6.5 Events.

#### 32.8.6 Data Output Value Clear

| Name:     | OUTCLR                           |

|-----------|----------------------------------|

| Offset:   | 0x14                             |

| Reset:    | 0x0000000                        |

| Property: | PAC Write-Protection, Mix-Secure |

**Important:** For **SAM L11 Non-Secure** accesses, read and write accesses (RW\*) are allowed only if the security attribution for the corresponding I/O pin is set as Non-Secured in the NONSEC register.

This register allows the user to set one or more output I/O pin drive levels low, without doing a readmodify-write operation. Changes in this register will also be reflected in the Data Output Value (OUT), Data Output Value Toggle (OUTTGL) and Data Output Value Set (OUTSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31          | 30        | 29        | 28        | 27        | 26        | 25        | 24        |

|--------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|        |             |           |           | OUTCL     | R[31:24]  |           |           |           |

| Access | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0           | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |             |           |           |           |           |           |           |           |

| Bit    | 23          | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|        |             |           |           | OUTCL     | R[23:16]  |           |           |           |

| Access | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0           | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |             |           |           |           |           |           |           |           |

| Bit    | 15          | 14        | 13        | 12        | 11        | 10        | 9         | 8         |

|        |             |           |           | OUTCL     | .R[15:8]  |           |           |           |

| Access | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0           | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

|        |             |           |           |           |           |           |           |           |

| Bit    | 7           | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|        | OUTCLR[7:0] |           |           |           |           |           |           |           |

| Access | RW/RW*/RW   | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW | RW/RW*/RW |

| Reset  | 0           | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

#### Bits 31:0 - OUTCLR[31:0] PORT Data Output Value Clear

Writing '0' to a bit has no effect.

When using the synchronous path, the channel is able to generate interrupts. The channel status bits in the Channel Status register (CHSTATUS) are also updated and available for use.

#### **Resynchronized Path**

The resynchronized path are used when the event generator and the event channel do not share the same generator for the generic clock. When the resynchronized path is used, resynchronization of the event from the event generator is done in the channel.

When the resynchronized path is used, the channel is able to generate interrupts. The channel status bits in the Channel Status register (CHSTATUS) are also updated and available for use.

#### 33.5.2.7 Edge Detection

When synchronous or resynchronized paths are used, edge detection must be enabled. The event system can execute edge detection in three different ways:

- Generate an event only on the rising edge

- Generate an event only on the falling edge

- Generate an event on rising and falling edges.

Edge detection is selected by writing to the Edge Selection bit group of the Channel register (CHANNELn.EDGSEL).

#### 33.5.2.8 Event Latency

An event from an event generator is propagated to an event user with different latency, depending on event channel configuration.

- Asynchronous Path: The maximum routing latency of an external event is related to the internal signal routing and it is device dependent.

- Synchronous Path: The maximum routing latency of an external event is one GCLK\_EVSYS\_CHANNEL\_n clock cycle.

- Resynchronized Path: The maximum routing latency of an external event is three GCLK\_EVSYS\_CHANNEL\_n clock cycles.

The maximum propagation latency of a user event to the peripheral clock core domain is three peripheral clock cycles.

The event generators, event channel and event user clocks ratio must be selected in relation with the internal event latency constraints. Events propagation or event actions in peripherals may be lost if the clock setup violates the internal latencies.

#### 33.5.2.9 The Overrun Channel n Interrupt

The Overrun Channel n interrupt flag in the Interrupt Flag Status and Clear register (CHINTFLAGn.OVR) will be set, and the optional interrupt will be generated in the following cases:

- One or more event users on channel n is not ready when there is a new event.

- An event occurs when the previous event on channel m has not been handled by all event users connected to that channel.

The flag will only be set when using synchronous or resynchronized paths. In the case of asynchronous path, the CHINTFLAGn.OVR is always read as zero.

#### 33.5.2.10 The Event Detected Channel n Interrupt

The Event Detected Channel n interrupt flag in the Interrupt Flag Status and Clear register (CHINTFLAGn.EVD) is set when an event coming from the event generator configured on channel n is detected.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 34.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 34.5.10 Analog Connections

Not applicable.

#### 34.6 Functional Description

#### 34.6.1 Principle of Operation

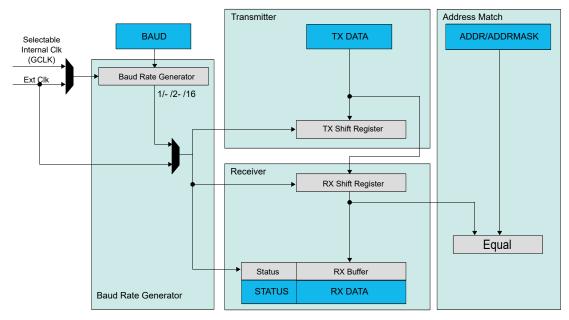

The basic structure of the SERCOM serial engine is shown in Figure 34-2. Labels in capital letters are synchronous to the system clock and accessible by the CPU; labels in lowercase letters can be configured to run on the GCLK\_SERCOMx\_CORE clock or an external clock.

#### Figure 34-2. SERCOM Serial Engine

The transmitter consists of a single write buffer and a shift register.

# 37. SERCOM I<sup>2</sup>C – SERCOM Inter-Integrated Circuit

# 37.1 Overview

The inter-integrated circuit ( $I^2C$ ) interface is one of the available modes in the serial communication interface (SERCOM).

The I<sup>2</sup>C interface uses the SERCOM transmitter and receiver configured as shown in Figure 37-1. Labels in capital letters are registers accessible by the CPU, while lowercase labels are internal to the SERCOM.

A SERCOM instance can be configured to be either an  $I^2C$  master or an  $I^2C$  slave. Both master and slave have an interface containing a shift register, a transmit buffer and a receive buffer. In addition, the  $I^2C$  master uses the SERCOM baud-rate generator, while the  $I^2C$  slave uses the SERCOM address match logic.

### **Related Links**

34. SERCOM – Serial Communication Interface

# 37.2 Features

SERCOM I<sup>2</sup>C includes the following features:

- Master or slave operation

- Can be used with DMA

- Philips I<sup>2</sup>C compatible

- SMBus<sup>™</sup> compatible

- PMBus compatible

- Support of 100kHz and 400kHz, 1MHz and 3.4MHz I<sup>2</sup>C mode

- 4-Wire operation supported

- Physical interface includes:

- Slew-rate limited outputs

- Filtered inputs

- Slave operation:

- Operation in all sleep modes

- Wake-up on address match

- 7-bit and 10-bit Address match in hardware for:

- Unique address and/or 7-bit general call address

- Address range

- Two unique addresses can be used with DMA

#### **Related Links**

34.2 Features

#### 37.10.5 Interrupt Enable Set

Name:INTENSETOffset:0x16Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7     | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|-------|---|---|---|---|---|-----|-----|

|        | ERROR |   |   |   |   |   | SB  | MB  |

| Access | R/W   |   |   |   |   |   | R/W | R/W |

| Reset  | 0     |   |   |   |   |   | 0   | 0   |

#### Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

**Bit 1 – SB** Slave on Bus Interrupt Enable Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Slave on Bus Interrupt Enable bit, which enables the Slave on Bus interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Slave on Bus interrupt is disabled. |

| 1     | The Slave on Bus interrupt is enabled.  |

Bit 0 – MB Master on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Master on Bus Interrupt Enable bit, which enables the Master on Bus interrupt.

| ν | /alue | Description                              |

|---|-------|------------------------------------------|

| 0 |       | The Master on Bus interrupt is disabled. |

| 1 |       | The Master on Bus interrupt is enabled.  |

#### 38.7.1.17 Channel x Compare Buffer Value, 8-bit Mode

Name:CCBUFxOffset:0x30 + x\*0x01 [x=0..1]Reset:0x00Property:Write-Synchronized

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

| Γ      |     |     |     | CCBL | JF[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

#### Bits 7:0 – CCBUF[7:0] Channel x Compare Buffer Value

These bits hold the value of the Channel x Compare Buffer Value. When the buffer valid flag is '1' and double buffering is enabled (CTRLBCLR.LUPD=1), the data from buffer registers will be copied into the corresponding CCx register under UPDATE condition (CTRLBSET.CMD=0x3), including the software update command.

#### 38.7.3.17 Channel x Compare Buffer Value, 32-bit Mode

| Name:     | CCBUFx               |

|-----------|----------------------|

| Offset:   | 0x30 + x*0x04 [x=01] |

| Reset:    | 0x0000000            |

| Property: | Write-Synchronized   |

| Bit    | 31  | 30           | 29  | 28    | 27      | 26  | 25  | 24  |

|--------|-----|--------------|-----|-------|---------|-----|-----|-----|

|        |     | CCBUF[31:24] |     |       |         |     |     |     |

| Access | R/W | R/W          | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0            | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |              |     |       |         |     |     |     |

| Bit    | 23  | 22           | 21  | 20    | 19      | 18  | 17  | 16  |

|        |     |              |     | CCBUF | [23:16] |     |     |     |

| Access | R/W | R/W          | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0            | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |              |     |       |         |     |     |     |

| Bit    | 15  | 14           | 13  | 12    | 11      | 10  | 9   | 8   |

|        |     |              |     | CCBU  | F[15:8] |     |     |     |

| Access | R/W | R/W          | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0            | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |              |     |       |         |     |     |     |

| Bit    | 7   | 6            | 5   | 4     | 3       | 2   | 1   | 0   |

|        |     |              |     | CCBL  | JF[7:0] |     |     |     |

| Access | R/W | R/W          | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0            | 0   | 0     | 0       | 0   | 0   | 0   |

#### Bits 31:0 – CCBUF[31:0] Channel x Compare Buffer Value

These bits hold the value of the Channel x Compare Buffer Value. When the buffer valid flag is '1' and double buffering is enabled (CTRLBCLR.LUPD=1), the data from buffer registers will be copied into the corresponding CCx register under UPDATE condition (CTRLBSET.CMD=0x3), including the software update command.

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 40.5.10 Analog Connections

Not applicable.

#### 40.6 Functional Description

#### 40.6.1 Principle of Operation

Configurable Custom Logic (CCL) is a programmable logic block that can use the device port pins, internal peripherals, and the internal Event System as both input and output channels. The CCL can serve as glue logic between the device and external devices. The CCL can eliminate the need for external logic component and can also help the designer overcome challenging real-time constrains by combining core independent peripherals in clever ways to handle the most time critical parts of the application independent of the CPU.

#### 40.6.2 Operation

#### 40.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the corresponding even LUT is disabled (LUTCTRLx.ENABLE=0):

• Sequential Selection bits in the Sequential Control x (SEQCTRLx.SEQSEL) register

The following registers are enable-protected, meaning that they can only be written when the corresponding LUT is disabled (LUTCTRLx.ENABLE=0):

• LUT Control x (LUTCTRLx) register, except the ENABLE bit

Enable-protected bits in the LUTCTRLx registers can be written at the same time as LUTCTRLx.ENABLE is written to '1', but not at the same time as LUTCTRLx.ENABLE is written to '0'.

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 40.6.2.2 Enabling, Disabling, and Resetting

The CCL is enabled by writing a '1' to the Enable bit in the Control register (CTRL.ENABLE). The CCL is disabled by writing a '0' to CTRL.ENABLE.

Each LUT is enabled by writing a '1' to the Enable bit in the LUT Control x register (LUTCTRLx.ENABLE). Each LUT is disabled by writing a '0' to LUTCTRLx.ENABLE.

The CCL is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST). All registers in the CCL will be reset to their initial state, and the CCL will be disabled. Refer to 40.8.1 CTRL for details.

#### 40.6.2.3 Lookup Table Logic

The lookup table in each LUT unit can generate any logic expression OUT as a function of three inputs (IN[2:0]), as shown in Figure 40-2. One or more inputs can be masked. The truth table for the expression is defined by TRUTH bits in LUT Control x register (LUTCTRLx.TRUTH).

#### 41.8.8 Sequence Status

| Name:     | SEQSTATUS |

|-----------|-----------|

| Offset:   | 0x07      |

| Reset:    | 0x00      |

| Property: | -         |

| Bit    | 7       | 6 | 5 | 4 | 3 | 2             | 1 | 0 |

|--------|---------|---|---|---|---|---------------|---|---|

|        | SEQBUSY |   |   |   |   | SEQSTATE[4:0] |   |   |

| Access | R       |   |   | R | R | R             | R | R |

| Reset  | 0       |   |   | 0 | 0 | 0             | 0 | 0 |

#### Bit 7 – SEQBUSY Sequence busy

This bit is set when the sequence start.

This bit is clear when the last conversion in a sequence is done.

#### Bits 4:0 - SEQSTATE[4:0] Sequence State

These bit fields are the pointer of sequence. This value identifies the last conversion done in the sequence.

## 41.8.14 Window Monitor Upper Threshold

| Name:     | WINUT                                    |

|-----------|------------------------------------------|

| Offset:   | 0x10                                     |

| Reset:    | 0x0000                                   |

| Property: | PAV Write-Protection, Write-Synchronized |

| Bit    | 15  | 14          | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----|-------------|-----|------|--------|-----|-----|-----|

|        |     | WINUT[15:8] |     |      |        |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |             |     |      |        |     |     |     |

| Bit    | 7   | 6           | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |             |     | WINU | T[7:0] |     |     |     |

| Access | R/W | R/W         | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0           | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 15:0 - WINUT[15:0] Window Upper Threshold

If the window monitor is enabled, these bits define the upper threshold value.

#### 42.8.7 Status A

| Name:     | STATUSA   |

|-----------|-----------|

| Offset:   | 0x07      |

| Reset:    | 0x00      |

| Property: | Read-Only |

| Bit    | 7 | 6 | 5     | 4       | 3 | 2 | 1      | 0      |

|--------|---|---|-------|---------|---|---|--------|--------|

|        |   |   | WSTAT | E0[1:0] |   |   | STATEx | STATEx |

| Access |   |   | R     | R       |   |   | R      | R      |

| Reset  |   |   | 0     | 0       |   |   | 0      | 0      |

#### Bits 5:4 – WSTATE0[1:0] Window 0 Current State

These bits show the current state of the signal if the window 0 mode is enabled.

| Value | Name   | Description             |

|-------|--------|-------------------------|

| 0x0   | ABOVE  | Signal is above window  |

| 0x1   | INSIDE | Signal is inside window |

| 0x2   | BELOW  | Signal is below window  |

| 0x3   |        | Reserved                |

Bits 1,0 – STATEx Comparator x Current State

This bit shows the current state of the output signal from COMPx. STATEx is valid only when STATUSB.READYx is one.